Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf870-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

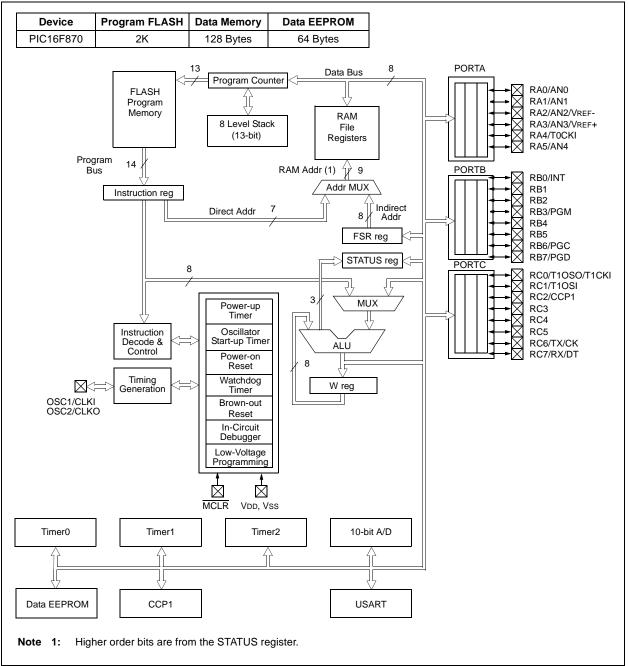

# 1.0 DEVICE OVERVIEW

This document contains device specific information. Additional information may be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules. There are two devices (PIC16F870 and PIC16F871) covered by this data sheet. The PIC16F870 device comes in a 28-pin package and the PIC16F871 device comes in a 40-pin package. The 28-pin device does not have a Parallel Slave Port implemented.

The following two figures are device block diagrams sorted by pin number: 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

FIGURE 1-1: PIC16F870 BLOCK DIAGRAM

| TABLE 1-2: | PIC16F871 PINOUT DESCRIPTION |

|------------|------------------------------|

|------------|------------------------------|

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                             |

|-------------------|-------------|--------------|-------------|---------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKI         | 13          | 14           | 30          | Ι             | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                   |

| OSC2/CLKO         | 14          | 15           | 31          | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp/THV      | 1           | 2            | 18          | I/P           | ST                     | Master Clear (Reset) input or programming voltage input or<br>High Voltage Test mode control. This pin is an active low<br>RESET to the device.                                                         |

|                   |             |              |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                     |

| RA0/AN0           | 2           | 3            | 19          | I/O           | TTL                    | RA0 can also be analog input 0.                                                                                                                                                                         |

| RA1/AN1           | 3           | 4            | 20          | I/O           | TTL                    | RA1 can also be analog input 1.                                                                                                                                                                         |

| RA2/AN2/VREF-     | 4           | 5            | 21          | I/O           | TTL                    | RA2 can also be analog input 2 or negative analog reference voltage.                                                                                                                                    |

| RA3/AN3/VREF+     | 5           | 6            | 22          | I/O           | TTL                    | RA3 can also be analog input 3 or positive analog reference voltage.                                                                                                                                    |

| RA4/T0CKI         | 6           | 7            | 23          | I/O           | ST                     | RA4 can also be the clock input to the Timer0 timer/counter. Output is open drain type.                                                                                                                 |

| RA5/AN4           | 7           | 8            | 24          | I/O           | TTL                    | RA5 can also be analog input 4.                                                                                                                                                                         |

|                   |             |              |             |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                           |

| RB0/INT           | 33          | 36           | 8           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                             |

| RB1               | 34          | 37           | 9           | I/O           | TTL                    |                                                                                                                                                                                                         |

| RB2               | 35          | 38           | 10          | I/O           | TTL                    |                                                                                                                                                                                                         |

| RB3/PGM           | 36          | 39           | 11          | I/O           | TTL/ST <sup>(1)</sup>  | RB3 can also be the low voltage programming input.                                                                                                                                                      |

| RB4               | 37          | 41           | 14          | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                |

| RB5               | 38          | 42           | 15          | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                |

| RB6/PGC           | 39          | 43           | 16          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming clock.                                                                                                                        |

| RB7/PGD           | 40          | 44           | 17          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming data.                                                                                                                         |

|                   |             |              |             |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                     |

| RC0/T1OSO/T1CKI   | 15          | 16           | 32          | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or a Timer1<br>clock input.                                                                                                                                |

| RC1/T1OSI         | 16          | 18           | 35          | I/O           | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                            |

| RC2/CCP1          | 17          | 19           | 36          | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output.<br>PWM1 output.                                                                                                                                     |

| RC3               | 18          | 20           | 37          | I/O           | ST                     |                                                                                                                                                                                                         |

| RC4               | 23          | 25           | 42          | I/O           | ST                     |                                                                                                                                                                                                         |

| RC5               | 24          | 26           | 43          | I/O           | ST                     |                                                                                                                                                                                                         |

| RC6/TX/CK         | 25          | 27           | 44          | I/O           | ST                     | RC6 can also be the USART Asynchronous Transmit of<br>Synchronous Clock.                                                                                                                                |

| RC7/RX/DT         | 26          | 29           | 1           | I/O           | ST                     | RC7 can also be the USART Asynchronous Receive of<br>Synchronous Data.                                                                                                                                  |

| Legend: I = input |             | O = 0        | utput       |               | I/O = input/ou         | Itput P = power                                                                                                                                                                                         |

| — = Not           | used        |              | TTL inp     |               | ST = Schmitt           |                                                                                                                                                                                                         |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt or LVP mode.

This buffer is a Schmitt Trigger input when conligured as an external interrupt of LVP mode

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

## 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6          | Bit 5         | Bit 4          | Bit 3          | Bit 2           | Bit 1      | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS <sup>(2)</sup> |

|----------------------|---------|----------------------|----------------|---------------|----------------|----------------|-----------------|------------|---------|-----------------------|------------------------------------------------|

| Bank 0               |         |                      |                |               |                |                |                 |            |         |                       |                                                |

| 00h <sup>(4)</sup>   | INDF    | Addressing           | this location  | l register)   | 0000 0000      | 0000 0000      |                 |            |         |                       |                                                |

| 01h                  | TMR0    | Timer0 Mod           | dule's Regist  | er            |                |                |                 |            |         | xxxx xxxx             | uuuu uuuu                                      |

| 02h <sup>(4)</sup>   | PCL     | Program Co           | ounter's (PC   | ) Least Sigr  | ificant Byte   |                |                 |            |         | 0000 0000             | 0000 0000                                      |

| 03h <sup>(4)</sup>   | STATUS  | IRP                  | RP1            | RP0           | TO             | PD             | Z               | DC         | С       | 0001 1xxx             | 000q quuu                                      |

| 04h <sup>(4)</sup>   | FSR     | Indirect Dat         | ta Memory A    | ddress Poir   | nter           |                |                 | •          | •       | xxxx xxxx             | uuuu uuuu                                      |

| 05h                  | PORTA   | —                    | —              | PORTA Da      | ta Latch whe   | n written: PO  | RTA pins wh     | ien read   |         | 0x 0000               | 0u 0000                                        |

| 06h                  | PORTB   | PORTB Da             | ta Latch whe   | en written: P | ORTB pins v    | vhen read      |                 |            |         | xxxx xxxx             | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Da             | ta Latch whe   | en written: F | ORTC pins v    | when read      |                 |            |         | xxxx xxxx             | uuuu uuuu                                      |

| 08h <sup>(5)</sup>   | PORTD   | PORTD Da             | ta Latch whe   | en written: F | ORTD pins v    | when read      |                 |            |         | xxxx xxxx             | uuuu uuuu                                      |

| 09h <sup>(5)</sup>   | PORTE   | _                    | _              | _             | _              | _              | RE2             | RE1        | RE0     | xxx                   | uuu                                            |

| 0Ah <sup>(1,4)</sup> | PCLATH  | _                    | _              | _             | Write Buffer   | for the upper  | r 5 bits of the | Program Co | ounter  | 0 0000                | 0 0000                                         |

| 0Bh <sup>(4)</sup>   | INTCON  | GIE                  | PEIE           | TOIE          | INTE           | RBIE           | T0IF            | INTF       | RBIF    | 0000 000x             | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF           | RCIF          | TXIF           | _              | CCP1IF          | TMR2IF     | TMR1IF  | 0000 -000             | 0000 -000                                      |

| 0Dh                  | PIR2    | _                    | _              | _             | EEIF           | _              | _               | _          | _       |                       | 0                                              |

| 0Eh                  | TMR1L   | Holding Re           | gister for the | Least Sign    | ificant Byte o | f the 16-bit T | MR1 Registe     | er         |         | xxxx xxxx             | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding Re           | gister for the | Most Signi    | ficant Byte of | the 16-bit TM  | VR1 Register    | r          |         | XXXX XXXX             | uuuu uuuu                                      |

| 10h                  | T1CON   | —                    | —              | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC          | TMR1CS     | TMR1ON  | 00 0000               | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 Mod           | dule's Regist  | er            |                |                |                 |            |         | 0000 0000             | 0000 0000                                      |

| 12h                  | T2CON   | —                    | TOUTPS3        | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON          | T2CKPS1    | T2CKPS0 | -000 0000             | -000 0000                                      |

| 13h                  | _       | Unimpleme            | nted           |               |                |                |                 |            |         | _                     | _                                              |

| 14h                  | _       | Unimpleme            | nted           |               |                |                |                 |            |         | _                     | _                                              |

| 15h                  | CCPR1L  | Capture/Co           | mpare/PWN      | 1 Register1   | (LSB)          |                |                 |            |         | xxxx xxxx             | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co           | mpare/PWN      | 1 Register1   | (MSB)          |                |                 |            |         | XXXX XXXX             | uuuu uuuu                                      |

| 17h                  | CCP1CON | _                    | _              | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2          | CCP1M1     | CCP1M0  | 00 0000               | 00 0000                                        |

| 18h                  | RCSTA   | SPEN                 | RX9            | SREN          | CREN           | ADDEN          | FERR            | OERR       | RX9D    | 0000 000x             | 0000 000x                                      |

| 19h                  | TXREG   | USART Tra            | Insmit Data I  | Register      |                |                |                 |            |         | 0000 0000             | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Re             | ceive Data F   | Register      |                |                |                 |            |         | 0000 0000             | 0000 0000                                      |

| 1Bh                  | _       | Unimpleme            | nted           |               |                |                |                 |            |         | _                     | _                                              |

| 1Ch                  | —       | Unimpleme            | nted           |               |                |                |                 |            |         | _                     | _                                              |

| 1Dh                  | _       | Unimpleme            | nted           |               |                |                |                 |            |         | _                     | _                                              |

| 1Eh                  | ADRESH  | -                    | Register Hig   | h Byte        |                |                |                 |            |         | xxxx xxxx             | uuuu uuuu                                      |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0          | CHS2          | CHS1           | CHS0           | GO/DONE         |            | ADON    | 0000 00-0             | 0000 00-0                                      |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

## 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary".

| Note 1: | The C and DC bits operate as a borrow       |  |  |  |  |  |  |  |  |  |

|---------|---------------------------------------------|--|--|--|--|--|--|--|--|--|

|         | and digit borrow bit, respectively, in sub- |  |  |  |  |  |  |  |  |  |

|         | traction. See the SUBLW and SUBWF           |  |  |  |  |  |  |  |  |  |

|         | instructions for examples.                  |  |  |  |  |  |  |  |  |  |

## REGISTER 2-1: STATUS REGISTER (ADDRESS: 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                                                                                                                                   | R/W-0                                           | R/W-0       | R-1           | R-1                          | R/W-x        | R/W-x          | R/W-x |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------|---------------|------------------------------|--------------|----------------|-------|--|--|--|--|--|

|         | IRP                                                                                                                                                                                                                                                     | RP1                                             | RP0         | TO            | PD                           | Z            | DC             | С     |  |  |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                   |                                                 |             |               |                              |              |                | bit 0 |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                         |                                                 |             |               |                              |              |                |       |  |  |  |  |  |

| bit 7-6 | IRP: Register Bank Select bit (used for indirect addressing)                                                                                                                                                                                            |                                                 |             |               |                              |              |                |       |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                         | 2, 3 (100h - 1                                  | -           |               |                              |              |                |       |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                         | 0, 1 (00h - Fl                                  | ,           | ite (used for | direct addres                |              |                |       |  |  |  |  |  |

| bit 6-5 |                                                                                                                                                                                                                                                         | -                                               |             | nts (used for | direct addres                | ssing)       |                |       |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                         | : 3 (180h - 1l<br>: 2 (100h - 1]                |             |               |                              |              |                |       |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                         | 1 (80h - FF                                     |             |               |                              |              |                |       |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                         | 0 (00h - 7F                                     | •           |               |                              |              |                |       |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                         | k is 128 byte                                   | S.          |               |                              |              |                |       |  |  |  |  |  |

| bit 4   | TO: Time-                                                                                                                                                                                                                                               |                                                 |             | <i></i>       | · · ·                        |              |                |       |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                         | ower-up, CI<br>T time-out o                     |             | uction, or SL | EEP instructio               | on           |                |       |  |  |  |  |  |

| bit 3   | PD: Powe                                                                                                                                                                                                                                                | r-down bit                                      |             |               |                              |              |                |       |  |  |  |  |  |

|         | 1 = After p                                                                                                                                                                                                                                             | 1 = After power-up or by the CLRWDT instruction |             |               |                              |              |                |       |  |  |  |  |  |

|         | 0 = By exe                                                                                                                                                                                                                                              | ecution of the                                  | e SLEEP ins | struction     |                              |              |                |       |  |  |  |  |  |

| bit 2   | Z: Zero bit                                                                                                                                                                                                                                             | t                                               |             |               |                              |              |                |       |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                         | esult of an ar<br>esult of an ar                |             |               | on is zero<br>on is not zero | )            |                |       |  |  |  |  |  |

| bit 1   |                                                                                                                                                                                                                                                         |                                                 | •           |               | BLW, SUBWF II                | nstructions) |                |       |  |  |  |  |  |

|         | (for borrow, the polarity is reversed)                                                                                                                                                                                                                  |                                                 |             |               |                              |              |                |       |  |  |  |  |  |

|         | <ul> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> </ul>                                                                                                |                                                 |             |               |                              |              |                |       |  |  |  |  |  |

| bit 0   | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)                                                                                                                                                                                           |                                                 |             |               |                              |              |                |       |  |  |  |  |  |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                 |                                                 |             |               |                              |              |                |       |  |  |  |  |  |

|         | <b>Note:</b> For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register. |                                                 |             |               |                              |              |                |       |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                         |                                                 |             |               |                              |              |                |       |  |  |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                 |                                                 |             | A/ */ 11 1*/  |                              |              |                |       |  |  |  |  |  |

|         | R = Reada                                                                                                                                                                                                                                               | able bit                                        | VV = V      | Nritable bit  | U = Unim                     | plemented l  | oit, read as ' | ·0′   |  |  |  |  |  |

'1' = Bit is set

n = Value at POR

x = Bit is unknown

'0' = Bit is cleared

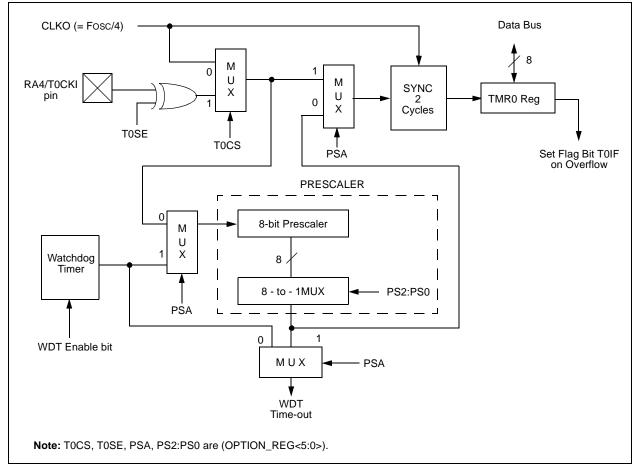

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

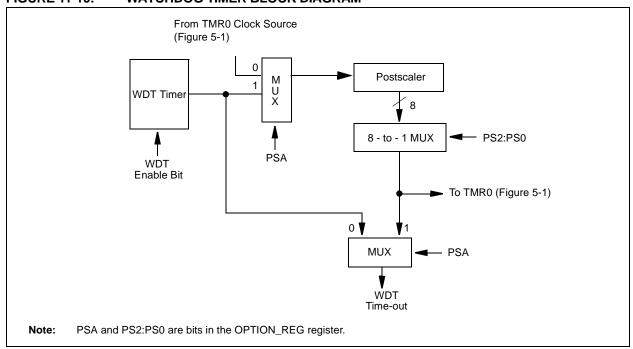

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PIC® Mid-Range MCU Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising, or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

# 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

# PIC16F870/871

NOTES:

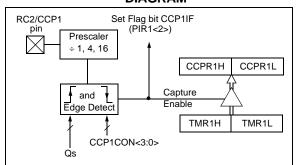

## 8.2 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following:

- Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

The type of event is configured by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new value.

## 8.2.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|

|       | output, a write to the port can cause a |  |  |  |  |  |  |  |

|       | capture condition.                      |  |  |  |  |  |  |  |

### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

## 8.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in Operating mode.

## 8.2.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

| EXAMPLE 8-1: | CHANGING BETWEEN   |

|--------------|--------------------|

|              | CAPTURE PRESCALERS |

| -     |             |   | Turn CCP module off    |

|-------|-------------|---|------------------------|

| MOVLW | NEW_CAPT_PS | ; | Load the W reg with    |

|       |             | ; | the new prescaler      |

|       |             | ; | move value and CCP ON  |

| MOVWF | CCP1CON     | ; | Load CCP1CON with this |

|       |             | ; | value                  |

|       |             |   |                        |

# 9.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 9-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 9-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

## 9.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

## TABLE 9-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | N/A                        |

|      |                                           |                            |

Legend: X = value in SPBRG (0 to 255)

## TABLE 9-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7    | Bit 6                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|-------|----------|-----------------------------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 98h     | TXSTA | CSRC     | TX9                         | TXEN  | SYNC  |       | BRGH  | TRMT  | TX9D  | 0000 -010             | 0000 -010                       |

| 18h     | RCSTA | SPEN     | RX9                         | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000x             | x000 000x                       |

| 99h     | SPBRG | Baud Rat | aud Rate Generator Register |       |       |       |       |       |       |                       | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

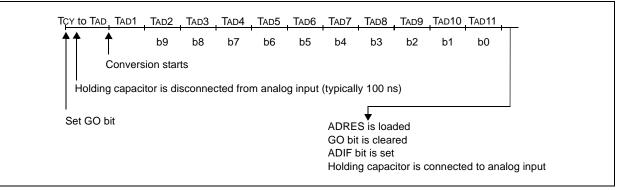

## 10.4 A/D Conversions

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2 TAD wait is required before the next

## FIGURE 10-3: A/D CONVERSION TAD CYCLES

acquisition is started. After this 2 TAD wait, acquisition on the selected channel is automatically started. The GO/DONE bit can then be set to start the conversion.

In Figure 10-3, after the GO bit is set, the first time segment has a minimum of TCY and a maximum of TAD.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

## 10.4.1 A/D RESULT REGISTERS

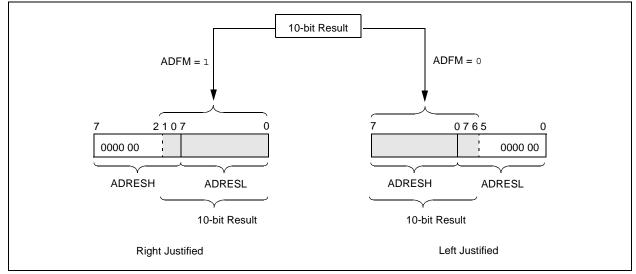

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16-bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D For-

mat Select bit (ADFM) controls this justification. Figure 10-4 shows the operation of the A/D result justification. The extra bits are loaded with '0'. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

## FIGURE 10-4: A/D RESULT JUSTIFICATION

# 11.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTEN (Section 11.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## FIGURE 11-10: WATCHDOG TIMER BLOCK DIAGRAM

## TABLE 11-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|-----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BOREN <sup>(1)</sup> | CP1   | CP0   | PWRTEN <sup>(1)</sup> | WDTEN | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 11-1 for operation of these bits.

| Rotate Left f through Carry                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |

| $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                               |

| See description below                                                                                                                                                                                         |

| С                                                                                                                                                                                                             |

| The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |

|                                                                                                                                                                                                               |

# SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                 |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is cleared. Time-out status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                             |

| Operands:        | None                                                                                                                                                       |

| Operation:       | $TOS\toPC$                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                       |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                   |

| Operation:       | See description below                                                                                                                                                                                             |

| Status Affected: | С                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |

|                  | C Register f                                                                                                                                                                                                      |

| SUBLW            | Subtract W from Literal                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |

| Operation:       | $k \text{ - } (W) \to (W)$                                                                                                   |

| Status Affected: | C, DC, Z                                                                                                                     |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |

| SUBWF               | Subtract W from f                                                                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [label] SUBWF f,d                                                                                                                                                                       |

| Operands:           | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                       |

| Operation:          | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                   |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                                |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |

# 13.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM.net<sup>™</sup> Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 4 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ<sup>®</sup>

- PICDEM MSC

- microID®

- CAN

- PowerSmart®

- Analog

# 13.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor with color coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High level source code debugging

- Mouse over variable inspection

- Extensive on-line help

- The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

# 13.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects

- User defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

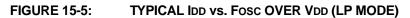

## 14.1 DC Characteristics: PIC16F870/871 (Industrial, Extended) PIC16LF870/871 (Commercial, Industrial) (Continued)

| PIC16LI<br>(Com       |       | <b>1</b><br>Industrial)                   |     |                   |                | ure -40°       | litions (unless otherwise stated)<br>$^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$\le TA \le +70^{\circ}C$ for Commercial                                                          |

|-----------------------|-------|-------------------------------------------|-----|-------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIC16F8<br>(Indus     |       | ttended)                                  |     |                   |                | ure -40        | litions (unless otherwise stated)<br>$^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$^{\circ}C \le TA \le +125^{\circ}C$ for Extended                                                 |

| Param<br>No.          | Sym   | Characteristic                            | Min | Тур†              | Max            | Units          | Conditions                                                                                                                                                                                   |

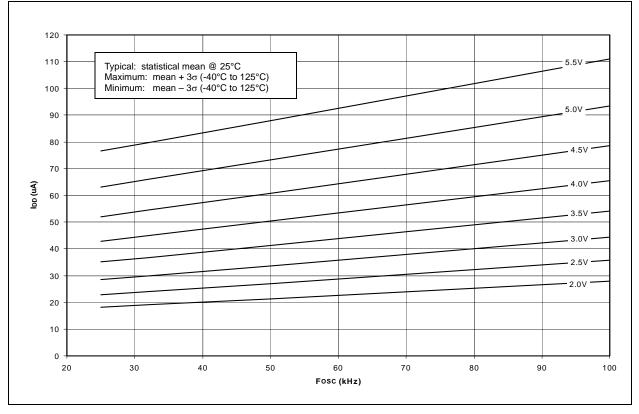

|                       | Idd   | Supply Current <sup>(2,5)</sup>           |     |                   |                |                |                                                                                                                                                                                              |

| D010                  |       | PIC16LF870/871                            | —   | 0.6               | 2.0            | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V <b>(Note 4)</b>                                                                                                                         |

| D010A                 |       |                                           |     | 20                | 35             | μA             | LP osc configuration<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                              |

| D010                  |       | PIC16F870/871                             |     | 1.6               | 4              | mA             | XT, RC osc configuration<br>FOSC = 4 MHz, VDD = 5.5V <b>(Note 4)</b>                                                                                                                         |

| D013                  |       |                                           | —   | 7                 | 15             |                | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V, -40°C to +85°C                                                                                                                            |

|                       |       |                                           |     | 7                 | 15             | mA             | HS osc configuration<br>FOSC = 10 MHz, VDD = $5.5V$ , $-40^{\circ}C$ to $+125^{\circ}C$                                                                                                      |

| D015*                 | ∆lbor | Brown-out Reset<br>Current <sup>(6)</sup> | —   | 85                | 200            | μA             | BOR enabled, VDD = 5.0V                                                                                                                                                                      |

|                       | IPD   | Power-down Current <sup>(3,5)</sup>       |     |                   |                |                |                                                                                                                                                                                              |

| D020<br>D021<br>D021A |       | PIC16LF870/871                            |     | 7.5<br>0.8<br>0.9 | 30<br>4.5<br>5 | μΑ<br>μΑ<br>μΑ | VDD = 3.0V, WDT enabled, -40°C to +85°C<br>VDD = 3.0V, WDT disabled, 0°C to +70°C<br>VDD = 3.0V, WDT disabled, -40°C to +85°C                                                                |

| D020<br>D20A          |       | PIC16F870/871                             |     | 10.5<br>10.5      | 42<br>60       | μΑ<br>μΑ       | VDD = 4.0V, WDT enabled, -40°C to +85°C<br>VDD = 4.0V, WDT enabled, -40°C to +125°C                                                                                                          |

| D021<br>D021A<br>D21B |       |                                           |     | 1.5<br>1.5<br>1.5 | 16<br>19<br>30 | μΑ<br>μΑ<br>μΑ | VDD = 4.0V, WDT disabled, $-0^{\circ}$ C to $+70^{\circ}$ C<br>VDD = 4.0V, WDT disabled, $-40^{\circ}$ C to $+85^{\circ}$ C<br>VDD = 4.0V, WDT disabled, $-40^{\circ}$ C to $+125^{\circ}$ C |

| D023*                 | ∆lbor | Brown-out Reset<br>Current <sup>(6)</sup> | _   | 85                | 200            | μΑ             | BOR enabled, $VDD = 5.0V$                                                                                                                                                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

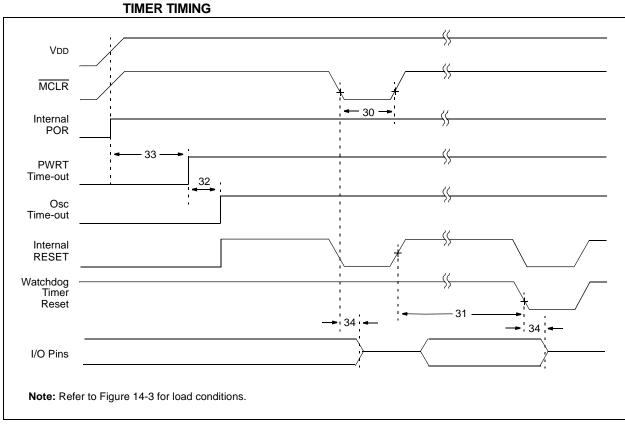

# FIGURE 14-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

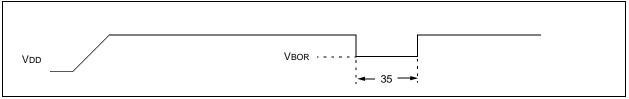

## FIGURE 14-7: BROWN-OUT RESET TIMING

# TABLE 14-3:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                         | Min | Тур†      | Max | Units | Conditions               |

|--------------|-------|--------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30           | TmcL  | MCLR Pulse Width (low)                                 | 2   | _         | _   | μS    | VDD = 5V, -40°C to +85°C |

| 31*          | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32           | Tost  | Oscillation Start-up Timer Period                      | _   | 1024 Tosc | —   |       | Tosc = OSC1 period       |

| 33*          | TPWRT | Power up Timer Period                                  | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34           | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _         | 2.1 | μS    |                          |

| 35           | TBOR  | Brown-out Reset pulse width                            | 100 | —         | —   | μS    | $VDD \leq VBOR (D005)$   |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16F870/871

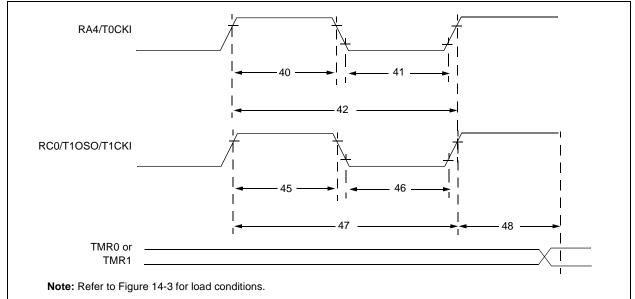

## FIGURE 14-8: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| Param<br>No. | Sym       |                                                | Characteristic     |                       | Min                                              | Тур† | Max    | Units | Conditions                         |

|--------------|-----------|------------------------------------------------|--------------------|-----------------------|--------------------------------------------------|------|--------|-------|------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse V                             | Vidth              | No Prescaler          | 0.5 TCY + 20                                     | —    | _      | ns    | Must also meet                     |

|              |           |                                                |                    | With Prescaler        | 10                                               | _    | _      | ns    | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pulse W                              | /idth              | No Prescaler          | 0.5 TCY + 20                                     | —    | _      | ns    | Must also meet                     |

|              |           |                                                |                    | With Prescaler        | 10                                               | —    |        | ns    | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period                                   |                    | No Prescaler          | TCY + 40                                         | —    | _      | ns    |                                    |

|              |           |                                                |                    | With Prescaler        | Greater of:<br>20 or <u>TcY + 40</u><br>N        | -    |        | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time                                | Synchronous, Pres  | scaler = 1            | 0.5 TCY + 20                                     | —    | _      | ns    | Must also meet                     |

|              |           |                                                | Synchronous,       | Standard(F)           | 15                                               | —    |        | ns    | parameter 47                       |

|              |           |                                                | Prescaler = 2,4,8  | Extended(LF)          | 25                                               | —    |        | ns    |                                    |

|              |           |                                                | Asynchronous       | Standard(F)           | 30                                               | —    | —      | ns    |                                    |

|              |           |                                                |                    | Extended(LF)          | 50                                               | —    | _      | ns    |                                    |

| 46*          | Tt1L      | T1CKI Low Time                                 | Synchronous, Pres  | scaler = 1            | 0.5 TCY + 20                                     | _    |        | ns    | Must also meet                     |

|              |           |                                                | Synchronous,       | Standard(F)           | 15                                               | —    |        | ns    | parameter 47                       |

|              |           |                                                | Prescaler = 2,4,8  | Extended(LF)          | 25                                               | —    |        | ns    |                                    |

|              |           |                                                | Asynchronous       | Standard(F)           | 30                                               | —    | _      | ns    |                                    |

|              |           |                                                |                    | Extended(LF)          | 50                                               | —    | _      | ns    |                                    |

| 47*          | Tt1P      | T1CKI input period                             | Synchronous        | Standard( <b>F</b> )  | <u>Greater of:</u><br>30 or <u>Tcy + 40</u><br>N | _    |        | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                |                    | Extended( <b>LF</b> ) | <u>Greater of:</u><br>50 or <u>Tcy + 40</u><br>N |      |        |       | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                | Asynchronous       | Standard(F)           | 60                                               | —    | _      | ns    |                                    |

|              |           |                                                |                    | Extended(LF)          | 100                                              | _    | _      | ns    |                                    |

|              | Ft1       | Timer1 oscillator inp<br>(oscillator enabled b |                    |                       | DC                                               | —    | 200    | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from external                            | clock edge to time | rincrement            | 2 Tosc                                           | —    | 7 Tosc | —     |                                    |

| TABLE 14-4: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|             |                                               |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

© 2000-2013 Microchip Technology Inc.

# **16.0 PACKAGING INFORMATION**

# 16.1 Package Marking Information

## 28-Lead PDIP (Skinny DIP)

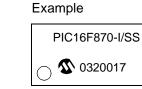

### Example

## 28-Lead SOIC

## Example

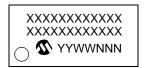

## 28-Lead SSOP

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                               | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                  |