Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 64 x 8                                                                     |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf870t-i-ss |

| Key Features<br>PICmicro™ Mid-Range MCU Family Reference Manual<br>(DS33023) | PIC16F870            | PIC16F871            |

|------------------------------------------------------------------------------|----------------------|----------------------|

| Operating Frequency                                                          | DC - 20 MHz          | DC - 20 MHz          |

| RESETS (and Delays)                                                          | POR, BOR (PWRT, OST) | POR, BOR (PWRT, OST) |

| FLASH Program Memory (14-bit words)                                          | 2K                   | 2K                   |

| Data Memory (bytes)                                                          | 128                  | 128                  |

| EEPROM Data Memory                                                           | 64                   | 64                   |

| Interrupts                                                                   | 10                   | 11                   |

| I/O Ports                                                                    | Ports A,B,C          | Ports A,B,C,D,E      |

| Timers                                                                       | 3                    | 3                    |

| Capture/Compare/PWM modules                                                  | 1                    | 1                    |

| Serial Communications                                                        | USART                | USART                |

| Parallel Communications                                                      | _                    | PSP                  |

| 10-bit Analog-to-Digital Module                                              | 5 input channels     | 8 input channels     |

| Instruction Set                                                              | 35 Instructions      | 35 Instructions      |

**TABLE 1-2:** PIC16F871 PINOUT DESCRIPTION

| Pin Name        | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                             |  |  |

|-----------------|-------------|--------------|-------------|---------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OSC1/CLKI       | 13          | 14           | 30          | I             | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                   |  |  |

| OSC2/CLKO       | 14          | 15           | 31          | 0             | Н                      | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |  |  |

| MCLR/VPP/THV    | 1           | 2            | 18          | I/P           | ST                     | Master Clear (Reset) input or programming voltage input or High Voltage Test mode control. This pin is an active low RESET to the device.                                                               |  |  |

|                 |             |              |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                     |  |  |

| RA0/AN0         | 2           | 3            | 19          | I/O           | TTL                    | RA0 can also be analog input 0.                                                                                                                                                                         |  |  |

| RA1/AN1         | 3           | 4            | 20          | I/O           | TTL                    | RA1 can also be analog input 1.                                                                                                                                                                         |  |  |

| RA2/AN2/VREF-   | 4           | 5            | 21          | I/O           | TTL                    | RA2 can also be analog input 2 or negative analog reference voltage.                                                                                                                                    |  |  |

| RA3/AN3/VREF+   | 5           | 6            | 22          | I/O           | TTL                    | RA3 can also be analog input 3 or positive analog reference voltage.                                                                                                                                    |  |  |

| RA4/T0CKI       | 6           | 7            | 23          | I/O           | ST                     | RA4 can also be the clock input to the Timer0 timer/counter. Output is open drain type.                                                                                                                 |  |  |

| RA5/AN4         | 7           | 8            | 24          | I/O           | TTL                    | RA5 can also be analog input 4.                                                                                                                                                                         |  |  |

|                 |             |              |             |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                           |  |  |

| RB0/INT         | 33          | 36           | 8           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                             |  |  |

| RB1             | 34          | 37           | 9           | I/O           | TTL                    |                                                                                                                                                                                                         |  |  |

| RB2             | 35          | 38           | 10          | I/O           | TTL                    |                                                                                                                                                                                                         |  |  |

| RB3/PGM         | 36          | 39           | 11          | I/O           | TTL/ST <sup>(1)</sup>  | RB3 can also be the low voltage programming input.                                                                                                                                                      |  |  |

| RB4             | 37          | 41           | 14          | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                |  |  |

| RB5             | 38          | 42           | 15          | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                |  |  |

| RB6/PGC         | 39          | 43           | 16          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming clock.                                                                                                                           |  |  |

| RB7/PGD         | 40          | 44           | 17          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming data.                                                                                                                         |  |  |

|                 |             |              |             |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                     |  |  |

| RC0/T1OSO/T1CKI | 15          | 16           | 32          | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or a Timer1 clock input.                                                                                                                                   |  |  |

| RC1/T1OSI       | 16          | 18           | 35          | I/O           | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                            |  |  |

| RC2/CCP1        | 17          | 19           | 36          | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                                                                                                                         |  |  |

| RC3             | 18          | 20           | 37          | I/O           | ST                     |                                                                                                                                                                                                         |  |  |

| RC4             | 23          | 25           | 42          | I/O           | ST                     |                                                                                                                                                                                                         |  |  |

| RC5             | 24          | 26           | 43          | I/O           | ST                     |                                                                                                                                                                                                         |  |  |

| RC6/TX/CK       | 25          | 27           | 44          | I/O           | ST                     | RC6 can also be the USART Asynchronous Transmit or Synchronous Clock.                                                                                                                                   |  |  |

| RC7/RX/DT       | 26          | 29           | 1           | I/O           | ST                     | RC7 can also be the USART Asynchronous Receive or Synchronous Data.                                                                                                                                     |  |  |

|                 |             |              |             |               |                        | thuit D namer                                                                                                                                                                                           |  |  |

Legend: I = input O = output

I/O = input/output

P = power

TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt or LVP mode.

- 2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

- 4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

FIGURE 2-2: PIC16F870/871 REGISTER FILE MAP

|                      | File<br>Address |                      | File<br>Address |                     | File<br>Address | P                       | File<br>Address |

|----------------------|-----------------|----------------------|-----------------|---------------------|-----------------|-------------------------|-----------------|

| Indirect addr.(*)    | 00h             | Indirect addr.(*)    | 80h             | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180h            |

| TMR0                 | 01h             | OPTION_REG           | 81h             | TMR0                | 101h            | OPTION_REG              | 181h            |

| PCL                  | 02h             | PCL                  | 82h             | PCL                 | 102h            | PCL                     | 182h            |

| STATUS               | 03h             | STATUS               | 83h             | STATUS              | 103h            | STATUS                  | 183h            |

| FSR                  | 04h             | FSR                  | 84h             | FSR                 | 104h            | FSR                     | 184h            |

| PORTA                | 05h             | TRISA                | 85h             |                     | 105h            |                         | 185h            |

| PORTB                | 06h             | TRISB                | 86h             | PORTB               | 106h            | TRISB                   | 186h            |

| PORTC                | 07h             | TRISC                | 87h             |                     | 107h            |                         | 187h            |

| PORTD <sup>(2)</sup> | 08h             | TRISD <sup>(2)</sup> | 88h             |                     | 108h            |                         | 188h            |

| PORTE <sup>(2)</sup> | 09h             | TRISE <sup>(2)</sup> | 89h             |                     | 109h            |                         | 189h            |

| PCLATH               | 0Ah             | PCLATH               | 8Ah             | PCLATH              | 10Ah            | PCLATH                  | 18Ah            |

| INTCON               | 0Bh             | INTCON               | 8Bh             | INTCON              | 10Bh            | INTCON                  | 18Bh            |

| PIR1                 | 0Ch             | PIE1                 | 8Ch             | EEDATA              | 10Ch            | EECON1                  | 18Ch            |

| PIR2                 | 0Dh             | PIE2                 | 8Dh             | EEADR               | 10Dh            | EECON2                  | 18Dh            |

| TMR1L                | 0Eh             | PCON                 | 8Eh             | EEDATH              | 10Eh            | Reserved <sup>(1)</sup> | 18Eh            |

| TMR1H                | 0Fh             |                      | 8Fh             | EEADRH              | 10Fh            | Reserved <sup>(1)</sup> | 18Fh            |

| T1CON                | 10h             |                      | 90h             |                     | 110h            |                         | 190h            |

| TMR2                 | 11h             |                      | 91h             |                     |                 |                         |                 |

| T2CON                | 12h             | PR2                  | 92h             |                     |                 |                         |                 |

|                      | 13h             |                      | 93h             |                     |                 |                         |                 |

|                      | 14h             |                      | 94h             |                     |                 |                         |                 |

| CCPR1L               | 15h             |                      | 95h             |                     |                 |                         |                 |

| CCPR1H               | 16h             |                      | 96h             |                     |                 |                         |                 |

| CCP1CON              | 17h             |                      | 97h             |                     |                 |                         |                 |

| RCSTA                | 18h             | TXSTA                | 98h             |                     |                 |                         |                 |

| TXREG                | 19h             | SPBRG                | 99h             |                     |                 |                         |                 |

| RCREG                | 1Ah             |                      | 9Ah             |                     |                 |                         |                 |

|                      | 1Bh             |                      | 9Bh             |                     |                 |                         |                 |

|                      | 1Ch             |                      | 9Ch             |                     |                 |                         |                 |

|                      | 1Dh             |                      | 9Dh             |                     |                 |                         |                 |

| ADRESH               | 1Eh             | ADRESL               | 9Eh             |                     |                 |                         |                 |

| ADCON0               | 1Fh             | ADCON1               | 9Fh             |                     | 120h            |                         | 1A0h            |

|                      | 20h             | General              | A0h             |                     | 12011           |                         | IAUII           |

|                      |                 | Purpose              |                 | accesses            |                 | accesses                |                 |

|                      |                 | Register             |                 | 20h-7Fh             |                 | A0h - BFh               |                 |

| General<br>Purpose   |                 | 32 Bytes             | BFh             |                     |                 |                         | 1BFh            |

| Register             |                 |                      | C0h             |                     |                 |                         | 1C0h            |

| 96 Bytes             |                 |                      |                 |                     | 16Fh            |                         | 1 E E b         |

|                      |                 |                      | EFh<br>F0h      |                     | 170h            |                         | 1EFh<br>1F0h    |

|                      |                 | accesses             | 1 011           | accesses<br>70h-7Fh |                 | accesses                | IFUII           |

|                      | 7Fh             | 70h-7Fh              | FFh             |                     | 17Fh            | 70h-7Fh                 | 1FFh            |

| Bank 0               |                 | Bank 1               |                 | Bank 2              |                 | Bank 3                  |                 |

|                      |                 |                      |                 |                     |                 |                         |                 |

Unimplemented data memory locations, read as '0'.

<sup>\*</sup> Not a physical register.

Note 1: These registers are reserved; maintain these registers clear.

<sup>2:</sup> These registers are not implemented on the PIC16F870.

### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bit for the EEPROM write operation interrupt.

### REGISTER 2-6: PIE2 REGISTER (ADDRESS: 8Dh)

| U-0   | U-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-------|-----|-----|-----|-------|

| _     | _   | _   | EEIE  | _   | _   |     | _     |

| bit 7 |     | •   |       | •   |     | •   | bit 0 |

bit 7-5 Unimplemented: Read as '0'

bit 4 **EEIE**: EEPROM Write Operation Interrupt Enable bit

1 = Enable EE write interrupt0 = Disable EE write interrupt

bit 3-0 Unimplemented: Read as '0'

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) Since the microcontroller does not execute instructions during the write cycle, the firmware does not necessarily have to check either EEIF, or WR, to determine if the write had finished.

#### **EXAMPLE 3-4:** FLASH PROGRAM WRITE

| BSF   | ,        |       | •                        |

|-------|----------|-------|--------------------------|

| BCF   | -        |       | ;Bank 2                  |

| MOVF  | ADDRL, V | N .   | ;Write address           |

| MOVWF | EEADR    |       | ;of desired              |

| MOVF  | ADDRH, V | V     | ;program memory          |

| MOVWF | EEADRH   |       | ;location                |

| MOVF  | VALUEL,  | W     | ;Write value to          |

| MOVWF | EEDATA   |       | ;program at              |

| MOVF  | VALUEH,  | W     | ;desired memory          |

| MOVWF | EEDATH   |       | ;location                |

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BSF   | EECON1,  | EEPGD | ;Point to Program memory |

| BSF   | EECON1,  | WREN  | ;Enable writes           |

|       |          |       | ;Only disable interrupts |

| BCF   | INTCON,  | GIE   | ;if already enabled,     |

|       |          |       | ;otherwise discard       |

| MOVLW | 0x55     |       | ;Write 55h to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| MOVLW | 0xAA     |       | ;Write AAh to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| BSF   | EECON1,  | WR    | ;Start write operation   |

| NOP   |          |       | ;Two NOPs to allow micro |

| NOP   |          |       | ;to setup for write      |

|       |          |       | ;Only enable interrupts  |

| BSF   | INTCON,  | GIE   | ;if using interrupts,    |

|       |          |       | ;otherwise discard       |

| BCF   | EECON1,  | WREN  | ;Disable writes          |

### 3.7 Write Verify

The PIC16F870/871 devices do not automatically verify the value written during a write operation. Depending on the application, good programming practice may dictate that the value written to memory be verified against the original value. This should be used in applications where excessive writes can stress bits near the specified endurance limits.

## 3.8 Protection Against Spurious Writes

There are conditions when the device may not want to write to the EEPROM data memory or FLASH program memory. To protect against these spurious write conditions, various mechanisms have been built into the PIC16F870/871 devices. On power-up, the WREN bit is cleared and the Power-up Timer (if enabled) prevents writes.

The write initiate sequence and the WREN bit together, help prevent any accidental writes during brown-out, power glitches, or firmware malfunction.

### 3.9 Operation While Code Protected

The PIC16F870/871 devices have two code protect mechanisms, one bit for EEPROM data memory and two bits for FLASH program memory. Data can be read and written to the EEPROM data memory, regardless of the state of the code protection bit, CPD. When code protection is enabled and CPD cleared, external access via ICSP is disabled, regardless of the state of the program memory code protect bits. This prevents the contents of EEPROM data memory from being read out of the device.

The state of the program memory code protect bits, CP0 and CP1, do not affect the execution of instructions out of program memory. The PIC16F870/871 devices can always read the values in program memory, regardless of the state of the code protect bits. However, the state of the code protect bits and the WRT bit will have different effects on writing to program memory. Table 4-1 shows the effect of the code protect bits and the WRT bit on program memory.

Once code protection has been enabled for either EEPROM data memory or FLASH program memory, only a full erase of the entire device will disable code protection.

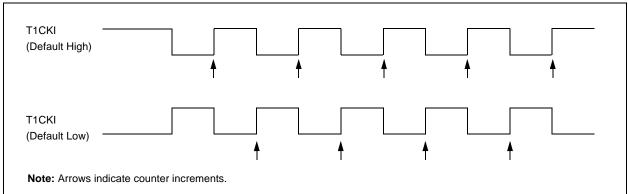

## 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 5.3 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF1, MOVWF1, BSF1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0, will clear the prescaler count, but will not change the prescaler assignment.

### REGISTER 5-1: OPTION\_REG REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

bit 7 RBPU

bit 6 INTEDG

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (CLKO)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on TOCKI pin 0 = Increment on low-to-high transition on TOCKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 PS2:PS0: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1:128    |

To avoid an unintended device RESET, the instruction sequence shown in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

Note:

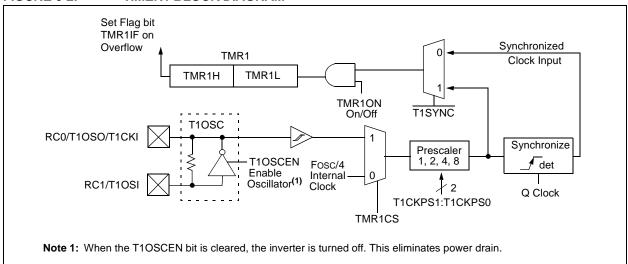

### 6.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is Fosc/4. The synchronize control bit, T1SYNC (T1CON<2>), has no effect, since the internal clock is always in sync.

### 6.2 Timer1 Counter Operation

Timer1 may operate in either a Synchronous, or an Asynchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

## 6.3 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

If T1SYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

TABLE 9-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | F        | osc = 20 M              | Hz  | F        | osc = 16 M | Hz                          | Fosc = 10 MHz |            |                             |  |

|-------------|----------|-------------------------|-----|----------|------------|-----------------------------|---------------|------------|-----------------------------|--|

| RATE<br>(K) | KBAUD    | % SPBRG value (decimal) |     | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | -        | -                       | -   | -        | -          | -                           | -             | -          | -                           |  |

| 1.2         | -        | -                       | -   | -        | -          | -                           | -             | -          | -                           |  |

| 2.4         | -        | -                       | -   | -        | -          | -                           | 2.441         | 1.71       | 255                         |  |

| 9.6         | 9.615    | 0.16                    | 129 | 9.615    | 0.16       | 103                         | 9.615         | 0.16       | 64                          |  |

| 19.2        | 19.231   | 0.16                    | 64  | 19.231   | 0.16       | 51                          | 19.531        | 1.72       | 31                          |  |

| 28.8        | 29.070   | 0.94                    | 42  | 29.412   | 2.13       | 33                          | 28.409        | 1.36       | 21                          |  |

| 33.6        | 33.784   | 0.55                    | 36  | 33.333   | 0.79       | 29                          | 32.895        | 2.10       | 18                          |  |

| 57.6        | 59.524   | 3.34                    | 20  | 58.824   | 2.13       | 16                          | 56.818        | 1.36       | 10                          |  |

| HIGH        | 4.883    | -                       | 255 | 3.906    | -          | 255                         | 2.441         | -          | 255                         |  |

| LOW         | 1250.000 | -                       | 0   | 1000.000 |            | 0                           | 625.000       | -          | 0                           |  |

| BAUD        | F       | osc = 4 MH | Ηz                          | Fosc = 3.6864 MHz |            |                             |  |

|-------------|---------|------------|-----------------------------|-------------------|------------|-----------------------------|--|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | -       | -          | -                           | -                 | -          | -                           |  |

| 1.2         | 1.202   | 0.17       | 207                         | 1.2               | 0          | 191                         |  |

| 2.4         | 2.404   | 0.17       | 103                         | 2.4               | 0          | 95                          |  |

| 9.6         | 9.615   | 0.16       | 25                          | 9.6               | 0          | 23                          |  |

| 19.2        | 19.231  | 0.16       | 12                          | 19.2              | 0          | 11                          |  |

| 28.8        | 27.798  | 3.55       | 8                           | 28.8              | 0          | 7                           |  |

| 33.6        | 35.714  | 6.29       | 6                           | 32.9              | 2.04       | 6                           |  |

| 57.6        | 62.500  | 8.51       | 3                           | 57.6              | 0          | 3                           |  |

| HIGH        | 0.977   | -          | 255                         | 0.9               | -          | 255                         |  |

| LOW         | 250.000 | -          | 0                           | 230.4             | -          | 0                           |  |

## PIC16F870/871

## REGISTER 11-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

| CP1                 | CP0 | DEBUG                                                                                                                  | _                                                                                                                                                           | WRT      | CPD            | LVP                  | BOREN                                   | CP1      | CP0        | PWRTEN                  | WDTEN FO       | OSC1  | FOSC0 |

|---------------------|-----|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------|----------------------|-----------------------------------------|----------|------------|-------------------------|----------------|-------|-------|

| bit 13              | I   |                                                                                                                        |                                                                                                                                                             |          |                |                      | ·                                       |          |            |                         | l l            |       | bit 0 |

| bit 13-1<br>bit 5-4 | 12, | 11 = Cod<br>10 = Not<br>01 = Not                                                                                       | CP1:CP0: FLASH Program Memory Code Protection bits <sup>(2)</sup> 11 = Code protection off  10 = Not supported  11 = Not supported  10 = Code protection on |          |                |                      |                                         |          |            |                         |                |       |       |

| bit 11              |     |                                                                                                                        | cuit Del                                                                                                                                                    | ougger ( | disable        | d, RB6               |                                         |          |            | rpose I/O p             |                |       |       |

| bit 10              |     | Unimpler                                                                                                               | nented                                                                                                                                                      | : Read   | as '1'         |                      |                                         |          |            |                         |                |       |       |

| bit 9               |     | -                                                                                                                      | otected                                                                                                                                                     | progran  | n mem          | ory ma               | y be writte                             | -        |            | N control<br>CON contro | ol             |       |       |

| bit 8               |     | <b>CPD:</b> Date 1 = Code 0 = Data 1                                                                                   | protect                                                                                                                                                     | ion off  |                |                      |                                         |          |            |                         |                |       |       |

| bit 7               |     | 1 = RB3/F                                                                                                              | PGM pii                                                                                                                                                     | n has P  | GM f <u>ur</u> | ction,               | ogramming<br>low voltago<br>oust be use | e progra | amming     |                         |                |       |       |

| bit 6               |     | <b>BOREN</b> : 1 = BOR 0 = BOR                                                                                         | enabled                                                                                                                                                     | t        | et Ena         | ble bit <sup>(</sup> | 3)                                      |          |            |                         |                |       |       |

| bit 3               |     | 1 = PWR 0 = PWR                                                                                                        | T disabl                                                                                                                                                    | ed .     | ner Ena        | able bit             | (3)                                     |          |            |                         |                |       |       |

| bit 2               |     | 1 = WDT                                                                                                                | WDTEN: Watchdog Timer Enable bit  1 = WDT enabled  0 = WDT disabled                                                                                         |          |                |                      |                                         |          |            |                         |                |       |       |

| bit 1-0             |     | FOSC1:FOSC0: Oscillator Selection bits  11 = RC oscillator  10 = HS oscillator  01 = XT oscillator  00 = LP oscillator |                                                                                                                                                             |          |                |                      |                                         |          |            |                         |                |       |       |

|                     |     | Legend:                                                                                                                |                                                                                                                                                             |          |                |                      |                                         |          |            |                         |                |       |       |

|                     |     | R = Read                                                                                                               | lable bit                                                                                                                                                   |          | ١              | V = Wı               | ritable bit                             | U        | = Unim     | plemented               | bit, read as ' | '0'   |       |

|                     |     | - n = Valu                                                                                                             | e at PC                                                                                                                                                     | R        | •              | 1' = Bit             | t is set                                | '0       | ' = Bit is | s cleared               | x = Bit is     | unkno | wn    |

Note 1: The erased (unprogrammed) value of the configuration word is 3FFFh.

2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

3: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTEN. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECFSZ f,d                                                                                                                                                                                                                                                                                |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                  |

| Operation:       | (f) - 1 → (destination); skip if result = 0                                                                                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead making it a 2 TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                     |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] INCFSZ f,d                                                                                                                                       |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                         |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                 |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |  |  |

|                  | If the result is 1, the next instruction is executed. If the result is 0, a NOP is executed instead, making it a 2 Tcy instruction.                        |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] GOTO k                                                                                                                                                                  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                   |

| Status Affected: | None                                                                                                                                                                              |

| Description:     | GOTO is an unconditional branch. The eleven-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two-cycle instruction. |

| IORLW            | Inclusive OR Literal with W                                                                                      |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] IORLW k                                                                                                |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                              |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow (W)$                                                                                     |  |  |  |  |

| Status Affected: | Z                                                                                                                |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the eight bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| Syntax:          | [ label ] INCF f,d                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                        |

| Status Affected: | Z                                                                                                                                                          |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

Increment f

**INCF**

| IORWF            | Inclusive OR W with f                                                                                                                                     |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                       |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                        |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'. |  |  |  |  |  |

## 13.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 13.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 13.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

## 13.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

#### 13.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

#### 13.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

## 13.20 PICDEM 18R PIC18C601/801 Demonstration Board

The PICDEM 18R demonstration board serves to assist development of the PIC18C601/801 family of Microchip microcontrollers. It provides hardware implementation of both 8-bit Multiplexed/De-multiplexed and 16-bit Memory modes. The board includes 2 Mb external FLASH memory and 128 Kb SRAM memory, as well as serial EEPROM, allowing access to the wide range of memory types supported by the PIC18C601/801.

## 13.21 PICDEM LIN PIC16C43X Demonstration Board

The powerful LIN hardware and software kit includes a series of boards and three PIC microcontrollers. The small footprint PIC16C432 and PIC16C433 are used as slaves in the LIN communication and feature onboard LIN transceivers. A PIC16F874 FLASH microcontroller serves as the master. All three microcontrollers are programmed with firmware to provide LIN bus communication.

#### 13.22 PICkit<sup>™</sup> 1 FLASH Starter Kit

A complete "development system in a box", the PICkit FLASH Starter Kit includes a convenient multi-section board for programming, evaluation, and development of 8/14-pin FLASH PIC® microcontrollers. Powered via USB, the board operates under a simple Windows GUI. The PICkit 1 Starter Kit includes the user's guide (on CD ROM), PICkit 1 tutorial software and code for various applications. Also included are MPLAB® IDE (Integrated Development Environment) software, software and hardware "Tips 'n Tricks for 8-pin FLASH PIC® Microcontrollers" Handbook and a USB Interface Cable. Supports all current 8/14-pin FLASH PIC microcontrollers, as well as many future planned devices.

## 13.23 PICDEM USB PIC16C7X5 Demonstration Board

The PICDEM USB Demonstration Board shows off the capabilities of the PIC16C745 and PIC16C765 USB microcontrollers. This board provides the basis for future USB products.

### 13.24 Evaluation and Programming Tools

In addition to the PICDEM series of circuits, Microchip has a line of evaluation kits and demonstration software for these products.

- KEELOQ evaluation and programming tools for Microchip's HCS Secure Data Products

- CAN developers kit for automotive network applications

- · Analog design boards and filter design software

- PowerSmart battery charging evaluation/ calibration kits

- IrDA<sup>®</sup> development kit

- microID development and rfLab<sup>™</sup> development software

- SEEVAL<sup>®</sup> designer kit for memory evaluation and endurance calculations

- PICDEM MSC demo boards for Switching mode power supply, high power IR driver, delta sigma ADC, and flow rate sensor

Check the Microchip web page and the latest Product Line Card for the complete list of demonstration and evaluation kits.

### 14.2 DC Characteristics: PIC16F870/871 (Industrial)

| DC CHA       | RACTI | ERISTICS                           | Operating ter      | mperat | ure -40°C | $S \leq TA \leq$ | nless otherwise stated)  = +85°C for Industrial                                          |

|--------------|-------|------------------------------------|--------------------|--------|-----------|------------------|------------------------------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                     | Min                | Тур†   | Max       | Units            | Conditions                                                                               |

|              | VIL   | Input Low Voltage                  |                    |        |           |                  |                                                                                          |

|              |       | I/O ports:                         |                    |        |           |                  |                                                                                          |

| D030         |       | with TTL buffer                    | Vss                | _      | 0.15 VDD  | V                | For entire VDD range                                                                     |

| D030A        |       |                                    | Vss                | _      | 0.8V      | V                | $4.5V \le VDD \le 5.5V$                                                                  |

| D031         |       | with Schmitt Trigger buffer        | Vss                | _      | 0.2 VDD   | V                |                                                                                          |

| D032         |       | MCLR, OSC1 (in RC mode)            | Vss                | _      | 0.2 VDD   | V                |                                                                                          |

| D033         |       | OSC1 (in XT, HS and LP)            | Vss                | _      | 0.3 VDD   | V                | (Note 1)                                                                                 |

|              |       | Ports RC3 and RC4:                 |                    |        |           |                  |                                                                                          |

| D034         |       | with Schmitt Trigger buffer        | Vss                | _      | 0.3 VDD   | V                | For entire VDD range                                                                     |

| D034A        |       | with SMBus                         | -0.5               | _      | 0.6       | V                | For $VDD = 4.5 \text{ to } 5.5V$                                                         |

|              | VIH   | Input High Voltage                 |                    |        |           |                  |                                                                                          |

|              |       | I/O ports:                         |                    | _      |           |                  |                                                                                          |

| D040         |       | with TTL buffer                    | 2.0                | _      | Vdd       | V                | $4.5V \le VDD \le 5.5V$                                                                  |

| D040A        |       |                                    | 0.25 VDD +<br>0.8V | _      | VDD       | V                | For entire VDD range                                                                     |

| D041         |       | with Schmitt Trigger buffer        | 0.8 VDD            | _      | Vdd       | V                | For entire VDD range                                                                     |

| D042         |       | MCLR                               | 0.8 VDD            | _      | Vdd       | V                |                                                                                          |

| D042A        |       | OSC1 (XT, HS and LP)               | 0.7 VDD            | _      | Vdd       | V                | (Note 1)                                                                                 |

| D043         |       | OSC1 (in RC mode)                  | 0.9 VDD            | _      | Vdd       | V                |                                                                                          |

|              |       | Ports RC3 and RC4:                 |                    |        |           |                  |                                                                                          |

| D044         |       | with Schmitt Trigger buffer        | 0.7 VDD            | _      | Vdd       | V                | For entire VDD range                                                                     |

| D044A        |       | with SMBus                         | 1.4                | _      | 5.5       | V                | for VDD = 4.5 to 5.5V                                                                    |

| D070         | IPURB | PORTB Weak Pull-up<br>Current      | 50                 | 250    | 400       | μА               | VDD = 5V, VPIN = VSS                                                                     |

|              | lı∟   | Input Leakage Current (Notes 2, 3) |                    |        |           |                  |                                                                                          |

| D060         |       | I/O ports                          | _                  | _      | ±1        | μΑ               | Vss ≤ VPIN ≤ VDD,<br>Pin at hi-impedance                                                 |

| D061         |       | MCLR, RA4/T0CKI                    | _                  | _      | ±5        | μΑ               | $Vss \le VPIN \le VDD$                                                                   |

| D063         |       | OSC1                               | _                  | _      | ±5        | μΑ               | $\label{eq:VSS}  \mbox{VPIN} \leq \mbox{VDD, XT, HS and} \\ \mbox{LP osc configuration}$ |

These parameters are characterized but not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F870/871 be driven with external clock in RC mode.

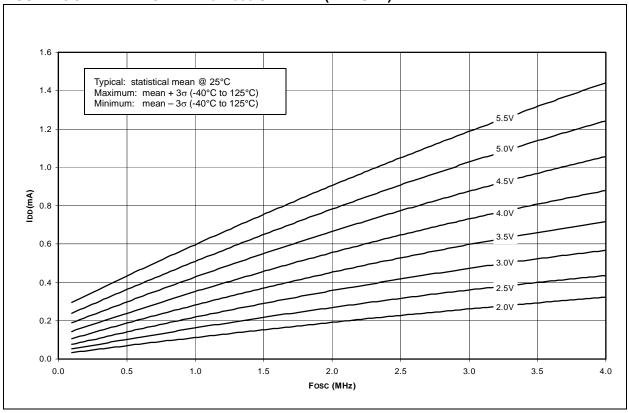

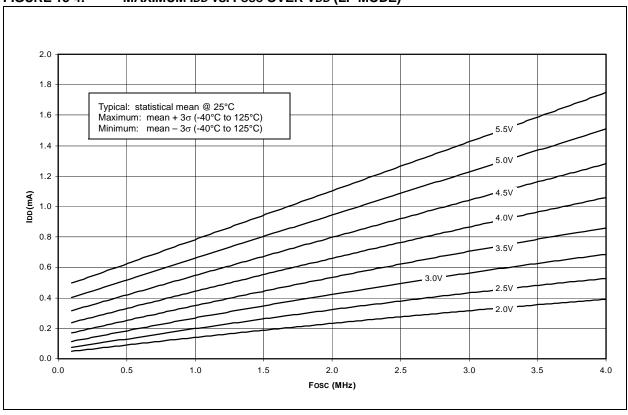

FIGURE 15-3: TYPICAL IDD vs. FOSC OVER VDD (XT MODE)

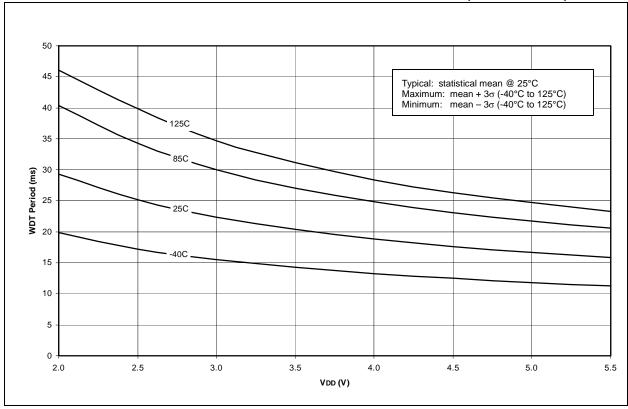

FIGURE 15-16: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO 125°C)

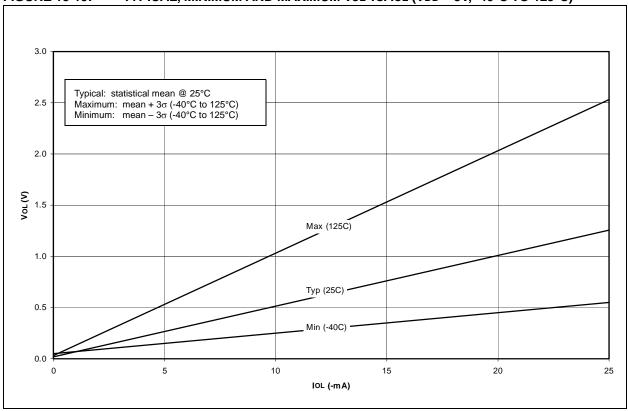

FIGURE 15-19: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 3V, -40°C TO 125°C)

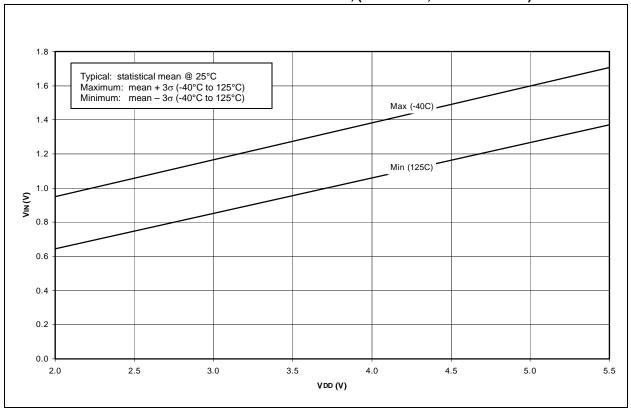

FIGURE 15-20: MINIMUM AND MAXIMUM VIN vs. VDD, (TTL INPUT, -40°C TO 125°C)

# PIC16F870/871

NOTES:

APPENDIX E: MIGRATION FROM HIGH-END TO ENHANCED DEVICES

A detailed discussion of the migration pathway and differences between the high-end MCU devices (i.e., PIC17CXXX) and the enhanced devices (i.e., PIC18FXXXX) is provided in AN726, "PIC17CXXX to PIC18CXXX Migration." This Application Note is available as Literature Number DS00726.

## **INDEX**

| A                                                       | Timer1                    |

|---------------------------------------------------------|---------------------------|

| A/D79                                                   | Timer2                    |

| Acquisition Requirements82                              | USART A                   |

| ADCON0 Register79                                       | USART A                   |

| ADCON1 Register79                                       | USART T                   |

| ADIF Bit80                                              | Watchdoo                  |

| ADRESH Register79                                       | BOR. See Brog<br>BRGH Bit |

| ADRESL Register79                                       |                           |

| Analog Port Pins41, 42                                  | Brown-out Res             |

| Associated Registers and Bits85                         | BOR Stat                  |

| Calculating Acquisition Time82                          | С                         |

| Configuring Analog Port Pins83                          | C Compilers               |

| Configuring the Interrupt81                             | MPLAB C                   |

| Configuring the Module81                                | MPLAB C                   |

| Conversion Clock83                                      | MPLAB C                   |

| Conversions 84                                          | Capture/Comp              |

| Delays 82                                               | Associate                 |

| Effects of a RESET85                                    | Capi                      |

| GO/DONE Bit80                                           | PWN                       |

| Internal Sampling Switch (Rss) Impedance82              | Capture N                 |

| Operation During SLEEP85                                | CCF                       |

| Result Registers84                                      | Pres                      |

| Source Impedance                                        | CCP Time                  |

| Time Delays                                             | Compare                   |

| Absolute Maximum Ratings                                | Spec                      |

| ADCONO Register                                         | Compare                   |

| ADDON1 Register                                         | Softv                     |

| ADRESH Registers                                        | Spec                      |

| ADRESL Register                                         | PWM Mo                    |

| Analog-to-Digital Converter. See A/D. Application Notes | Duty                      |

| AN552 (Implementing Wake-up on Key Stroke) 35           | Exar                      |

| AN556 (Implementing wake-up on Key Stroke)24            | PWN                       |

| Assembler                                               | Setu                      |

| MPASM Assembler111                                      | Special E                 |

| Asynchronous Reception                                  | CCP. See Cap              |

| Associated Registers69                                  | CCP1CON Re                |

| Asynchronous Reception (9-bit Mode)                     | CCP1M0 Bit                |

| Associated Registers71                                  | CCP1M1 Bit                |

| _                                                       | CCP1M2 Bit                |

| В                                                       | CCP1M3 Bit                |

| Banking, Data Memory11                                  | CCP1X Bit                 |

| Baud Rate Generator (BRG)                               | CCP1Y Bit                 |

| Associated Registers63                                  | CCPR1H Regi               |

| Block Diagrams                                          | Code Example              |

| A/D81                                                   | Changing                  |

| Analog Input Model 82                                   | EEPROM                    |

| Capture Mode Operation56                                | EEPROM                    |

| Compare Mode Operation57                                | FLASH P                   |

| Interrupt Logic                                         | FLASH P                   |

| On-Chip RESET Circuit91                                 | Indirect A                |

| PIC16F870                                               | Initializing              |

| PIC16F871                                               | Saving S                  |

| PORTC (Peripheral Output Override)                      | in R                      |

| PORTD (In I/O Port Mode)                                | Code Protecte             |

| PORTD and PORTE (Parallel Slave Port)                   | Data EEF                  |

| PORTE (In I/O Port Mode)39                              | Code Protection           |

| PWM Mode58  RA3:RA0 and RA5 Pins33                      | Computed GO               |

| RA3:RA0 and RA5 PINS                                    | Configuration I           |

| RB3:RB0 Pins                                            | Configuration \           |

| RB7:RB4 Pins                                            | Conversion Co             |

| Timer0/WDT Prescaler                                    |                           |

|                                                         |                           |

| Timer2                                                                                                               | 50                                                 |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1 1111012                                                                                                            | 53                                                 |

| USART Asynchronous Receive                                                                                           | 68                                                 |

| USART Asynchronous Receive (9-bit Mode)                                                                              | 70                                                 |

| USART Transmit                                                                                                       |                                                    |

| Watchdog Timer                                                                                                       |                                                    |

| · · · · · · · · · · · · · · · · · · ·                                                                                | 99                                                 |

| BOR. See Brown-out Reset.                                                                                            |                                                    |

| BRGH Bit                                                                                                             |                                                    |

| Brown-out Reset (BOR) 87, 91, 92                                                                                     | 2, 93                                              |

| BOR Status (BOR Bit)                                                                                                 | 23                                                 |

| ( , ,                                                                                                                |                                                    |

|                                                                                                                      |                                                    |

| Compilere                                                                                                            |                                                    |

| Compilers                                                                                                            |                                                    |

| MPLAB C17                                                                                                            |                                                    |

| MPLAB C18                                                                                                            | 112                                                |

| MPLAB C30                                                                                                            | 112                                                |

| Capture/Compare/PWM (CCP)                                                                                            | 55                                                 |

| Associated Registers                                                                                                 |                                                    |

|                                                                                                                      | <b>E</b> 0                                         |

| Capture, Compare and Timer1                                                                                          |                                                    |

| PWM and Timer2                                                                                                       |                                                    |

| Capture Mode                                                                                                         | 56                                                 |