Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf871-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## 3.5 Reading the FLASH Program Memory

Reading FLASH program memory is much like that of EEPROM data memory, only two NOP instructions must be inserted after the RD bit is set. These two instruction cycles that the NOP instructions execute, will be used by the microcontroller to read the data out of program memory and insert the value into the EEDATH:EEDATA registers. Data will be available following the second NOP instruction. EEDATH and EEDATA will hold their value until another read operation is initiated, or until they are written by firmware.

The steps to reading the FLASH program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F870/871 devices.

- 2. Set the EEPGD bit to point to FLASH program memory.

- 3. Set the RD bit to start the read operation.

- 4. Execute two NOP instructions to allow the microcontroller to read out of program memory.

- 5. Read the data from the EEDATH:EEDATA registers.

| BSF   | STATUS, RP1   | ;                        |

|-------|---------------|--------------------------|

| BCF   | STATUS, RPO   | ;Bank 2                  |

| MOVF  | ADDRL, W      | ;Write the               |

| MOVWF | EEADR         | ;address bytes           |

| MOVF  | ADDRH,W       | ;for the desired         |

| MOVWF | EEADRH        | ;address to read         |

| BSF   | STATUS, RPO   | ;Bank 3                  |

| BSF   | EECON1, EEPGD | ;Point to Program memory |

| BSF   | EECON1, RD    | ;Start read operation    |

| NOP   |               | ;Required two NOPs       |

| NOP   |               | ;                        |

| BCF   | STATUS, RPO   | ;Bank 2                  |

| MOVF  | EEDATA, W     | ;DATAL = EEDATA          |

| MOVWF | DATAL         | ;                        |

| MOVF  | EEDATH,W      | ;DATAH = EEDATH          |

| MOVWF | DATAH         | ;                        |

|       |               |                          |

EXAMPLE 3-3: FLASH PROGRAM READ

# 3.6 Writing to the FLASH Program Memory

Writing to FLASH program memory is unique, in that the microcontroller does not execute instructions while programming is taking place. The oscillator continues to run and all peripherals continue to operate and queue interrupts, if enabled. Once the write operation completes (specification D133), the processor begins executing code from where it left off. The other important difference when writing to FLASH program memory is that the WRT configuration bit, when clear, prevents any writes to program memory (see Table 3-1).

Just like EEPROM data memory, there are many steps in writing to the FLASH program memory. Both address and data values must be written to the SFRs. The EEPGD bit must be set, and the WREN bit must be set to enable writes. The WREN bit should be kept clear at all times, except when writing to the FLASH program memory. The WR bit can only be set if the WREN bit was set in a previous operation (i.e., they both cannot be set in the same operation). The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to program memory must also be prefaced with a special sequence of instructions that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruption for each byte written. These instructions must then be followed by two NOP instructions to allow the microcontroller to setup for the write operation. Once the write is complete, the execution of instructions starts with the instruction after the second NOP.

The steps to write to program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F870/871 devices.

- 2. Write the 14-bit data value to be programmed in the EEDATH:EEDATA registers.

- 3. Set the EEPGD bit to point to FLASH program memory.

- 4. Set the WREN bit to enable program operations.

- 5. Disable interrupts (if enabled).

- 6. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 7. Execute two NOP instructions to allow the microcontroller to setup for write operation.

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

| IABLE 4 0. |      |                       |                                                                                                                                                   |  |  |  |  |  |  |  |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Name       | Bit# | Buffer                | Function                                                                                                                                          |  |  |  |  |  |  |  |

| RB0/INT    | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |  |  |  |  |  |  |  |

| RB1        | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |  |  |  |  |  |  |  |

| RB2        | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |  |  |  |  |  |  |  |

| RB3/PGM    | bit3 | TTL/ST <sup>(1)</sup> | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |  |  |  |  |  |  |  |

| RB4        | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |  |  |  |  |  |  |  |

| RB5        | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |  |  |  |  |  |  |  |

| RB6/PGC    | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |  |  |  |  |  |  |  |

| RB7/PGD    | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |  |  |  |  |  |  |  |

### TABLE 4-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt or LVP mode.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

### TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7   | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|-----------|------------|---------|-------------------------------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7     | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | XXXX XXXX             | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB [ | PORTB Data Direction Register |       |       |       |       |       |       |                       | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU    | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

# 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

# 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Typ                                                                                                                                                                                                                                                                                                     | е        | Freq.                          | C1    | C2    |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------|-------|-------|--|--|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                          |          | 32 kHz                         | 33 pF | 33 pF |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                             |          | 100 kHz                        | 15 pF | 15 pF |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                             |          | 200 kHz                        | 15 pF | 15 pF |  |  |  |  |  |  |

| These values are for design guidance only.                                                                                                                                                                                                                                                                  |          |                                |       |       |  |  |  |  |  |  |

| Crystals Tested:                                                                                                                                                                                                                                                                                            |          |                                |       |       |  |  |  |  |  |  |

| 32.768 kl                                                                                                                                                                                                                                                                                                   | ± 20 PPM |                                |       |       |  |  |  |  |  |  |

| 100 kH:                                                                                                                                                                                                                                                                                                     | Z        | Epson C-2 100.00 KC-P ± 20 PPN |       |       |  |  |  |  |  |  |

| 200 kH:                                                                                                                                                                                                                                                                                                     | Z        | STD XTL 200.000 kHz ± 20 P     |       |       |  |  |  |  |  |  |

| <ul> <li>Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |          |                                |       |       |  |  |  |  |  |  |

# 6.6 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP | י1  |

|-------|-----------------------------------------|-----|

|       | module will not set interrupt flag b    | oit |

|       | TMR1IF (PIR1<0>).                       |     |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPRH:CCPRL register pair effectively becomes the period register for Timer1.

# 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device RESET (POR, MCLR Reset, WDT Reset, or BOR)

TMR2 is not cleared when T2CON is written.

# 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate shift clock.

| TABLE 7-1: | <b>REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER</b> |

|------------|------------------------------------------------------------|

|            |                                                            |

| Address               | Name   | Bit 7                | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | Valu<br>all c<br>RES | other |

|-----------------------|--------|----------------------|-------------|---------|---------|---------|--------|---------|---------|---------------|------|----------------------|-------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE        | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000          | 000x | 0000                 | 000u  |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF        | RCIF    | TXIF    | _       | CCP1IF | TMR2IF  | TMR1IF  | 0000          | -000 | 0000                 | -000  |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE        | RCIE    | TXIE    | -       | CCP1IE | TMR2IE  | TMR1IE  | 0000          | -000 | 0000                 | -000  |

| 11h                   | TMR2   | Timer2 M             | lodule's Re | gister  |         |         |        |         |         | 0000          | 0000 | 0000                 | 0000  |

| 12h                   | T2CON  |                      | TOUTPS3     | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000                 | 0000  |

| 92h                   | PR2    | Timer2 P             | eriod Regis | ter     |         |         |        |         |         | 1111          | 1111 | 1111                 | 1111  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

| BAUD        | F        | osc = 20 M | Hz                          | F        | osc = 16 M | Hz                          | Fosc = 10 MHz |            |                             |  |

|-------------|----------|------------|-----------------------------|----------|------------|-----------------------------|---------------|------------|-----------------------------|--|

| RATE<br>(K) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | -        | -          | -                           | -        | -          | -                           | -             | -          | -                           |  |

| 1.2         | -        | -          | -                           | -        | -          | -                           | -             | -          | -                           |  |

| 2.4         | -        | -          | -                           | -        | -          | -                           | 2.441         | 1.71       | 255                         |  |

| 9.6         | 9.615    | 0.16       | 129                         | 9.615    | 0.16       | 103                         | 9.615         | 0.16       | 64                          |  |

| 19.2        | 19.231   | 0.16       | 64                          | 19.231   | 0.16       | 51                          | 19.531        | 1.72       | 31                          |  |

| 28.8        | 29.070   | 0.94       | 42                          | 29.412   | 2.13       | 33                          | 28.409        | 1.36       | 21                          |  |

| 33.6        | 33.784   | 0.55       | 36                          | 33.333   | 0.79       | 29                          | 32.895        | 2.10       | 18                          |  |

| 57.6        | 59.524   | 3.34       | 20                          | 58.824   | 2.13       | 16                          | 56.818        | 1.36       | 10                          |  |

| HIGH        | 4.883    | -          | 255                         | 3.906    | -          | 255                         | 2.441         | -          | 255                         |  |

| LOW         | 1250.000 | -          | 0                           | 1000.000 |            | 0                           | 625.000       | -          | 0                           |  |

# TABLE 9-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | F       | osc = 4 MH | łz                          | Fosc = 3.6864 MHz |            |                             |  |  |  |

|-------------|---------|------------|-----------------------------|-------------------|------------|-----------------------------|--|--|--|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3         | -       | -          | -                           | -                 | -          | -                           |  |  |  |

| 1.2         | 1.202   | 0.17       | 207                         | 1.2               | 0          | 191                         |  |  |  |

| 2.4         | 2.404   | 0.17       | 103                         | 2.4               | 0          | 95                          |  |  |  |

| 9.6         | 9.615   | 0.16       | 25                          | 9.6               | 0          | 23                          |  |  |  |

| 19.2        | 19.231  | 0.16       | 12                          | 19.2              | 0          | 11                          |  |  |  |

| 28.8        | 27.798  | 3.55       | 8                           | 28.8              | 0          | 7                           |  |  |  |

| 33.6        | 35.714  | 6.29       | 6                           | 32.9              | 2.04       | 6                           |  |  |  |

| 57.6        | 62.500  | 8.51       | 3                           | 57.6              | 0          | 3                           |  |  |  |

| HIGH        | 0.977   | -          | 255                         | 0.9               | -          | 255                         |  |  |  |

| LOW         | 250.000 | -          | 0                           | 230.4             | -          | 0                           |  |  |  |

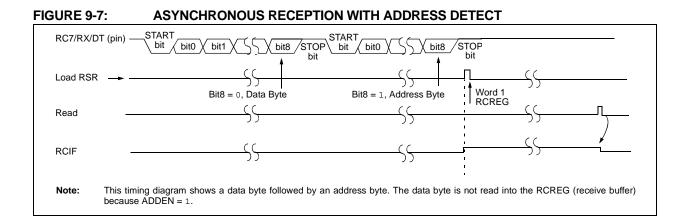

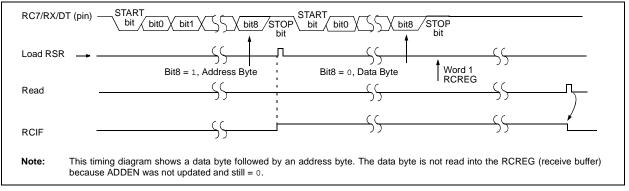

#### FIGURE 9-8: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

#### TABLE 9-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|-----------|-----------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TOIE      | INTE      | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF      | —     | CCP1IF | TMR2IF | TMR1IF | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN      | CREN      | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | x000 000x                       |

| 1Ah                    | RCREG  | USART Re             | ceive Re | gister    |           |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE      | —     | CCP1IE | TMR2IE | TMR1IE | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN      | SYNC      | —     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            |          | 0000 0000 | 0000 0000 |       |        |        |        |                       |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

| Address                | Name                                   | Bit 7                | Bit 6     | Bit 5   | Bit 4     | Bit 3   | Bit 2       | Bit 1       | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|------------------------|----------------------------------------|----------------------|-----------|---------|-----------|---------|-------------|-------------|-----------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                 | GIE                  | PEIE      | TOIE    | INTE      | RBIE    | TOIF        | INTF        | R0IF      | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF      | _       | CCP1IF      | TMR2IF      | TMR1IF    | 0000 -000             | 0000 -000                       |

| 18h                    | RCSTA                                  | SPEN                 | RX9       | SREN    | CREN      | _       | FERR        | OERR        | RX9D      | 0000 -00x             | 0000 -00x                       |

| 1Ah                    | RCREG                                  | USART R              | eceive Re | gister  |           |         |             |             |           | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE      | _       | CCP1IE      | TMR2IE      | TMR1IE    | 0000 -000             | 0000 -000                       |

| 98h                    | TXSTA                                  | CSRC                 | TX9       | TXEN    | SYNC      | _       | BRGH        | TRMT        | TX9D      | 0000 -010             | 0000 -010                       |

| 99h                    | 99h SPBRG Baud Rate Generator Register |                      |           |         |           |         |             |             |           | 0000 0000             | 0000 0000                       |

| Logond                 | unkno                                  |                      | malamant  | od rood | 20 '0' SH | adad ca | lle ara not | upped for a | nchronour | montor recent         | ion                             |

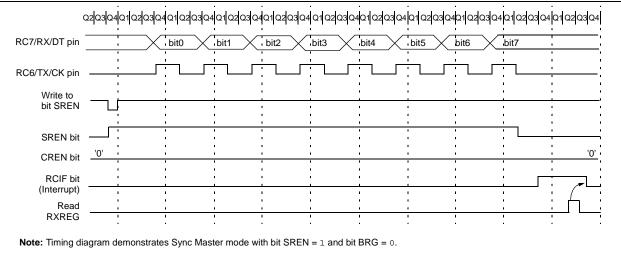

TABLE 9-9:

REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F870; always maintain these bits clear.

# 11.0 SPECIAL FEATURES OF THE CPU

The PIC16F870/871 devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide Power Saving Operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

- Low Voltage In-Circuit Serial Programming

- In-Circuit Debugger

PIC16F870/871 devices have a Watchdog Timer, which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

# 11.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. The erased, or unprogrammed value of the configuration word is 3FFFh. These bits are mapped in program memory location 2007h.

It is important to note that address 2007h is beyond the user program memory space, which can be accessed only during programming.

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | х   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 11-4: STATUS BITS AND THEIR SIGNIFICANCE

Legend: x = don't care, u = unchanged

#### TABLE 11-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### TABLE 11-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register | Devices   |           | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |

|----------|-----------|-----------|------------------------------------|--------------------------|---------------------------------|--|

| W        | PIC16F870 | PIC16F871 | XXXX XXXX                          | uuuu uuuu                | սսսս սսսս                       |  |

| INDF     | PIC16F870 | PIC16F871 | N/A                                | N/A                      | N/A                             |  |

| TMR0     | PIC16F870 | PIC16F871 | xxxx xxxx                          | uuuu uuuu                | սսսս սսսս                       |  |

| PCL      | PIC16F870 | PIC16F871 | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |  |

| STATUS   | PIC16F870 | PIC16F871 | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <sup>(3)</sup>        |  |

| FSR      | PIC16F870 | PIC16F871 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTA    | PIC16F870 | PIC16F871 | 0x 0000                            | 0u 0000                  | uu uuuu                         |  |

| PORTB    | PIC16F870 | PIC16F871 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTC    | PIC16F870 | PIC16F871 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTD    | PIC16F870 | PIC16F871 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTE    | PIC16F870 | PIC16F871 | xxx                                | uuu                      | uuu                             |  |

| PCLATH   | PIC16F870 | PIC16F871 | 0 0000                             | 0 0000                   | u uuuu                          |  |

| INTCON   | PIC16F870 | PIC16F871 | 0000 000x                          | 0000 000u                | սսսս սսսս <b>(1)</b>            |  |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- **2:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- **3:** See Table 11-5 for RESET value for specific condition.

# 12.0 INSTRUCTION SET SUMMARY

Each PIC16F870/871 instruction is a 14-bit word, divided into an OPCODE, which specifies the instruction type, and one or more operands, which further specify the operation of the instruction. The PIC16F870/871 instruction set summary in Table 12-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 12-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

# TABLE 12-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                  |

| PC    | Program Counter                                                                                                                                                                   |

| ТО    | Time-out bit                                                                                                                                                                      |

| PD    | Power-down bit                                                                                                                                                                    |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles, with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 12-2 lists the instructions recognized by the MPASM<sup>™</sup> assembler.

Figure 12-1 shows the general formats that the instructions can have.

| Note: | To maintain upward compatibility with |

|-------|---------------------------------------|

|       | future PIC16F870/871 products, do not |

|       | use the OPTION and TRIS instructions. |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 12-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file r                                                                  | egist                                                                        | er op  | eratio | ons         |   |  |  |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------|--------|-------------|---|--|--|

| 13                                                                                    | 8                                                                            | 7      | 6      |             | 0 |  |  |

| OPCODE                                                                                |                                                                              | d      |        | f (FILE #)  |   |  |  |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |                                                                              |        |        |             |   |  |  |

| Bit-oriented file reg                                                                 | jister                                                                       | · oper | ation  | S           |   |  |  |

| 13                                                                                    | 10                                                                           | 9      | 7      | 6           | 0 |  |  |

| OPCODE                                                                                |                                                                              | b (Bl  | T #)   | f (FILE #)  |   |  |  |

| Literal and control<br>General                                                        | f = 7-bit file register address<br>Literal and control operations<br>General |        |        |             |   |  |  |

| 13                                                                                    |                                                                              | 8      | 7      |             | 0 |  |  |

| OPCODE                                                                                |                                                                              |        |        | k (literal) |   |  |  |

| k = 8-bit immediate value                                                             |                                                                              |        |        |             |   |  |  |

| CALL and GOTO instructions only                                                       |                                                                              |        |        |             |   |  |  |

| -                                                                                     | 13 11 10 0                                                                   |        |        |             |   |  |  |

| OPCODE                                                                                |                                                                              |        | k (    | literal)    |   |  |  |

| k = 11-bit im                                                                         | med                                                                          | iate v | alue   |             |   |  |  |

A description of each instruction is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

# 13.9 MPLAB ICE 2000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

# 13.10 MPLAB ICE 4000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PIC microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory, and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

# 13.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low cost, run-time development tool, connecting to the host PC via an RS-232 or high speed USB interface. This tool is based on the FLASH PIC MCUs and can be used to develop for these and other PIC microcontrollers. The MPLAB ICD 2 utilizes the incircuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, singlestepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

# 13.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify, and program PIC devices without a PC connection. It can also set code protection in this mode.

# 13.13 PICSTART Plus Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus development programmer supports most PIC devices up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

# 14.1 DC Characteristics: PIC16F870/871 (Industrial, Extended) PIC16LF870/871 (Commercial, Industrial)

| PIC16LI<br>(Com                         | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature -40°C} \leq TA \leq +85°C \mbox{ for Industrial} \\ \mbox{0°C} \leq TA \leq +70°C \mbox{ for Commercial} \end{array}$ |                                                                  |              |                                                                                                                                                                                                                                                              |            |        |                                                                                       |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|---------------------------------------------------------------------------------------|--|--|

| PIC16F870/871<br>(Industrial, Extended) |                                                                                                                                                                                                                                       |                                                                  |              | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |        |                                                                                       |  |  |

| Param<br>No.                            | Sym Characteristic                                                                                                                                                                                                                    |                                                                  |              | Тур†                                                                                                                                                                                                                                                         | Max        | Units  | Conditions                                                                            |  |  |

|                                         | Vdd                                                                                                                                                                                                                                   | Supply Voltage                                                   |              |                                                                                                                                                                                                                                                              |            |        |                                                                                       |  |  |

| D001                                    |                                                                                                                                                                                                                                       | PIC16LF870/871                                                   | 2.0          |                                                                                                                                                                                                                                                              | 5.5        | V      | All configurations. See Figure 14-2 for details.                                      |  |  |

| D001<br>D001A                           |                                                                                                                                                                                                                                       | PIC16F870/871                                                    | 4.0<br>Vbor* | _                                                                                                                                                                                                                                                            | 5.5<br>5.5 | V<br>V | All configurations.<br>BOR enabled, FMAX = 14 MHz <b>(Note 7)</b> ,<br>-40°C to +85°C |  |  |

|                                         |                                                                                                                                                                                                                                       |                                                                  | VBOR         | —                                                                                                                                                                                                                                                            | 5.5        | V      | BOR enabled, FMAX = 10 MHz <b>(Note 7)</b> ,<br>-40°C to +125°C                       |  |  |

| D002*                                   | Vdr                                                                                                                                                                                                                                   | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —            | 1.5                                                                                                                                                                                                                                                          | —          | V      |                                                                                       |  |  |

| D003                                    | Vpor                                                                                                                                                                                                                                  | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —            | Vss                                                                                                                                                                                                                                                          | —          | V      | See section on Power-on Reset for details                                             |  |  |

| D004*                                   | SVDD                                                                                                                                                                                                                                  | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05         | —                                                                                                                                                                                                                                                            | —          | V/ms   | See section on Power-on Reset for details                                             |  |  |

| D005                                    | VBOR                                                                                                                                                                                                                                  | Brown-out Reset<br>Voltage                                       | 3.7          | 4.0                                                                                                                                                                                                                                                          | 4.35       | V      | BOREN bit in configuration word enabled                                               |  |  |

These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active Operation mode are:

- <u>OSC1</u> = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

# 14.2 DC Characteristics: PIC16F870/871 (Industrial) (Continued)

| DC CHARACTERISTICS |       |                                                        | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>Operating voltage VDD range as described in DC spec Section 14.1<br>and Section 14.2. |      |     |       |                                                                         |  |

|--------------------|-------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-------------------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                                         | Min                                                                                                                                                                                                                             | Тур† | Max | Units | Conditions                                                              |  |

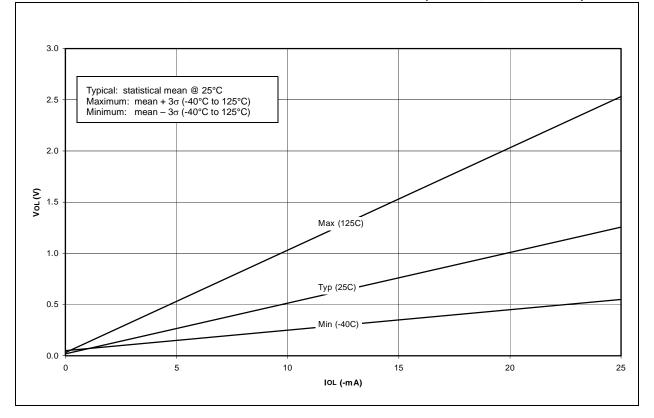

|                    | Vol   | Output Low Voltage                                     |                                                                                                                                                                                                                                 |      |     |       |                                                                         |  |

| D080               |       | I/O ports                                              | _                                                                                                                                                                                                                               | -    | 0.6 | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                             |  |

| D083               |       | OSC2/CLKO (RC osc config)                              | _                                                                                                                                                                                                                               | -    | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                             |  |

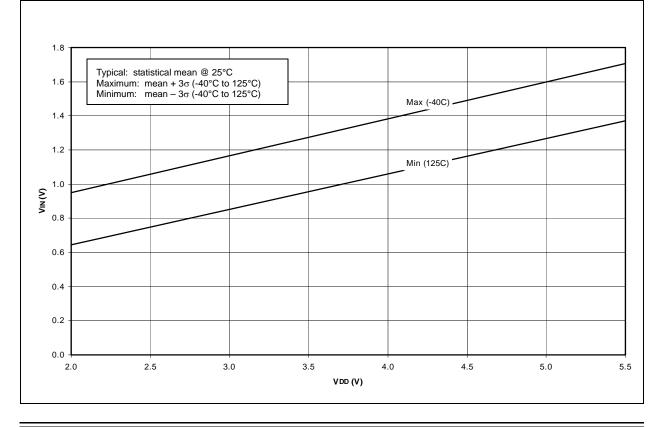

|                    | Vон   | Output High Voltage                                    |                                                                                                                                                                                                                                 |      |     |       |                                                                         |  |

| D090               |       | I/O ports <b>(Note 3)</b>                              | Vdd - 0.7                                                                                                                                                                                                                       | -    | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |

| D092               |       | OSC2/CLKO (RC osc config)                              | Vdd - 0.7                                                                                                                                                                                                                       | -    | —   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |

| D150*              | Vod   | Open Drain High Voltage                                | —                                                                                                                                                                                                                               | _    | 8.5 | V     | RA4 pin                                                                 |  |

| D100               | Cosc2 | Capacitive Loading Specs<br>on Output Pins<br>OSC2 pin | _                                                                                                                                                                                                                               | _    | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |  |

| D101               | Сю    | All I/O pins and OSC2<br>(in RC mode)                  | —                                                                                                                                                                                                                               | _    | 50  | pF    |                                                                         |  |

| D102               | Св    | SCL, SDA in I <sup>2</sup> C mode                      |                                                                                                                                                                                                                                 | —    | 400 | pF    |                                                                         |  |

|                    |       | Data EEPROM Memory                                     |                                                                                                                                                                                                                                 |      |     |       |                                                                         |  |

| D120               | ED    | Endurance                                              | 100K                                                                                                                                                                                                                            | —    | —   | E/W   | 25°C at 5V                                                              |  |

| D121               | Vdrw  | VDD for read/write                                     | Vmin                                                                                                                                                                                                                            | -    | 5.5 | V     | Using EECON to read/write<br>VMIN = min operating voltage               |  |

| D122               | TDEW  | Erase/write cycle time                                 | —                                                                                                                                                                                                                               | 4    | 8   | ms    |                                                                         |  |

|                    |       | Program FLASH Memory                                   |                                                                                                                                                                                                                                 |      |     |       |                                                                         |  |

| D130               | Eр    | Endurance                                              | 1000                                                                                                                                                                                                                            | —    | —   | E/W   | 25°C at 5V                                                              |  |

| D131               | Vpr   | VDD for read                                           | Vmin                                                                                                                                                                                                                            | —    | 5.5 | V     | VMIN = min operating voltage                                            |  |

| D132a              |       | VDD for erase/write                                    | Vmin                                                                                                                                                                                                                            | -    | 5.5 | V     | Using EECON to read/write,<br>VMIN = min operating voltage              |  |

| D133               | TPEW  | Erase/Write cycle time                                 | —                                                                                                                                                                                                                               | 4    | 8   | ms    |                                                                         |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F870/871 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

NOTES:

DS30569C-page 144

# Package Marking Information (Cont'd)

# Example PIC16F871-I/P

# Example

44-Lead TQFP

### 44-Lead PLCC

Example

| PORTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PORTC Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RC0/T1OSO/T1CKI Pin7, 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RC1/T1OSI Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RC2/CCP1 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RC3 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |