# E. Lattice Semiconductor Corporation - <u>LFSC3GA15E-6F900C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                     |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 3750                                                                         |

| Number of Logic Elements/Cells | 15000                                                                        |

| Total RAM Bits                 | 1054720                                                                      |

| Number of I/O                  | 300                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 0.95V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 900-BBGA                                                                     |

| Supplier Device Package        | 900-FPBGA (31x31)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfsc3ga15e-6f900c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

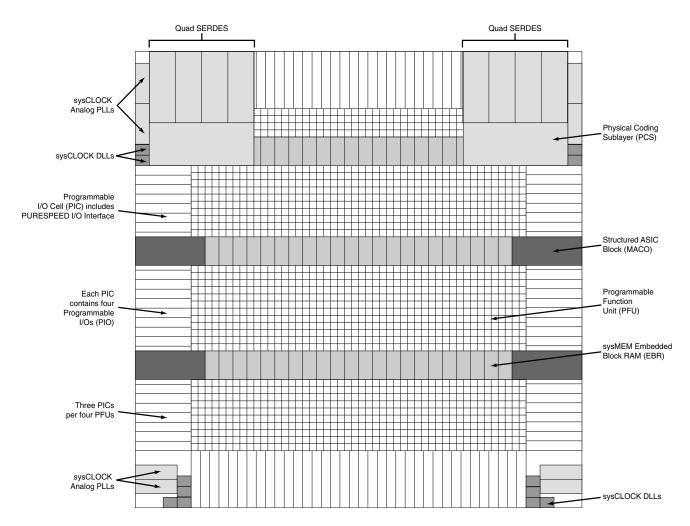

DLLs and dynamic glitch free clock MUXs which are required in today's high end system designs. High-speed, high-bandwidth I/O make this family ideal for high-throughput systems.

The ispLEVER<sup>®</sup> design tool from Lattice allows large complex designs to be efficiently implemented using the LatticeSC family of FPGA devices. Synthesis library support for LatticeSC is available for popular logic synthesis tools. The ispLEVER tool uses the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeSC device. The ispLEVER tool extracts the timing from the routing and backannotates it into the design for timing verification.

Lattice provides many pre-designed IP (Intellectual Property) ispLeverCORE<sup>™</sup> modules for the LatticeSC family. By using these IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

Innovative high-performance FPGA architecture, high-speed SERDES with PCS support, sysMEM embedded memory and high performance I/O are combined in the LatticeSC to provide excellent performance for today's leading edge systems designs. Table 1-3 details the performance of several common functions implemented within the LatticeSC.

Table1-3. Speed Performance for Typical Functions<sup>1</sup>

| Functions                                         | Performance (MHz) <sup>2</sup> |

|---------------------------------------------------|--------------------------------|

| 32-bit Address Decoder                            | 539                            |

| 64-bit Address Decoder                            | 517                            |

| 32:1 Multiplexer                                  | 779                            |

| 64-bit Adder (ripple)                             | 353                            |

| 32x8 Distributed Single Port (SP) RAM             | 768                            |

| 64-bit Counter (up or down counter, non-loadable) | 369                            |

| True Dual-Port 1024x18 bits                       | 372                            |

| FIFO Port A: x36 bits, B: x9 bits                 | 375                            |

1. For additional information, see Typical Building BLock Function Performance table in this data sheet.

2. Advance information (-7 speed grade).

### **PFU Modes of Operation**

Slices can be combined within a PFU to form larger functions. Table 2-4 tabulates these modes and documents the functionality possible at the PFU level.

#### Table 2-4. PFU Modes of Operation

| Logic                      | Ripple            | RAM                          | ROM          |

|----------------------------|-------------------|------------------------------|--------------|

| LUT 4x8 or<br>MUX 2x1 x 8  | 2-bit Add x 4     | SPR 16x2 x 4<br>DPR 16x2 x 2 | ROM 16x1 x 8 |

| LUT 5x4 or<br>MUX 4x1 x 4  | 2-bit Sub x 4     | SPR 16x4 x 2<br>DPR 16x4 x 1 | ROM 16x2 x 4 |

| LUT 6x2 or<br>MUX 8x1 x 2  | 2-bit Counter x 4 | SPR 16x8 x 1                 | ROM 16x4 x 2 |

| LUT 7x1 or<br>MUX 16x1 x 1 | 2-bit Comp x 4    |                              | ROM 16x8 x1  |

### Routing

There are many resources provided in the LatticeSC devices to route signals individually or as busses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with x1 (spans two PFU), x2 (spans three PFU) and x6 (spans seven PFU) resources. The x1 and x2 connections provide fast and efficient connections in horizontal, vertical and diagonal directions. All connections are buffered to ensure high-speed operation even with long high-fanout connections.

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

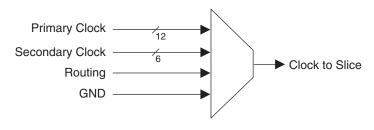

### sysCLOCK Network

The LatticeSC devices have three distinct clock networks for use in distributing high-performance clocks within the device: primary clocks, secondary clocks and edge clocks. In addition to these dedicated clock networks, users are free to route clocks within the device using the general purpose routing. Figure 2-4 shows the clock resources available to each slice.

#### Figure 2-4. Slice Clock Selection

Note: GND is available to switch off the network.

### **Primary Clock Sources**

LatticeSC devices have a wide variety of primary clock sources available. Primary clocks sources consists of the following:

- Primary clock input pins

- Edge clock input pins

- Two outputs per DLL

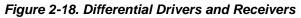

high-speed interfaces in the LatticeSC devices. Figure 2-18 shows how differential receivers and drivers are arranged between PIOs.

\*Differential Driver only available on right and left of the device.

### PIO

The PIO contains five blocks: an input register block, output register block, tristate register block, update block, and a control logic block. These blocks contain registers for both single data rate (SDR), double data rate (DDR), and shift register operation along with the necessary clock and selection logic.

### Input Register Block

The input register block contains delay elements and registers that can be used to condition signals before they are passed to the device core. Figure 2-20 show the diagram of the input register block. The signal from the PURE-SPEED I/O buffer (DI) enters the input register block and can be used for three purposes, as a source for the combinatorial (INDD) and clock outputs (INCK), the input into the SDR register/latch block and the input to the delay block. The output of the delay block can be used as combinatorial (INDD) and clock (INCK) outputs, an input to the DDR/Shift Register Block or an input into the SDR register block.

#### Input SDR Register/Latch Block

The SDR register/latch block has a latch and a register/latch that can be used in a variety of combinations to provide a registered or latched output (INFF). The latch operates off high-speed input clocks and latches data on the positive going edge. The register/latch operates off the low-speed input clock and registers/latches data on the positive going edge. Both the latch and the register/latch have a clock enable input that is driven by the input clock enable. In addition both have a variety of programmable options for set/reset including, set or reset, asynchronous or synchronous Local Set Reset LSR (LSR has precedence over CE) and Global Set Reset GSR enable or disable. The register and latch LSR inputs are driven from LSRI, which is generated from the PIO control MUX. The GSR inputs are driven from the GSR output of the PIO control MUX, which allows the global set-reset to be disabled on a PIO basis.

#### Input Delay Block

The delay block uses 144 tapped delay lines to obtain coarse and fine delay resolution. These delays can be adjusted during configuration or automatically via DLL or AIL blocks. The Adaptive Input Logic (AIL) uses this delay block to adjust automatically the delay in the data path to ensure that it has sufficient setup and hold time.

The delay line in this block matches the delay line that is used in the 12 on-chip DLLs. The delay line can be set via configuration bits or driven from a calibration bus that allows the setting to be controlled either from one of the on-chip DLLs or user logic. Controlling the delay from one of the on-chip DLLs allow the delay to be calibrated to the DLL clock and hence compensated for the variations in process, voltage and temperature.

VDDAX25 needs to be connected independent of the use of the SERDES. This supply is used to control the SERDES CML I/O regardless of the SERDES being used in the design.

#### Supported Source Synchronous Interfaces

The LatticeSC devices contain a variety of hardware, such as delay elements, DDR registers and PLLs, to simplify the implementation of Source Synchronous interfaces. Table 2-11 lists Source Synchronous and DDR/QDR standards supported in the LatticeSC. For additional detail refer to technical information at the end of the data sheet.

Source Synchronous Standard Clocking Speeds (MHz) Data Rate (Mbps) RapidIO DDR 500 1000 SPI4.2 (POS-PHY4)/NPSI DDR 1000 500 DDR 334 667 SFI4/XSBI SDR 667 DDR XGMII 156.25 312 CSIX SDR 250 250 QDRII/QDRII+ memory interface DDR 300 600 DDR memory interface DDR 240 480 DDR 333 667 DDRII memory interface DDR 400 800 **RLDRAM** memory interface

#### Table 2-11. Source Synchronous Standards Table<sup>1</sup>

1. Memory width is dependent on the system design and limited by the number of I/Os in the device.

### flexiPCS<sup>™</sup> (Physical Coding Sublayer Block)

#### flexiPCS Functionality

The LatticeSC family combines a high-performance FPGA fabric, high-performance I/Os and large embedded RAM in a single industry leading architecture. LatticeSC devices also feature up to 32 channels of embedded SERDES with associated Physical Coding Sublayer (PCS) logic. The flexiPCS logic can be configured to support numerous industry standard high-speed data transfer protocols.

Each channel of flexiPCS logic contains dedicated transmit and receive SERDES for high-speed, full-duplex serial data transfers at data rates up to 3.8 Gbps. The PCS logic in each channel can be configured to support an array of popular data protocols including SONET (STS-12/STS-12c, STS-48/STS-48c, and TFI-5 support of 10 Gbps or above), Gigabit Ethernet (compliant to the IEEE 1000BASE-X specification), 1.02 or 2.04 Gbps Fibre Channel, PCI-Express, and Serial RapidIO. In addition, the protocol based logic can be fully or partially bypassed in a number of configurations to allow users flexibility in designing their own high-speed data interface.

Protocols requiring data rates above 3.8 Gbps can be accommodated by dedicating either one pair or all four channels in one flexiPCS quad block to one data link. One quad can support full-duplex serial data transfers at data rates up to 15.2 Gbps. A single flexiPCS quad can be configured to support 10Gb Ethernet (with a fully compliant XAUI interface), 10Gb Fibre Channel, and x4 PCI-Express and 4x RapidIO.

The flexiPCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic which can also be geared to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic. Each SERDES pin can be DC coupled independently and can allow for both high-speed and low-speed operation down to DC rates on the same SERDES pin, as required by some Serial Digital Video applications.

The ispLEVER design tools from Lattice support all modes of the flexiPCS. Most modes are dedicated to applications associated with a specific industry standard data protocol. Other more general purpose modes allow a user to define their own operation. With ispLEVER, the user can define the mode for each quad in a design. Nine modes are currently supported by the ispLEVER design flow:

# PURESPEED I/O Differential Electrical Characteristics LVDS

| Parameter<br>Symbol                | Parameter Description                           | Test Conditions                                                | Min.   | Тур. | Max.  | Units                           |

|------------------------------------|-------------------------------------------------|----------------------------------------------------------------|--------|------|-------|---------------------------------|

| V <sub>INP,</sub> V <sub>INM</sub> | Input voltage                                   |                                                                | 0      | _    | 2.4   | V                               |

| V <sub>THD</sub>                   | Differential input threshold $(Q-\overline{Q})$ |                                                                | +/-100 | _    | —     | mV                              |

| V <sub>CM</sub>                    | Input common mode voltage                       |                                                                | 0.05   | 1.2  | 2.35  | V                               |

| I <sub>IN</sub>                    | Input current                                   | Power on or power off                                          | —      | _    | +/-10 | μΑ                              |

| V <sub>OH</sub>                    | Output high voltage for $V_{OP}$ or $V_{OM}$    | R <sub>T</sub> = 100 Ohm                                       | —      | 1.38 | 1.60  | V                               |

| V <sub>OL</sub>                    | Output low voltage for $V_{OP}$ or $V_{OM}$     | R <sub>T</sub> = 100 Ohm                                       | 0.9V   | 1.03 | —     | V                               |

| V <sub>OD</sub>                    | Output voltage differential                     | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm | 250    | 350  | 450   | mV                              |

| ΔV <sub>OD</sub>                   | Change in V <sub>OD</sub> between high and low  |                                                                | —      | _    | 50    | mV                              |

| V <sub>OS</sub>                    | Output voltage offset                           | $(V_{OP} - V_{OM})/2, R_T = 100 \text{ Ohm}$                   | 1.125  | 1.20 | 1.375 | V                               |

| $\Delta V_{OS}$                    | Change in V <sub>OS</sub> between H and L       |                                                                | —      |      | 50    | mV                              |

| I <sub>SAB</sub>                   | Output short circuit current                    | V <sub>OD</sub> = 0V Driver outputs shorted                    | —      | _    | 12    | mA                              |

| T <sub>R</sub> , T <sub>F</sub>    | Output rise and fall times, 20% to 80%          | _                                                              | —      | 500  | ps    | T <sub>R</sub> , T <sub>F</sub> |

#### **Over Recommended Operating Conditions**

Notes:

1. Data is for 3.5mA differential current drive. Other differential driver current options are available.

2. If the low power mode of the input buffer is used, the minimum  $V_{CM}$  is 600 mV.

#### **Mini-LVDS**

#### **Over Recommended Operating Conditions**

| Parameter Symbol                | Description                                                       | Min.                      | Тур. | Max.                      | Units |

|---------------------------------|-------------------------------------------------------------------|---------------------------|------|---------------------------|-------|

| Z <sub>O</sub>                  | Single-ended PCB trace impedance                                  | 30                        | 50   | 75                        | ohms  |

| R <sub>T</sub>                  | Differential termination resistance                               | 60                        | 100  | 150                       | ohms  |

| V <sub>OD</sub>                 | Output voltage, differential,  V <sub>OP</sub> - V <sub>OM</sub>  | 300                       | _    | 600                       | mV    |

| V <sub>OS</sub>                 | Output voltage, common mode, $ V_{OP} + V_{OM} /2$                | 1                         | 1.2  | 1.4                       | V     |

| ΔV <sub>OD</sub>                | Change in V <sub>OD</sub> , between H and L                       | —                         | _    | 50                        | mV    |

| $\Delta V_{ID}$                 | Change in V <sub>OS</sub> , between H and L                       | —                         | _    | 50                        | mV    |

| V <sub>THD</sub>                | Input voltage, differential,  V <sub>INP</sub> - V <sub>INM</sub> | 200                       | _    | 600                       | mV    |

| V <sub>CM</sub>                 | Input voltage, common mode, $ V_{INP} + V_{INM} /2$               | 0.3+(V <sub>THD</sub> /2) | _    | 2.1-(V <sub>THD</sub> /2) |       |

| T <sub>R</sub> , T <sub>F</sub> | Output rise and fall times, 20% to 80%                            | —                         | _    | 500                       | ps    |

| T <sub>ODUTY</sub>              | Output clock duty cycle                                           | 45                        | _    | 55                        | %     |

| T <sub>IDUTY</sub>              | Input clock duty cycle                                            | 40                        | _    | 60                        | %     |

Note: Data is for 6mA differential current drive. Other differential driver current options are available.

### **Signal Descriptions (Cont.)**

| Signal Name         | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESP_[ULC/URC]      | _   | Calibration resistor to be placed between this pin and either ground or RESPN_[ULC/URC]. RESPN_[ULC/URC] is available on select pack-<br>ages. If available, connection of calibration resistor between RESP_[ULC/URC] and RESPN_[ULC/URC] takes precedence over connection of calibration resistor between RESP_[ULC/URC] and ground. Note: only one per side of the device. Value: 4.02K ohm +/- 1% ohm. |

| RESPN_[ULC/URC]     | _   | Available on selected packages. If available, calibration resistor should be placed between RESP_[ULC/URC] and RESPN_[ULC/URC] instead of between RESP_[ULC/URC] and ground. Note: only one per side of the device. Value: 4.02K ohm +/- 1% ohm.                                                                                                                                                           |

| [A:D]_VDDIBx_[L/R]  | _   | Input buffer power supply for channel x (1.2V/1.5V) on left [L] or right [R] side of device.                                                                                                                                                                                                                                                                                                               |

| [A:D]_VDDOBx_[L/R]  | -   | Output buffer power supply for channel x (1.2V/1.5V) on left [L] or right [R] side of device.                                                                                                                                                                                                                                                                                                              |

| [A:D]_VDDAX25_[L/R] | -   | Auxiliary power for input and output termination (2.5V) on left [L] or right [R] side of device.                                                                                                                                                                                                                                                                                                           |

1. The ispLEVER software tools may specify VDDRX, VDDTX, VDDP and VCCL pins. These pins should be considered VCC12 pins. Note: Signals listed as Signal A / Signal B define the same physical pin that is used for different functions based on configuration mode.

|                | LFSC/M15      |               |               |               |               | LFSC/M25      |

|----------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Ball<br>Number | Ball Function | VCCIO<br>Bank | Dual Function | Ball Function | VCCIO<br>Bank | Dual Function |

| B29            | NC            | -             |               | NC            | -             |               |

1. Differential pair grouping within a PIC is A (True) and B (Complement) and C (True) and D (Complement).

2. The LatticeSC/M15 and LatticeSC/M25 in a 900-pin package supports a 16-bit MPI interface.

| Ball         |               | LFSC/N     |               |               | LFSC/      |               |

|--------------|---------------|------------|---------------|---------------|------------|---------------|

| Number       | Ball Function | VCCIO Bank | Dual Function | Ball Function | VCCIO Bank | Dual Function |

| E22          | VCC12         | -          |               | VCC12         | -          |               |

| E21          | VCC12         | -          |               | VCC12         | -          |               |

| E3           | VCC12         | -          |               | VCC12         | -          |               |

| E4           | VCC12         | -          |               | VCC12         | -          |               |

| E6           | VCC12         | -          |               | VCC12         | -          |               |

| E7           | VCC12         | -          |               | VCC12         | -          |               |

| E8           | VCC12         | -          |               | VCC12         | -          |               |

| E9           | VCC12         | -          |               | VCC12         | -          |               |

| E11          | VCC12         | -          |               | VCC12         | -          |               |

| E12          | VCC12         | -          |               | VCC12         | -          |               |

| A23          | GND           | -          |               | GND           | -          |               |

| A31          | GND           | -          |               | GND           | -          |               |

| AA13         | GND           | -          |               | GND           | -          |               |

| AA15         | GND           | -          |               | GND           | -          |               |

| AA18         | GND           | -          |               | GND           | -          |               |

| AA20         | GND           | -          |               | GND           | -          |               |

| AA26         | GND           | -          |               | GND           | -          |               |

| AA6          | GND           | -          |               | GND           | -          |               |

| AB10         | GND           | -          |               | GND           | -          |               |

| AB24         | GND           | -          |               | GND           | -          |               |

| AC14         | GND           | -          |               | GND           | -          |               |

| AC14<br>AC22 | GND           |            |               | GND           | -          |               |

|              |               | -          |               |               |            |               |

| AC29         | GND           | -          |               | GND           | -          |               |

| AC3          | GND           | -          |               | GND           | -          |               |

| AD11         | GND           | -          |               | GND           | -          |               |

| AD19         | GND           | -          |               | GND           | -          |               |

| AD27         | GND           | -          |               | GND           | -          |               |

| AD7          | GND           | -          |               | GND           | -          |               |

| AF12         | GND           | -          |               | GND           | -          |               |

| AF18         | GND           | -          |               | GND           | -          |               |

| AF24         | GND           | -          |               | GND           | -          |               |

| AF30         | GND           | -          |               | GND           | -          |               |

| AF4          | GND           | -          |               | GND           | -          |               |

| AG15         | GND           | -          |               | GND           | -          |               |

| AG21         | GND           | -          |               | GND           | -          |               |

| AG9          | GND           | -          |               | GND           | -          |               |

| AJ10         | GND           | -          |               | GND           | -          |               |

| AJ16         | GND           | -          |               | GND           | -          |               |

| AJ20         | GND           | -          |               | GND           | -          |               |

| AJ26         | GND           | -          |               | GND           | -          |               |

| AJ29         | GND           | -          |               | GND           | -          |               |

| AJ4          | GND           | -          |               | GND           | -          |               |

| AK13         | GND           | -          |               | GND           | -          |               |

| AK17         | GND           | -          |               | GND           | -          |               |

| AK23         | GND           | -          |               | GND           | -          |               |

| AK7          | GND           | -          |               | GND           | -          |               |

| AL1          | GND           | -          |               | GND           | -          |               |

| AL32         | GND           | -          |               | GND           | -          |               |

| AM2          | GND           | -          |               | GND           | -          |               |

| AM31         | GND           | -          |               | GND           | -          |               |

|                |                  | LFSC/M40      |                             |                  | LFSC/M80      |                             |  |  |

|----------------|------------------|---------------|-----------------------------|------------------|---------------|-----------------------------|--|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual Function               | Ball<br>Function | VCCIO<br>Bank | Dual Function               |  |  |

| L1             | PR31A            | 2             |                             | PR43A            | 2             |                             |  |  |

| T10            | PR30D            | 2             |                             | PR42D            | 2             |                             |  |  |

| U10            | PR30C            | 2             |                             | PR42C            | 2             |                             |  |  |

| N2             | PR30B            | 2             |                             | PR42B            | 2             |                             |  |  |

| M2             | PR30A            | 2             |                             | PR42A            | 2             |                             |  |  |

| R11            | PR29D            | 2             |                             | PR37D            | 2             |                             |  |  |

| P11            | PR29C            | 2             |                             | PR37C            | 2             |                             |  |  |

| N4             | PR29B            | 2             |                             | PR37B            | 2             |                             |  |  |

| M4             | PR29A            | 2             |                             | PR37A            | 2             |                             |  |  |

| N5             | PR27D            | 2             |                             | PR35D            | 2             |                             |  |  |

| M5             | PR27C            | 2             |                             | PR35C            | 2             |                             |  |  |

| L2             | PR27B            | 2             |                             | PR35B            | 2             |                             |  |  |

| K2             | PR27A            | 2             |                             | PR35A            | 2             |                             |  |  |

| P8             | PR26D            | 2             |                             | PR33D            | 2             |                             |  |  |

| N8             | PR26C            | 2             |                             | PR33C            | 2             |                             |  |  |

| J2             | PR26B            | 2             |                             | PR33B            | 2             |                             |  |  |

| H2             | PR26A            | 2             |                             | PR33A            | 2             |                             |  |  |

| M6             | PR25D            | 2             |                             | PR31D            | 2             |                             |  |  |

| L6             | PR25C            | 2             |                             | PR31C            | 2             |                             |  |  |

| K3             | PR25B            | 2             |                             | PR31B            | 2             |                             |  |  |

| J3             | PR25A            | 2             |                             | PR31A            | 2             |                             |  |  |

| M8             | PR23D            | 2             | DIFFR_2                     | PR29D            | 2             | DIFFR_2                     |  |  |

| L8             | PR23C            | 2             | VREF1_2                     | PR29C            | 2             | VREF1_2                     |  |  |

| K4             | PR23B            | 2             |                             | PR29B            | 2             |                             |  |  |

| J4             | PR23A            | 2             |                             | PR29A            | 2             |                             |  |  |

| M7             | PR22D            | 2             |                             | PR21D            | 2             |                             |  |  |

| L7             | PR22C            | 2             |                             | PR21C            | 2             |                             |  |  |

| J5             | PR22B            | 2             |                             | PR21B            | 2             |                             |  |  |

| H5             | PR22A            | 2             |                             | PR21A            | 2             |                             |  |  |

| N9             | PR21D            | 2             |                             | PR20D            | 2             |                             |  |  |

| P9             | PR21C            | 2             |                             | PR20C            | 2             |                             |  |  |

| G3             | PR21B            | 2             |                             | PR20B            | 2             |                             |  |  |

| F3             | PR21A            | 2             |                             | PR20A            | 2             |                             |  |  |

| J6             | PR18D            | 2             | VREF2_2                     | PR18D            | 2             | VREF2_2                     |  |  |

| H6             | PR18C            | 2             |                             | PR18C            | 2             |                             |  |  |

| E2             | PR18B            | 2             | URC_DLLC_IN_D/URC_DLLC_FB_C | PR18B            | 2             | URC_DLLC_IN_D/URC_DLLC_FB_C |  |  |

| D2             | PR18A            | 2             | URC_DLLT_IN_D/URC_DLLT_FB_C | PR18A            | 2             | URC_DLLT_IN_D/URC_DLLT_FB_C |  |  |

| P10            | PR17D            | 2             | URC_PLLC_IN_B/URC_PLLC_FB_A | PR17D            | 2             | URC_PLLC_IN_B/URC_PLLC_FB_A |  |  |

| N10            | PR17C            | 2             | URC_PLLT_IN_B/URC_PLLT_FB_A | PR17C            | 2             | URC_PLLT_IN_B/URC_PLLT_FB_A |  |  |

| G4             | PR17B            | 2             | URC_DLLC_IN_C/URC_DLLC_FB_D | PR17B            | 2             | URC_DLLC_IN_C/URC_DLLC_FB_D |  |  |

| F4             | PR17A            | 2             | URC_DLLT_IN_C/URC_DLLT_FB_D | PR17A            | 2             | URC_DLLT_IN_C/URC_DLLT_FB_D |  |  |

| J7             | PR16D            | 2             |                             | PR16D            | 2             |                             |  |  |

| H7             | PR16C            | 2             |                             | PR16C            | 2             |                             |  |  |

| G5             | PR16B            | 2             | URC_PLLC_IN_A/URC_PLLC_FB_B | PR16B            | 2             | URC_PLLC_IN_A/URC_PLLC_FB_B |  |  |

| F5             | PR16A            | 2             | URC_PLLT_IN_A/URC_PLLT_FB_B | PR16A            | 2             | URC_PLLT_IN_A/URC_PLLT_FB_B |  |  |

| Γ              |                  | LFSC/M40      |                             |                  | LFSC/M80      |                             |  |  |

|----------------|------------------|---------------|-----------------------------|------------------|---------------|-----------------------------|--|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual Function               | Ball<br>Function | VCCIO<br>Bank | Dual Function               |  |  |

| F15            | PT55A            | 1             | D5/MPI_DATA5                | PT74A            | 1             | D5/MPI_DATA5                |  |  |

| K14            | PT54D            | 1             | D4/MPI_DATA4                | PT73D            | 1             | D4/MPI_DATA4                |  |  |

| K13            | PT54C            | 1             | D3/MPI_DATA3                | PT73C            | 1             | D3/MPI_DATA3                |  |  |

| B15            | PT53B            | 1             | D2/MPI_DATA2                | PT73B            | 1             | D2/MPI_DATA2                |  |  |

| A15            | PT53A            | 1             | D1/MPI_DATA1                | PT73A            | 1             | D1/MPI_DATA1                |  |  |

| J14            | PT51D            | 1             | D16/PCLKC1_3/MPI_DATA16     | PT71D            | 1             | D16/PCLKC1_3/MPI_DATA16     |  |  |

| H14            | PT51C            | 1             | D17/PCLKT1_3/MPI_DATA17     | PT71C            | 1             | D17/PCLKT1_3/MPI_DATA17     |  |  |

| A16            | PT51B            | 1             | D0/MPI_DATA0                | PT71B            | 1             | D0/MPI_DATA0                |  |  |

| B16            | PT51A            | 1             | QOUT/CEON                   | PT71A            | 1             | QOUT/CEON                   |  |  |

| J13            | PT50D            | 1             | VREF2_1                     | PT70D            | 1             | VREF2_1                     |  |  |

| H13            | PT50C            | 1             | D18/MPI_DATA18              | PT70C            | 1             | D18/MPI_DATA18              |  |  |

| D15            | PT50B            | 1             | DOUT                        | PT70B            | 1             | DOUT                        |  |  |

| E15            | PT50A            | 1             | MCA_DONE_IN                 | PT70A            | 1             | MCA_DONE_IN                 |  |  |

| J16            | PT49D            | 1             | D19/PCLKC1_2/MPI_DATA19     | PT69D            | 1             | D19/PCLKC1_2/MPI_DATA19     |  |  |

| J17            | PT49C            | 1             | D20/PCLKT1_2/MPI_DATA20     | PT69C            | 1             | D20/PCLKT1_2/MPI_DATA20     |  |  |

| D16            | PT49B            | 1             | MCA_CLK_P1_OUT              | PT69B            | 1             | MCA_CLK_P1_OUT              |  |  |

| E16            | PT49A            | 1             | MCA_CLK_P1_IN               | PT69A            | 1             | MCA_CLK_P1_IN               |  |  |

| H15            | PT47D            | 1             | D21/PCLKC1_1/MPI_DATA21     | PT67D            | 1             | D21/PCLKC1_1/MPI_DATA21     |  |  |

| H16            | PT47C            | 1             | D22/PCLKT1_1/MPI_DATA22     | PT67C            | 1             | D22/PCLKT1_1/MPI_DATA22     |  |  |

| C15            | PT47B            | 1             | MCA_CLK_P2_OUT              | PT67B            | 1             | MCA_CLK_P2_OUT              |  |  |

| C16            | PT47A            | 1             | MCA_CLK_P2_IN               | PT67A            | 1             | MCA_CLK_P2_IN               |  |  |

| L17            | PT46D            | 1             | MCA_DONE_OUT                | PT66D            | 1             | MCA_DONE_OUT                |  |  |

| K17            | PT46C            | 1             | BUSYN/RCLK/SCK              | PT66C            | 1             | BUSYN/RCLK/SCK              |  |  |

| E17            | PT46B            | 1             | DP0/MPI_PAR0                | PT66B            | 1             | DP0/MPI_PAR0                |  |  |

| F17            | PT46A            | 1             | MPI_TA                      | PT66A            | 1             | MPI_TA                      |  |  |

| G17            | PT45D            | 1             | D23/MPI_DATA23              | PT65D            | 1             | D23/MPI_DATA23              |  |  |

| H17            | PT45C            | 1             | <br>DP2/MPI_PAR2            | PT65C            | 1             | <br>DP2/MPI_PAR2            |  |  |

| A17            | PT45B            | 1             | PCLKC1_0                    | PT65B            | 1             | PCLKC1_0                    |  |  |

| B17            | PT45A            | 1             | PCLKT1_0/MPI_CLK            | PT65A            | 1             | PCLKT1_0/MPI_CLK            |  |  |

| G18            | PT43D            | 1             | DP3/PCLKC1_4/MPI_PAR3       | PT63D            | 1             | DP3/PCLKC1_4/MPI_PAR3       |  |  |

| H18            | PT43C            | 1             | <br>D24/PCLKT1_4/MPI_DATA24 | PT63C            | 1             | <br>D24/PCLKT1_4/MPI_DATA24 |  |  |

| E18            | PT43B            | 1             | MPI_RETRY                   | PT63B            | 1             | MPI_RETRY                   |  |  |

| F18            | PT43A            | 1             | A0/MPI_ADDR14               | PT63A            | 1             | A0/MPI_ADDR14               |  |  |

| J18            | PT42D            | 1             | A1/MPI_ADDR15               | PT61D            | 1             | A1/MPI_ADDR15               |  |  |

| J19            | PT42C            | 1             | A2/MPI ADDR16               | PT61C            | 1             | A2/MPI_ADDR16               |  |  |

| C20            | PT42B            | 1             | A3/MPI_ADDR17               | PT61B            | 1             | A3/MPI_ADDR17               |  |  |

| C19            | PT42A            | 1             | A4/MPI ADDR18               | PT61A            | 1             | A4/MPI_ADDR18               |  |  |

| K18            | PT41D            | 1             | D25/PCLKC1_5/MPI_DATA25     | PT60D            | 1             | D25/PCLKC1_5/MPI_DATA25     |  |  |

| L18            | PT41C            | 1             | D26/PCLKT1_5/MPI_DATA26     | PT60C            | 1             | D26/PCLKT1_5/MPI_DATA26     |  |  |

| D19            | PT41B            | 1             | A5/MPI_ADDR19               | PT60B            | 1             | A5/MPI_ADDR19               |  |  |

| E19            | PT41A            | 1             | A6/MPI_ADDR20               | PT60A            | 1             | A6/MPI_ADDR20               |  |  |

| H19            | PT39D            | 1             | D27/MPI_DATA27              | PT59D            | 1             | D27/MPI_DATA27              |  |  |

| H20            | PT39C            | 1             | VREF1_1                     | PT59C            | 1             | VREF1_1                     |  |  |

| A18            | PT39B            | 1             | A7/MPI_ADDR21               | PT59B            | 1             | A7/MPI_ADDR21               |  |  |

| B18            | PT39A            | 1             | A8/MPI_ADDR22               | PT59A            | 1             | A8/MPI_ADDR22               |  |  |

|                | LFSC/M40         |               |                         |                  |               | LFSC/M80                |  |  |

|----------------|------------------|---------------|-------------------------|------------------|---------------|-------------------------|--|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual Function           | Ball<br>Function | VCCIO<br>Bank | Dual Function           |  |  |

| H21            | PT38D            | 1             | D28/PCLKC1_6/MPI_DATA28 | PT57D            | 1             | D28/PCLKC1_6/MPI_DATA28 |  |  |

| J21            | PT38C            | 1             | D29/PCLKT1_6/MPI_DATA29 | PT57C            | 1             | D29/PCLKT1_6/MPI_DATA29 |  |  |

| A19            | PT38B            | 1             | A9/MPI_ADDR23           | PT57B            | 1             | A9/MPI_ADDR23           |  |  |

| B19            | PT38A            | 1             | A10/MPI_ADDR24          | PT57A            | 1             | A10/MPI_ADDR24          |  |  |

| H22            | PT37D            | 1             | D30/PCLKC1_7/MPI_DATA30 | PT56D            | 1             | D30/PCLKC1_7/MPI_DATA30 |  |  |

| J22            | PT37C            | 1             | D31/PCLKT1_7/MPI_DATA31 | PT56C            | 1             | D31/PCLKT1_7/MPI_DATA31 |  |  |

| F20            | PT37B            | 1             | A11/MPI_ADDR25          | PT56B            | 1             | A11/MPI_ADDR25          |  |  |

| G20            | PT37A            | 1             | A12/MPI_ADDR26          | PT56A            | 1             | A12/MPI_ADDR26          |  |  |

| K21            | PT35D            | 1             | D11/MPI_DATA11          | PT55D            | 1             | D11/MPI_DATA11          |  |  |

| K22            | PT35C            | 1             | D12/MPI_DATA12          | PT55C            | 1             | D12/MPI_DATA12          |  |  |

| A20            | PT35B            | 1             | A13/MPI_ADDR27          | PT55B            | 1             | A13/MPI_ADDR27          |  |  |

| B20            | PT35A            | 1             | A14/MPI_ADDR28          | PT55A            | 1             | A14/MPI_ADDR28          |  |  |

| L21            | PT33D            | 1             | A16/MPI_ADDR30          | PT53D            | 1             | A16/MPI_ADDR30          |  |  |

| L20            | PT33C            | 1             | D13/MPI_DATA13          | PT53C            | 1             | D13/MPI_DATA13          |  |  |

| D20            | PT33B            | 1             | A15/MPI_ADDR29          | PT53B            | 1             | A15/MPI_ADDR29          |  |  |

| E20            | PT33A            | 1             | A17/MPI_ADDR31          | PT53A            | 1             | A17/MPI_ADDR31          |  |  |

| L19            | PT30D            | 1             | A19/MPI_TSIZ1           | PT52D            | 1             | A19/MPI_TSIZ1           |  |  |

| K19            | PT30C            | 1             | A20/MPI_BDIP            | PT52C            | 1             | A20/MPI_BDIP            |  |  |

| D21            | PT30B            | 1             | A18/MPI_TSIZ0           | PT52B            | 1             | A18/MPI_TSIZ0           |  |  |

| E21            | PT30A            | 1             | MPI_TEA                 | PT52A            | 1             | MPI_TEA                 |  |  |

| M20            | PT28D            | 1             | D14/MPI_DATA14          | PT51D            | 1             | D14/MPI_DATA14          |  |  |

| M19            | PT28C            | 1             | DP1/MPI_PAR1            | PT51C            | 1             | DP1/MPI_PAR1            |  |  |

| F21            | PT27B            | 1             | A21/MPI_BURST           | PT51B            | 1             | A21/MPI_BURST           |  |  |

| G21            | PT27A            | 1             | D15/MPI_DATA15          | PT51A            | 1             | D15/MPI_DATA15          |  |  |

| H24            | B_REFCLKP_L      | -             |                         | B_REFCLKP_L      | -             |                         |  |  |

| J24            | B_REFCLKN_L      | -             |                         | B_REFCLKN_L      | -             |                         |  |  |

| L22            | VCC12            | -             |                         | VCC12            | -             |                         |  |  |

| E26            | B_VDDIB3_L       | -             |                         | B_VDDIB3_L       | -             |                         |  |  |

| G22            | VCC12            | -             |                         | VCC12            | -             |                         |  |  |

| E22            | B_HDINP3_L       | -             | PCS 361 CH 3 IN P       | B_HDINP3_L       | -             | PCS 361 CH 3 IN P       |  |  |

| F22            | B_HDINN3_L       | -             | PCS 361 CH 3 IN N       | B_HDINN3_L       | -             | PCS 361 CH 3 IN N       |  |  |

| A21            | B_HDOUTP3_L      | -             | PCS 361 CH 3 OUT P      | B_HDOUTP3_L      | -             | PCS 361 CH 3 OUT P      |  |  |

| L24            | VCC12            | -             |                         | VCC12            | -             |                         |  |  |

| B21            | B_HDOUTN3_L      | -             | PCS 361 CH 3 OUT N      | B_HDOUTN3_L      | -             | PCS 361 CH 3 OUT N      |  |  |

| D22            | B_VDDOB3_L       | -             |                         | B_VDDOB3_L       | -             |                         |  |  |

| B22            | B_HDOUTN2_L      | -             | PCS 361 CH 2 OUT N      | B_HDOUTN2_L      | -             | PCS 361 CH 2 OUT N      |  |  |

| D23            | B_VDDOB2_L       | -             |                         | B_VDDOB2_L       | -             |                         |  |  |

| A22            | B_HDOUTP2_L      | -             | PCS 361 CH 2 OUT P      | B_HDOUTP2_L      | -             | PCS 361 CH 2 OUT P      |  |  |

| K24            | VCC12            | -             |                         | VCC12            | -             |                         |  |  |

| F23            | B_HDINN2_L       | -             | PCS 361 CH 2 IN N       | B_HDINN2_L       | -             | PCS 361 CH 2 IN N       |  |  |

| E23            | B_HDINP2_L       | -             | PCS 361 CH 2 IN P       | B_HDINP2_L       | -             | PCS 361 CH 2 IN P       |  |  |

| D26            | B_VDDIB2_L       | -             |                         | B_VDDIB2_L       | -             |                         |  |  |

| G23            | VCC12            | -             |                         | VCC12            | -             |                         |  |  |

| D27            | B_VDDIB1_L       | -             |                         | B_VDDIB1_L       | -             |                         |  |  |

| G24            | VCC12            | -             |                         | VCC12            | -             |                         |  |  |

# LFSC/M115 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup>

|             | LFSC/M115     |            |               |  |  |  |  |

|-------------|---------------|------------|---------------|--|--|--|--|

| Ball Number | Ball Function | VCCIO Bank | Dual Function |  |  |  |  |

| AD5         | PR94C         | 3          |               |  |  |  |  |

| AE2         | PR94B         | 3          |               |  |  |  |  |

| AD2         | PR94A         | 3          |               |  |  |  |  |

| AC5         | PR92D         | 3          |               |  |  |  |  |

| AB5         | PR92C         | 3          |               |  |  |  |  |

| AF1         | PR92B         | 3          |               |  |  |  |  |

| AE1         | PR92A         | 3          |               |  |  |  |  |

| AA11        | PR91D         | 3          |               |  |  |  |  |

| Y11         | PR91C         | 3          |               |  |  |  |  |

| AC4         | PR91B         | 3          |               |  |  |  |  |

| AB4         | PR91A         | 3          |               |  |  |  |  |

| AA8         | PR90D         | 3          | DIFFR_3       |  |  |  |  |

| AA9         | PR90C         | 3          |               |  |  |  |  |

| AC3         | PR90B         | 3          |               |  |  |  |  |

| AB3         | PR90A         | 3          |               |  |  |  |  |

| AA7         | PR79D         | 3          |               |  |  |  |  |

| Y7          | PR79C         | 3          |               |  |  |  |  |

| AA2         | PR79B         | 3          |               |  |  |  |  |

| Y2          | PR79A         | 3          |               |  |  |  |  |

| AA6         | PR77D         | 3          |               |  |  |  |  |

| Y6          | PR77C         | 3          |               |  |  |  |  |

| Y4          | PR77B         | 3          |               |  |  |  |  |

| W4          | PR77A         | 3          |               |  |  |  |  |

| W11         | PR74D         | 3          |               |  |  |  |  |

| V11         | PR74C         | 3          |               |  |  |  |  |

| W2          | PR74B         | 3          |               |  |  |  |  |

| V2          | PR74A         | 3          |               |  |  |  |  |

| W9          | PR71D         | 3          |               |  |  |  |  |

| V9          | PR71C         | 3          |               |  |  |  |  |

| V1          | PR71B         | 3          |               |  |  |  |  |

| U1          | PR71A         | 3          |               |  |  |  |  |

| W10         | PR70D         | 3          |               |  |  |  |  |

| V10         | PR70C         | 3          |               |  |  |  |  |

| U2          | PR70B         | 3          |               |  |  |  |  |

| T2          | PR70A         | 3          |               |  |  |  |  |

| Y8          | PR69D         | 3          |               |  |  |  |  |

| W8          | PR69C         | 3          | VREF1_3       |  |  |  |  |

| W5          | PR69B         | 3          |               |  |  |  |  |

| V5          | PR69A         | 3          |               |  |  |  |  |

| V7          | PR66D         | 3          | PCLKC3_2      |  |  |  |  |

| U7          | PR66C         | 3          | PCLKT3_2      |  |  |  |  |

| T1          | PR66B         | 3          |               |  |  |  |  |

| R1          | PR66A         | 3          |               |  |  |  |  |

# LFSC/M115 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup>

|             | LFSC/M115     |            |                         |  |  |  |  |

|-------------|---------------|------------|-------------------------|--|--|--|--|

| Ball Number | Ball Function | VCCIO Bank | Dual Function           |  |  |  |  |

| J17         | PT81C         | 1          | D20/PCLKT1_2/MPI_DATA20 |  |  |  |  |

| D16         | PT81B         | 1          | MCA_CLK_P1_OUT          |  |  |  |  |

| E16         | PT81A         | 1          | MCA_CLK_P1_IN           |  |  |  |  |

| H15         | PT78D         | 1          | D21/PCLKC1_1/MPI_DATA21 |  |  |  |  |

| H16         | PT78C         | 1          | D22/PCLKT1_1/MPI_DATA22 |  |  |  |  |

| C15         | PT78B         | 1          | MCA_CLK_P2_OUT          |  |  |  |  |

| C16         | PT78A         | 1          | MCA_CLK_P2_IN           |  |  |  |  |

| L17         | PT75D         | 1          | MCA_DONE_OUT            |  |  |  |  |

| K17         | PT75C         | 1          | BUSYN/RCLK/SCK          |  |  |  |  |

| E17         | PT75B         | 1          | DP0/MPI_PAR0            |  |  |  |  |

| F17         | PT75A         | 1          | MPI_TA                  |  |  |  |  |

| G17         | PT73D         | 1          | D23/MPI_DATA23          |  |  |  |  |

| H17         | PT73C         | 1          | DP2/MPI_PAR2            |  |  |  |  |

| A17         | PT73B         | 1          | PCLKC1_0                |  |  |  |  |

| B17         | PT73A         | 1          | PCLKT1_0/MPI_CLK        |  |  |  |  |

| G18         | PT71D         | 1          | DP3/PCLKC1_4/MPI_PAR3   |  |  |  |  |

| H18         | PT71C         | 1          | D24/PCLKT1_4/MPI_DATA24 |  |  |  |  |

| E18         | PT71B         | 1          | MPI_RETRY               |  |  |  |  |

| F18         | PT71A         | 1          | A0/MPI_ADDR14           |  |  |  |  |

| J18         | PT69D         | 1          | A1/MPI_ADDR15           |  |  |  |  |

| J19         | PT69C         | 1          | A2/MPI_ADDR16           |  |  |  |  |

| C20         | PT69B         | 1          | A3/MPI_ADDR17           |  |  |  |  |

| C19         | PT69A         | 1          | A4/MPI_ADDR18           |  |  |  |  |

| K18         | PT66D         | 1          | D25/PCLKC1_5/MPI_DATA25 |  |  |  |  |

| L18         | PT66C         | 1          | D26/PCLKT1_5/MPI_DATA26 |  |  |  |  |

| D19         | PT66B         | 1          | A5/MPI_ADDR19           |  |  |  |  |

| E19         | PT66A         | 1          | A6/MPI_ADDR20           |  |  |  |  |

| H19         | PT63D         | 1          | D27/MPI_DATA27          |  |  |  |  |

| H20         | PT63C         | 1          | VREF1_1                 |  |  |  |  |

| A18         | PT63B         | 1          | A7/MPI_ADDR21           |  |  |  |  |

| B18         | PT63A         | 1          | A8/MPI_ADDR22           |  |  |  |  |

| H21         | PT61D         | 1          | D28/PCLKC1_6/MPI_DATA28 |  |  |  |  |

| J21         | PT61C         | 1          | D29/PCLKT1_6/MPI_DATA29 |  |  |  |  |

| A19         | PT61B         | 1          | A9/MPI_ADDR23           |  |  |  |  |

| B19         | PT61A         | 1          | A10/MPI_ADDR24          |  |  |  |  |

| H22         | PT58D         | 1          | D30/PCLKC1_7/MPI_DATA30 |  |  |  |  |

| J22         | PT58C         | 1          | D31/PCLKT1_7/MPI_DATA31 |  |  |  |  |

| F20         | PT58B         | 1          | A11/MPI_ADDR25          |  |  |  |  |

| G20         | PT58A         | 1          | A12/MPI_ADDR26          |  |  |  |  |

| K21         | PT57D         | 1          | D11/MPI_DATA11          |  |  |  |  |

| K22         | PT57C         | 1          | <br>D12/MPI_DATA12      |  |  |  |  |

| A20         | PT57B         | 1          |                         |  |  |  |  |

| B20         | PT57A         | 1          | A14/MPI_ADDR28          |  |  |  |  |

| Т              |                  |               | FSC/M80          |                  | LFSC/M115     |                  |  |  |

|----------------|------------------|---------------|------------------|------------------|---------------|------------------|--|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function |  |  |

| AL23           | PB56D            | 5             |                  | PB58D            | 5             |                  |  |  |

| AW24           | PB57A            | 5             |                  | PB61A            | 5             |                  |  |  |

| AW23           | PB57B            | 5             |                  | PB61B            | 5             |                  |  |  |

| AN23           | PB57C            | 5             |                  | PB61C            | 5             |                  |  |  |

| AP23           | PB57D            | 5             |                  | PB61D            | 5             |                  |  |  |

| AY23           | PB59A            | 5             |                  | PB63A            | 5             |                  |  |  |

| AY24           | PB59B            | 5             |                  | PB63B            | 5             |                  |  |  |

| AU23           | PB59C            | 5             |                  | PB63C            | 5             |                  |  |  |

| AU22           | PB59D            | 5             |                  | PB63D            | 5             |                  |  |  |

| AV23           | PB60A            | 5             |                  | PB66A            | 5             |                  |  |  |

| AV22           | PB60B            | 5             |                  | PB66B            | 5             |                  |  |  |

| AM22           | PB60C            | 5             |                  | PB66C            | 5             |                  |  |  |

| AL22           | PB60D            | 5             |                  | PB66D            | 5             |                  |  |  |

| BA23           | PB61A            | 5             |                  | PB69A            | 5             |                  |  |  |

| BA22           | PB61B            | 5             |                  | PB69B            | 5             |                  |  |  |

| AN22           | PB61C            | 5             |                  | PB69C            | 5             |                  |  |  |

| AP22           | PB61D            | 5             |                  | PB69D            | 5             |                  |  |  |

| BB23           | PB63A            | 5             |                  | PB71A            | 5             |                  |  |  |

| BB22           | PB63B            | 5             |                  | PB71B            | 5             |                  |  |  |

| AT22           | PB63C            | 5             |                  | PB71C            | 5             |                  |  |  |

| AR22           | PB63D            | 5             |                  | PB71D            | 5             |                  |  |  |

| BB21           | PB65A            | 4             |                  | PB73A            | 4             |                  |  |  |

| BB20           | PB65B            | 4             |                  | PB73B            | 4             |                  |  |  |

| AR21           | PB65C            | 4             |                  | PB73C            | 4             |                  |  |  |

| AT21           | PB65D            | 4             |                  | PB73D            | 4             |                  |  |  |

| BA21           | PB66A            | 4             |                  | PB75A            | 4             |                  |  |  |

| BA20           | PB66B            | 4             |                  | PB75B            | 4             |                  |  |  |

| AP21           | PB66C            | 4             |                  | PB75C            | 4             |                  |  |  |

| AN21           | PB66D            | 4             |                  | PB75D            | 4             |                  |  |  |

| AV21           | PB67A            | 4             |                  | PB78A            | 4             |                  |  |  |

| AV20           | PB67B            | 4             |                  | PB78B            | 4             |                  |  |  |

| AM21           | PB67C            | 4             |                  | PB78C            | 4             |                  |  |  |

| AL21           | PB67D            | 4             |                  | PB78D            | 4             |                  |  |  |

| AY20           | PB69A            | 4             |                  | PB81A            | 4             |                  |  |  |

| AY19           | PB69B            | 4             |                  | PB81B            | 4             |                  |  |  |

| AU21           | PB69C            | 4             |                  | PB81C            | 4             |                  |  |  |

| AU20           | PB69D            | 4             |                  | PB81D            | 4             |                  |  |  |

| AW20           | PB70A            | 4             |                  | PB83A            | 4             |                  |  |  |

| AW19           | PB70B            | 4             |                  | PB83B            | 4             |                  |  |  |

| AP20           | PB70C            | 4             |                  | PB83C            | 4             |                  |  |  |

| AN20           | PB70D            | 4             |                  | PB83D            | 4             |                  |  |  |

| BB19           | PB71A            | 4             |                  | PB86A            | 4             |                  |  |  |

| BB18           | PB71B            | 4             |                  | PB86B            | 4             |                  |  |  |

| AM20           | PB71C            | 4             |                  | PB86C            | 4             |                  |  |  |

| AL20           | PB71D            | 4             |                  | PB86D            | 4             |                  |  |  |

|                |                  | LFSC/M80      | LFSC/M115          |                  |               |                    |  |

|----------------|------------------|---------------|--------------------|------------------|---------------|--------------------|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function   | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function   |  |

| E37            | B_HDINN0_L       | -             | PCS 361 CH 0 IN N  | B_HDINN0_L       | -             | PCS 361 CH 0 IN N  |  |

| D37            | B_HDINP0_L       | -             | PCS 361 CH 0 IN P  | B_HDINP0_L       | -             | PCS 361 CH 0 IN P  |  |

| F34            | B_VDDIB0_L       | -             |                    | B_VDDIB0_L       | -             |                    |  |

| N29            | VCC12            | -             |                    | VCC12            | -             |                    |  |

| L30            | A_VDDIB3_L       | -             |                    | A_VDDIB3_L       | -             |                    |  |

| K31            | VCC12            | -             |                    | VCC12            | -             |                    |  |

| D38            | A_HDINP3_L       | -             | PCS 360 CH 3 IN P  | A_HDINP3_L       | -             | PCS 360 CH 3 IN P  |  |

| E38            | A_HDINN3_L       | -             | PCS 360 CH 3 IN N  | A_HDINN3_L       | -             | PCS 360 CH 3 IN N  |  |

| A37            | A_HDOUTP3_L      | -             | PCS 360 CH 3 OUT P | A_HDOUTP3_L      | -             | PCS 360 CH 3 OUT P |  |

| G37            | VCC12            | -             |                    | VCC12            | -             |                    |  |

| B37            | A_HDOUTN3_L      | -             | PCS 360 CH 3 OUT N | A_HDOUTN3_L      | -             | PCS 360 CH 3 OUT N |  |

| L33            | A_VDDOB3_L       | -             |                    | A_VDDOB3_L       | -             |                    |  |

| B38            | A_HDOUTN2_L      | -             | PCS 360 CH 2 OUT N | A_HDOUTN2_L      | -             | PCS 360 CH 2 OUT N |  |

| D41            | A_VDDOB2_L       | -             |                    | A_VDDOB2_L       | -             |                    |  |

| A38            | A_HDOUTP2_L      | -             | PCS 360 CH 2 OUT P | A_HDOUTP2_L      | -             | PCS 360 CH 2 OUT P |  |

| K34            | VCC12            | -             |                    | VCC12            | -             |                    |  |

| E39            | A_HDINN2_L       | -             | PCS 360 CH 2 IN N  | A_HDINN2_L       | -             | PCS 360 CH 2 IN N  |  |

| D39            | A_HDINP2_L       | -             | PCS 360 CH 2 IN P  | A_HDINP2_L       | -             | PCS 360 CH 2 IN P  |  |

| M32            | A_VDDIB2_L       | -             |                    | A_VDDIB2_L       | -             |                    |  |

| J32            | VCC12            | -             |                    | VCC12            | -             |                    |  |

| E41            | A_VDDIB1_L       | -             |                    | A_VDDIB1_L       | -             |                    |  |

| M33            | VCC12            | -             |                    | VCC12            | -             |                    |  |

| D40            | A_HDINP1_L       | -             | PCS 360 CH 1 IN P  | A_HDINP1_L       | -             | PCS 360 CH 1 IN P  |  |

| E40            | A_HDINN1_L       | -             | PCS 360 CH 1 IN N  | A_HDINN1_L       | -             | PCS 360 CH 1 IN N  |  |

| B39            | A_HDOUTP1_L      | -             | PCS 360 CH 1 OUT P | A_HDOUTP1_L      | -             | PCS 360 CH 1 OUT P |  |

| B41            | VCC12            | -             |                    | VCC12            | -             |                    |  |

| A39            | A_HDOUTN1_L      | -             | PCS 360 CH 1 OUT N | A_HDOUTN1_L      | -             | PCS 360 CH 1 OUT N |  |

| C41            | A_VDDOB1_L       | -             |                    | A_VDDOB1_L       | -             |                    |  |

| B40            | A_HDOUTN0_L      | -             | PCS 360 CH 0 OUT N | A_HDOUTN0_L      | -             | PCS 360 CH 0 OUT N |  |

| E42            | A_VDDOB0_L       | -             |                    | A_VDDOB0_L       | -             |                    |  |

| A40            | A_HDOUTP0_L      | -             | PCS 360 CH 0 OUT P | A_HDOUTP0_L      | -             | PCS 360 CH 0 OUT P |  |

| F42            | VCC12            | -             |                    | VCC12            | -             |                    |  |

| D42            | A_HDINN0_L       | -             | PCS 360 CH 0 IN N  | A_HDINN0_L       | -             | PCS 360 CH 0 IN N  |  |

| C42            | A_HDINP0_L       | -             | PCS 360 CH 0 IN P  | A_HDINP0_L       | -             | PCS 360 CH 0 IN P  |  |

| H39            | A_VDDIB0_L       | -             |                    | A_VDDIB0_L       | -             |                    |  |

| F41            | VCC12            | -             |                    | VCC12            | -             |                    |  |

| P16            | VDDAX25_R        | -             |                    | VDDAX25_R        | -             |                    |  |

| P27            | VDDAX25_L        | -             |                    | VDDAX25_L        | -             |                    |  |

| K39            | NC               | -             |                    | PL32A            | 7             |                    |  |

| L39            | NC               | -             |                    | PL32B            | 7             |                    |  |

| M38            | NC               | -             |                    | PL35A            | 7             |                    |  |

| K40            | NC               | -             |                    | PL36A            | 7             |                    |  |

| L40            | NC               | -             |                    | PL36B            | 7             |                    |  |

| N37            | NC               | -             |                    | PL39A            | 7             |                    |  |

| P37            | NC               | -             |                    | PL39B            | 7             |                    |  |

| Γ              |                  | LFSC          |                  |                  | LFSC/M115     |                  |  |  |

|----------------|------------------|---------------|------------------|------------------|---------------|------------------|--|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function |  |  |

| C3             | GND              | -             |                  | GND              | -             |                  |  |  |

| C30            | GND              | -             |                  | GND              | -             |                  |  |  |

| C33            | GND              | -             |                  | GND              | -             |                  |  |  |

| C35            | GND              | -             |                  | GND              | -             |                  |  |  |

| C36            | GND              | -             |                  | GND              | -             |                  |  |  |

| C39            | GND              | -             |                  | GND              | -             |                  |  |  |

| C4             | GND              | -             |                  | GND              | -             |                  |  |  |

| C40            | GND              | -             |                  | GND              | -             |                  |  |  |

| C7             | GND              | -             |                  | GND              | -             |                  |  |  |

| C8             | GND              | -             |                  | GND              | -             |                  |  |  |

| D15            | GND              | -             |                  | GND              | -             |                  |  |  |

| D21            | GND              | -             |                  | GND              | -             |                  |  |  |

| D25            | GND              | -             |                  | GND              | -             |                  |  |  |

| D31            | GND              | -             |                  | GND              | -             |                  |  |  |

| F4             | GND              | -             |                  | GND              | -             |                  |  |  |

| F40            | GND              | -             |                  | GND              | -             |                  |  |  |

| G11            | GND              | -             |                  | GND              | -             |                  |  |  |

| G17            | GND              | -             |                  | GND              | -             |                  |  |  |

| G26            | GND              | -             |                  | GND              | -             |                  |  |  |

| G32            | GND              | -             |                  | GND              | -             |                  |  |  |

| H14            | GND              | -             |                  | GND              | -             |                  |  |  |

| H20            | GND              | -             |                  | GND              | -             |                  |  |  |

| H23            | GND              | -             |                  | GND              |               |                  |  |  |

| H29            | GND              | -             |                  | GND              | -             |                  |  |  |

| H35            | GND              | -             |                  | GND              | -             |                  |  |  |

| H8             | GND              | -             |                  | GND              | -             |                  |  |  |

| J3             | GND              | -             |                  | GND              | -             |                  |  |  |

| J39            | GND              | -             |                  | GND              | -             |                  |  |  |

| L16            | GND              | -             |                  | GND              | -             |                  |  |  |

| L27            | GND              | -             |                  | GND              | -             |                  |  |  |

| L36            | GND              | -             |                  | GND              | -             |                  |  |  |

| L7             | GND              | -             |                  | GND              |               |                  |  |  |

| M19            | GND              | -             |                  | GND              | -             |                  |  |  |

| M24            | GND              | -             |                  | GND              | -             |                  |  |  |

| M4             | GND              | -             |                  | GND              | -             |                  |  |  |

| M40            | GND              | -             |                  | GND              | -             |                  |  |  |

| N12            | GND              | -             |                  | GND              | -             |                  |  |  |

| N31            | GND              | -             |                  | GND              | -             |                  |  |  |

| P35            | GND              | -             |                  | GND              | -             |                  |  |  |