# E · / Fattice Semiconductor Corporation - <u>LFSC3GA40E-7FFN1152C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                        |

|--------------------------------|---------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 10000                                                                           |

| Number of Logic Elements/Cells | 40000                                                                           |

| Total RAM Bits                 | 4075520                                                                         |

| Number of I/O                  | 604                                                                             |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 0.95V ~ 1.26V                                                                   |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                 |

| Package / Case                 | 1152-BBGA                                                                       |

| Supplier Device Package        | 1152-FPBGA (35x35)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfsc3ga40e-7ffn1152c |

|                                |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **PFU Modes of Operation**

Slices can be combined within a PFU to form larger functions. Table 2-4 tabulates these modes and documents the functionality possible at the PFU level.

#### Table 2-4. PFU Modes of Operation

| Logic                      | Ripple            | RAM                          | ROM          |

|----------------------------|-------------------|------------------------------|--------------|

| LUT 4x8 or<br>MUX 2x1 x 8  | 2-bit Add x 4     | SPR 16x2 x 4<br>DPR 16x2 x 2 | ROM 16x1 x 8 |

| LUT 5x4 or<br>MUX 4x1 x 4  | 2-bit Sub x 4     | SPR 16x4 x 2<br>DPR 16x4 x 1 | ROM 16x2 x 4 |

| LUT 6x2 or<br>MUX 8x1 x 2  | 2-bit Counter x 4 | SPR 16x8 x 1                 | ROM 16x4 x 2 |

| LUT 7x1 or<br>MUX 16x1 x 1 | 2-bit Comp x 4    |                              | ROM 16x8 x1  |

### Routing

There are many resources provided in the LatticeSC devices to route signals individually or as busses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with x1 (spans two PFU), x2 (spans three PFU) and x6 (spans seven PFU) resources. The x1 and x2 connections provide fast and efficient connections in horizontal, vertical and diagonal directions. All connections are buffered to ensure high-speed operation even with long high-fanout connections.

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

### sysCLOCK Network

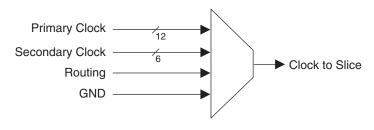

The LatticeSC devices have three distinct clock networks for use in distributing high-performance clocks within the device: primary clocks, secondary clocks and edge clocks. In addition to these dedicated clock networks, users are free to route clocks within the device using the general purpose routing. Figure 2-4 shows the clock resources available to each slice.

#### Figure 2-4. Slice Clock Selection

Note: GND is available to switch off the network.

### **Primary Clock Sources**

LatticeSC devices have a wide variety of primary clock sources available. Primary clocks sources consists of the following:

- Primary clock input pins

- Edge clock input pins

- Two outputs per DLL

### Lattice Semiconductor

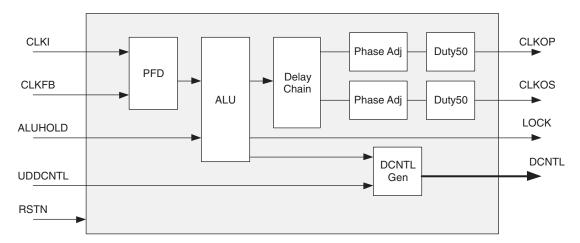

There is a Digital Control (DCNTL) bus available from the DLL block. This Digital Control bus is available to the delay lines in the PIC blocks in the adjacent banks. The UDDCNTL signal allows the user to latch the current value on the digital control bus.

Figure 2-12 shows the DLL block diagram of the DLL inputs and outputs. The output of the phase frequency detector controls an arithmetic logic unit (ALU) to add or subtract one delay tap. The digital output of this ALU is used to control the delay value of the delay chain and this digital code is transmitted via the DCNTL bus.

The sysCLOCK DLL can be configured at power-up, then, if desired, reconfigured dynamically through the Serial Memory Interface bus which interfaces with the on-chip Microprocessor Interface (MPI) bus. In addition, users can drive the SMI interface from routing if desired.

The user can configure the DLL for many common functions such as clock injection match and single delay cell. Lattice provides primitives in its design for time reference delay (DDR memory) and clock injection delay removal.

Figure 2-12. DLL Diagram

### PLL/DLL Cascading

The LatticeSC devices have been designed to allow certain combinations of PLL and DLL cascading. The allowable combinations are as follows:

- PLL to PLL

- PLL to DLL

- DLL to DLL

- DLL to PLL

DLLs are used to shift the clock in relation to the data for source synchronous inputs. PLLs are used for frequency synthesis and clock generation for source synchronous interfaces. Cascading PLL and DLL blocks allows applications to utilize the unique benefits of both DLL and PLLs.

When cascading the DLL to the PLL, the DLL can be used to drive the PLL to create fine phase shifts of an input clock signal. Figure 2-13 shows a shift of all outputs for CLKOP and CLKOS out in time.

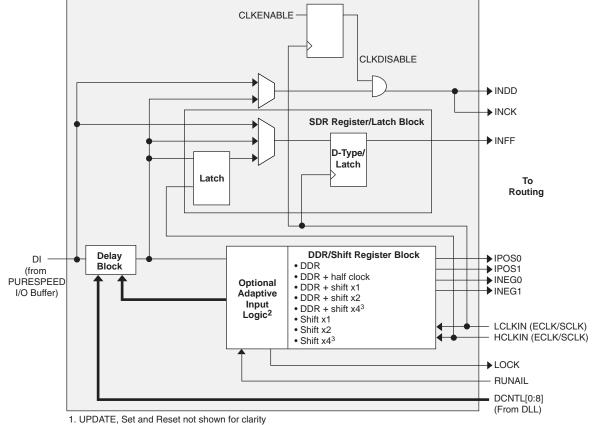

#### Figure 2-20. Input Register Block<sup>1</sup>

Adaptive input logic is only available in selected PIO

3. By four shift modes utilize DDR/shift register block from paired PIO.

4. CLKDISABLE is used to block the transitions on the DQS pin during post-amble. Its main use is to disable DQS (typically found in DDR memory interfaces) or other clock signals. It can also be used to disable any/all input signals to save power.

this allows for easy integration with the rest of the system. These capabilities make the LatticeSC ideal for many multiple power supply and hot-swap applications. The maximum current during hot socketing is 4mA. See Hot Socketing Specifications in Chapter 3 of this data sheet.

### **Power-Up Requirements**

To prevent high power supply and input pin currents, each VCC, VCC12, VCCAUX, VCCIO and VCCJ power supplies must have a monotonic ramp up time of 75 ms or less to reach its minimum operating voltage. Apart from VCC and VCC12, which have an additional requirement, and VCCIO and VCCAUX, which also have an additional requirement, the VCC, VCC12, VCCAUX, VCCIO and VCCJ power supplies can ramp up in any order, with no restriction on the time between them. However, the ramp time for each must be 75 ms or less. Configuration of the device will not proceed until the last power supply has reached its minimum operating voltage.

#### Additional Requirement for VCC and VCC12:

VCC12 must always be higher than VCC. This condition must be maintained at ALL times, including during powerup and power-down. Note that for 1.2V only operation, it is advisable to source both of these supplies from the same power supply.

#### Additional Requirement for VCCIO and VCCAUX:

If any VCCIOs are 1.2/1.5/1.8V, then VCCAUX MUST be applied before them. If any VCCIO is 1.2/1.5/1.8V and is powered up before VCCAUX, then when VCCAUX is powered up, it may drag VCCIO up with it as it crosses through the VCCIO value. (Note: If the VCCIO supply is capable of sinking current, as well as the more usual sourcing capability, this behavior is eliminated. However, the amount of current that the supply needs to sink is unknown and is likely to be in the hundreds of milliamps range).

### **Power-Down Requirements**

To prevent high power supply and input pin currents, power must be removed monotonically from either VCC or VCCAUX (and must reach the power-down trip point of 0.5V for VCC, 0.95V for VCCAUX) before power is removed monotonically from VCC12, any of the VCCIOs, or VCCJ. Note that VCC12 can be removed at the same time as VCC, but it cannot be removed earlier. In many applications, VCC and VCC12 will be sourced from the same power supply and so will be removed together. For systems where disturbance of the user pins is a don't care condition, the power supplies can be removed in any order as long as they power down monotonically within 200ms of each other.

Additionally, if any banks have VCCIO=3.3V nominal (potentially banks 1, 4, 5) then VCCIO for those banks must not be lower than VCCAUX during power-down. The normal variation in ramp-up times of power supplies and voltage regulators is not a concern here.

Note: The SERDES power supplies are NOT included in these requirements and have no specific sequencing requirements. However, when using the SERDES with VDDIB or VDDOB that is greater than 1.2V (1.5V nominal for example), the SERDES should not be left in a steady state condition with the 1.5V power applied and the 1.2V power not applied. Both the 1.2V and 1.5V power should be applied to the SERDES at nominally the same time. The normal variation in the ramp-up times of power supplies and voltage regulators is not a concern here.

### **SERDES Power Supply Sequencing Requirements**

When using the SERDES with 1.5V VDDIB or VDDOB supplies, the SERDES should not be left in a steady state condition with the 1.5V power applied and the 1.2V power not applied. Both the 1.2V and the 1.5V power should be applied to the SERDES at nominally the same time. The normal variation in ramp-up times of power supples and voltage regulators is not a concern.

### Additional Requirement for SERDES Power Supply

All VCC12 pins need to be connected on all devices independent of functionality used on the device. This analog supply is used by both the RX and TX portions of the SERDES and is used to control the core SERDES logic regardless of the SERDES being used in the design. VDDIB and VDDOB are used as supplies for the terminations on the CML input and output buffers. If a particular channel is not used, these can be UNCONNECTED (floating).

VDDAX25 needs to be connected independent of the use of the SERDES. This supply is used to control the SERDES CML I/O regardless of the SERDES being used in the design.

#### Supported Source Synchronous Interfaces

The LatticeSC devices contain a variety of hardware, such as delay elements, DDR registers and PLLs, to simplify the implementation of Source Synchronous interfaces. Table 2-11 lists Source Synchronous and DDR/QDR standards supported in the LatticeSC. For additional detail refer to technical information at the end of the data sheet.

Source Synchronous Standard Clocking Speeds (MHz) Data Rate (Mbps) RapidIO DDR 500 1000 SPI4.2 (POS-PHY4)/NPSI DDR 1000 500 DDR 334 667 SFI4/XSBI SDR 667 DDR XGMII 156.25 312 CSIX SDR 250 250 QDRII/QDRII+ memory interface DDR 300 600 DDR memory interface DDR 240 480 DDR 333 667 DDRII memory interface DDR 400 800 **RLDRAM** memory interface

#### Table 2-11. Source Synchronous Standards Table<sup>1</sup>

1. Memory width is dependent on the system design and limited by the number of I/Os in the device.

### flexiPCS<sup>™</sup> (Physical Coding Sublayer Block)

#### flexiPCS Functionality

The LatticeSC family combines a high-performance FPGA fabric, high-performance I/Os and large embedded RAM in a single industry leading architecture. LatticeSC devices also feature up to 32 channels of embedded SERDES with associated Physical Coding Sublayer (PCS) logic. The flexiPCS logic can be configured to support numerous industry standard high-speed data transfer protocols.

Each channel of flexiPCS logic contains dedicated transmit and receive SERDES for high-speed, full-duplex serial data transfers at data rates up to 3.8 Gbps. The PCS logic in each channel can be configured to support an array of popular data protocols including SONET (STS-12/STS-12c, STS-48/STS-48c, and TFI-5 support of 10 Gbps or above), Gigabit Ethernet (compliant to the IEEE 1000BASE-X specification), 1.02 or 2.04 Gbps Fibre Channel, PCI-Express, and Serial RapidIO. In addition, the protocol based logic can be fully or partially bypassed in a number of configurations to allow users flexibility in designing their own high-speed data interface.

Protocols requiring data rates above 3.8 Gbps can be accommodated by dedicating either one pair or all four channels in one flexiPCS quad block to one data link. One quad can support full-duplex serial data transfers at data rates up to 15.2 Gbps. A single flexiPCS quad can be configured to support 10Gb Ethernet (with a fully compliant XAUI interface), 10Gb Fibre Channel, and x4 PCI-Express and 4x RapidIO.

The flexiPCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic which can also be geared to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic. Each SERDES pin can be DC coupled independently and can allow for both high-speed and low-speed operation down to DC rates on the same SERDES pin, as required by some Serial Digital Video applications.

The ispLEVER design tools from Lattice support all modes of the flexiPCS. Most modes are dedicated to applications associated with a specific industry standard data protocol. Other more general purpose modes allow a user to define their own operation. With ispLEVER, the user can define the mode for each quad in a design. Nine modes are currently supported by the ispLEVER design flow:

### **Switching Characteristics**

All devices are 100% functionally tested. Listed below are representative values of internal and external timing parameters. For more specific, more precise, and worst-case guaranteed data at a particular temperature and volt-age, use the values reported by the static timing analyzer in the ispLEVER design tool from Lattice and back-annotate to the simulation net list.

### LatticeSC/M Family Timing Adders (Continued)

|                  |                               | -      | 7      | -      | 6      | -      | 5      |       |

|------------------|-------------------------------|--------|--------|--------|--------|--------|--------|-------|

| Buffer Type      | Description                   | Min.   | Max.   | Min.   | Max.   | Min.   | Max.   | Units |

| GTLPLUS15        | GTLPLUS15                     | -0.013 | -0.017 | 0.012  | 0.004  | 0.037  | 0.024  | ns    |

| GTL12            | GTL12                         | -0.063 | -0.071 | -0.007 | -0.048 | 0.056  | -0.032 | ns    |

| Output Adjusters |                               |        |        |        |        |        |        |       |

| LVDS             | LVDS                          | 0.708  | 0.854  | 0.856  | 1.021  | 1.005  | 1.189  | ns    |

| RSDS             | RSDS                          | 0.708  | 0.854  | 0.856  | 1.021  | 1.005  | 1.189  | ns    |

| BLVDS25          | BLVDS                         | -0.129 | 0.05   | -0.136 | 0.069  | -0.136 | 0.083  | ns    |

| MLVDS25          | MLVDS                         | -0.059 | 0.059  | -0.057 | 0.096  | -0.054 | 0.133  | ns    |

| LVPECL33         | LVPECL                        | -0.334 | -0.181 | -0.325 | -1.389 | -0.315 | -2.598 | ns    |

| HSTL18_I         | HSTL_18 class I               | 0.132  | 0.209  | 0.153  | 0.24   | 0.175  | 0.272  | ns    |

| HSTL18_II        | HSTL_18 class II              | 0.24   | 0.176  | 0.268  | 0.255  | 0.298  | 0.333  | ns    |

| HSTL18D_I        | Differential HSTL 18 class I  | 0.132  | 0.209  | 0.153  | 0.24   | 0.175  | 0.272  | ns    |

| HSTL18D_II       | Differential HSTL 18 class II | 0.24   | 0.176  | 0.268  | 0.255  | 0.298  | 0.333  | ns    |

| HSTL15_I         | HSTL_15 class I               | 0.096  | 0.172  | 0.112  | 0.198  | 0.129  | 0.224  | ns    |

| HSTL15_II        | HSTL_15 class II              | 0.208  | 0.131  | 0.233  | 0.203  | 0.259  | 0.275  | ns    |

| HSTL15D_I        | Differential HSTL 15 class I  | 0.096  | 0.172  | 0.112  | 0.198  | 0.129  | 0.224  | ns    |

| HSTL15D_II       | Differential HSTL 15 class II | 0.208  | 0.131  | 0.233  | 0.203  | 0.259  | 0.275  | ns    |

| SSTL33_I         | SSTL_3 class I                | 0.133  | 0.177  | 0.11   | 0.166  | 0.088  | 0.154  | ns    |

| SSTL33_II        | SSTL_3 class II               | 0.173  | 0.247  | 0.164  | 0.253  | 0.156  | 0.258  | ns    |

| SSTL33D_I        | Differential SSTL_3 class I   | 0.133  | 0.177  | 0.11   | 0.166  | 0.088  | 0.154  | ns    |

| SSTL33D_II       | Differential SSTL_3 class II  | 0.173  | 0.247  | 0.164  | 0.253  | 0.156  | 0.258  | ns    |

| SSTL25_I         | SSTL_2 class I                | 0.215  | 0.125  | 0.239  | 0.228  | 0.264  | 0.331  | ns    |

| SSTL25_II        | SSTL_2 class II               | 0.277  | 0.181  | 0.311  | 0.284  | 0.345  | 0.387  | ns    |

| SSTL25D_I        | Differential SSTL_2 class I   | 0.215  | 0.125  | 0.239  | 0.228  | 0.264  | 0.331  | ns    |

| SSTL25D_II       | Differential SSTL_2 class II  | 0.277  | 0.181  | 0.311  | 0.284  | 0.345  | 0.387  | ns    |

| SSTL18_I         | SSTL_2 class I                | 0.16   | 0.081  | 0.179  | 0.173  | 0.199  | 0.265  | ns    |

| SSTL18_II        | SSTL_2 class II               | 0.238  | 0.15   | 0.263  | 0.244  | 0.295  | 0.338  | ns    |

| SSTL18D_I        | Differential SSTL_2 class I   | 0.16   | 0.081  | 0.179  | 0.173  | 0.199  | 0.265  | ns    |

| SSTL18D_II       | Differential SSTL_2 class II  | 0.238  | 0.15   | 0.263  | 0.244  | 0.295  | 0.338  | ns    |

| LVTTL33_8mA      | LVTTL 8mA drive               | -0.346 | -0.165 | -0.496 | -0.296 | -0.646 | -0.428 | ns    |

| LVTTL33_16mA     | LVTTL 16mA drive              | -0.11  | -0.18  | -0.218 | -0.32  | -0.325 | -0.46  | ns    |

| LVTTL33_24mA     | LVTTL 24mA drive              | -0.012 | -0.18  | -0.099 | -0.321 | -0.185 | -0.463 | ns    |

| LVCMOS33_8mA     | LVCMOS 3.3 8mA drive          | -0.346 | -0.165 | -0.496 | -0.296 | -0.646 | -0.428 | ns    |

| LVCMOS33_16mA    | LVCMOS 3.3 16mA drive         | -0.11  | -0.18  | -0.218 | -0.32  | -0.325 | -0.46  | ns    |

| LVCMOS33_24mA    | LVCMOS 3.3 24mA drive         | -0.012 | -0.18  | -0.099 | -0.321 | -0.185 | -0.463 | ns    |

| LVCMOS25_4mA     | LVCMOS 2.5 4mA drive          | -0.174 | 0.004  | -0.195 | 0.002  | -0.215 | 0      | ns    |

| LVCMOS25_8mA     | LVCMOS 2.5 8mA drive          | 0      | 0      | 0      | 0      | 0      | 0      | ns    |

| LVCMOS25_12mA    | LVCMOS 2.5 12mA drive         | 0.094  | -0.025 | 0.107  | 0.096  | 0.12   | 0.216  | ns    |

| LVCMOS25_16mA    | LVCMOS 2.5 16mA drive         | 0.145  | -0.054 | 0.162  | 0.063  | 0.181  | 0.179  | ns    |

| LVCMOS25_OD      | LVCMOS 2.5 open drain         | 0.073  | -0.125 | 0.081  | -0.081 | 0.091  | -0.09  | ns    |

| LVCMOS18_4mA     | LVCMOS 1.8 4mA drive          | -0.278 | -0.099 | -0.312 | -0.115 | -0.345 | -0.131 | ns    |

| LVCMOS18_8mA     | LVCMOS 1.8 8mA drive          | -0.073 | -0.078 | -0.078 | -0.084 | -0.083 | -0.089 | ns    |

### Over Recommended Operating Conditions at VCC = 1.2V +/- 5%

### LatticeSC/M Family Timing Adders (Continued)

|               |                       | -      | 7      | -      | 6      | -      | 5      |       |

|---------------|-----------------------|--------|--------|--------|--------|--------|--------|-------|

| Buffer Type   | Description           | Min.   | Max.   | Min.   | Max.   | Min.   | Max.   | Units |

| LVCMOS18_12mA | LVCMOS 1.8 12mA drive | 0.024  | -0.106 | 0.019  | -0.004 | 0.016  | 0.099  | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16mA drive | 0.074  | -0.134 | 0.08   | -0.022 | 0.088  | 0.089  | ns    |

| LVCMOS18_OD   | LVCMOS 1.8 open drain | 0.002  | -0.206 | 0      | -0.196 | -0.002 | -0.221 | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive  | -0.344 | -0.164 | -0.379 | -0.186 | -0.412 | -0.209 | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive  | -0.125 | -0.137 | -0.145 | -0.157 | -0.164 | -0.176 | ns    |

| LVCMOS15_12mA | LVCMOS 1.5 12mA drive | -0.027 | -0.166 | -0.043 | -0.07  | -0.059 | 0.026  | ns    |

| LVCMOS15_16mA | LVCMOS 1.5 16mA drive | 0.025  | -0.195 | 0.013  | -0.089 | 0.003  | 0.017  | ns    |

| LVCMOS15_OD   | LVCMOS 1.5 open drain | -0.047 | -0.267 | -0.067 | -0.267 | -0.087 | -0.299 | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive  | -0.473 | -0.293 | -0.505 | -0.317 | -0.537 | -0.34  | ns    |

| LVCMOS12_4mA  | LVCMOS 1.2 4mA drive  | -0.218 | -0.239 | -0.25  | -0.271 | -0.28  | -0.303 | ns    |

| LVCMOS12_8mA  | LVCMOS 1.2 8mA drive  | -0.109 | -0.269 | -0.143 | -0.181 | -0.176 | -0.093 | ns    |

| LVCMOS12_12mA | LVCMOS 1.2 12mA drive | -0.054 | -0.3   | -0.085 | -0.203 | -0.114 | -0.106 | ns    |

| LVCMOS12_OD   | LVCMOS 1.2 open drain | -0.126 | -0.371 | -0.166 | -0.398 | -0.204 | -0.43  | ns    |

| PCI33         | PCI                   | -0.216 | -0.791 | -0.417 | -1.263 | -0.618 | -1.735 | ns    |

| PCIX33        | PCI-X 3.3             | -0.216 | -0.791 | -0.417 | -1.263 | -0.618 | -1.735 | ns    |

| PCIX15        | PCI-X 1.5             | 0.208  | 0.227  | 0.233  | 0.312  | 0.259  | 0.398  | ns    |

| AGP1X33       | AGP-1X 3.3            | -0.216 | -0.791 | -0.417 | -1.263 | -0.618 | -1.735 | ns    |

| AGP2X33       | AGP-2X                | -0.216 | -0.791 | -0.417 | -1.263 | -0.618 | -1.735 | ns    |

#### Over Recommended Operating Conditions at VCC = 1.2V +/- 5%

### LFSC/M15 Logic Signal Connections: 256 fpBGA<sup>1,2</sup> (Cont.)

|             | LFSC/M15      |            |               |  |  |  |  |

|-------------|---------------|------------|---------------|--|--|--|--|

| Ball Number | Ball Function | VCCIO Bank | Dual Function |  |  |  |  |

| J9          | VCC           | -          |               |  |  |  |  |

| K8          | VCC           | -          |               |  |  |  |  |

| F6          | VCC12         | -          |               |  |  |  |  |

| F11         | VCC12         | -          |               |  |  |  |  |

| L11         | VCC12         | -          |               |  |  |  |  |

| L6          | VCC12         | -          |               |  |  |  |  |

| K7          | VCC12         | -          |               |  |  |  |  |

| K10         | VCC12         | -          |               |  |  |  |  |

| F10         | VCCAUX        | -          |               |  |  |  |  |

| F7          | VCCAUX        | -          |               |  |  |  |  |

| T1          | GND           | -          |               |  |  |  |  |

| G11         | VCCAUX        | -          |               |  |  |  |  |

| K11         | VCCAUX        | -          |               |  |  |  |  |

| L10         | VCCAUX        | -          |               |  |  |  |  |

| L9          | VCCAUX        | -          |               |  |  |  |  |

| L7          | VCCAUX        | -          |               |  |  |  |  |

| L8          | VCCAUX        | -          |               |  |  |  |  |

| T16         | GND           | -          |               |  |  |  |  |

| G6          | VCCAUX        | -          |               |  |  |  |  |

| K6          | VCCAUX        | -          |               |  |  |  |  |

| B13         | VCCIO1        | -          |               |  |  |  |  |

| D11         | VCCIO1        | -          |               |  |  |  |  |

| D14         | VCCIO1        | -          |               |  |  |  |  |

| F12         | VCCIO2        | -          |               |  |  |  |  |

| G15         | VCCIO2        | -          |               |  |  |  |  |

| K14         | VCCIO3        | -          |               |  |  |  |  |

| N15         | VCCIO3        | -          |               |  |  |  |  |

| M11         | VCCIO4        | -          |               |  |  |  |  |

| P13         | VCCIO4        | -          |               |  |  |  |  |

| R10         | VCCIO4        | -          |               |  |  |  |  |

| N6          | VCCIO5        | -          |               |  |  |  |  |

| P7          | VCCIO5        | -          |               |  |  |  |  |

| R4          | VCCIO5        | -          |               |  |  |  |  |

| K2          | VCCIO6        | -          |               |  |  |  |  |

| N3          | VCCIO6        | -          |               |  |  |  |  |

| F4          | VCCIO7        | -          |               |  |  |  |  |

| G3          | VCCI07        | -          |               |  |  |  |  |

| D4          | VCC12         | -          |               |  |  |  |  |

| D7          | VCC12         | -          |               |  |  |  |  |

| D5          | VCC12         | -          |               |  |  |  |  |

| D6          | VCC12         | -          |               |  |  |  |  |

1. Differential pair grouping within a PIC is A (True) and B (Complement) and C (True) and D (Complement).

2. The LatticeSC/M15 in a 256-pin package does not support an MPI interface.

# LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup> (Cont.)

|                |               |               | C/M15         |               | LFSC/M25      |               |  |  |

|----------------|---------------|---------------|---------------|---------------|---------------|---------------|--|--|

| Ball<br>Number | Ball Function | VCCIO<br>Bank | Dual Function | Ball Function | VCCIO<br>Bank | Dual Function |  |  |

| AB10           | VCC           | -             |               | VCC           | -             |               |  |  |

| AB21           | VCC           | -             |               | VCC           | -             |               |  |  |

| J10            | VCC           | -             |               | VCC           | -             |               |  |  |

| J21            | VCC           | -             |               | VCC           | -             |               |  |  |

| K10            | VCC           | -             |               | VCC           | -             |               |  |  |

| K11            | VCC           | -             |               | VCC           | -             |               |  |  |

| K12            | VCC           | -             |               | VCC           | -             |               |  |  |

| K13            | VCC           | -             |               | VCC           | -             |               |  |  |

| K14            | VCC           | -             |               | VCC           | -             |               |  |  |

| K17            | VCC           | -             |               | VCC           | -             |               |  |  |

| K18            | VCC           | -             |               | VCC           | -             |               |  |  |

| K19            | VCC           | -             |               | VCC           | -             |               |  |  |

| K20            | VCC           | -             |               | VCC           | -             |               |  |  |

| K21            | VCC           | -             |               | VCC           | -             |               |  |  |

| K22            | VCC           | -             |               | VCC           | -             |               |  |  |

| K9             | VCC           | -             |               | VCC           | -             |               |  |  |

| L10            | VCC           | -             |               | VCC           | -             |               |  |  |

| L21            | VCC           | -             |               | VCC           | -             |               |  |  |

| M10            | VCC           | -             |               | VCC           | -             |               |  |  |

| M21            | VCC           | -             |               | VCC           | -             |               |  |  |

| N10            | VCC           | -             |               | VCC           | -             |               |  |  |

| N21            | VCC           | -             |               | VCC           | -             |               |  |  |

| P10            | VCC           | -             |               | VCC           | -             |               |  |  |

| P21            | VCC           | -             |               | VCC           | -             |               |  |  |

| U10            | VCC           | -             |               | VCC           | -             |               |  |  |

| U21            | VCC           | -             |               | VCC           | -             |               |  |  |

| V10            | VCC           | -             |               | VCC           | -             |               |  |  |

| V21            | VCC           | -             |               | VCC           | -             |               |  |  |

| W10            | VCC           | -             |               | VCC           | -             |               |  |  |

| W21            | VCC           | -             |               | VCC           | -             |               |  |  |

| Y10            | VCC           | -             |               | VCC           | -             |               |  |  |

| Y21            | VCC           | -             |               | VCC           | -             |               |  |  |

| H11            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| H12            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| H19            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| H20            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| M23            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| M24            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| N23            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| N24            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| U23            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| U24            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| V23            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| V24            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

| W23            | VCCAUX        | -             |               | VCCAUX        | -             |               |  |  |

# LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup> (Cont.)

|                | LFSC/M15      |               |               |               | LFSC/M25      |               |  |  |

|----------------|---------------|---------------|---------------|---------------|---------------|---------------|--|--|

| Ball<br>Number | Ball Function | VCCIO<br>Bank | Dual Function | Ball Function | VCCIO<br>Bank | Dual Function |  |  |

| AG11           | VCCIO5        | -             |               | VCCIO5        | -             |               |  |  |

| AJ9            | VCCIO5        | -             |               | VCCIO5        | -             |               |  |  |

| AJ23           | VCCIO4        | -             |               | VCCIO4        | -             |               |  |  |

| AG20           | VCCIO4        | -             |               | VCCIO4        | -             |               |  |  |

| AJ26           | VCCIO4        | -             |               | VCCIO4        | -             |               |  |  |

| AG23           | VCCIO4        | -             |               | VCCIO4        | -             |               |  |  |

| AC29           | VCCIO3        | -             |               | VCCIO3        | -             |               |  |  |

| AA26           | VCCIO3        | -             |               | VCCIO3        | -             |               |  |  |

| Y28            | VCCIO3        | -             |               | VCCIO3        | -             |               |  |  |

| AA29           | VCCIO3        | -             |               | VCCIO3        | -             |               |  |  |

| G30            | VCCIO2        | -             |               | VCCIO2        | -             |               |  |  |

| J29            | VCCIO2        | -             |               | VCCIO2        | -             |               |  |  |

| K27            | VCCIO2        | -             |               | VCCIO2        | -             |               |  |  |

| N25            | VCCIO2        | -             |               | VCCIO2        | -             |               |  |  |

| F20            | VCCIO1        | -             |               | VCCIO1        | -             |               |  |  |

| C19            | VCCIO1        | -             |               | VCCIO1        | -             |               |  |  |

| C12            | VCCIO1        | -             |               | VCCIO1        | -             |               |  |  |

| F11            | VCCIO1        | -             |               | VCCIO1        | -             |               |  |  |

| H1             | GND           | -             |               | GND           | -             |               |  |  |

| L4             | GND           | -             |               | GND           | -             |               |  |  |

| M3             | GND           | -             |               | GND           | -             |               |  |  |

| N5             | GND           | -             |               | GND           | -             |               |  |  |

| K2             | GND           | -             |               | GND           | -             |               |  |  |

| M2             | GND           | -             |               | GND           | -             |               |  |  |

| P6             | GND           | -             |               | GND           | -             |               |  |  |

| G4             | GND           | -             |               | GND           | -             |               |  |  |

| H3             | GND           | -             |               | GND           | -             |               |  |  |

| AC2            | GND           | -             |               | GND           | -             |               |  |  |

| AA3            | GND           | -             |               | GND           | -             |               |  |  |

| AE1            | GND           | -             |               | GND           | -             |               |  |  |

| Y4             | GND           | -             |               | GND           | -             |               |  |  |

| AB4            | GND           | -             |               | GND           | -             |               |  |  |

| AA5            | GND           | -             |               | GND           | -             |               |  |  |

| AE6            | GND           | -             |               | GND           | -             |               |  |  |

| AE8            | GND           | -             |               | GND           | -             |               |  |  |

| AH5            | GND           | -             |               | GND           | -             |               |  |  |

| AG9            | GND           | -             |               | GND           | -             |               |  |  |

| AG6            | GND           | -             |               | GND           | -             |               |  |  |

| AF11           | GND           | -             |               | GND           | -             |               |  |  |

| AG12           | GND           | -             |               | GND           | -             |               |  |  |

| AJ10           | GND           | -             |               | GND           | -             |               |  |  |

| AK26           | GND           | -             |               | GND           | -             |               |  |  |

| AJ22           | GND           | -             |               | GND           | -             |               |  |  |

| AF20           | GND           | -             |               | GND           | -             |               |  |  |

| AJ25           | GND           | -             |               | GND           | -             |               |  |  |

### LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup> (Cont.)

|                | LFSC/M15      |               |               |               |               | LFSC/M25      |

|----------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Ball<br>Number | Ball Function | VCCIO<br>Bank | Dual Function | Ball Function | VCCIO<br>Bank | Dual Function |

| B29            | NC            | -             |               | NC            | -             |               |

1. Differential pair grouping within a PIC is A (True) and B (Complement) and C (True) and D (Complement).

2. The LatticeSC/M15 and LatticeSC/M25 in a 900-pin package supports a 16-bit MPI interface.

### LFSC/M25, LFSC/M40 Logic Signal Connections: 1020 fcBGA<sup>1, 2</sup> (Cont.)

| Ball   |               | LFSC/M     | 25            |               | LFSC/M40   |               |  |  |

|--------|---------------|------------|---------------|---------------|------------|---------------|--|--|

| Number | Ball Function | VCCIO Bank | Dual Function | Ball Function | VCCIO Bank | Dual Function |  |  |

| U12    | VCC12         | -          |               | VCC12         | -          |               |  |  |

| U21    | VCC12         | -          |               | VCC12         | -          |               |  |  |

| AA16   | VCC12         | -          |               | VCC12         | -          |               |  |  |

| AA17   | VCC12         | -          |               | VCC12         | -          |               |  |  |

| M14    | VCC12         | -          |               | VCC12         | -          |               |  |  |

| P12    | VCC12         | -          |               | VCC12         | -          |               |  |  |

| W12    | VCC12         | -          |               | VCC12         | -          |               |  |  |

| AA14   | VCC12         | -          |               | VCC12         | -          |               |  |  |

| AA19   | VCC12         | -          |               | VCC12         | -          |               |  |  |

| W21    | VCC12         | -          |               | VCC12         | -          |               |  |  |

| P21    | VCC12         | -          |               | VCC12         | -          |               |  |  |

| M19    | VCC12         | -          |               | VCC12         | -          |               |  |  |

| A2     | GND           | -          |               | GND           | -          |               |  |  |

| A10    | GND           | -          |               | GND           | -          |               |  |  |

| E28    | NC            | -          |               | NC            | -          |               |  |  |

| E5     | NC            | -          |               | NC            | -          |               |  |  |

| F10    | NC            | -          |               | NC            | -          |               |  |  |

| E10    | NC            | -          |               | NC            | -          |               |  |  |

| E23    | NC            | -          |               | NC            | -          |               |  |  |

| F23    | NC            | -          |               | NC            | -          |               |  |  |

1. Differential pair grouping within a PIC is A (True) and B (Complement) and C (True) and D (Complement).

2. The LatticeSC/M25 and LatticeSC/M40 in a 1020-pin package support a 16-bit MPI interface.

### LFSC/M40, LFSC/M80 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup> (Cont.)

|                |                  |               |               | LFSC/M80         |               |               |  |

|----------------|------------------|---------------|---------------|------------------|---------------|---------------|--|

|                |                  |               | LFSC/M40      |                  |               |               |  |

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual Function | Ball<br>Function | VCCIO<br>Bank | Dual Function |  |

| AC19           | VTT_5            | 5             |               | VTT_5            | 5             |               |  |

| AC20           | VTT_5            | 5             |               | VTT_5            | 5             |               |  |

| AD22           | VTT_5            | 5             |               | VTT_5            | 5             |               |  |

| AB24           | VTT_6            | 6             |               | VTT_6            | 6             |               |  |

| W23            | VTT_6            | 6             |               | VTT_6            | 6             |               |  |

| Y23            | VTT_6            | 6             |               | VTT_6            | 6             |               |  |

| N24            | VTT_7            | 7             |               | VTT_7            | 7             |               |  |

| R23            | VTT_7            | 7             |               | VTT_7            | 7             |               |  |

| T23            | VTT_7            | 7             |               | VTT_7            | 7             |               |  |

| M12            | VDDAX25_R        | -             |               | VDDAX25_R        | -             |               |  |

| M23            | VDDAX25_L        | -             |               | VDDAX25_L        | -             |               |  |

| Y16            | GND              | -             |               | GND              | -             |               |  |

| Y14            | GND              | -             |               | GND              | -             |               |  |

| N21            | VCC12            | -             |               | VCC12            | -             |               |  |

| P22            | VCC12            | -             |               | VCC12            | -             |               |  |

| AA22           | VCC12            | -             |               | VCC12            | -             |               |  |

| AB21           | VCC12            | -             |               | VCC12            | -             |               |  |

| AB14           | VCC12            | -             |               | VCC12            | -             |               |  |

| AA13           | VCC12            | -             |               | VCC12            | -             |               |  |

| P13            | VCC12            | -             |               | VCC12            | -             |               |  |

| N14            | VCC12            | -             |               | VCC12            | -             |               |  |

| G26            | NC               | -             |               | NC               | -             |               |  |

| G9             | NC               | -             |               | NC               | -             |               |  |

| J12            | NC               | -             |               | NC               | -             |               |  |

| H12            | NC               | -             |               | NC               | -             |               |  |

| H23            | NC               | -             |               | NC               | -             |               |  |

| J23            | NC               | -             |               | NC               | -             |               |  |

1. Differential pair grouping within a PCI is A (True) and B (complement) and C (True) and D (Complement).

2. The LatticeSC/M40 and LatticeSC/M80 in an 1152-pin package support a 32-bit MPI interface.

## LFSC/M115 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup>

|             | LFSC/M115     |            |                           |  |  |  |  |  |

|-------------|---------------|------------|---------------------------|--|--|--|--|--|

| Ball Number | Ball Function | VCCIO Bank | Dual Function             |  |  |  |  |  |

| G27         | A_REFCLKP_L   | -          |                           |  |  |  |  |  |

| H27         | A_REFCLKN_L   | -          |                           |  |  |  |  |  |

| H25         | VCC12         | -          |                           |  |  |  |  |  |

| H26         | RESP_ULC      | -          |                           |  |  |  |  |  |

| B33         | RESETN        | 1          |                           |  |  |  |  |  |

| C34         | TSALLN        | 1          |                           |  |  |  |  |  |

| D34         | DONE          | 1          |                           |  |  |  |  |  |

| C33         | INITN         | 1          |                           |  |  |  |  |  |

| J27         | MO            | 1          |                           |  |  |  |  |  |

| K27         | M1            | 1          |                           |  |  |  |  |  |

| M26         | M2            | 1          |                           |  |  |  |  |  |

| L26         | M3            | 1          |                           |  |  |  |  |  |

| F30         | PL15A         | 7          | ULC_PLLT_IN_A/ULC_PLLT_FB |  |  |  |  |  |

| G30         | PL15B         | 7          | ULC_PLLC_IN_A/ULC_PLLC_FB |  |  |  |  |  |

| H28         | PL15C         | 7          |                           |  |  |  |  |  |

| J28         | PL15D         | 7          |                           |  |  |  |  |  |

| F31         | PL17A         | 7          | ULC_DLLT_IN_C/ULC_DLLT_FB |  |  |  |  |  |

| G31         | PL17B         | 7          | ULC_DLLC_IN_C/ULC_DLLC_FB |  |  |  |  |  |

| N25         | PL17C         | 7          | ULC_PLLT_IN_B/ULC_PLLT_FB |  |  |  |  |  |

| P25         | PL17D         | 7          | ULC_PLLC_IN_B/ULC_PLLC_FB |  |  |  |  |  |

| D33         | PL18A         | 7          | ULC_DLLT_IN_D/ULC_DLLT_FB |  |  |  |  |  |

| E33         | PL18B         | 7          | ULC_DLLC_IN_D/ULC_DLLC_FB |  |  |  |  |  |

| H29         | PL18C         | 7          |                           |  |  |  |  |  |

| J29         | PL18D         | 7          | VREF2_7                   |  |  |  |  |  |

| F32         | PL19A         | 7          |                           |  |  |  |  |  |

| G32         | PL19B         | 7          |                           |  |  |  |  |  |

| P26         | PL19C         | 7          |                           |  |  |  |  |  |

| N26         | PL19D         | 7          |                           |  |  |  |  |  |

| H30         | PL26A         | 7          |                           |  |  |  |  |  |

| J30         | PL26B         | 7          |                           |  |  |  |  |  |

| L28         | PL26C         | 7          |                           |  |  |  |  |  |

| M28         | PL26D         | 7          |                           |  |  |  |  |  |

| J31         | PL43A         | 7          |                           |  |  |  |  |  |

| K31         | PL43B         | 7          |                           |  |  |  |  |  |

| L27         | PL43C         | 7          | VREF1_7                   |  |  |  |  |  |

| M27         | PL43D         | 7          | <br>DIFFR_7               |  |  |  |  |  |

| J32         | PL45A         | 7          |                           |  |  |  |  |  |

| K32         | PL45B         | 7          |                           |  |  |  |  |  |

| L29         | PL45C         | 7          |                           |  |  |  |  |  |

| M29         | PL45D         | 7          |                           |  |  |  |  |  |

| H33         | PL47A         | 7          |                           |  |  |  |  |  |

| J33         | PL47B         | 7          |                           |  |  |  |  |  |

# LFSC/M115 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup>

|             | LFSC/M115     |            |                    |  |  |  |  |  |

|-------------|---------------|------------|--------------------|--|--|--|--|--|

| Ball Number | Ball Function | VCCIO Bank | Dual Function      |  |  |  |  |  |

| F6          | A_VDDOB0_R    | -          |                    |  |  |  |  |  |

| B4          | A_HDOUTN0_R   | -          | PCS 3E0 CH 0 OUT N |  |  |  |  |  |

| F7          | A_VDDOB1_R    | -          |                    |  |  |  |  |  |

| B5          | A_HDOUTN1_R   | -          | PCS 3E0 CH 1 OUT N |  |  |  |  |  |

| E6          | VCC12         | -          |                    |  |  |  |  |  |

| A5          | A_HDOUTP1_R   | -          | PCS 3E0 CH 1 OUT P |  |  |  |  |  |

| B6          | A_HDINN1_R    | -          | PCS 3E0 CH 1 IN N  |  |  |  |  |  |

| A6          | A_HDINP1_R    | -          | PCS 3E0 CH 1 IN P  |  |  |  |  |  |

| C6          | VCC12         | -          |                    |  |  |  |  |  |

| D4          | A_VDDIB1_R    | -          |                    |  |  |  |  |  |

| C7          | VCC12         | -          |                    |  |  |  |  |  |

| D5          | A_VDDIB2_R    | -          |                    |  |  |  |  |  |

| A7          | A_HDINP2_R    | -          | PCS 3E0 CH 2 IN P  |  |  |  |  |  |

| B7          | A_HDINN2_R    | -          | PCS 3E0 CH 2 IN N  |  |  |  |  |  |

| E7          | VCC12         | -          |                    |  |  |  |  |  |

| A8          | A_HDOUTP2_R   | -          | PCS 3E0 CH 2 OUT P |  |  |  |  |  |

| F8          | A_VDDOB2_R    | -          |                    |  |  |  |  |  |

| B8          | A_HDOUTN2_R   | -          | PCS 3E0 CH 2 OUT N |  |  |  |  |  |

| F9          | A_VDDOB3_R    | -          |                    |  |  |  |  |  |

| B9          | A_HDOUTN3_R   | -          | PCS 3E0 CH 3 OUT N |  |  |  |  |  |

| E8          | VCC12         | -          |                    |  |  |  |  |  |

| A9          | A_HDOUTP3_R   | -          | PCS 3E0 CH 3 OUT P |  |  |  |  |  |

| B10         | A_HDINN3_R    | -          | PCS 3E0 CH 3 IN N  |  |  |  |  |  |

| A10         | A_HDINP3_R    | -          | PCS 3E0 CH 3 IN P  |  |  |  |  |  |

| C10         | VCC12         | -          |                    |  |  |  |  |  |

| D6          | A_VDDIB3_R    | -          |                    |  |  |  |  |  |

| G10         | VCC12         | -          |                    |  |  |  |  |  |

| D7          | B_VDDIB0_R    | -          |                    |  |  |  |  |  |

| E10         | B_HDINP0_R    | -          | PCS 3E1 CH 0 IN P  |  |  |  |  |  |

| F10         | B_HDINN0_R    | -          | PCS 3E1 CH 0 IN N  |  |  |  |  |  |

| K10         | VCC12         | -          |                    |  |  |  |  |  |

| A11         | B_HDOUTP0_R   | -          | PCS 3E1 CH 0 OUT P |  |  |  |  |  |

| D10         | B_VDDOB0_R    | -          |                    |  |  |  |  |  |

| B11         | B_HDOUTN0_R   | -          | PCS 3E1 CH 0 OUT N |  |  |  |  |  |

| D11         | B_VDDOB1_R    | -          |                    |  |  |  |  |  |

| B12         | B_HDOUTN1_R   | -          | PCS 3E1 CH 1 OUT N |  |  |  |  |  |

| L10         | VCC12         | -          |                    |  |  |  |  |  |

| A12         | B_HDOUTP1_R   | -          | PCS 3E1 CH 1 OUT P |  |  |  |  |  |

| F11         | B_HDINN1_R    | -          | PCS 3E1 CH 1 IN N  |  |  |  |  |  |

| E11         | B_HDINP1_R    | -          | PCS 3E1 CH 1 IN P  |  |  |  |  |  |

| G11         | VCC12         | -          |                    |  |  |  |  |  |

| D8          | B_VDDIB1_R    | -          |                    |  |  |  |  |  |

| G12         | VCC12         | -          |                    |  |  |  |  |  |

### LFSC/M80, LFSC/M115 Logic Signal Connections: 1704 fcBGA<sup>1, 2</sup> (Cont.)

|                |                  |               | LFSC/M80           | LFSC/M115                        |               |                    |  |

|----------------|------------------|---------------|--------------------|----------------------------------|---------------|--------------------|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function   | Ball<br>Function                 | VCCIO<br>Bank | Dual<br>Function   |  |

| D1             | A_HDINN0_R       | -             | PCS 3E0 CH 0 IN N  | A_HDINN0_R                       | -             | PCS 3E0 CH 0 IN N  |  |

| F1             | VCC12            | -             |                    | VCC12                            | -             |                    |  |

| A3             | A_HDOUTP0_R      | -             | PCS 3E0 CH 0 OUT P | A_HDOUTP0_R                      | -             | PCS 3E0 CH 0 OUT P |  |

| E1             | A_VDDOB0_R       | -             |                    | A_VDDOB0_R                       | -             |                    |  |

| B3             | A_HDOUTN0_R      | -             | PCS 3E0 CH 0 OUT N | A_HDOUTN0_R                      | -             | PCS 3E0 CH 0 OUT N |  |

| C2             | A_VDDOB1_R       | -             |                    | A_VDDOB1_R                       | -             |                    |  |

| A4             | A_HDOUTN1_R      | -             | PCS 3E0 CH 1 OUT N | A_HDOUTN1_R                      | -             | PCS 3E0 CH 1 OUT N |  |

| B2             | VCC12            | -             |                    | VCC12                            | -             |                    |  |

| B4             | A_HDOUTP1_R      | -             | PCS 3E0 CH 1 OUT P | A_HDOUTP1_R                      | -             | PCS 3E0 CH 1 OUT P |  |

| E3             | A_HDINN1_R       | -             | PCS 3E0 CH 1 IN N  | A_HDINN1_R                       | -             | PCS 3E0 CH 1 IN N  |  |

| D3             | A_HDINP1_R       | -             | PCS 3E0 CH 1 IN P  | A_HDINP1_R                       | -             | PCS 3E0 CH 1 IN P  |  |

| M10            | VCC12            | -             |                    | VCC12                            | -             |                    |  |

| E2             | A_VDDIB1_R       | -             |                    | A_VDDIB1_R                       | -             |                    |  |

| J11            | VCC12            | -             |                    | VCC12                            | -             |                    |  |

| M11            | A_VDDIB2_R       | -             |                    | A_VDDIB2_R                       | -             |                    |  |

| D4             | A_HDINP2_R       | -             | PCS 3E0 CH 2 IN P  | A_HDINP2_R                       | -             | PCS 3E0 CH 2 IN P  |  |

| E4             | A_HDINN2_R       | -             | PCS 3E0 CH 2 IN N  | A_HDINN2_R                       | -             | PCS 3E0 CH 2 IN N  |  |

| K9             | VCC12            | -             |                    | VCC12                            | -             | 1                  |  |

| A5             | A_HDOUTP2_R      | -             | PCS 3E0 CH 2 OUT P | A_HDOUTP2_R                      | -             | PCS 3E0 CH 2 OUT P |  |

| D2             | A_VDDOB2_R       | -             |                    | A_VDDOB2_R                       | -             |                    |  |

| B5             | A_HDOUTN2_R      | -             | PCS 3E0 CH 2 OUT N | A_HDOUTN2_R                      | -             | PCS 3E0 CH 2 OUT N |  |

| L10            | A_VDDOB3_R       | -             |                    | A_VDDOB3_R                       | -             |                    |  |

| B6             | A_HDOUTN3_R      | -             | PCS 3E0 CH 3 OUT N | A_HDOUTN3_R                      | -             | PCS 3E0 CH 3 OUT N |  |

| G6             | VCC12            | -             |                    | VCC12                            | -             |                    |  |

| A6             | A_HDOUTP3_R      | -             | PCS 3E0 CH 3 OUT P | PCS 3E0 CH 3 OUT P A_HDOUTP3_R - |               | PCS 3E0 CH 3 OUT P |  |

| E5             | A_HDINN3_R       | -             | PCS 3E0 CH 3 IN N  | A_HDINN3_R                       | -             | PCS 3E0 CH 3 IN N  |  |

| D5             | A_HDINP3_R       | -             | PCS 3E0 CH 3 IN P  | A_HDINP3_R                       | -             | PCS 3E0 CH 3 IN P  |  |

| K12            | VCC12            | -             |                    | VCC12                            | -             |                    |  |

| L13            | A_VDDIB3_R       | -             |                    | A_VDDIB3_R                       | -             |                    |  |

| N14            | VCC12            | -             |                    | VCC12                            | -             |                    |  |

| F9             | B_VDDIB0_R       | -             |                    | B_VDDIB0_R                       | -             |                    |  |

| D6             | B_HDINP0_R       | -             | PCS 3E1 CH 0 IN P  | B_HDINP0_R                       | -             | PCS 3E1 CH 0 IN P  |  |

| E6             | B_HDINN0_R       | -             | PCS 3E1 CH 0 IN N  | B_HDINN0_R                       | -             | PCS 3E1 CH 0 IN N  |  |

| J8             | VCC12            | -             |                    | VCC12                            | -             |                    |  |

| B7             | B_HDOUTP0_R      | -             | PCS 3E1 CH 0 OUT P | B_HDOUTP0_R                      | -             | PCS 3E1 CH 0 OUT P |  |

| G4             | B_VDDOB0_R       | -             |                    | B_VDDOB0_R                       | -             |                    |  |

| A7             | B_HDOUTN0_R      | -             | PCS 3E1 CH 0 OUT N | B_HDOUTN0_R                      | -             | PCS 3E1 CH 0 OUT N |  |

| K8             | B_VDDOB1_R       | -             |                    | B_VDDOB1_R                       | -             |                    |  |

| A8             | B_HDOUTN1_R      | -             | PCS 3E1 CH 1 OUT N | B_HDOUTN1_R                      | -             | PCS 3E1 CH 1 OUT N |  |

| L9             | VCC12            | -             |                    | VCC12                            | -             |                    |  |

| B8             | B_HDOUTP1_R      | -             | PCS 3E1 CH 1 OUT P | B_HDOUTP1_R                      | -             | PCS 3E1 CH 1 OUT P |  |

| E7             | B_HDINN1_R       | -             | PCS 3E1 CH 1 IN N  | B_HDINN1_R                       | -             | PCS 3E1 CH 1 IN N  |  |

| D7             | B_HDINP1_R       | -             | PCS 3E1 CH 1 IN P  | B_HDINP1_R                       | -             | PCS 3E1 CH 1 IN P  |  |

| F10            | VCC12            | -             |                    | VCC12                            | -             |                    |  |

| K13            | B_VDDIB1_R       | -             |                    | B_VDDIB1_R                       | -             |                    |  |

### LFSC/M80, LFSC/M115 Logic Signal Connections: 1704 fcBGA<sup>1, 2</sup> (Cont.)

|                |                  | LFSC/M80      | LFSC/M115               |                     |                 |                         |  |

|----------------|------------------|---------------|-------------------------|---------------------|-----------------|-------------------------|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function        | Ball<br>Function    | VCCIO<br>Bank   | Dual<br>Function        |  |

| B22            | PT61B            | 1             | A3/MPI_ADDR17           | PT69B               | 1               | A3/MPI_ADDR17           |  |

| B23            | PT61A            | 1             | A4/MPI_ADDR18           | PT69A               | 1 A4/MPI_ADDR18 |                         |  |

| K23            | PT60D            | 1             | D25/PCLKC1_5/MPI_DATA25 | PT66D 1 D25/PCLKC1_ |                 | D25/PCLKC1_5/MPI_DATA25 |  |

| J23            | PT60C            | 1             | D26/PCLKT1_5/MPI_DATA26 | PT66C               | 1               | D26/PCLKT1_5/MPI_DATA26 |  |

| D22            | PT60B            | 1             | A5/MPI_ADDR19           | PT66B               | 1               | A5/MPI_ADDR19           |  |

| E22            | PT60A            | 1             | A6/MPI_ADDR20 PT66A     |                     | 1               | A6/MPI_ADDR20           |  |

| K22            | PT59D            | 1             | D27/MPI_DATA27          | PT63D               | 1               | D27/MPI_DATA27          |  |

| J22            | PT59C            | 1             | VREF1_1                 | PT63C               | 1               | VREF1_1                 |  |

| D23            | PT59B            | 1             | A7/MPI_ADDR21           | PT63B               | 1               | A7/MPI_ADDR21           |  |

| C23            | PT59A            | 1             | A8/MPI_ADDR22           | PT63A               | 1               | A8/MPI_ADDR22           |  |

| L23            | PT57D            | 1             | D28/PCLKC1_6/MPI_DATA28 | PT61D               | 1               | D28/PCLKC1_6/MPI_DATA28 |  |

| M23            | PT57C            | 1             | D29/PCLKT1_6/MPI_DATA29 | PT61C               | 1               | D29/PCLKT1_6/MPI_DATA29 |  |

| A24            | PT57B            | 1             | A9/MPI_ADDR23           | PT61B               | 1               | A9/MPI_ADDR23           |  |

| B24            | PT57A            | 1             | A10/MPI_ADDR24          | PT61A               | 1               | A10/MPI_ADDR24          |  |

| K25            | PT56D            | 1             | D30/PCLKC1_7/MPI_DATA30 | PT58D               | 1               | D30/PCLKC1_7/MPI_DATA30 |  |

| J25            | PT56C            | 1             | D31/PCLKT1_7/MPI_DATA31 | PT58C               | 1               | D31/PCLKT1_7/MPI_DATA31 |  |

| F23            | PT56B            | 1             | A11/MPI_ADDR25          | PT58B               | 1               | A11/MPI_ADDR25          |  |

| F22            | PT56A            | 1             | A12/MPI_ADDR26          | PT58A               | 1               | A12/MPI_ADDR26          |  |

| J26            | PT55D            | 1             | D11/MPI_DATA11          | PT57D               | 1               | D11/MPI_DATA11          |  |

| K26            | PT55C            | 1             | D12/MPI_DATA12          | PT57C               | 1               | D12/MPI_DATA12          |  |

| E23            | PT55B            | 1             | A13/MPI_ADDR27          | PT57B               | 1               | A13/MPI_ADDR27          |  |

| E24            | PT55A            | 1             | A14/MPI_ADDR28          | PT57A               | 1               | A14/MPI_ADDR28          |  |

| G23            | PT53D            | 1             | A16/MPI_ADDR30          | PT55D               | PT55D 1 A16/MPI |                         |  |

| G24            | PT53C            | 1             | D13/MPI_DATA13          | PT55C               | 1               | D13/MPI_DATA13          |  |

| F26            | PT53B            | 1             | A15/MPI_ADDR29          | PT55B               | 1               | A15/MPI_ADDR29          |  |

| F27            | PT53A            | 1             | A17/MPI_ADDR31          | PT55A               | 1               | A17/MPI_ADDR31          |  |

| H25            | PT52D            | 1             | A19/MPI_TSIZ1           | PT54D               | 1               | A19/MPI_TSIZ1           |  |

| H24            | PT52C            | 1             | A20/MPI_BDIP            | PT54C               | 1               | A20/MPI_BDIP            |  |

| C25            | PT52B            | 1             | A18/MPI_TSIZ0           | PT54B               | 1               | A18/MPI_TSIZ0           |  |

| C26            | PT52A            | 1             | MPI_TEA                 | PT54A               | 1               | MPI_TEA                 |  |

| K24            | PT51D            | 1             | D14/MPI_DATA14          | PT51D               | 1               | D14/MPI_DATA14          |  |

| J24            | PT51C            | 1             | DP1/MPI_PAR1            | PT51C               | 1               | DP1/MPI_PAR1            |  |

| F24            | PT51B            | 1             | A21/MPI_BURST           | PT51B               | 1               | A21/MPI_BURST           |  |

| F25            | PT51A            | 1             | D15/MPI_DATA15          | PT51A               | 1               | D15/MPI_DATA15          |  |

| L26            | D_REFCLKP_L      | -             |                         | D_REFCLKP_L         | -               |                         |  |

| M26            | D_REFCLKN_L      | -             |                         | D_REFCLKN_L         | -               |                         |  |

| G27            | VCC12            | -             |                         | VCC12               | -               |                         |  |

| C29            | D_VDDIB3_L       | -             |                         | D_VDDIB3_L          | -               |                         |  |

| F28            | VCC12            | -             |                         | VCC12               | -               |                         |  |

| D26            | D_HDINP3_L       | -             | PCS 363 CH 3 IN P       | D_HDINP3_L          | -               | PCS 363 CH 3 IN P       |  |

| E26            | D_HDINN3_L       | -             | PCS 363 CH 3 IN N       | D_HDINN3_L          | -               | PCS 363 CH 3 IN N       |  |

| B25            | D_HDOUTP3_L      | -             | PCS 363 CH 3 OUT P      | D_HDOUTP3_L         | -               | PCS 363 CH 3 OUT P      |  |

| D24            | VCC12            | -             |                         | VCC12               | -               |                         |  |

| A25            | D_HDOUTN3_L      | -             | PCS 363 CH 3 OUT N      | D_HDOUTN3_L         | -               | PCS 363 CH 3 OUT N      |  |

| E25            | D_VDDOB3_L       | -             |                         | D_VDDOB3_L          | -               |                         |  |

### Commercial, Cont.

| Part Number                          | Grade | Package       | Balls | Temp. | LUTs (K) |

|--------------------------------------|-------|---------------|-------|-------|----------|

| LFSCM3GA115EP1-6FC1152C <sup>1</sup> | -6    | Ceramic fcBGA | 1152  | COM   | 115.2    |

| LFSCM3GA115EP1-5FC1152C <sup>1</sup> | -5    | Ceramic fcBGA | 1152  | COM   | 115.2    |

| LFSCM3GA115EP1-6FF1152C              | -6    | Organic fcBGA | 1152  | COM   | 115.2    |

| LFSCM3GA115EP1-5FF1152C              | -5    | Organic fcBGA | 1152  | COM   | 115.2    |

| LFSCM3GA115EP1-6FC1704C <sup>1</sup> | -6    | Ceramic fcBGA | 1704  | COM   | 115.2    |

| LFSCM3GA115EP1-5FC1704C1             | -5    | Ceramic fcBGA | 1704  | COM   | 115.2    |

| LFSCM3GA115EP1-6FF1704C              | -6    | Organic fcBGA | 1704  | COM   | 115.2    |

| LFSCM3GA115EP1-5FF1704C              | -5    | Organic fcBGA | 1704  | COM   | 115.2    |

1. Converted to organic flip-chip BGA package per PCN #01A-10.

| Date                  | Version         | Section                                     | Change Summary                                                                                                           |

|-----------------------|-----------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| March 2007<br>(cont.) | 01.5<br>(cont.) | DC and Switching<br>Characteristics (cont.) | Updated LatticeSC Internal Timing Parameters with ispLEVER 6.1 SP1 results.                                              |

|                       |                 |                                             | Updated t <sub>FDEL</sub> and t <sub>CDEL</sub> specifications.                                                          |

|                       |                 |                                             | Updated LatticeSC Family Timing Adders with ispLEVER 6.1 SP1 results.                                                    |

|                       |                 |                                             | Updated PLL specifications to expand frequency range down to 2 MHz and break out jitter for the different ranges.        |

|                       |                 |                                             | Added footnote to sysCLOCK PLL Timing table specifying the condi-<br>tions for the jitter measurements.                  |

|                       |                 |                                             | Added t <sub>DLL</sub> specification to sysCLOCK DLL Timing table.                                                       |

|                       |                 |                                             | Added footnote to sysCLOCK DLL Timing table specifying the condi-<br>tions for the jitter measurements.                  |

|                       |                 |                                             | Added sysCONFIG Master Parallel Configuration Mode and sysCON-<br>FIG SPI Port to LatticeSC sysCONFIG Port Timing table. |

|                       |                 | Pin Information                             | Updated Pin Information Summary with SC40 information.                                                                   |

|                       |                 |                                             | Updated LFSC25 Logic Signal Connections: FF1020 with SC40 infor-<br>mation.                                              |

|                       |                 |                                             | Updated LFSC80 Logic Signal Connections: FC1152 with SC40 infor-<br>mation.                                              |

| August 2007           | 01.6            | General                                     | Changed references of "HDC" to "HDC/SI".                                                                                 |

|                       |                 |                                             | Changed references of "LDCN" to "LDCN/SCS".                                                                              |

|                       |                 |                                             | Changed references of "BUSYN/RCLK" to "BUSYN/RCLK/SCK".                                                                  |

|                       |                 |                                             | Changed references of "RDCFGN" to "TSALLN".                                                                              |

|                       |                 |                                             | Changed references of "TDO/RDDATA" to "TDO".                                                                             |

|                       |                 | Architecture                                | Updated text in Ripple Mode section.                                                                                     |

|                       |                 |                                             | Added information to Global Set/Reset.                                                                                   |

|                       |                 |                                             | Added information for Spread Spectrum Clocking                                                                           |

|                       |                 |                                             | Modified information for PLL/DLL Cascading. DLL to PLL is now supported.                                                 |

|                       |                 |                                             | Modified AIL Block text and figure.                                                                                      |

|                       |                 |                                             | Modified Figure 2-20 DDR/Shift Register Block.                                                                           |

|                       |                 |                                             | Added Information to Hot Socketing.                                                                                      |

|                       |                 |                                             | Added new information for I/O Architecture Rules.                                                                        |

|                       |                 |                                             | Added information to SERDES Power Supply Sequencing Require-<br>ments.                                                   |

|                       |                 | DC and Switching<br>Characteristics         | Added footnote to Hot Socketing Specifications table.                                                                    |

|                       |                 |                                             | Modified Initialization and Standby Supply Current table.                                                                |

|                       |                 |                                             | Modified GSR Timing table.                                                                                               |

|                       |                 |                                             | Modified sysCLOCK DLL Timing table to include I <sub>DUTY.</sub>                                                         |

|                       |                 |                                             | Deleted Readback Timing information from sysCONFIG Port Timing table.                                                    |

|                       |                 |                                             | Modified data in External Switching Characteristics table.                                                               |

|                       |                 | Pin Information                             | Added information to the Signal Descriptions table for HDC/SI, LDCN/SCS.                                                 |

|                       |                 |                                             | Added footnote to Signal Descriptions table.                                                                             |