Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                |

|--------------------------------|--------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                       |

| Number of LABs/CLBs            | 20000                                                                          |

| Number of Logic Elements/Cells | 80000                                                                          |

| Total RAM Bits                 | 5816320                                                                        |

| Number of I/O                  | 904                                                                            |

| Number of Gates                | -                                                                              |

| Voltage - Supply               | 0.95V ~ 1.26V                                                                  |

| Mounting Type                  | Surface Mount                                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                |

| Package / Case                 | 1704-BCBGA, FCBGA                                                              |

| Supplier Device Package        | 1704-CFCBGA (42.5x42.5)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfsc3ga80e-5fc1704c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1-1. LatticeSC Family Selection Guide<sup>1</sup>

| Device                                       | SC15           | SC25   | SC40   | SC80   | SC115  |

|----------------------------------------------|----------------|--------|--------|--------|--------|

| LUT4s (K)                                    | 15             | 25     | 40     | 80     | 115    |

| sysMEM Blocks (18Kb)                         | 56             | 104    | 216    | 308    | 424    |

| Embedded Memory (Mbits)                      | 1.03           | 1.92   | 3.98   | 5.68   | 7.8    |

| Max. Distributed Memory (Mbits)              | 0.24           | 0.41   | 0.65   | 1.28   | 1.84   |

| Number of 3.8Gbps SERDES (Max.)              | 8              | 16     | 16     | 32     | 32     |

| DLLs                                         | 12             | 12     | 12     | 12     | 12     |

| Analog PLLs                                  | 8              | 8      | 8      | 8      | 8      |

| MACO Blocks                                  | 4              | 6      | 10     | 10     | 12     |

| Package I/O/SERDES Combinations (1           | mm ball pitch) |        |        |        |        |

| 256-ball fpBGA (17 x 17mm)                   | 139/4          |        |        |        |        |

| 900-ball fpBGA (31 x 31mm)                   | 300/8          | 378/8  |        |        |        |

| 1020-ball fcBGA (33 x 33mm) <sup>2</sup>     |                | 476/16 | 562/16 |        |        |

| 1152-ball fcBGA (35 x 35mm) <sup>3</sup>     |                |        | 604/16 | 660/16 | 660/16 |

| 1704-ball fcBGA (42.5 x 42.5mm) <sup>3</sup> |                |        |        | 904/32 | 942/32 |

<sup>1.</sup> The information in this preliminary data sheet is by definition not final and subject to change. Please consult the Lattice web site and your local Lattice sales office to ensure you have the latest information regarding the specifications for these products as you make critical design decisions.

The LatticeSCM devices add MACO-enabled IP functionality to the base LatticeSC devices. Table 1-2 shows the type and number of each pre-engineered IP core.

Table 1-2. LatticeSCM Family

| Device                                                                                                  | SCM15 | SCM25 | SCM40 | SCM80 | SCM115 |

|---------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--------|

| flexiMAC Blocks                                                                                         | 1     | 2     | 2     | 2     | 4      |

| SPI4.2 Blocks                                                                                           | 1     | 2     | 2     | 2     | 2      |

| Memory Controller Blocks  • DDR/DDR2 DRAM Mode  • QDR II/II+ SRAM Mode  • RLDRAM I  • RLDRAM II CIO/SIO | 1     | 2     | 2     | 2     | 2      |

| Low-Speed CDR Blocks                                                                                    | 0     | 0     | 2     | 2     | 2      |

| PCI Express LTSSM (PHY) Blocks                                                                          | 1     | 0     | 2     | 2     | 2      |

Note: See each IP core user's guide for more information about support for specific LatticeSCM devices.

### Introduction

The LatticeSC family of FPGAs combines a high-performance FPGA fabric, high-speed SERDES, high-performance I/Os and large embedded RAM in a single industry leading architecture. This FPGA family is fabricated in a state of the art technology to provide one of the highest performing FPGAs in the industry.

This family of devices includes features to meet the needs of today's communication network systems. These features include SERDES with embedded advance PCS (Physical Coding sub-layer), up to 7.8 Mbits of sysMEM embedded block RAM, dedicated logic to support system level standards such as RAPIDIO, SPI4.2, SFI-4, UTO-PIA, XGMII and CSIX. The devices in this family feature clock multiply, divide and phase shift PLLs, numerous

<sup>2.</sup> Organic fcBGA converted to organic fcBGA revision 2 per PCN #02A-10.

<sup>3.</sup> Ceramic fcBGA converted to organic fcBGA per PCN #01A-10.

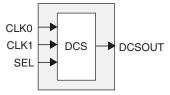

toggled. There are eight DCS blocks per device, located in pairs at the center of each side. Figure 2-9 illustrates the DCS Block diagram.

#### Figure 2-9. DCS Block Diagram

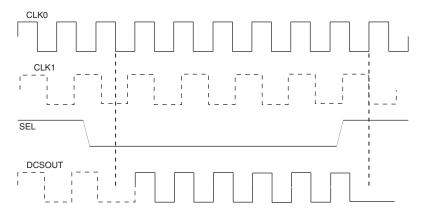

Figure 2-10 shows timing waveforms for one of the DCS operating modes. The DCS block can be programmed to other modes. For more information on the DCS, please see details of additional technical documentation at the end of this data sheet.

Figure 2-10. DCS Waveforms

### **Clock Boosting**

There are programmable delays available in the clock signal paths in the PFU, PIC and EBR blocks. These allow setup and clock-to-output times to be traded to meet critical timing without slowing the system clock. If this feature is enabled then the design tool automatically uses these delays to improve timing performance.

### Global Set/Reset

There is a global set/reset (GSR) network on the device that is distributed to all FFs, PLLs, DLLs and other blocks on the device. This GSR network can operate in two modes:

- a) asynchronous no clock is required to get into or out of the reset state.

- b) synchronous The global GSR net is synchronized to a user selected clock. In this mode it continues to be asynchronous to get into the reset state, but is synchronous to get out of the reset state. This allows all registers on the device to become operational in the same clock period. The synchronous GSR goes out of reset in two cycles from the clock edge where the setup time of the FF was met (not from the GSR being released).

### sysCLOCK Phase Locked Loops (PLLs)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. Each PLL has four dividers associated with it: input clock divider, feedback divider and two clock output dividers. The input divider is used to divide the input clock signal, while the feedback divider is used to multiply the input clock signal.

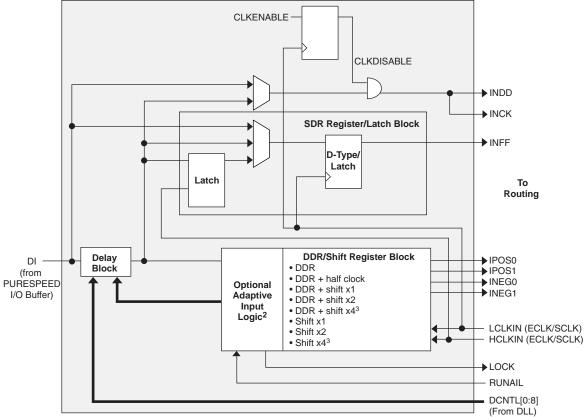

Figure 2-20. Input Register Block<sup>1</sup>

- 1. UPDATE, Set and Reset not shown for clarity

- 2. Adaptive input logic is only available in selected PIO 3. By four shift modes utilize DDR/shift register block from paired PIO.

- 4. CLKDISABLE is used to block the transitions on the DQS pin during post-amble. Its main use is to disable DQS (typically found in DDR memory interfaces) or other clock signals. It can also be used to disable any/all input signals to save power.

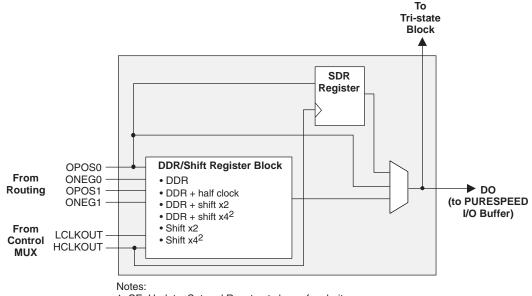

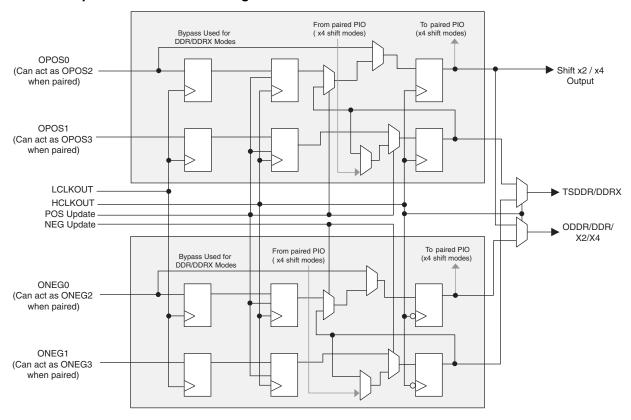

Figure 2-22. Output Register Block<sup>1</sup>

- 1. CE, Update, Set and Reset not shown for clarity.

- 2. By four shift modes utilizes DDR/Shift register block from paired PIO.

- 3. DDR/Shift register block shared with tristate block.

Figure 2-23. Output/Tristate DDR/Shift Register Block

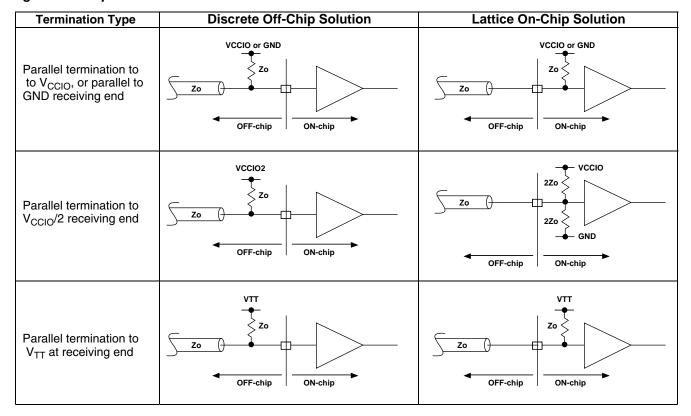

Single Ended Inputs: The SC devices support a number of different termination schemes for single ended inputs:

- Parallel to V<sub>CCIO</sub> or GND

- Parallel to V<sub>CCIO</sub>/2

- Parallel to V<sub>TT</sub>

Figure 2-28 shows the single ended input schemes that are supported. The nominal values of the termination resistors are shown in Table 2-9.

Figure 2-28. Input Termination Schemes

In many situations designers can chose whether to use Thevenin or parallel to  $V_{TT}$  termination. The Thevenin approach has the benefit of not requiring a termination voltage to be applied to the device. The parallel to  $V_{TT}$  approach consumes less power.

#### **VTT Termination Resources**

Each I/O bank, except bank 1, has a number of  $V_{TT}$  pins that must be connected if  $V_{TT}$  is used. Note  $V_{TT}$  pins can sink or source current and the power supply they are connected to must be able to handle the relatively high currents associated with the termination circuits. Note:  $V_{TT}$  is not available in all package styles.

On-chip parallel termination to  $V_{TT}$  is supported at the receiving end only. On-chip parallel output termination to  $V_{TT}$  is not supported.

The  $V_{TT}$  internal bus is also connected to the internal  $V_{CMT}$  node. Thus in one bank designers can implement either  $V_{TT}$  termination or  $V_{CMT}$  termination for differential inputs.

### **DDRII/RLDRAMII Termination Support**

The DDR II memory and RLDRAMII (in Bidirection Data mode) standards require that the on-chip termination to  $V_{TT}$  be turned on when a pin is an input and off when the pin is an output. The LatticeSC devices contain the required circuitry to support this behavior. For additional detail refer to technical information at the end of the data sheet.

this allows for easy integration with the rest of the system. These capabilities make the LatticeSC ideal for many multiple power supply and hot-swap applications. The maximum current during hot socketing is 4mA. See Hot Socketing Specifications in Chapter 3 of this data sheet.

### **Power-Up Requirements**

To prevent high power supply and input pin currents, each VCC, VCC12, VCCAUX, VCCIO and VCCJ power supplies must have a monotonic ramp up time of 75 ms or less to reach its minimum operating voltage. Apart from VCC and VCC12, which have an additional requirement, and VCCIO and VCCAUX, which also have an additional requirement, the VCC, VCC12, VCCAUX, VCCIO and VCCJ power supplies can ramp up in any order, with no restriction on the time between them. However, the ramp time for each must be 75 ms or less. Configuration of the device will not proceed until the last power supply has reached its minimum operating voltage.

#### Additional Requirement for VCC and VCC12:

VCC12 must always be higher than VCC. This condition must be maintained at ALL times, including during powerup and power-down. Note that for 1.2V only operation, it is advisable to source both of these supplies from the same power supply.

#### Additional Requirement for VCCIO and VCCAUX:

If any VCCIOs are 1.2/1.5/1.8V, then VCCAUX MUST be applied before them. If any VCCIO is 1.2/1.5/1.8V and is powered up before VCCAUX, then when VCCAUX is powered up, it may drag VCCIO up with it as it crosses through the VCCIO value. (Note: If the VCCIO supply is capable of sinking current, as well as the more usual sourcing capability, this behavior is eliminated. However, the amount of current that the supply needs to sink is unknown and is likely to be in the hundreds of milliamps range).

### **Power-Down Requirements**

To prevent high power supply and input pin currents, power must be removed monotonically from either VCC or VCCAUX (and must reach the power-down trip point of 0.5V for VCC, 0.95V for VCCAUX) before power is removed monotonically from VCC12, any of the VCCIOs, or VCCJ. Note that VCC12 can be removed at the same time as VCC, but it cannot be removed earlier. In many applications, VCC and VCC12 will be sourced from the same power supply and so will be removed together. For systems where disturbance of the user pins is a don't care condition, the power supplies can be removed in any order as long as they power down monotonically within 200ms of each other.

Additionally, if any banks have VCCIO=3.3V nominal (potentially banks 1, 4, 5) then VCCIO for those banks must not be lower than VCCAUX during power-down. The normal variation in ramp-up times of power supplies and voltage regulators is not a concern here.

Note: The SERDES power supplies are NOT included in these requirements and have no specific sequencing requirements. However, when using the SERDES with VDDIB or VDDOB that is greater than 1.2V (1.5V nominal for example), the SERDES should not be left in a steady state condition with the 1.5V power applied and the 1.2V power not applied. Both the 1.2V and 1.5V power should be applied to the SERDES at nominally the same time. The normal variation in the ramp-up times of power supplies and voltage regulators is not a concern here.

### **SERDES Power Supply Sequencing Requirements**

When using the SERDES with 1.5V VDDIB or VDDOB supplies, the SERDES should not be left in a steady state condition with the 1.5V power applied and the 1.2V power not applied. Both the 1.2V and the 1.5V power should be applied to the SERDES at nominally the same time. The normal variation in ramp-up times of power supples and voltage regulators is not a concern.

#### Additional Requirement for SERDES Power Supply

All VCC12 pins need to be connected on all devices independent of functionality used on the device. This analog supply is used by both the RX and TX portions of the SERDES and is used to control the core SERDES logic regardless of the SERDES being used in the design. VDDIB and VDDOB are used as supplies for the terminations on the CML input and output buffers. If a particular channel is not used, these can be UNCONNECTED (floating).

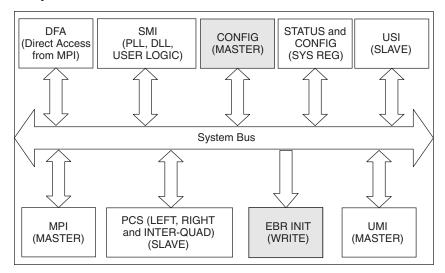

Figure 2-31. LatticeSC System Bus Interfaces

Several interfaces exist between the System Bus and other FPGA elements. The MPI interface acts as a bridge between the external microprocessor bus and System Bus. The MPI may work in an independent clock domain from the System Bus if the System Bus clock is not sourced from the external microprocessor clock. Pipelined operation allows high-speed memory interface to the EBR and peripheral access without the requirement for additional cycles on the bus. Burst transfers allow optimal use of the memory interface by giving advance information of the nature of the transfers.

Details for the majority of the peripherals can be found in the associated technical documentation, see details at the end of this data sheet. Additional details of the MPI are provided below.

#### **Microprocessor Interface (MPI)**

The LatticeSC family devices have a dedicated synchronous MPI function block. The MPI is programmable to operate with PowerPC/PowerQUICC MPC860/MPC8260 series microprocessors. The MPI implements an 8-, 16-, or 32-bit interface with 1-bit, 2-bit, or 4-bit parity to the host processor (PowerPC) that can be used for configuration and read-back of the FPGA as well as for user-defined data processing and general monitoring of FPGA functions.

The control portion of the MPI is available following power-up of the FPGA if the mode pins specify MPI mode, even if the FPGA is not yet configured. The width of the data port is selectable among 8-, 16-, or 32-bit and the parity bus can be 1-, 2-, or 4-bit. In configuration mode the data and parity bus width are related to the state of the M[0:3] mode pins. For post-configuration use, the MPI must be included in the configuration bit stream by using an MPI library element in your design from the ispLEVER primitive library, or by setting the bit of the MPI configuration control register prior to the start of configuration. The user can also enable and disable the parity bus through the configuration bit stream. These pads can be used as general I/O when they are not needed for MPI use.

The MPI block also provides the capability to interface directly to the FPGA fabric with a databus after configuration. The bus protocol is still handled by the MPI block but the direct FPGA access allows high-speed block data transfers such as DMA transactions. Figure 2-32 shows one of the ways a PowerPC is connected to MPI.

### **LatticeSC/M Family Timing Adders (Continued)**

Over Recommended Operating Conditions at VCC = 1.2V +/- 5%

|                  |                               | -      | 7      | -6     |        | -      | 5      |       |

|------------------|-------------------------------|--------|--------|--------|--------|--------|--------|-------|

| Buffer Type      | Description                   | Min.   | Max.   | Min.   | Max.   | Min.   | Max.   | Units |

| GTLPLUS15        | GTLPLUS15                     | -0.013 | -0.017 | 0.012  | 0.004  | 0.037  | 0.024  | ns    |

| GTL12            | GTL12                         | -0.063 | -0.071 | -0.007 | -0.048 | 0.056  | -0.032 | ns    |

| Output Adjusters |                               | I      | l .    | l .    | l .    | l .    |        |       |

| LVDS             | LVDS                          | 0.708  | 0.854  | 0.856  | 1.021  | 1.005  | 1.189  | ns    |

| RSDS             | RSDS                          | 0.708  | 0.854  | 0.856  | 1.021  | 1.005  | 1.189  | ns    |

| BLVDS25          | BLVDS                         | -0.129 | 0.05   | -0.136 | 0.069  | -0.136 | 0.083  | ns    |

| MLVDS25          | MLVDS                         | -0.059 | 0.059  | -0.057 | 0.096  | -0.054 | 0.133  | ns    |

| LVPECL33         | LVPECL                        | -0.334 | -0.181 | -0.325 | -1.389 | -0.315 | -2.598 | ns    |

| HSTL18_I         | HSTL_18 class I               | 0.132  | 0.209  | 0.153  | 0.24   | 0.175  | 0.272  | ns    |

| HSTL18_II        | HSTL_18 class II              | 0.24   | 0.176  | 0.268  | 0.255  | 0.298  | 0.333  | ns    |

| HSTL18D_I        | Differential HSTL 18 class I  | 0.132  | 0.209  | 0.153  | 0.24   | 0.175  | 0.272  | ns    |

| HSTL18D_II       | Differential HSTL 18 class II | 0.24   | 0.176  | 0.268  | 0.255  | 0.298  | 0.333  | ns    |

| HSTL15_I         | HSTL_15 class I               | 0.096  | 0.172  | 0.112  | 0.198  | 0.129  | 0.224  | ns    |

| HSTL15_II        | HSTL_15 class II              | 0.208  | 0.131  | 0.233  | 0.203  | 0.259  | 0.275  | ns    |

| HSTL15D_I        | Differential HSTL 15 class I  | 0.096  | 0.172  | 0.112  | 0.198  | 0.129  | 0.224  | ns    |

| HSTL15D_II       | Differential HSTL 15 class II | 0.208  | 0.131  | 0.233  | 0.203  | 0.259  | 0.275  | ns    |

| SSTL33_I         | SSTL_3 class I                | 0.133  | 0.177  | 0.11   | 0.166  | 0.088  | 0.154  | ns    |

| SSTL33_II        | SSTL_3 class II               | 0.173  | 0.247  | 0.164  | 0.253  | 0.156  | 0.258  | ns    |

| SSTL33D_I        | Differential SSTL_3 class I   | 0.133  | 0.177  | 0.11   | 0.166  | 0.088  | 0.154  | ns    |

| SSTL33D_II       | Differential SSTL_3 class II  | 0.173  | 0.247  | 0.164  | 0.253  | 0.156  | 0.258  | ns    |

| SSTL25_I         | SSTL_2 class I                | 0.215  | 0.125  | 0.239  | 0.228  | 0.264  | 0.331  | ns    |

| SSTL25_II        | SSTL_2 class II               | 0.277  | 0.181  | 0.311  | 0.284  | 0.345  | 0.387  | ns    |

| SSTL25D_I        | Differential SSTL_2 class I   | 0.215  | 0.125  | 0.239  | 0.228  | 0.264  | 0.331  | ns    |

| SSTL25D_II       | Differential SSTL_2 class II  | 0.277  | 0.181  | 0.311  | 0.284  | 0.345  | 0.387  | ns    |

| SSTL18_I         | SSTL_2 class I                | 0.16   | 0.081  | 0.179  | 0.173  | 0.199  | 0.265  | ns    |

| SSTL18_II        | SSTL_2 class II               | 0.238  | 0.15   | 0.263  | 0.244  | 0.295  | 0.338  | ns    |

| SSTL18D_I        | Differential SSTL_2 class I   | 0.16   | 0.081  | 0.179  | 0.173  | 0.199  | 0.265  | ns    |

| SSTL18D_II       | Differential SSTL_2 class II  | 0.238  | 0.15   | 0.263  | 0.244  | 0.295  | 0.338  | ns    |

| LVTTL33_8mA      | LVTTL 8mA drive               | -0.346 | -0.165 | -0.496 | -0.296 | -0.646 | -0.428 | ns    |

| LVTTL33_16mA     | LVTTL 16mA drive              | -0.11  | -0.18  | -0.218 | -0.32  | -0.325 | -0.46  | ns    |

| LVTTL33_24mA     | LVTTL 24mA drive              | -0.012 | -0.18  | -0.099 | -0.321 | -0.185 | -0.463 | ns    |

| LVCMOS33_8mA     | LVCMOS 3.3 8mA drive          | -0.346 | -0.165 | -0.496 | -0.296 | -0.646 | -0.428 | ns    |

| LVCMOS33_16mA    | LVCMOS 3.3 16mA drive         | -0.11  | -0.18  | -0.218 | -0.32  | -0.325 | -0.46  | ns    |

| LVCMOS33_24mA    | LVCMOS 3.3 24mA drive         | -0.012 | -0.18  | -0.099 | -0.321 | -0.185 | -0.463 | ns    |

| LVCMOS25_4mA     | LVCMOS 2.5 4mA drive          | -0.174 | 0.004  | -0.195 | 0.002  | -0.215 | 0      | ns    |

| LVCMOS25_8mA     | LVCMOS 2.5 8mA drive          | 0      | 0      | 0      | 0      | 0      | 0      | ns    |

| LVCMOS25_12mA    | LVCMOS 2.5 12mA drive         | 0.094  | -0.025 | 0.107  | 0.096  | 0.12   | 0.216  | ns    |

| LVCMOS25_16mA    | LVCMOS 2.5 16mA drive         | 0.145  | -0.054 | 0.162  | 0.063  | 0.181  | 0.179  | ns    |

| LVCMOS25_OD      | LVCMOS 2.5 open drain         | 0.073  | -0.125 | 0.081  | -0.081 | 0.091  | -0.09  | ns    |

| LVCMOS18_4mA     | LVCMOS 1.8 4mA drive          | -0.278 | -0.099 | -0.312 | -0.115 | -0.345 | -0.131 | ns    |

| LVCMOS18_8mA     | LVCMOS 1.8 8mA drive          | -0.073 | -0.078 | -0.078 | -0.084 | -0.083 | -0.089 | ns    |

### **LatticeSC/M sysCONFIG Port Timing**

### **Over Recommended Operating Conditions**

| Parameter                | Description                                                         | Min.                 | Max.                 | Units           |

|--------------------------|---------------------------------------------------------------------|----------------------|----------------------|-----------------|

| General Configu          | ration Timing                                                       | •                    | •                    |                 |

| t <sub>SMODE</sub>       | M[3:0] Setup Time to INITN High                                     | 0                    | _                    | ns              |

| t <sub>HMODE</sub>       | M[3:0] Hold Time from INITN High                                    | 600                  | _                    | ns              |

| t <sub>RW</sub>          | RESETN Pulse Width Low to Start Reconfiguration (1.2 V)             | 50 (or 100 at 0.95V) | _                    | ns              |

| t <sub>PGW</sub>         | PROGRAMN Pulse Width Low to Start Reconfiguration (1.2 V)           | 50 (or 100 at 0.95V) | _                    | ns              |

| f <sub>ESB_CLK_FRQ</sub> | System Bus ESB_CLK Frequency (No Wait States)                       | _                    | 133                  | MHz             |

| sysCONFIG Mas            | ster Parallel Configuration Mode                                    | •                    | •                    |                 |

| t <sub>SMB</sub>         | D[7:0] Setup Time to RCLK High                                      | 6                    | _                    | ns              |

| t <sub>HMB</sub>         | D[7:0] Hold Time to RCLK High                                       | 0                    | _                    | ns              |

| +                        | RCLK Low Time (Non-compressed Bitstreams)                           | 0.5                  | 0.5                  | CCLK<br>periods |

| <sup>t</sup> CLMB        | RCLK Low Time (Compressed Bitstreams)                               | 0.5                  | 7.5                  | CCLK<br>periods |

| t <sub>CHMB</sub>        | RCLK High Time                                                      | 0.5                  | 0.5                  | CCLK<br>periods |

| sysCONFIG SPI            | Port                                                                |                      |                      |                 |

| t <sub>CFGX</sub>        | INITN High to CSCK Low                                              | _                    | 80                   | ns              |

| t <sub>CSSPI</sub>       | INITN High to CSSPIN Low                                            | 0                    | 2                    | μs              |

| t <sub>SCK</sub>         | CSCK Low before CSSPIN Low                                          | 0                    | _                    | ns              |

| t <sub>SOCDO</sub>       | CSCK Low to Output Valid                                            | _                    | 15                   | ns              |

| t <sub>CSPID</sub>       | CSSPIN Low to CSCK high Setup Time                                  | _                    | 15                   | ns              |

| f <sub>MAXSPI</sub>      | Max CCLK Frequency - SPI Flash Fast Read Opcode (0x0B) (SPIFASTN=0) | _                    | 50                   | MHz             |

| t <sub>SUSPI</sub>       | SOSPI/D0 Data Setup Time Before CSCK                                | 7                    | _                    | ns              |

| t <sub>HSPI</sub>        | SOSPI/D0 Data Hold Time After CSCK                                  | 2                    | _                    | ns              |

|                          | Master Clock Frequency                                              | Selected value - 30% | Selected value + 30% | MHz             |

|                          | Duty Cycle                                                          | 40                   | 60                   | %               |

| sysCONFIG Mas            | ster Serial Configuration Mode                                      |                      | ı                    |                 |

| t <sub>SMS</sub>         | DIN Setup Time                                                      | 4.4                  | _                    | ns              |

| t <sub>HMS</sub>         | DIN Hold Time                                                       | 0                    | _                    | ns              |

| f <sub>CMS</sub>         | CCLK Frequency (No Divider)                                         | 90                   | 190                  | MHz             |

| f <sub>C_DIV</sub>       | CCLK Frequency (Div 128)                                            | 0.70                 | 1.48                 | MHz             |

| t <sub>D</sub>           | CCLK to DOUT Delay                                                  | _                    | 7.5                  | ns              |

| sysCONFIG Mas            | ter Parallel Configuration Mode                                     | ·                    | l                    |                 |

| t <sub>AVMP</sub>        | RCLK to Address Valid                                               | _                    | 10                   | ns              |

| t <sub>SMP</sub>         | D[7:0] Setup Time to RCLK High                                      | 6                    | _                    | ns              |

| t <sub>HMP</sub>         | D[7:0] Hold Time to RCLK High                                       | 0                    | _                    | ns              |

|                          | RCLK Low Time (Non-compressed Bitstream)                            | 7.5                  | 7.5                  | CCLK            |

| t <sub>CLMP</sub>        | RCLK Low Time (Compressed Bitstream)                                | 0.5                  | 63.5                 | periods         |

| t <sub>CHMP</sub>        | RCLK High Time                                                      | 0.5                  | 0.5                  | CCLK<br>periods |

| t <sub>DMP</sub>         | CCLK to DOUT                                                        | _                    | 7.5                  | ns              |

### **LatticeSC/M sysCONFIG Port Timing (Continued)**

### **Over Recommended Operating Conditions**

| Parameter          | Description                             | Min.     | Max. | Units           |

|--------------------|-----------------------------------------|----------|------|-----------------|

| sysCONFIG Asy      | nchronous Peripheral Configuration Mode | <b>'</b> |      | •               |

| t <sub>WRAP</sub>  | WRN, CS0N and CS1 Pulse Width           | 5        | -    | ns              |

| t <sub>SAP</sub>   | D[7:0] Setup Time                       | 1.5      | -    | ns              |

| t <sub>RDYAP</sub> | RDY Delay                               |          | 8    | ns              |

| t <sub>BAP</sub>   | RDY Low                                 | 1        | 8    | CCLK<br>periods |

| t <sub>WR2AP</sub> | Earliest WRN After RDY Goes High        | 0        | _    | ns              |

| t <sub>DENAP</sub> | RDN to D[7:0] Enable/Disable            | _        | 7.5  | ns              |

| t <sub>DAP</sub>   | CCLK to DOUT                            | _        | 7.5  | ns              |

| sysCONFIG Slav     | ve Serial Configuration Mode            | <u>.</u> |      |                 |

| t <sub>SSS</sub>   | DIN Setup Time                          | 5.2      | _    | ns              |

| t <sub>HSS</sub>   | DIN Hold Time                           | 0        | _    | ns              |

| t <sub>CHSS</sub>  | CCLK High Time                          | 3.75     | _    | ns              |

| t <sub>CLSS</sub>  | CCLK Low Time                           | 3.75     | _    | ns              |

| f <sub>CSS</sub>   | CCLK Frequency                          |          | 150  | MHz             |

| t <sub>DSS</sub>   | CCLK to DOUT                            |          | 7.5  | ns              |

| sysCONFIG Slav     | ve Parallel Configuration Mode          | <u>.</u> |      |                 |

| t <sub>S1SP</sub>  | CS0N, CS1, WRN Setup Time               | 5.2      | _    | ns              |

| t <sub>H1SP</sub>  | CS0N, CS1, WRN Hold Time                | 0        | _    | ns              |

| t <sub>S2SP</sub>  | D[7:0] Setup Time                       | 5.2      | _    | ns              |

| t <sub>H2SP</sub>  | D[7:0] Hold Time                        | 0        | _    | ns              |

| t <sub>CHSP</sub>  | CCLK High Time                          | 3.75     | _    | ns              |

| t <sub>CL</sub>    | CCLK Low Time                           | 3.75     | _    | ns              |

| f <sub>CSP</sub>   | CCLK Frequency                          |          | 150  | MHz             |

### sysCONFIG MPI Port

|                          |                                                                   | -    | 7    | -    | 6    | -    | 5    |       |

|--------------------------|-------------------------------------------------------------------|------|------|------|------|------|------|-------|

| Parameter                | Description                                                       | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| t <sub>MPICTRL_SET</sub> | MPI Control (MPCSTRBN, MPCWRN, MPCCLK, etc.) to MPCCLK Setup Time | 4.9  | _    | 5.2  | _    | 5.5  | _    | ns    |

| t <sub>MPIADR_SET</sub>  | MPI Address to MPCCLK Setup Time                                  | 3.9  | _    | 4.2  | _    | 4.5  |      | ns    |

| t <sub>MPIDAT_SET</sub>  | MPI Write Data to MPCCLK Setup Time                               | 4.9  | _    | 5.2  |      | 5.5  |      | ns    |

| t <sub>MPIDPAR_SET</sub> | MPI Write Parity Data to MPCCLK Setup Time                        | 3.9  | _    | 4.2  | _    | 4.5  | _    | ns    |

| t <sub>MPI_HLD</sub>     | All Hold Times                                                    | 0    | _    | 0    | _    | 0    | _    | ns    |

| t <sub>MPICTRL_DEL</sub> | MPCCLK to MPI Control (MPCTA, MPCTEA, MPCRETRY)                   | _    | 5.6  | _    | 6.7  | _    | 8.7  | ns    |

| t <sub>MPIDAT_DEL</sub>  | MPCCLK to MPI Data                                                | _    | 5.6  |      | 6.7  |      | 8.7  | ns    |

| t <sub>MPIDPAR_DEL</sub> | MPCCLK to MPI Parity Data                                         | _    | 4.9  | _    | 5.7  |      | 7.7  | ns    |

| f <sub>MPI_CLK_FRQ</sub> | MPCCLK Frequency                                                  | _    | 100  | _    | 83   | _    | 66   | MHz   |

### LFSC/M15 Logic Signal Connections: 256 fpBGA<sup>1,2</sup> (Cont.)

|             | LFSC/M15      |            |                             |  |  |  |

|-------------|---------------|------------|-----------------------------|--|--|--|

| Ball Number | Ball Function | VCCIO Bank | Dual Function               |  |  |  |

| F14         | PR17A         | 2          | URC_DLLT_IN_C/URC_DLLT_FB_D |  |  |  |

| E15         | PR15B         | 2          | URC_PLLC_IN_A/URC_PLLC_FB_B |  |  |  |

| E14         | PR15A         | 2          | URC_PLLT_IN_A/URC_PLLT_FB_B |  |  |  |

| D9          | VCCJ          | -          |                             |  |  |  |

| C16         | TDO           | -          | TDO                         |  |  |  |

| B15         | TMS           | -          |                             |  |  |  |

| B16         | TCK           | -          |                             |  |  |  |

| E13         | TDI           | -          |                             |  |  |  |

| C14         | PROGRAMN      | 1          |                             |  |  |  |

| C15         | CCLK          | 1          |                             |  |  |  |

| A15         | PT43D         | 1          | HDC/SI                      |  |  |  |

| A14         | PT43C         | 1          | LDCN/SCS                    |  |  |  |

| B14         | PT41A         | 1          | CS1                         |  |  |  |

| E12         | PT39B         | 1          | CS0N                        |  |  |  |

| D13         | PT39A         | 1          | RDN                         |  |  |  |

| D12         | PT37D         | 1          | WRN                         |  |  |  |

| E10         | PT37C         | 1          | D7                          |  |  |  |

| C11         | PT37B         | 1          | D6                          |  |  |  |

| D10         | PT37A         | 1          | D5                          |  |  |  |

| A13         | PT36D         | 1          | D4                          |  |  |  |

| B12         | PT36C         | 1          | D3                          |  |  |  |

| A12         | PT35B         | 1          | D2                          |  |  |  |

| C12         | PT35A         | 1          | D1                          |  |  |  |

| A11         | PT33B         | 1          | D0                          |  |  |  |

| B11         | PT33A         | 1          | QOUT/CEON                   |  |  |  |

| E9          | PT32D         | 1          | VREF2_1                     |  |  |  |

| E8          | PT32B         | 1          | DOUT                        |  |  |  |

| D8          | PT28C         | 1          | BUSYN/RCLK/SCK              |  |  |  |

| A10         | PT27B         | 1          | PCLKC1_0                    |  |  |  |

| C10         | PT27A         | 1          | PCLKT1_0                    |  |  |  |

| E7          | PT21C         | 1          | VREF1_1                     |  |  |  |

| C9          | A_VDDIB3_L    | -          |                             |  |  |  |

| A9          | A_HDINP3_L    | -          | PCS 360 CH 3 IN P           |  |  |  |

| В9          | A_HDINN3_L    | -          | PCS 360 CH 3 IN N           |  |  |  |

| A8          | A_HDOUTP3_L   | -          | PCS 360 CH 3 OUT P          |  |  |  |

| B8          | A_HDOUTN3_L   | -          | PCS 360 CH 3 OUT N          |  |  |  |

| C8          | A_VDDOB3_L    | -          |                             |  |  |  |

| B7          | A_HDOUTN2_L   | -          | PCS 360 CH 2 OUT N          |  |  |  |

| C7          | A_VDDOB2_L    | -          |                             |  |  |  |

| A7          | A_HDOUTP2_L   | -          | PCS 360 CH 2 OUT P          |  |  |  |

| В6          | A_HDINN2_L    | -          | PCS 360 CH 2 IN N           |  |  |  |

| A6          | A_HDINP2_L    | -          | PCS 360 CH 2 IN P           |  |  |  |

| C6          | A_VDDIB2_L    | -          |                             |  |  |  |

### LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup> (Cont.)

|                |               | LFSC/M15      |               |               | LFSC/M25      |               |

|----------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Ball<br>Number | Ball Function | VCCIO<br>Bank | Dual Function | Ball Function | VCCIO<br>Bank | Dual Function |

| B29            | NC            | -             |               | NC            | -             |               |

<sup>1.</sup> Differential pair grouping within a PIC is A (True) and B (Complement) and C (True) and D (Complement).

<sup>2.</sup> The LatticeSC/M15 and LatticeSC/M25 in a 900-pin package supports a 16-bit MPI interface.

# LFSC/M25, LFSC/M40 Logic Signal Connections: 1020 fcBGA<sup>1, 2</sup> (Cont.)

|                | LFSC/M25 LFSC/M |            |                    |               | LFSC/M25 LFSC/M40 |                    |  |  |

|----------------|-----------------|------------|--------------------|---------------|-------------------|--------------------|--|--|

| Ball<br>Number | Ball Function   | VCCIO Bank | Dual Function      | Ball Function | VCCIO Bank        | Dual Function      |  |  |

| B30            | A_HDOUTN0_L     | -          | PCS 360 CH 0 OUT N | A_HDOUTN0_L   | -                 | PCS 360 CH 0 OUT N |  |  |

| D30            | A_VDDOB0_L      | -          |                    | A_VDDOB0_L    | -                 |                    |  |  |

| A30            | A_HDOUTP0_L     | -          | PCS 360 CH 0 OUT P | A_HDOUTP0_L   | -                 | PCS 360 CH 0 OUT P |  |  |

| C31            | A_HDINN0_L      | -          | PCS 360 CH 0 IN N  | A_HDINN0_L    | -                 | PCS 360 CH 0 IN N  |  |  |

| C32            | A_HDINP0_L      | -          | PCS 360 CH 0 IN P  | A_HDINP0_L    | -                 | PCS 360 CH 0 IN P  |  |  |

| B31            | A_VDDIB0_L      | -          |                    | A_VDDIB0_L    | -                 |                    |  |  |

| AL25           | NC              | -          |                    | PB26A         | 5                 |                    |  |  |

| AL24           | NC              | -          |                    | PB26B         | 5                 |                    |  |  |

| AG27           | NC              | -          |                    | PB26C         | 5                 |                    |  |  |

| AH27           | NC              | -          |                    | PB26D         | 5                 |                    |  |  |

| AM25           | NC              | -          |                    | PB27A         | 5                 |                    |  |  |

| AM24           | NC              | -          |                    | PB27B         | 5                 |                    |  |  |

| AL9            | NC              | -          |                    | PB62A         | 4                 |                    |  |  |

| AL8            | NC              | -          |                    | PB62B         | 4                 |                    |  |  |

| AK9            | NC              | -          |                    | PB63A         | 4                 |                    |  |  |

| AJ9            | NC              | -          |                    | PB63B         | 4                 |                    |  |  |

| AG10           | NC<br>NC        | -          |                    | PB63C         | 4                 |                    |  |  |

| AG10<br>AG11   | NC<br>NC        | -          |                    | PB63D         | 4                 |                    |  |  |

|                |                 |            |                    |               | 7                 |                    |  |  |

| J30            | NC              | -          |                    | PL26A         | 7                 |                    |  |  |

| H30            | NC              | -          |                    | PL26B         |                   |                    |  |  |

| M28            | NC              | -          |                    | PL26C         | 7                 |                    |  |  |

| N28            | NC              | -          |                    | PL26D         | 7                 |                    |  |  |

| J32            | NC              | -          |                    | PL27A         | 7                 |                    |  |  |

| J31            | NC              | -          |                    | PL27B         | 7                 |                    |  |  |

| N26            | NC              | -          |                    | PL27C         | 7                 |                    |  |  |

| N27            | NC              | -          |                    | PL27D         | 7                 |                    |  |  |

| K31            | NC              | -          |                    | PL29A         | 7                 |                    |  |  |

| K32            | NC              | -          |                    | PL29B         | 7                 |                    |  |  |

| P25            | NC              | -          |                    | PL29C         | 7                 |                    |  |  |

| P26            | NC              | -          |                    | PL29D         | 7                 |                    |  |  |

| L27            | NC              | -          |                    | PL22C         | 7                 |                    |  |  |

| L28            | NC              | -          |                    | PL22D         | 7                 |                    |  |  |

| M29            | NC              | -          |                    | PL30A         | 7                 |                    |  |  |

| L29            | NC              | -          |                    | PL30B         | 7                 |                    |  |  |

| M30            | NC              | -          |                    | PL31A         | 7                 |                    |  |  |

| L30            | NC              | -          |                    | PL31B         | 7                 |                    |  |  |

| L31            | NC              | -          |                    | PL34A         | 7                 |                    |  |  |

| M31            | NC              | -          |                    | PL34B         | 7                 |                    |  |  |

| AA29           | NC              | -          |                    | PL56A         | 6                 |                    |  |  |

| AA30           | NC              | -          |                    | PL56B         | 6                 |                    |  |  |

| AB31           | NC              | -          |                    | PL57A         | 6                 |                    |  |  |

| AA31           | NC              | -          |                    | PL57B         | 6                 |                    |  |  |

| AG30           | NC              | -          |                    | PL57C         | 6                 |                    |  |  |

| AG29           | NC              | -          |                    | PL57D         | 6                 |                    |  |  |

| AB29           | NC              | -          |                    | PL58A         | 6                 |                    |  |  |

| AB30           | NC              | -          |                    | PL58B         | 6                 |                    |  |  |

| Y25            | NC              | -          |                    | PL58C         | 6                 |                    |  |  |

| AA25           | NC              | -          |                    | PL58D         | 6                 |                    |  |  |

| AA8            | NC              | -          |                    | PR58D         | 3                 |                    |  |  |

| Y8             | NC              | -          |                    | PR58C         | 3                 |                    |  |  |

### LFSC/M40, LFSC/M80 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup> (Cont.)

|                |                  | LFSC/M40      |               |                  | LFSC/M80      |               |  |

|----------------|------------------|---------------|---------------|------------------|---------------|---------------|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual Function | Ball<br>Function | VCCIO<br>Bank | Dual Function |  |

| AG18           | PB42C            | 5             |               | PB61C            | 5             |               |  |

| AF18           | PB42D            | 5             |               | PB61D            | 5             |               |  |

| AP19           | PB43A            | 5             |               | PB63A            | 5             |               |  |

| AP18           | PB43B            | 5             |               | PB63B            | 5             |               |  |

| AJ18           | PB43C            | 5             |               | PB63C            | 5             |               |  |

| AH18           | PB43D            | 5             |               | PB63D            | 5             |               |  |

| AP17           | PB45A            | 4             |               | PB65A            | 4             |               |  |

| AP16           | PB45B            | 4             |               | PB65B            | 4             |               |  |

| AJ17           | PB45C            | 4             |               | PB65C            | 4             |               |  |

| AH17           | PB45D            | 4             |               | PB65D            | 4             |               |  |

| AN17           | PB46A            | 4             |               | PB66A            | 4             |               |  |

| AN16           | PB46B            | 4             |               | PB66B            | 4             |               |  |

| AE17           | PB46C            | 4             |               | PB66C            | 4             |               |  |

| AD17           | PB46D            | 4             |               | PB66D            | 4             |               |  |

| AK17           | PB47A            | 4             |               | PB67A            | 4             |               |  |

| AK16           | PB47B            | 4             |               | PB67B            | 4             |               |  |

| AG17           | PB47C            | 4             |               | PB67C            | 4             |               |  |

| AF17           | PB47D            | 4             |               | PB67D            | 4             |               |  |

| AM16           | PB49A            | 4             |               | PB69A            | 4             |               |  |

| AM15           | PB49B            | 4             |               | PB69B            | 4             |               |  |

| AJ15           | PB49C            | 4             |               | PB69C            | 4             |               |  |

| AJ14           | PB49D            | 4             |               | PB69D            | 4             |               |  |

| AL16           | PB50A            | 4             |               | PB70A            | 4             |               |  |

| AL15           | PB50B            | 4             |               | PB70B            | 4             |               |  |

| AG16           | PB50C            | 4             |               | PB70C            | 4             |               |  |

| AF16           | PB50D            | 4             |               | PB70D            | 4             |               |  |

| AP15           | PB51A            | 4             |               | PB71A            | 4             |               |  |

| AP14           | PB51B            | 4             |               | PB71B            | 4             |               |  |

| AH15           | PB51C            | 4             |               | PB71C            | 4             |               |  |

| AH14           | PB51D            | 4             |               | PB71D            | 4             |               |  |

| AN15           | PB53A            | 4             | PCLKT4_2      | PB74A            | 4             | PCLKT4_2      |  |

| AN14           | PB53B            | 4             | PCLKC4_2      | PB74B            | 4             | PCLKC4_2      |  |

| AE16           | PB53C            | 4             | PCLKT4_7      | PB74C            | 4             | PCLKT4_7      |  |

| AD16           | PB53D            | 4             | PCLKC4_7      | PB74D            | 4             | PCLKC4_7      |  |

| AK15           | PB54A            | 4             | PCLKT4_1      | PB75A            | 4             | PCLKT4_1      |  |

| AK14           | PB54B            | 4             | PCLKC4_1      | PB75B            | 4             | PCLKC4_1      |  |

| AG15           | PB54C            | 4             | PCLKT4_6      | PB75C            | 4             | PCLKT4_6      |  |

| AG14           | PB54D            | 4             | PCLKC4_6      | PB75D            | 4             | PCLKC4_6      |  |

| AM13           | PB55A            | 4             | PCLKT4_0      | PB77A            | 4             | PCLKT4_0      |  |

| AM12           | PB55B            | 4             | PCLKC4_0      | PB77B            | 4             | PCLKC4_0      |  |

| AJ12           | PB55C            | 4             | VREF2_4       | PB77C            | 4             | VREF2_4       |  |

| AJ11           | PB55D            | 4             |               | PB77D            | 4             |               |  |

| AL13           | PB57A            | 4             | PCLKT4_5      | PB79A            | 4             | PCLKT4_5      |  |

| AL12           | PB57B            | 4             | PCLKC4_5      | PB79B            | 4             | PCLKC4_5      |  |

| AH12           | PB57C            | 4             |               | PB79C            | 4             |               |  |

# LFSC/M40, LFSC/M80 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup> (Cont.)

|                | LFSC/M40         |               |               |                  | LFSC/M80                                         |               |

|----------------|------------------|---------------|---------------|------------------|--------------------------------------------------|---------------|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual Function | Ball<br>Function | VCCIO<br>Bank                                    | Dual Function |

| K20            | GND              | -             |               | GND              | -                                                |               |

| K23            | GND              | -             |               | GND              | -                                                |               |

| K26            | GND              | -             |               | GND              | -                                                |               |

| K28            | GND              | -             |               | GND              | -                                                |               |

| K6             | GND              | -             |               | GND              | -                                                |               |

| K9             | GND              | -             |               | GND              | -                                                |               |

| L12<br>L32     | GND<br>GND       | -             |               | GND<br>GND       | -                                                |               |

| L32            | GND              | -             |               | GND              | -                                                |               |

| M10            | GND              |               |               | GND              | + -                                              |               |

| M17            | GND              | _             |               | GND              | <del>  -</del>                                   |               |

| M24            | GND              | _             |               | GND              | <del>                                     </del> |               |

| N29            | GND              | _             |               | GND              | _                                                |               |

| N7             | GND              | _             |               | GND              | <del> </del> -                                   |               |

| P15            | GND              | -             |               | GND              | -                                                |               |

| P20            | GND              | -             |               | GND              | -                                                |               |

| P3             | GND              | -             |               | GND              | -                                                |               |

| P31            | GND              | -             |               | GND              | -                                                |               |

| R10            | GND              | -             |               | GND              | -                                                |               |

| R14            | GND              | -             |               | GND              | -                                                |               |

| R16            | GND              | -             |               | GND              | -                                                |               |

| R19            | GND              | -             |               | GND              | -                                                |               |

| R21            | GND              | -             |               | GND              | -                                                |               |

| R26            | GND              | -             |               | GND              | -                                                |               |

| T15            | GND              | -             |               | GND              | -                                                |               |

| T17            | GND              | -             |               | GND              | -                                                |               |

| T18            | GND              | -             |               | GND              | -                                                |               |

| T20            | GND              | -             |               | GND              | -                                                |               |

| T28            | GND              | -             |               | GND              | -                                                |               |

| Т6             | GND              | -             |               | GND              | -                                                |               |

| U16            | GND              | -             |               | GND              | -                                                |               |

| U19            | GND              | -             |               | GND              | -                                                |               |

| U23            | GND              | -             |               | GND              | -                                                |               |

| U32            | GND              | -             |               | GND              | -                                                |               |

| U4             | GND              | -             |               | GND              | -                                                |               |

| V12<br>V16     | GND<br>GND       | -             |               | GND<br>GND       | -                                                |               |

| V16<br>V19     | GND              | -             |               | GND              | -                                                |               |

| V19<br>V3      | GND              | -             |               | GND              | -                                                |               |

| V31            | GND              | <u> </u>      |               | GND              | + -                                              |               |

| W15            | GND              | _             |               | GND              | _                                                |               |

| W17            | GND              | _             |               | GND              | -                                                |               |

| W18            | GND              | _             |               | GND              | -                                                |               |

| W20            | GND              | -             |               | GND              | -                                                |               |

| W29            | GND              | -             |               | GND              | -                                                |               |

| 0              | J. 1D            | l             |               | 5110             |                                                  |               |

### LFSC/M80, LFSC/M115 Logic Signal Connections: 1704 fcBGA<sup>1, 2</sup> (Cont.)

|                |                  | LFS           | C/M80            |                  | ı             | LFSC/M115        |

|----------------|------------------|---------------|------------------|------------------|---------------|------------------|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function |

| AC24           | GND              | -             |                  | GND              | -             |                  |

| AC26           | GND              | -             |                  | GND              | -             |                  |

| AC35           | GND              | -             |                  | GND              | -             |                  |

| AC8            | GND              | -             |                  | GND              | -             |                  |

| AD12           | GND              | -             |                  | GND              | -             |                  |

| AD16           | GND              | -             |                  | GND              | -             |                  |

| AD18           | GND              | -             |                  | GND              | -             |                  |

| AD20           | GND              | -             |                  | GND              | -             |                  |

| AD23           | GND              | -             |                  | GND              | -             |                  |

| AD25           | GND              | -             |                  | GND              | -             |                  |

| AD27           | GND              | -             |                  | GND              | -             |                  |

| AD31           | GND              | -             |                  | GND              | -             |                  |

| AE17           | GND              | -             |                  | GND              | -             |                  |

| AE19           | GND              | -             |                  | GND              | -             |                  |

| AE24           | GND              | -             |                  | GND              | -             |                  |

| AE26           | GND              | -             |                  | GND              | -             |                  |

| AE3            | GND              | -             |                  | GND              | -             |                  |

| AE39           | GND              | -             |                  | GND              | -             |                  |

| AF18           | GND              | -             |                  | GND              | -             |                  |

| AF20           | GND              | -             |                  | GND              | -             |                  |

| AF23           | GND              | -             |                  | GND              | -             |                  |

| AF25           | GND              | -             |                  | GND              | -             |                  |

| AF36           | GND              | -             |                  | GND              | -             |                  |

| AF7            | GND              | -             |                  | GND              | -             |                  |

| AG11           | GND              | -             |                  | GND              | -             |                  |

| AG16           | GND              | -             |                  | GND              | -             |                  |

| AG19           | GND              | -             |                  | GND              | -             |                  |

| AG24           | GND              | -             |                  | GND              | -             |                  |

| AG27           | GND              | -             |                  | GND              | -             |                  |

| AG32           | GND              | -             |                  | GND              | -             |                  |

| AH15           | GND              | -             |                  | GND              | -             |                  |

| AH28           | GND              | -             |                  | GND              | -             |                  |

| AH4            | GND              | -             |                  | GND              | -             |                  |

| AH40           | GND              | -             |                  | GND              | -             |                  |

| AJ35           | GND              | -             |                  | GND              | -             |                  |

| AJ8            | GND              | -             |                  | GND              | -             |                  |

| AK12           | GND              | -             |                  | GND              | -             |                  |

| AK31           | GND              | -             |                  | GND              | -             |                  |

| AL13           | GND              | -             |                  | GND              | -             |                  |

| AL19           | GND              | -             |                  | GND              | -             |                  |

| AL24           | GND              | -             |                  | GND              | -             |                  |

| AL3            | GND              | -             |                  | GND              | -             |                  |

| AL30           | GND              | -             |                  | GND              | -             |                  |

| AL39           | GND              | -             |                  | GND              | -             |                  |

| AM16           | GND              | -             |                  | GND              | -             |                  |

### Commercial, Cont.

| Part Number                      | Grade | Package       | Balls | Temp. | LUTs (K) |

|----------------------------------|-------|---------------|-------|-------|----------|

| LFSC3GA80E-7FC1152C <sup>1</sup> | -7    | Ceramic fcBGA | 1152  | COM   | 80.1     |

| LFSC3GA80E-6FC1152C <sup>1</sup> | -6    | Ceramic fcBGA | 1152  | COM   | 80.1     |

| LFSC3GA80E-5FC1152C1             | -5    | Ceramic fcBGA | 1152  | COM   | 80.1     |

| LFSC3GA80E-7FF1152C              | -7    | Organic fcBGA | 1152  | COM   | 80.1     |

| LFSC3GA80E-6FF1152C              | -6    | Organic fcBGA | 1152  | COM   | 80.1     |

| LFSC3GA80E-5FF1152C              | -5    | Organic fcBGA | 1152  | COM   | 80.1     |

| LFSC3GA80E-7FC1704C <sup>1</sup> | -7    | Ceramic fcBGA | 1704  | COM   | 80.1     |

| LFSC3GA80E-6FC1704C <sup>1</sup> | -6    | Ceramic fcBGA | 1704  | COM   | 80.1     |

| LFSC3GA80E-5FC1704C1             | -5    | Ceramic fcBGA | 1704  | COM   | 80.1     |

| LFSC3GA80E-7FF1704C              | -7    | Organic fcBGA | 1704  | COM   | 80.1     |

| LFSC3GA80E-6FF1704C              | -6    | Organic fcBGA | 1704  | COM   | 80.1     |

| LFSC3GA80E-5FF1704C              | -5    | Organic fcBGA | 1704  | COM   | 80.1     |

<sup>1.</sup> Converted to organic flip-chip BGA package per PCN #01A-10.

| Part Number                         | Grade | Package       | Balls | Temp. | LUTs (K) |

|-------------------------------------|-------|---------------|-------|-------|----------|

| LFSCM3GA80EP1-7FC1152C1             | -7    | Ceramic fcBGA | 1152  | COM   | 80.1     |

| LFSCM3GA80EP1-6FC1152C1             | -6    | Ceramic fcBGA | 1152  | COM   | 80.1     |

| LFSCM3GA80EP1-5FC1152C1             | -5    | Ceramic fcBGA | 1152  | COM   | 80.1     |

| LFSCM3GA80EP1-7FF1152C              | -7    | Organic fcBGA | 1152  | COM   | 80.1     |

| LFSCM3GA80EP1-6FF1152C              | -6    | Organic fcBGA | 1152  | COM   | 80.1     |

| LFSCM3GA80EP1-5FF1152C              | -5    | Organic fcBGA | 1152  | COM   | 80.1     |

| LFSCM3GA80EP1-7FC1704C <sup>1</sup> | -7    | Ceramic fcBGA | 1704  | COM   | 80.1     |

| LFSCM3GA80EP1-6FC1704C1             | -6    | Ceramic fcBGA | 1704  | COM   | 80.1     |

| LFSCM3GA80EP1-5FC1704C <sup>1</sup> | -5    | Ceramic fcBGA | 1704  | COM   | 80.1     |

| LFSCM3GA80EP1-7FF1704C              | -7    | Organic fcBGA | 1704  | COM   | 80.1     |

| LFSCM3GA80EP1-6FF1704C              | -6    | Organic fcBGA | 1704  | COM   | 80.1     |

| LFSCM3GA80EP1-5FF1704C              | -5    | Organic fcBGA | 1704  | COM   | 80.1     |

<sup>1.</sup> Converted to organic flip-chip BGA package per PCN #01A-10.

| Part Number                       | Grade | Package       | Balls | Temp. | LUTs (K) |

|-----------------------------------|-------|---------------|-------|-------|----------|

| LFSC3GA115E-6FC1152C <sup>1</sup> | -6    | Ceramic fcBGA | 1152  | COM   | 115.2    |

| LFSC3GA115E-5FC1152C1             | -5    | Ceramic fcBGA | 1152  | COM   | 115.2    |

| LFSC3GA115E-6FF1152C              | -6    | Organic fcBGA | 1152  | COM   | 115.2    |

| LFSC3GA115E-5FF1152C              | -5    | Organic fcBGA | 1152  | COM   | 115.2    |

| LFSC3GA115E-6FC1704C <sup>1</sup> | -6    | Ceramic fcBGA | 1704  | COM   | 115.2    |

| LFSC3GA115E-5FC1704C <sup>1</sup> | -5    | Ceramic fcBGA | 1704  | COM   | 115.2    |

| LFSC3GA115E-6FF1704C              | -6    | Organic fcBGA | 1704  | COM   | 115.2    |

| LFSC3GA115E-5FF1704C              | -5    | Organic fcBGA | 1704  | COM   | 115.2    |

<sup>1.</sup> Converted to organic flip-chip BGA package per PCN #01A-10.

#### Industrial

| Part Number       | Grade | Package | Balls | Temp. | LUTs (K) |

|-------------------|-------|---------|-------|-------|----------|

| LFSC3GA15E-6F256I | -6    | fpBGA   | 256   | IND   | 15.2     |

| LFSC3GA15E-5F256I | -5    | fpBGA   | 256   | IND   | 15.2     |

| LFSC3GA15E-6F900I | -6    | fpBGA   | 900   | IND   | 15.2     |

| LFSC3GA15E-5F900I | -5    | fpBGA   | 900   | IND   | 15.2     |

| Part Number          | Grade | Package | Balls | Temp. | LUTs (K) |

|----------------------|-------|---------|-------|-------|----------|

| LFSCM3GA15EP1-6F256I | -6    | fpBGA   | 256   | IND   | 15.2     |

| LFSCM3GA15EP1-5F256I | -5    | fpBGA   | 256   | IND   | 15.2     |

| LFSCM3GA15EP1-6F900I | -6    | fpBGA   | 900   | IND   | 15.2     |

| LFSCM3GA15EP1-5F900I | -5    | fpBGA   | 900   | IND   | 15.2     |

| Part Number                      | Grade | Package                  | Balls | Temp. | LUTs (K) |

|----------------------------------|-------|--------------------------|-------|-------|----------|

| LFSC3GA25E-6F900I                | -6    | fpBGA                    | 900   | IND   | 25.4     |

| LFSC3GA25E-5F900I                | -5    | fpBGA                    | 900   | IND   | 25.4     |

| LFSC3GA25E-6FF1020I <sup>1</sup> | -6    | Organic fcBGA            | 1020  | IND   | 25.4     |

| LFSC3GA25E-5FF1020I <sup>1</sup> | -5    | Organic fcBGA            | 1020  | IND   | 25.4     |

| LFSC3GA25E-6FFA1020I             | -6    | Organic fcBGA Revision 2 | 1020  | IND   | 25.4     |

| LFSC3GA25E-5FFA1020I             | -5    | Organic fcBGA Revision 2 | 1020  | IND   | 25.4     |

<sup>1.</sup> Converted to organic flip-chip BGA package revision 2 per PCN #02A-10.

| Part Number                         | Grade | Package                  | Balls | Temp. | LUTs (K) |

|-------------------------------------|-------|--------------------------|-------|-------|----------|

| LFSCM3GA25EP1-6F900I                | -6    | fpBGA                    | 900   | IND   | 25.4     |

| LFSCM3GA25EP1-5F900I                | -5    | fpBGA                    | 900   | IND   | 25.4     |

| LFSCM3GA25EP1-6FF1020I <sup>1</sup> | -6    | Organic fcBGA            | 1020  | IND   | 25.4     |

| LFSCM3GA25EP1-5FF1020I <sup>1</sup> | -5    | Organic fcBGA            | 1020  | IND   | 25.4     |

| LFSCM3GA25EP1-6FFA1020I             | -6    | Organic fcBGA Revision 2 | 1020  | IND   | 25.4     |

| LFSCM3GA25EP1-5FFA1020I             | -5    | Organic fcBGA Revision 2 | 1020  | IND   | 25.4     |

<sup>1.</sup> Converted to organic flip-chip BGA package revision 2 per PCN #02A-10.

| Part Number                      | Grade | Package                  | Balls | Temp. | LUTs (K) |

|----------------------------------|-------|--------------------------|-------|-------|----------|

| LFSC3GA40E-6FF1020I <sup>1</sup> | -6    | Organic fcBGA            | 1020  | IND   | 40.4     |

| LFSC3GA40E-5FF1020I <sup>1</sup> | -5    | Organic fcBGA            | 1020  | IND   | 40.4     |

| LFSC3GA40E-6FFA1020I             | -6    | Organic fcBGA Revision 2 | 1020  | IND   | 40.4     |

| LFSC3GA40E-5FFA1020I             | -5    | Organic fcBGA Revision 2 | 1020  | IND   | 40.4     |

| LFSC3GA40E-6FC1152I <sup>2</sup> | -6    | Ceramic fcBGA            | 1152  | IND   | 40.4     |

| LFSC3GA40E-5FC1152I <sup>2</sup> | -5    | Ceramic fcBGA            | 1152  | IND   | 40.4     |

| LFSC3GA40E-6FF1152I              | -6    | Organic fcBGA            | 1152  | IND   | 40.4     |

| LFSC3GA40E-5FF1152I              | -5    | Organic fcBGA            | 1152  | IND   | 40.4     |

<sup>1.</sup> Converted to organic flip-chip BGA package revision 2 per PCN #02A-10.

<sup>2.</sup> Converted to organic flip-chip BGA package per PCN #01A-10.

# LatticeSC/M Family Data Sheet Revision History

December 2011 Data Sheet DS1004

| Date          | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                              |

|---------------|---------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2006 | 01.0    | _                                   | Initial release.                                                                                                                                                                                                                                                                                                                            |

| March 2006    | 01.1    | Introduction                        | SC25 1020 I/O count changed to 476.                                                                                                                                                                                                                                                                                                         |

|               |         | Architecture                        | Changed ROM 16X4 to ROM 16X2.                                                                                                                                                                                                                                                                                                               |

|               |         |                                     | Changed "X2 or X4" to "DIV2 or DIV4".                                                                                                                                                                                                                                                                                                       |

|               |         |                                     | Added Global Set/Reset Section.                                                                                                                                                                                                                                                                                                             |

|               |         | DC and Switching                    | Added notes 5 and 6 to Recommended Operating Conditions table.                                                                                                                                                                                                                                                                              |

|               |         | Characteristics                     | Added Power Supply Ramp Rates table.                                                                                                                                                                                                                                                                                                        |