Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                |

|--------------------------------|--------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                       |

| Number of LABs/CLBs            | 20000                                                                          |

| Number of Logic Elements/Cells | 80000                                                                          |

| Total RAM Bits                 | 5816320                                                                        |

| Number of I/O                  | 904                                                                            |

| Number of Gates                | -                                                                              |

| Voltage - Supply               | 0.95V ~ 1.26V                                                                  |

| Mounting Type                  | Surface Mount                                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                |

| Package / Case                 | 1704-BCBGA, FCBGA                                                              |

| Supplier Device Package        | 1704-CFCBGA (42.5x42.5)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfsc3ga80e-7fc1704c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

DLLs and dynamic glitch free clock MUXs which are required in today's high end system designs. High-speed, high-bandwidth I/O make this family ideal for high-throughput systems.

The ispLEVER® design tool from Lattice allows large complex designs to be efficiently implemented using the LatticeSC family of FPGA devices. Synthesis library support for LatticeSC is available for popular logic synthesis tools. The ispLEVER tool uses the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeSC device. The ispLEVER tool extracts the timing from the routing and backannotates it into the design for timing verification.

Lattice provides many pre-designed IP (Intellectual Property) ispLeverCORE™ modules for the LatticeSC family. By using these IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

Innovative high-performance FPGA architecture, high-speed SERDES with PCS support, sysMEM embedded memory and high performance I/O are combined in the LatticeSC to provide excellent performance for today's leading edge systems designs. Table 1-3 details the performance of several common functions implemented within the LatticeSC.

Table 1-3. Speed Performance for Typical Functions<sup>1</sup>

| Functions                                         | Performance (MHz) <sup>2</sup> |

|---------------------------------------------------|--------------------------------|

| 32-bit Address Decoder                            | 539                            |

| 64-bit Address Decoder                            | 517                            |

| 32:1 Multiplexer                                  | 779                            |

| 64-bit Adder (ripple)                             | 353                            |

| 32x8 Distributed Single Port (SP) RAM             | 768                            |

| 64-bit Counter (up or down counter, non-loadable) | 369                            |

| True Dual-Port 1024x18 bits                       | 372                            |

| FIFO Port A: x36 bits, B: x9 bits                 | 375                            |

For additional information, see Typical Building BLock Function Performance table in this data sheet.

<sup>2.</sup> Advance information (-7 speed grade).

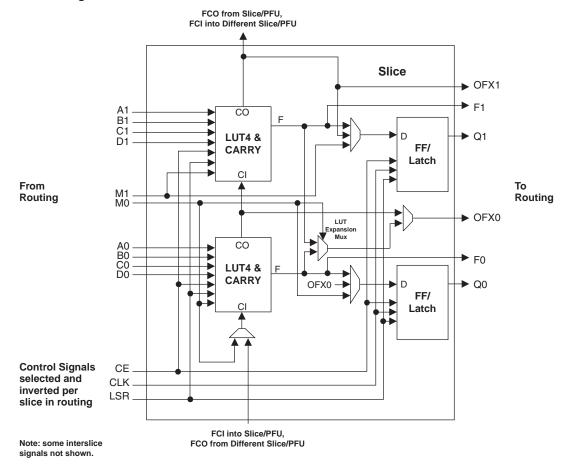

Figure 2-3. Slice Diagram

Table 2-1. Slice Signal Descriptions

| Function | Туре             | Signal Names   | Description                                                          |

|----------|------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal      | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal      | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose    | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose    | M1             | Multipurpose Input                                                   |

| Input    | Control signal   | CE             | Clock Enable                                                         |

| Input    | Control signal   | LSR            | Local Set/Reset                                                      |

| Input    | Control signal   | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal | FCI            | Fast Carry In <sup>1</sup>                                           |

| Output   | Data signals     | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals     | Q0, Q1         | Register Outputs                                                     |

| Output   | Data signals     | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals     | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal | FCO            | For the right most PFU the fast carry chain output <sup>2</sup>      |

<sup>1.</sup> See Figure 2-2 for connection details.

<sup>2.</sup> Requires two PFUs.

#### **PFU Modes of Operation**

Slices can be combined within a PFU to form larger functions. Table 2-4 tabulates these modes and documents the functionality possible at the PFU level.

Table 2-4. PFU Modes of Operation

| Logic                      | Ripple            | RAM                          | ROM          |

|----------------------------|-------------------|------------------------------|--------------|

| LUT 4x8 or<br>MUX 2x1 x 8  | 2-bit Add x 4     | SPR 16x2 x 4<br>DPR 16x2 x 2 | ROM 16x1 x 8 |

| LUT 5x4 or<br>MUX 4x1 x 4  | 2-bit Sub x 4     | SPR 16x4 x 2<br>DPR 16x4 x 1 | ROM 16x2 x 4 |

| LUT 6x2 or<br>MUX 8x1 x 2  | 2-bit Counter x 4 | SPR 16x8 x 1                 | ROM 16x4 x 2 |

| LUT 7x1 or<br>MUX 16x1 x 1 | 2-bit Comp x 4    |                              | ROM 16x8 x1  |

### Routing

There are many resources provided in the LatticeSC devices to route signals individually or as busses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with x1 (spans two PFU), x2 (spans three PFU) and x6 (spans seven PFU) resources. The x1 and x2 connections provide fast and efficient connections in horizontal, vertical and diagonal directions. All connections are buffered to ensure high-speed operation even with long high-fanout connections.

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

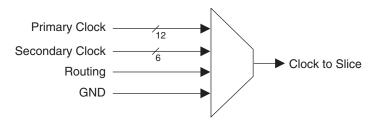

## sysCLOCK Network

The LatticeSC devices have three distinct clock networks for use in distributing high-performance clocks within the device: primary clocks, secondary clocks and edge clocks. In addition to these dedicated clock networks, users are free to route clocks within the device using the general purpose routing. Figure 2-4 shows the clock resources available to each slice.

Figure 2-4. Slice Clock Selection

Note: GND is available to switch off the network.

#### **Primary Clock Sources**

LatticeSC devices have a wide variety of primary clock sources available. Primary clocks sources consists of the following:

- · Primary clock input pins

- · Edge clock input pins

- Two outputs per DLL

The setup and hold times of the device can be improved by programming a delay in the feedback or input path of the PLL which will advance or delay the output clock with reference to the input clock. This delay can be either programmed during configuration or can be adjusted dynamically.

The Phase Select block can modify the phase of the clock signal if desired. The Spread Spectrum block supports the modulation of the PLL output frequency. This reduces the peak energy in the fundamental and its harmonics providing for lower EMI (Electro Magnetic Interference).

The sysCLOCK PLL can be configured at power-up and then, if desired, reconfigured dynamically through the serial memory interface bus which connects with the on-chip system bus. For example, the user can select inputs, loop filters, divider setting, delay settings and phase shift settings. The user can also directly access the SMI bus through the routing.

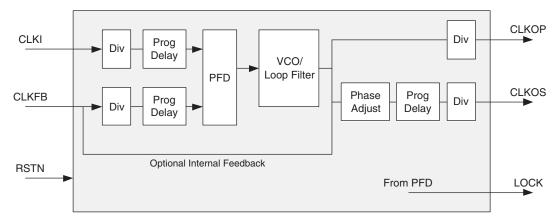

The PLL clock input, from pin or routing, feeds into an input divider. There are four sources of feedback signal to the feedback divider: from the clock net, directly from the voltage controlled oscillator (VCO) output, from the routing or from an external pin. The signal from the input clock divider and the feedback divider are passed through the programmable delay before entering the phase frequency detector (PFD) unit. The output of this PFD is used to control the voltage controlled oscillator. There is a PLL\_LOCK signal to indicate that VCO has locked on to the input clock signal. Figure 2-11 shows the sysCLOCK PLL diagram.

Figure 2-11. PLL Diagram

For more information on the PLL, please see details of additional technical documentation at the end of this data sheet.

## **Spread Spectrum Clocking (SSC)**

The PLL supports spread spectrum clocking to reduce peak EMI by using "down-spread" modulation. The spread spectrum operation will vary the output frequency (at 30KHz to 500KHz) in a range that is between its nominal value, down to a frequency that is a programmable 1%, 2%, or 3% lower than normal.

## Digital Locked Loop (DLLs)

In addition to PLLs, the LatticeSC devices have up to 12 DLLs per device. DLLs assist in the management of clocks and strobes. DLLs are well suited to applications where the clock may be stopped or transferring jitter from input to output is important, for example forward clocked interfaces. PLLs are good for applications requiring the lowest output jitter or jitter filtering. All DLL outputs are routed as primary/edge clock sources.

The DLL has two independent clock outputs, CLKOP and CLKOS. These outputs can individually select one of the outputs from the tapped delay line. The CLKOS has optional fine phase shift and divider blocks to allow this output to be further modified, if required. The fine phase shift block allows the CLKOS output to phase shifted a further 45, 22.5 or 11.25 degrees relative to its normal position. LOCK output signal is asserted when the DLL is locked. The ALU HOLD signal setting allows users to freeze the DLL at its current delay setting.

#### **EBR Asynchronous Reset**

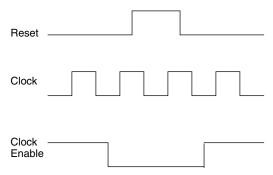

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the low-to-high transition of the reset, as shown in Figure 2-16.

Figure 2-16. EBR Asynchronous Reset (Including GSR) Timing Diagram

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device Wake Up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM, FIFO and shift register implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-16. The reset timing rules apply to the RPReset input vs. the RE input and the RST input vs. the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs. For the EBR shift register mode, the GSR signal is always enabled and the local RESET pin is always asynchronous.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled. For more information about on-chip memory, see TN1094, On-Chip Memory Usage Guide for LatticeSC Devices.

## Programmable I/O Cells (PIC)

Each PIC contains four PIOs connected to their respective PURESPEED I/O Buffer which are then connected to the PADs as shown in Figure 2-17. The PIO Block supplies the output data (DO) and the Tri-state control signal (TO) to PURESPEED I/O buffer, and receives input (DI) from the buffer. The PIO contains advanced capabilities to allow the support of speeds up to 2Gbps. These include dedicated shift and DDR logic and adaptive input logic. The dedicated resources simplify the design of robust interfaces.

From paired PIO To paired PIO for wide muxing for wide muxing Bypass used for DDR IPOS0 (Can act as IPOS2 Data Input when paired) (From Delay Block) IPOS1 (Can act as IPOS3 when paired) **HCLKIN** LCLKIN POS Update **NEG Update** Bypass used for DDR INEG0 (Can act as INEG2 when paired) Used for DDR with Half Clock Transfer INEG1 (Can act as INEG3 when paired) From paired PIO for wide muxing To paired PIO for wide muxing

Figure 2-21. Input DDR/Shift Register Block

#### **Output Register Block**

The output register block provides the ability to register signals from the core of the device before they are passed to the PURESPEED I/O buffers. The block contains a register for SDR operation and a group of registers for DDR and shift register operation. The output signal (DO) can be derived directly from one of the inputs (bypass mode), the SDR register or the DDR/shift register block. Figure 2-22 shows the diagram of the Output Register Block.

#### **Output SDR Register/Latch Block**

The SDR register operates on the positive edge of the high-speed clock. It has clock enable that is driven by the clock enable output signal generated by the control MUX. In addition it has a variety of programmable options for set/reset including, set or reset, asynchronous or synchronous Local Set Reset LSR (LSR has precedence over CE) and Global Set Reset GSR enable or disable. The register LSR input is driven from LSRO, which is generated from the PIO control MUX. The GSR inputs is driven from the GSR output of the PIO control MUX, which allows the global set-reset to be disabled on a PIO basis.

#### **Output DDR/Shift Block**

The DDR/Shift block contains registers and associated logic that support DDR and shift register functions using the high-speed clock and the associated transfer from the low-speed clock domain. It functions as a gearbox allowing low-speed parallel data from the FPGA fabric be output as a higher speed serial stream. Each PIO supports DDR and x2 shift functions. If desired PIOs A and B or C and D can be combined to form x4 shift functions. Figure 2-22 shows a simplified block diagram of the shift register block.

Table 2-9. Supported Input Standards

| Input Standard                         | V <sub>REF</sub> (Nom.) | V <sub>CCIO</sub> ¹ (Nom.) | On-chip Termination                                                                                                                                |

|----------------------------------------|-------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Single Ended Interfaces                | •                       |                            |                                                                                                                                                    |

| LVTTL33 <sup>3</sup>                   | _                       | 3.3                        | None                                                                                                                                               |

| LVCMOS 33, 25, 18, 15, 12 <sup>3</sup> | _                       | 3.3/2.5/1.8/1.5/1.2        | None                                                                                                                                               |

| PCI33, PCIX33, AGP1X33 <sup>3</sup>    | _                       | 3.3                        | None                                                                                                                                               |

| PCIX15                                 | 0.75                    | 1.5 <sup>2</sup>           | None / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210                                                                           |

| AGP2X33                                | 1.32                    | _                          | None                                                                                                                                               |

| HSTL18_I, II                           | 0.9                     | 1.8 <sup>2</sup>           | None / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210                                                                           |

| HSTL18_III, IV                         | 1.08                    | 1.8 <sup>2</sup>           | None / V <sub>CCIO</sub> : 50                                                                                                                      |

| HSTL15_I, II                           | 0.75                    | 1.5 <sup>2</sup>           | None / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210                                                                           |

| HSTL15_III, IV                         | 0.9                     | 1.5 <sup>2</sup>           | None / V <sub>CCIO</sub> : 50                                                                                                                      |

| SSTL33_I, II                           | 1.5                     | 3.3                        | None                                                                                                                                               |

| SSTL25_I, II                           | 1.25                    | 2.5 <sup>2</sup>           | None / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210                                                                           |

| SSTL18_I, II                           | 0.9                     | 1.8 <sup>2</sup>           | None / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210                                                                           |

| GTL+, GTL                              | 1.0 / 0.8               | 1.5 / 1.2 <sup>2</sup>     | None / V <sub>CCIO</sub> : 50                                                                                                                      |

| Differential Interfaces                |                         |                            |                                                                                                                                                    |

| SSTL18D_I, II                          | _                       | 1.8 <sup>2</sup>           | None / Diff: 120, 150, 220, 420/ Diff to V <sub>CMT</sub> : 120, 150, 220, 420 / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210 |

| SSTL25D_I, II                          | _                       | 2.5 <sup>2</sup>           | None / Diff: 120, 150, 220, 420/ Diff to V <sub>CMT</sub> : 120, 150, 220, 420 / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210 |

| SSTL33D_I, II                          | _                       | 3.3                        | None                                                                                                                                               |

| HSTL15D_I, II                          | _                       | 1.5²                       | None / Diff: 120, 150, 220, 420/ Diff to V <sub>CMT</sub> : 120, 150, 220, 420 / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210 |

| HSTL18D_I, II                          | _                       | 1.8 <sup>2</sup>           | None / Diff: 120, 150, 220, 420/ Diff to V <sub>CMT</sub> : 120, 150, 220, 420 / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210 |

| LVDS                                   | _                       | _                          | None / Diff: 120, 150, 220, 240/ Diff to V <sub>CMT</sub> : 120, 150, 220, 240                                                                     |

| Mini-LVDS                              | _                       | _                          | None / Diff: 120, 150 / Diff to V <sub>CMT</sub> : 120, 150                                                                                        |

| BLVDS25                                | _                       | _                          | None                                                                                                                                               |

| MLVDS25                                | _                       | _                          | None                                                                                                                                               |

| RSDS                                   | _                       | _                          | None / Diff: 120, 150, 220, 240/ Diff to V <sub>CMT</sub> : 120, 150, 220, 240                                                                     |

| LVPECL33                               | _                       | ≤2.5                       | None / Diff: 120, 150, 220, 240/ Diff to V <sub>CMT</sub> : 120, 150, 220, 240                                                                     |

When not specified V<sub>CCIO</sub> can be set anywhere in the valid operating range.

V<sub>CCIO</sub> needed for on-chip termination to V<sub>CCIO</sub>/2 or V<sub>CCIO</sub> only. V<sub>CCIO</sub> is not specified for off-chip termination or V<sub>TT</sub> termination.

All ratioed input buffers and dedicated pin input buffers include hysteresis with a typical value of 50mV.

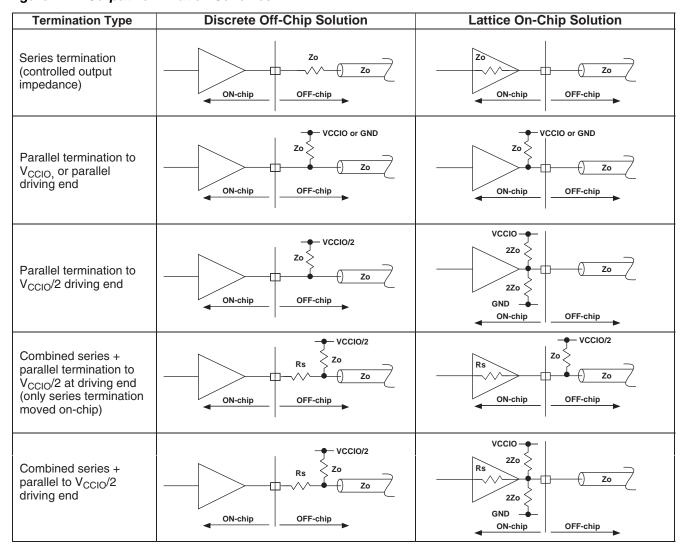

Figure 2-27. Output Termination Schemes

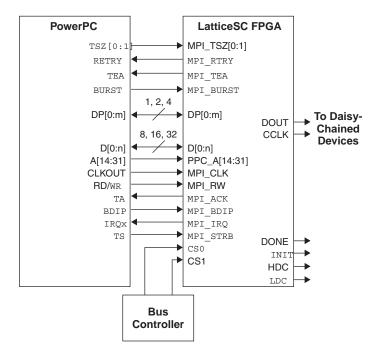

Figure 2-32. PowerPCI and MPI Schematic

### **Configuration and Testing**

The following section describes the configuration and testing features of the LatticeSC family of devices.

#### IEEE 1149.1-Compliant Boundary Scan Testability

All LatticeSC devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant test access port (TAP). This allows functional testing of the circuit board, on which the device is mounted, through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port has its own supply voltage V<sub>CCJ</sub> and can operate with LVCMOS33, 25 and 18 standards. For additional detail refer to technical information at the end of the data sheet.

#### **Device Configuration**

All LatticeSC devices contain three possible ports that can be used for device configuration. The serial port, which supports bit-wide configuration, and the sysCONFIG port that supports both byte-wide and serial configuration. The MPI port supports 8-bit, 16-bit or 32-bit configuration.

The serial port supports both the IEEE Std. 1149.1 Boundary Scan specification and the IEEE Std. 1532 In-System Configuration specification. The sysCONFIG port is a 20-pin interface with six of the I/Os used as dedicated pins and the rest being dual-use pins. When sysCONFIG mode is not used, these dual-use pins are available for general purpose I/O. All I/Os for the sysCONFIG and MPI ports are in I/O bank #1.

On power-up, the FPGA SRAM is ready to be configured with the sysCONFIG port active. The IEEE 1149.1 serial mode can be activated any time after power-up by sending the appropriate command through the TAP port. Once a configuration port is selected, that port is locked and another configuration port cannot be activated until the next re-initialization sequence. For additional detail refer to technical information at the end of the data sheet.

### **Power Supply Ramp Rates**

| Symbol            | Parameter                                         | Condition              | Min. | Тур. | Max | Units |

|-------------------|---------------------------------------------------|------------------------|------|------|-----|-------|

| t <sub>RAMP</sub> | Power supply ramp rates for all power supplies 1. | Over process, voltage, | 3.45 | _    |     | mV/μs |

|                   |                                                   | temperature            |      | _    | 75  | ms    |

- 1. See the Power-up and Power-Down requirements section for more details on power sequencing.

- 2. From 0.5V to minimum operating voltage.

## Hot Socketing Specifications<sup>1</sup>

| Symbol | Parameter                                                                            | Condition                       | Min. | Тур. | Max   | Units |

|--------|--------------------------------------------------------------------------------------|---------------------------------|------|------|-------|-------|

|        | Programmable and dedicated Input or I/O leakage current <sup>2, 3, 4, 5, 6</sup>     | $0 \ll V_{IN} \ll V_{IH} (MAX)$ | _    | _    | ±1500 | μΑ    |

|        | SERDES average input current when device powered down and inputs driven <sup>7</sup> |                                 | _    | _    | 4     | mA    |

- 1. See Hot Socket power up/down information in Chapter 2 of this document.

- 2. Assumes monotonic rise/fall rates for all power supplies.

- 3. Sensitive to power supply sequencing as described in hot socketing section.

- 4. Assumes power supplies are between 0 and maximum recommended operations conditions.

- 5. IDK is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ .

- 6. Represents DC conditions. For the first 20ns after hot insertion, current specification is 8 mA.

- 7. Assumes that the device is powered down with all supplies grounded, both P and N inputs driven by a CML driver with maximum allowed VDDOB of 1.575V, 8b/10b data and internal AC coupling.

## DC Electrical Characteristics<sup>5</sup>

#### **Over Recommended Operating Conditions**

| Symbol                                        | Parameter                                   | Condition                                                                                                                                                                                                                                    | Min. <sup>3</sup>                                     | Тур. | Max.                  | Units |

|-----------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|-----------------------|-------|

| I <sub>IL,</sub> I <sub>IH</sub> <sup>1</sup> | Input or I/O Low leakage                    | $0 \le V_{IN} \le V_{IH} (MAX)$                                                                                                                                                                                                              | _                                                     | _    | 10                    | μΑ    |

| I <sub>PU</sub>                               | I/O Active Pull-up Current                  | $0 \le V_{IN} \le 0.7 \ V_{CCIO}$                                                                                                                                                                                                            | -30                                                   | _    | -210                  | μΑ    |

| I <sub>PD</sub>                               | I/O Active Pull-down Current                | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{IH}$ (MAX)                                                                                                                                                                                               | 30                                                    | _    | 210                   | μΑ    |

| I <sub>BHLS</sub>                             | Bus Hold Low Sustaining<br>Current          | $V_{IN} = V_{IL} (MAX)$                                                                                                                                                                                                                      | 30                                                    | _    | _                     | μΑ    |

| I <sub>BHHS</sub>                             | Bus Hold High Sustaining<br>Current         | V <sub>IN</sub> = 0.7V <sub>CCIO</sub>                                                                                                                                                                                                       | -30                                                   | _    | _                     | μΑ    |

| I <sub>BHLO</sub>                             | Bus Hold Low Overdrive<br>Current           | $0 \le V_{IN} \le V_{IH}$ (MAX)                                                                                                                                                                                                              | _                                                     | _    | 210                   | μΑ    |

| I <sub>BHLH</sub>                             | Bus Hold High Overdrive<br>Current          | $0 \le V_{IN} \le V_{IH} $ (MAX)                                                                                                                                                                                                             | _                                                     | _    | -210                  | μΑ    |

| I <sub>CL</sub>                               | PCI Low Clamp Current                       | -3 < V <sub>IN</sub> ≤ -1                                                                                                                                                                                                                    | -25 + (V <sub>IN</sub> + 1)/0.015                     | _    | _                     | mA    |

| I <sub>CH</sub>                               | PCI High Clamp Current                      | $V_{CC} + 4 > V_{IN} \ge V_{CC} + 1$                                                                                                                                                                                                         | 25 + (V <sub>IN</sub> - V <sub>CC</sub> -1)/<br>0.015 | _    | _                     | mA    |

| $V_{BHT}$                                     | Bus Hold trip Points                        | $0 \le V_{IN} \le V_{IH} (MAX)$                                                                                                                                                                                                              | V <sub>IL</sub> (MAX)                                 | _    | V <sub>IH</sub> (MIN) | ٧     |

| C1                                            | I/O Capacitance <sup>2</sup>                | $\begin{aligned} &V_{CCIO} = 3.3 \text{V, } 2.5 \text{V, } 1.8 \text{V, } 1.5 \text{V, } 1.2 \text{V,} \\ &V_{CC} = 1.2 \text{V, } V_{CCIP2} = 1.2 \text{V,} \\ &V_{CCAUX} = 2.5, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)} \end{aligned}$ | _                                                     | 8    | _                     | pf    |

| C3 <sup>2</sup>                               | Dedicated Input<br>Capacitance <sup>2</sup> | $\begin{aligned} &V_{CCIO} = 3.3 \text{V, } 2.5 \text{V, } 1.8 \text{V, } 1.5 \text{V, } 1.2 \text{V,} \\ &V_{CC} = 1.2 \text{V, } V_{CCIP2} = 1.2 \text{V,} \\ &V_{CCAUX} = 2.5, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)} \end{aligned}$ | _                                                     | 6    | _                     | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

<sup>2.</sup> T<sub>A</sub> 25°C, f = 1.0MHz

<sup>3.</sup>  $I_{PU,\ I_{PD}}$ ,  $I_{BHLS}$  and  $I_{BHHS}$  have minimum values of 15 or -15 $\mu$ A if  $V_{CCIO}$  is set to 1.2V nominal.

<sup>4.</sup> This table does not apply to SERDES pins.

<sup>5.</sup> For programmable I/Os.

### **Initialization and Standby Supply Current**

The table below indicates initialization and standby supply current while operating at 85°C junction temperature  $(T_J)$ , which is the high end of the commercial temperature range, and 105°C, which is the high end of the industrial temperature range. This data assumes all outputs are tri-stated and all inputs are configured as LVCMOS and held at  $V_{CCIO}$  or GND. The remaining SERDES supply current for  $V_{DDIB}$  and  $V_{DDOB}$  is detailed in the SERDES section of this data sheet. For power at your design temperature, it is recommended to use the Power Calculator tool which is accessible in ispLEVER or can be used as a standalone tool. For more information on supply current, see the reference to additional technical documentation available at the end of this data sheet.

#### **Over Recommended Operating Conditions**

|                                        |                     |                                                                                    |           | 25°C<br>Typ. <sup>1</sup> |        | °C<br>IX.² | 105°C<br>Max. <sup>2</sup> | Units |

|----------------------------------------|---------------------|------------------------------------------------------------------------------------|-----------|---------------------------|--------|------------|----------------------------|-------|

| Symbol                                 | Condition           | Parameter                                                                          | Device    | All                       | -5, -6 | -7         | -5, -6                     |       |

|                                        |                     |                                                                                    | LFSC/M15  | 65                        | 449    | 678        | 755                        | mA    |

|                                        |                     |                                                                                    | LFSC/M25  | 113                       | 798    | 1255       | 1343                       | mA    |

|                                        | (VCC = 1.2V +/- 5%) | Core Operating Power Supply Current                                                | LFSC/M40  | 159                       | 1178   | 2006       | 1981                       | mA    |

|                                        |                     | Garrent                                                                            | LFSC/M80  | 276                       | 2122   | 3827       | 3569                       | mA    |

| l                                      |                     |                                                                                    | LFSC/M115 | 454                       | 3376   | _          | 5679                       | mA    |

| Icc                                    |                     |                                                                                    | LFSC/M15  | 45                        | 312    | 471        | 524                        | mA    |

|                                        |                     |                                                                                    | LFSC/M25  | 79                        | 554    | 872        | 933                        | mA    |

|                                        | (VCC = 1.0V +/- 5%) | Core Operating Power Supply Current                                                | LFSC/M40  | 110                       | 818    | 1393       | 1375                       | mA    |

|                                        |                     | Carron                                                                             | LFSC/M80  | 191                       | 1473   | 2658       | 2478                       | mA    |

|                                        |                     |                                                                                    | LFSC/M115 | 315                       | 2344   | _          | 3943                       | mA    |

|                                        |                     |                                                                                    | LFSC/M15  | 23                        | 39     | 59         | 35                         | mA    |

|                                        |                     | 1.2V Power Supply Current for Configuration Logic, FPGA PLL, SERDES PLL and SERDES | LFSC/M25  | 25                        | 50     | 78         | 56                         | mA    |

| I <sub>CC12</sub>                      |                     |                                                                                    | LFSC/M40  | 31                        | 78     | 133        | 89                         | mA    |

|                                        |                     | Analog Supplies                                                                    | LFSC/M80  | 50                        | 108    | 195        | 123                        | mA    |

|                                        |                     |                                                                                    | LFSC/M115 | 65                        | 131    | _          | 154                        | mA    |

|                                        |                     |                                                                                    | LFSC/M15  | 7                         | 12     | 19         | 14                         | mA    |

|                                        |                     | Associtions Consumbing December Consumb                                            | LFSC/M25  | 9                         | 16     | 25         | 18                         | mA    |

| I <sub>CCAUX</sub>                     |                     | Auxiliary Operating Power Supply Current                                           | LFSC/M40  | 12                        | 23     | 39         | 25                         | mA    |

|                                        |                     |                                                                                    | LFSC/M80  | 13                        | 25     | 45         | 23                         | mA    |

|                                        |                     |                                                                                    | LFSC/M115 | 16                        | 27     | _          | 26                         | mA    |

|                                        |                     |                                                                                    | LFSC/M15  | 0.1                       | 0.2    | 0.3        | 0.2                        | mA    |

| 1                                      |                     | Bords Bousey County Course                                                         | LFSC/M25  | 0.3                       | 0.6    | 1.0        | 0.7                        | mA    |

| I <sub>CCIO</sub> and I <sub>CCJ</sub> |                     | Bank Power Supply Current (per bank)                                               | LFSC/M40  | 0.4                       | 0.9    | 1.5        | 1.0                        | mA    |

| 000                                    |                     | W                                                                                  | LFSC/M80  | 0.5                       | 1.1    | 2.1        | 1.3                        | mA    |

|                                        | ·"                  |                                                                                    | LFSC/M115 | 0.7                       | 1.5    | _          | 1.8                        | mA    |

<sup>1.</sup>  $I_{CC}$  is specified at  $T_J = 25^{\circ}C$  and typical  $V_{CC}$ .

<sup>2.</sup> I<sub>CC</sub> is specified at the respective commercial and industrial maximum T<sub>J</sub> and V<sub>CC</sub> limits.

## **LatticeSC/M sysCONFIG Port Timing**

### **Over Recommended Operating Conditions**

| Parameter                            | Description                                                         | Min.                 | Max.                 | Units           |

|--------------------------------------|---------------------------------------------------------------------|----------------------|----------------------|-----------------|

| General Configu                      | ration Timing                                                       | •                    | •                    |                 |

| t <sub>SMODE</sub>                   | M[3:0] Setup Time to INITN High                                     | 0                    | _                    | ns              |

| t <sub>HMODE</sub>                   | M[3:0] Hold Time from INITN High                                    | 600                  | _                    | ns              |

| t <sub>RW</sub>                      | RESETN Pulse Width Low to Start Reconfiguration (1.2 V)             | 50 (or 100 at 0.95V) | _                    | ns              |

| t <sub>PGW</sub>                     | PROGRAMN Pulse Width Low to Start Reconfiguration (1.2 V)           | 50 (or 100 at 0.95V) | _                    | ns              |

| f <sub>ESB_CLK_FRQ</sub>             | System Bus ESB_CLK Frequency (No Wait States)                       | _                    | 133                  | MHz             |

| sysCONFIG Mas                        | ster Parallel Configuration Mode                                    | •                    | •                    |                 |

| t <sub>SMB</sub>                     | D[7:0] Setup Time to RCLK High                                      | 6                    | _                    | ns              |

| t <sub>HMB</sub>                     | D[7:0] Hold Time to RCLK High                                       | 0                    | _                    | ns              |

| +                                    | RCLK Low Time (Non-compressed Bitstreams)                           | 0.5                  | 0.5                  | CCLK<br>periods |

| <sup>t</sup> CLMB                    | RCLK Low Time (Compressed Bitstreams)                               | 0.5                  | 7.5                  | CCLK<br>periods |

| t <sub>CHMB</sub>                    | RCLK High Time                                                      | 0.5                  | 0.5                  | CCLK<br>periods |

| sysCONFIG SPI                        | Port                                                                |                      |                      |                 |

| t <sub>CFGX</sub>                    | INITN High to CSCK Low                                              | _                    | 80                   | ns              |

| t <sub>CSSPI</sub>                   | INITN High to CSSPIN Low                                            | 0                    | 2                    | μs              |

| t <sub>SCK</sub>                     | CSCK Low before CSSPIN Low                                          | 0                    | _                    | ns              |

| t <sub>SOCDO</sub>                   | CSCK Low to Output Valid                                            | _                    | 15                   | ns              |

| t <sub>CSPID</sub>                   | CSSPIN Low to CSCK high Setup Time                                  | _                    | 15                   | ns              |

| f <sub>MAXSPI</sub>                  | Max CCLK Frequency - SPI Flash Fast Read Opcode (0x0B) (SPIFASTN=0) | _                    | 50                   | MHz             |

| t <sub>SUSPI</sub>                   | SOSPI/D0 Data Setup Time Before CSCK                                | 7                    | _                    | ns              |

| t <sub>HSPI</sub>                    | SOSPI/D0 Data Hold Time After CSCK                                  | 2                    | _                    | ns              |

|                                      | Master Clock Frequency                                              | Selected value - 30% | Selected value + 30% | MHz             |

|                                      | Duty Cycle                                                          | 40                   | 60                   | %               |

| sysCONFIG Mas                        | ster Serial Configuration Mode                                      |                      | ı                    |                 |

| t <sub>SMS</sub>                     | DIN Setup Time                                                      | 4.4                  | _                    | ns              |

| t <sub>HMS</sub>                     | DIN Hold Time                                                       | 0                    | _                    | ns              |

| f <sub>CMS</sub>                     | CCLK Frequency (No Divider)                                         | 90                   | 190                  | MHz             |

| f <sub>C_DIV</sub>                   | CCLK Frequency (Div 128)                                            | 0.70                 | 1.48                 | MHz             |

| t <sub>D</sub>                       | CCLK to DOUT Delay                                                  | _                    | 7.5                  | ns              |

| sysCONFIG Mas                        | ter Parallel Configuration Mode                                     | ·                    | l                    |                 |

| t <sub>AVMP</sub>                    | RCLK to Address Valid                                               | _                    | 10                   | ns              |

| t <sub>SMP</sub>                     | D[7:0] Setup Time to RCLK High                                      | 6                    | _                    | ns              |

| t <sub>HMP</sub>                     | D[7:0] Hold Time to RCLK High                                       | 0                    | _                    | ns              |

|                                      | RCLK Low Time (Non-compressed Bitstream)                            | 7.5                  | 7.5                  | CCLK            |

| RCLK Low Time (Compressed Bitstream) |                                                                     | 0.5                  | 63.5                 | periods         |

| t <sub>CHMP</sub>                    | RCLK High Time                                                      | 0.5                  | 0.5                  | CCLK<br>periods |

| t <sub>DMP</sub>                     | CCLK to DOUT                                                        | _                    | 7.5                  | ns              |

## **Signal Descriptions (Cont.)**

| Signal Name                                | 1/0 | Description                                                                                                                                                                                           |  |  |  |

|--------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MPI_STRBN                                  | I   | Driven active low indicates the start of a transaction on the PowerPC bus. MPI will strobe the address bus at next rising edge of clock.                                                              |  |  |  |

| MPI_ADDR[31:14]                            | I   | Address bus driven by a PowerPC bus master. Only 18-bit width is needed. It has to be the least significant bit of the PowerPC 32-bit address A[31:14].                                               |  |  |  |

| MPI_DAT[n:0]                               | I/O | Selectable data bus width from 8, and 16-bit. Driven by a bus mas in a write transaction. Driven by MPI in a read transaction.                                                                        |  |  |  |

| MPI_PAR[m:0]                               | I/O | Selectable parity bus width from 1, 2, and 3-bit. MPI_DP[0] for MPI_D[7:0], MPI_DP[1] for MPI_D[15:8] and MPI_DP[2] for MPI_D[23:16].                                                                 |  |  |  |

| MPI_TA                                     | 0   | Transfer acknowledge. Driven active low indicates that MPI received the data on the write cycle or returned data on the read cycle.                                                                   |  |  |  |

| MPI_TEA                                    | 0   | Transfer Error Acknowledge. Driven active low indicates that MPI detects a bus error on the internal system bus for current transaction.                                                              |  |  |  |

| MPI_RETRY                                  | 0   | Active low MPI Retry requests the MPC860 to relinquish the bus and retry the cycle.                                                                                                                   |  |  |  |

| Multi-chip Alignment (User I/O if not used | d.) |                                                                                                                                                                                                       |  |  |  |

| MCA_DONE_OUT                               | 0   | Multi-chip alignment done output (to second MCA chip)                                                                                                                                                 |  |  |  |

| MCA_DONE_IN                                | I   | Multi-chip alignment done input (from second MCA chip)                                                                                                                                                |  |  |  |

| MCA_CLK_P[1:2]_OUT                         | 0   | Multi-chip alignment clock [1:2] output (sourced by MCA master chip)                                                                                                                                  |  |  |  |

| MCA_CLK_P[1:2]_IN                          | I   | Multi-chip alignment clock [1:2] input (from MCA master chip                                                                                                                                          |  |  |  |

| TEMP                                       | _   | Temperature sensing diode pin. Dedicated pin. Accuracy is typically +/- 10°C.                                                                                                                         |  |  |  |

| Miscellaneous Dedicated Pins               | l . |                                                                                                                                                                                                       |  |  |  |

| XRES                                       | _   | External reference resistor between this pin and ground. The reference resistor is used to calibrate the programmable terminating resistors used in the I/Os. Dedicated pin. Value: $1K \pm 1\%$ ohm. |  |  |  |

| DIFFRx                                     | _   | Only used if a differential driver is used in a bank. This DIFFRx must be connected to ground via an external 1K ±1% ohm resistor for all banks that have a differential driver.                      |  |  |  |

| SERDES Block (Dedicated Pins)              | l   |                                                                                                                                                                                                       |  |  |  |

| [A:D]_HDINPx_[L/R]                         | I   | High-speed input (positive) channel x on left [L] or right [R] side of device. PCS quad is defined in the dual function name column of the Logic Signal Connection table.                             |  |  |  |

| [A:D]_HDINNx_[L/R]                         | I   | High-speed input (negative) channel x on left [L] or right [R] side of device. PCS quad is defined in the dual function name column of the Logic Signal Connection table.                             |  |  |  |

| [A:D]_HDOUTPx_[L/R]                        | 0   | High-speed output (positive) channel x on left [L] or right [R] side of device. PCS quad is defined in the dual function name column of the Logic Signal Connection table.                            |  |  |  |

| [A:D]_HDOUTNx_[L/R]                        | 0   | High-speed output (negative) channel x on left [L] or right [R] side of device. PCS quad is defined in the dual function name column of the Logic Signal Connection table.                            |  |  |  |

| [A:D]_REFCLKP_[L/R]                        | I   | Ref clock input (positive), aux channel on left [L] or right [R] side of device.                                                                                                                      |  |  |  |

| [A:D]_REFCLKN_[L/R]                        | I   | Ref clock input (negative), aux channel on left [L] or right [R] side of device.                                                                                                                      |  |  |  |

# LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup> (Cont.)

|                |               | LFSC/M15 LFSC/M25 |                             |               | LFSC/M25      |                             |

|----------------|---------------|-------------------|-----------------------------|---------------|---------------|-----------------------------|

| Ball<br>Number | Ball Function | VCCIO<br>Bank     | Dual Function               | Ball Function | VCCIO<br>Bank | Dual Function               |

| N3             | PL27A         | 6                 |                             | PL30A         | 6             |                             |

| P3             | PL27B         | 6                 |                             | PL30B         | 6             |                             |

| P4             | PL27C         | 6                 | PCLKT6_3                    | PL30C         | 6             | PCLKT6_3                    |

| P2             | PL28A         | 6                 |                             | PL31A         | 6             |                             |

| R2             | PL28B         | 6                 |                             | PL31B         | 6             |                             |

| Т3             | PL28C         | 6                 | PCLKT6_2                    | PL31C         | 6             | PCLKT6_2                    |

| R3             | PL28D         | 6                 | PCLKC6_2                    | PL31D         | 6             | PCLKC6_2                    |

| P1             | PL31A         | 6                 |                             | PL34A         | 6             |                             |

| R1             | PL31B         | 6                 |                             | PL34B         | 6             |                             |

| R5             | PL31C         | 6                 | VREF1_6                     | PL34C         | 6             | VREF1_6                     |

| R4             | PL31D         | 6                 |                             | PL34D         | 6             |                             |

| T2             | PL32A         | 6                 |                             | PL35A         | 6             |                             |

| U2             | PL32B         | 6                 |                             | PL35B         | 6             |                             |

| T1             | PL33A         | 6                 |                             | PL38A         | 6             |                             |

| U1             | PL33B         | 6                 |                             | PL38B         | 6             |                             |

| V1             | PL35A         | 6                 |                             | PL42A         | 6             |                             |

| W1             | PL35B         | 6                 |                             | PL42B         | 6             |                             |

| V6             | PL35D         | 6                 | DIFFR_6                     | PL42D         | 6             | DIFFR_6                     |

| V2             | PL36A         | 6                 |                             | PL43A         | 6             |                             |

| W2             | PL36B         | 6                 |                             | PL43B         | 6             |                             |

| Y1             | PL37A         | 6                 |                             | PL44A         | 6             |                             |

| AA1            | PL37B         | 6                 |                             | PL44B         | 6             |                             |

| AB1            | PL39A         | 6                 |                             | PL48A         | 6             |                             |

| AC1            | PL39B         | 6                 |                             | PL48B         | 6             |                             |

| Y5             | PL40A         | 6                 |                             | PL49A         | 6             |                             |

| Y6             | PL40B         | 6                 |                             | PL49B         | 6             |                             |

| AD2            | PL41A         | 6                 |                             | PL51A         | 6             |                             |

| AE2            | PL41B         | 6                 |                             | PL51B         | 6             |                             |

| AB5            | PL41D         | 6                 | VREF2_6                     | PL51D         | 6             | VREF2_6                     |

| AC3            | PL43A         | 6                 |                             | PL52A         | 6             |                             |

| AD3            | PL43B         | 6                 |                             | PL52B         | 6             |                             |

| AF1            | PL44A         | 6                 |                             | PL55A         | 6             |                             |

| AG1            | PL44B         | 6                 |                             | PL55B         | 6             |                             |

| AB6            | PL44C         | 6                 | LLC_DLLT_IN_E/LLC_DLLT_FB_F | PL55C         | 6             | LLC_DLLT_IN_E/LLC_DLLT_FB_F |

| AC5            | PL44D         | 6                 | LLC_DLLC_IN_E/LLC_DLLC_FB_F | PL55D         | 6             | LLC_DLLC_IN_E/LLC_DLLC_FB_F |

| AF2            | PL45A         | 6                 | LLC_DLLT_IN_F/LLC_DLLT_FB_E | PL57A         | 6             | LLC_DLLT_IN_F/LLC_DLLT_FB_E |

| AG2            | PL45B         | 6                 | LLC_DLLC_IN_F/LLC_DLLC_FB_E | PL57B         | 6             | LLC_DLLC_IN_F/LLC_DLLC_FB_E |

| AC6            | PL45C         | 6                 | LLC_PLLT_IN_B/LLC_PLLT_FB_A | PL57C         | 6             | LLC_PLLT_IN_B/LLC_PLLT_FB_A |

| AC7            | PL45D         | 6                 | LLC_PLLC_IN_B/LLC_PLLC_FB_A | PL57D         | 6             | LLC_PLLC_IN_B/LLC_PLLC_FB_A |

| AE4            | XRES          | -                 |                             | XRES          | -             |                             |

| AG4            | VCC12         | -                 |                             | VCC12         | -             |                             |

| AD5            | TEMP          | 6                 |                             | TEMP          | 6             |                             |

| AF5            | VCC12         | -                 |                             | VCC12         | -             |                             |

| AH1            | PB3A          | 5                 | LLC_PLLT_IN_A/LLC_PLLT_FB_B | PB3A          | 5             | LLC_PLLT_IN_A/LLC_PLLT_FB_B |

| AJ1            | PB3B          | 5                 | LLC_PLLC_IN_A/LLC_PLLC_FB_B | PB3B          | 5             | LLC_PLLC_IN_A/LLC_PLLC_FB_B |

# LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup> (Cont.)

|                |               | LFSC/M15      | LFSC/M25                    |               |               |                             |

|----------------|---------------|---------------|-----------------------------|---------------|---------------|-----------------------------|

| Ball<br>Number | Ball Function | VCCIO<br>Bank | Dual Function               | Ball Function | VCCIO<br>Bank | Dual Function               |

| R29            | PR28B         | 3             |                             | PR31B         | 3             |                             |

| P29            | PR28A         | 3             |                             | PR31A         | 3             |                             |

| P27            | PR27C         | 3             | PCLKT3_3                    | PR30C         | 3             | PCLKT3_3                    |

| N29            | PR27B         | 3             |                             | PR30B         | 3             |                             |

| N28            | PR27A         | 3             |                             | PR30A         | 3             |                             |

| R25            | PR26D         | 3             | PCLKC3_1                    | PR29D         | 3             | PCLKC3_1                    |

| R26            | PR26C         | 3             | PCLKT3_1                    | PR29C         | 3             | PCLKT3_1                    |

| R28            | PR26B         | 3             | PCLKC3_0                    | PR29B         | 3             | PCLKC3_0                    |

| P28            | PR26A         | 3             | PCLKT3_0                    | PR29A         | 3             | PCLKT3_0                    |

| N27            | PR24D         | 2             | PCLKC2_2                    | PR27D         | 2             | PCLKC2_2                    |

| P26            | PR24C         | 2             | PCLKT2_2                    | PR27C         | 2             | PCLKT2_2                    |

| L30            | PR24B         | 2             | PCLKC2_0                    | PR27B         | 2             | PCLKC2_0                    |

| K30            | PR24A         | 2             | PCLKT2_0                    | PR27A         | 2             | PCLKT2_0                    |

| J30            | PR23B         | 2             | PCLKC2_1                    | PR26B         | 2             | PCLKC2_1                    |

| H30            | PR23A         | 2             | PCLKT2_1                    | PR26A         | 2             | PCLKT2_1                    |

| M26            | PR22D         | 2             | DIFFR_2                     | PR25D         | 2             | DIFFR_2                     |

| M25            | PR22C         | 2             | VREF1_2                     | PR25C         | 2             | VREF1_2                     |

| G29            | PR22B         | 2             |                             | PR25B         | 2             |                             |

| F29            | PR22A         | 2             |                             | PR25A         | 2             |                             |

| H28            | PR19D         | 2             |                             | PR22D         | 2             |                             |

| J28            | PR19C         | 2             |                             | PR22C         | 2             |                             |

| E30            | PR19B         | 2             |                             | PR22B         | 2             |                             |

| E29            | PR19A         | 2             |                             | PR22A         | 2             |                             |

| L26            | PR18D         | 2             | VREF2_2                     | PR18D         | 2             | VREF2_2                     |

| L25            | PR18C         | 2             |                             | PR18C         | 2             |                             |

| F28            | PR18B         | 2             | URC_DLLC_IN_D/URC_DLLC_FB_C | PR18B         | 2             | URC_DLLC_IN_D/URC_DLLC_FB_C |

| G28            | PR18A         | 2             | URC_DLLT_IN_D/URC_DLLT_FB_C | PR18A         | 2             | URC_DLLT_IN_D/URC_DLLT_FB_C |

| K26            | PR17D         | 2             | URC_PLLC_IN_B/URC_PLLC_FB_A | PR17D         | 2             | URC_PLLC_IN_B/URC_PLLC_FB_A |

| K25            | PR17C         | 2             | URC_PLLT_IN_B/URC_PLLT_FB_A | PR17C         | 2             | URC_PLLT_IN_B/URC_PLLT_FB_A |

| D30            | PR17B         | 2             | URC_DLLC_IN_C/URC_DLLC_FB_D | PR17B         | 2             | URC_DLLC_IN_C/URC_DLLC_FB_D |

| D29            | PR17A         | 2             | URC_DLLT_IN_C/URC_DLLT_FB_D | PR17A         | 2             | URC_DLLT_IN_C/URC_DLLT_FB_D |

| G26            | PR15D         | 2             |                             | PR16D         | 2             |                             |

| H26            | PR15C         | 2             |                             | PR16C         | 2             |                             |

| E28            | PR15B         | 2             | URC_PLLC_IN_A/URC_PLLC_FB_B | PR16B         | 2             | URC_PLLC_IN_A/URC_PLLC_FB_B |

| D28            | PR15A         | 2             | URC_PLLT_IN_A/URC_PLLT_FB_B | PR16A         | 2             | URC_PLLT_IN_A/URC_PLLT_FB_B |

| J25            | VCCJ          | -             |                             | VCCJ          | -             |                             |

| H25            | TDO           | -             | TDO                         | TDO           | -             | TDO                         |

| J26            | TMS           | -             |                             | TMS           | -             |                             |

| G25            | TCK           | -             |                             | TCK           | -             |                             |

| G24            | TDI           | -             |                             | TDI           | -             |                             |

| F26            | PROGRAMN      | 1             |                             | PROGRAMN      | 1             |                             |

| H24            | MPIIRQN       | 1             | CFGIRQN/MPI_IRQ_N           | MPIIRQN       | 1             | CFGIRQN/MPI_IRQ_N           |

| F25            | CCLK          | 1             |                             | CCLK          | 1             |                             |

| D27            | VCC12         | -             |                             | VCC12         | -             |                             |

| E26            | VCC12         | -             |                             | VCC12         | -             |                             |

# LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup> (Cont.)

|                |               |               | LFSC/M15           | LFSC/M25      |               |                    |  |

|----------------|---------------|---------------|--------------------|---------------|---------------|--------------------|--|

| Ball<br>Number | Ball Function | VCCIO<br>Bank | Dual Function      | Ball Function | VCCIO<br>Bank | Dual Function      |  |

| D14            | PT15B         | 1             | A15/MPI_ADDR29     | PT25B         | 1             | A15/MPI_ADDR29     |  |

| D13            | PT15A         | 1             | A17/MPI_ADDR31     | PT25A         | 1             | A17/MPI_ADDR31     |  |

| F12            | PT13D         | 1             | A19/MPI_TSIZ1      | PT24D         | 1             | A19/MPI_TSIZ1      |  |

| F13            | PT13C         | 1             | A20/MPI_BDIP       | PT24C         | 1             | A20/MPI_BDIP       |  |

| B12            | PT11B         | 1             | A18/MPI_TSIZ0      | PT24B         | 1             | A18/MPI_TSIZ0      |  |

| B11            | PT11A         | 1             | MPI_TEA            | PT24A         | 1             | MPI_TEA            |  |

| E12            | PT10D         | 1             | D14/MPI_DATA14     | PT23D         | 1             | D14/MPI_DATA14     |  |

| D12            | PT10C         | 1             | DP1/MPI_PAR1       | PT23C         | 1             | DP1/MPI_PAR1       |  |

| G10            | PT9B          | 1             | A21/MPI_BURST      | PT23B         | 1             | A21/MPI_BURST      |  |

| G9             | PT9A          | 1             | D15/MPI_DATA15     | PT23A         | 1             | D15/MPI_DATA15     |  |

| C10            | A_VDDIB3_L    | -             |                    | A_VDDIB3_L    | -             |                    |  |

| E9             | VCC12         | -             |                    | VCC12         | -             |                    |  |

| B10            | A_HDINP3_L    | -             | PCS 360 CH 3 IN P  | A_HDINP3_L    | -             | PCS 360 CH 3 IN P  |  |

| B9             | A_HDINN3_L    | -             | PCS 360 CH 3 IN N  | A_HDINN3_L    | -             | PCS 360 CH 3 IN N  |  |

| A10            | A_HDOUTP3_L   | -             | PCS 360 CH 3 OUT P | A_HDOUTP3_L   | -             | PCS 360 CH 3 OUT P |  |

| D9             | VCC12         | -             |                    | VCC12         | -             |                    |  |

| A9             | A_HDOUTN3_L   | -             | PCS 360 CH 3 OUT N | A_HDOUTN3_L   | -             | PCS 360 CH 3 OUT N |  |

| C9             | A_VDDOB3_L    | -             |                    | A_VDDOB3_L    | -             |                    |  |

| A8             | A_HDOUTN2_L   | -             | PCS 360 CH 2 OUT N | A_HDOUTN2_L   | -             | PCS 360 CH 2 OUT N |  |

| C8             | A_VDDOB2_L    | -             |                    | A_VDDOB2_L    | -             |                    |  |

| A7             | A_HDOUTP2_L   | -             | PCS 360 CH 2 OUT P | A_HDOUTP2_L   | -             | PCS 360 CH 2 OUT P |  |

| E8             | VCC12         | -             |                    | VCC12         | -             |                    |  |

| B8             | A_HDINN2_L    | -             | PCS 360 CH 2 IN N  | A_HDINN2_L    | -             | PCS 360 CH 2 IN N  |  |

| B7             | A_HDINP2_L    | -             | PCS 360 CH 2 IN P  | A_HDINP2_L    | -             | PCS 360 CH 2 IN P  |  |

| C7             | A_VDDIB2_L    | -             |                    | A_VDDIB2_L    | -             |                    |  |

| D8             | VCC12         | -             |                    | VCC12         | -             |                    |  |

| C6             | A_VDDIB1_L    | -             |                    | A_VDDIB1_L    | -             |                    |  |

| E7             | VCC12         | -             |                    | VCC12         | -             |                    |  |

| B6             | A_HDINP1_L    | -             | PCS 360 CH 1 IN P  | A_HDINP1_L    | -             | PCS 360 CH 1 IN P  |  |

| B5             | A_HDINN1_L    | -             | PCS 360 CH 1 IN N  | A_HDINN1_L    | -             | PCS 360 CH 1 IN N  |  |

| A6             | A_HDOUTP1_L   | -             | PCS 360 CH 1 OUT P | A_HDOUTP1_L   | -             | PCS 360 CH 1 OUT P |  |

| D7             | VCC12         | -             |                    | VCC12         | -             |                    |  |

| A5             | A_HDOUTN1_L   | -             | PCS 360 CH 1 OUT N | A_HDOUTN1_L   | -             | PCS 360 CH 1 OUT N |  |

| C5             | A_VDDOB1_L    | -             |                    | A_VDDOB1_L    | -             |                    |  |

| A4             | A_HDOUTN0_L   | -             | PCS 360 CH 0 OUT N | A_HDOUTN0_L   |               | PCS 360 CH 0 OUT N |  |

| C4             | A_VDDOB0_L    |               |                    | A_VDDOB0_L    | _             |                    |  |

| A3             | A_HDOUTP0_L   | -             | PCS 360 CH 0 OUT P | A_HDOUTP0_L   | _             | PCS 360 CH 0 OUT P |  |

| E6             | VCC12         | -             |                    | VCC12         | -             |                    |  |

| B4             | A_HDINN0_L    | -             | PCS 360 CH 0 IN N  | A_HDINN0_L    | -             | PCS 360 CH 0 IN N  |  |

| B3             | A_HDINP0_L    | -             | PCS 360 CH 0 IN P  | A_HDINP0_L    | -             | PCS 360 CH 0 IN P  |  |

| C3             | A_VDDIB0_L    | -             |                    | A_VDDIB0_L    | -             |                    |  |

| D6             | VCC12         |               |                    | VCC12         | _             |                    |  |

| L5             | NC            | -             |                    | PL21A         | 7             |                    |  |

| M5             | NC            | -             |                    | PL21B         | 7             |                    |  |

| G2             | NC            | -             |                    | PL20A         | 7             |                    |  |

# LFSC/M25, LFSC/M40 Logic Signal Connections: 1020 fcBGA<sup>1, 2</sup> (Cont.)

|                |               | LF         | LFSC/M40                              |               |            |                                       |

|----------------|---------------|------------|---------------------------------------|---------------|------------|---------------------------------------|

| Ball<br>Number | Ball Function | VCCIO Bank | Dual Function                         | Ball Function | VCCIO Bank | Dual Function                         |

| Y24            | PL48C         | 6          |                                       | PL61C         | 6          |                                       |

| Y23            | PL48D         | 6          |                                       | PL61D         | 6          |                                       |