# E · / Fattice Semiconductor Corporation - <u>LFSCM3GA15EP1-6F256I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                        |

|--------------------------------|---------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 3750                                                                            |

| Number of Logic Elements/Cells | 15000                                                                           |

| Total RAM Bits                 | 1054720                                                                         |

| Number of I/O                  | 139                                                                             |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 0.95V ~ 1.26V                                                                   |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | -40°C ~ 105°C (TJ)                                                              |

| Package / Case                 | 256-BGA                                                                         |

| Supplier Device Package        | 256-FPBGA (17x17)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfscm3ga15ep1-6f256i |

|                                |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 2-5. sysMEM Block Configurations

| Memory Mode      | Configurations                                                              |

|------------------|-----------------------------------------------------------------------------|

| Single Port      | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

| True Dual Port   | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18             |

| Pseudo Dual Port | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

| FIFO             | 16,384 x 1<br>8,192 x 2<br>4,096 x 4<br>2,048 x 9<br>1,024 x 18<br>512 x 36 |

### Bus Size Matching

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1 and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

### RAM Initialization and ROM Operation

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

### Single, Dual and Pseudo-Dual Port Modes

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output. A clock is required even in asynchronous read mode.

The EBR memory supports two forms of write behavior for dual port operation:

- 1. **Normal** data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output.

- 2. Write Through a copy of the input data appears at the output of the same port.

### **FIFO Configuration**

The FIFO has a write port with Data-in, WCE, WE and WCLK signals. There is a separate read port with Data-out, RCE, RE and RCLK signals. The FIFO internally generates Almost Full, Full, Almost Empty, and Empty Flags. The Full and Almost Full flags are registered with WCLK. The Empty and Almost Empty flags are registered with RCLK.

#### Adaptive Input Logic (AIL) Overview

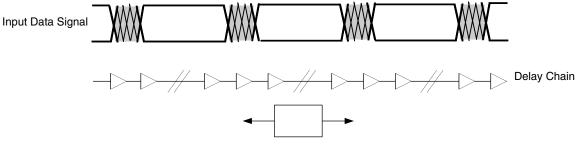

The Adaptive Input Logic (AIL) provides the ability of the input logic to dynamically find a solution by monitoring multiple samples of the input data. The input data signal from the input buffer is run through a delay chain. Data, transitions, jitter, noise are all contained inside of the delay chain. The AIL will then search the delay chain for a clean sampling point for data. Once found the AIL will monitor and walk with the data dynamically. This novel approach of using a delay chain to create multiple copies of the data provides a lower power solution than oversampling data with a higher speed clock. Figure 2-19 provides a high level view of the AIL methodology.

AIL Acquisition Window

The AIL slides the acquisition window through the delay chain searching for stable data based solely on data transitions. A specific training pattern is not required to perform this bit alignment, simply data transitions. The size of the acquisition window is user-selectable allowing the AIL to operate over the full range of the PURESPEED I/O range. Based on dynamic user control the AIL can either continuously adjust the window location based on data edge detection or it can be locked to a specific delay.

The AIL operates on single data and double data rate interfaces and is available on most FPGA input pins on the LatticeSC device and all buffer types. The AIL block is low power using only 0.003 mW/MHz typical (6 mW @ 2 Gbps) for PRBS 2<sup>7</sup> data. Multiple AIL inputs can be used to create a bus with a FPGA circuit to realign the bus to a common clock cycle. The FPGA circuit to realign the bus is required and is provided by Lattice as a reference design.

For more information on the LatticeSC AIL please refer to TN1158 <u>LatticeSC PURESPEED I/O Adaptive Input</u> <u>Logic User's Guide</u>.

#### Input DDR/Shift Block

The DDR/Shift block contains registers and associated logic that support DDR and shift register functions using the high-speed clock and the associated transfer to the low-speed clock domain. It functions as a gearbox allowing high-speed incoming data to be passed into the FPGA fabric. Each PIO supports DDR and x2 shift functions. If desired PIOs A and B or C and D can be combined to form x4 shift functions. The PIOs A and C on the left, right and bottom of the device also contain an optional Adaptive Input Logic (AIL) element. This logic automatically aligns incoming data with the clock allowing for easy design of high-speed interfaces. Figure 2-21 shows a simplified block diagram of the shift register block. The shift block in conjunction with the update and clock divider blocks automatically handles the hand off between the low-speed and high-speed clock domains.

### **PURESPEED I/O Buffer Banks**

LatticeSC devices have seven PURESPEED I/O buffer banks; each is capable of supporting multiple I/O standards. Each PURESPEED I/O bank has its own I/O supply voltage ( $V_{CCIO}$ ), and two voltage references  $V_{REF1}$  and  $V_{REF2}$  resources allowing each bank to be completely independent from each other. Figure 2-26 shows the seven banks and their associated supplies. Table 2-7 lists the maximum number of I/Os per bank for the whole LatticeSC family.

In the LatticeSC devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS, PCI33 and PCIX33) are powered using  $V_{CCIO}$ . In addition to the bank  $V_{CCIO}$  supplies, the LatticeSC devices have a  $V_{CC}$  core logic power supply, and a  $V_{CCAUX}$  supply that power all differential and referenced buffers. VCCAUX also powers a predriver of single-ended output buffers to enhance buffer performance.

Each bank can support up to two separate VREF voltages, VREF1 and VREF2 that set the threshold for the referenced input buffers. In the LatticeSC devices any I/O pin in a bank can be configured to be a dedicated reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

Differential drivers have user selectable internal or external bias. External bias is brought in by the VREF1 pin in the bank. External bias for differential buffers is needed for applications that requires tighter than standard output common mode range.

Since a bank can have only one external bias circuit for differential drivers, LVDS and RSDS differential outputs can be mixed in a bank.

If a differential driver is configured in a bank, one pin in that bank becomes a DIFFR pin. This DIFFR pin must be connected to ground via an external 1K +/-1% ohm resistor. Note that differential drivers are not supported in banks 1, 4 and 5.

In addition, there are dedicated Terminating Supply ( $V_{TT}$ ) pins to be used as terminating voltage for one of the two ways to perform parallel terminations. These  $V_{TT}$  pins are available in banks 2-7, these pins are not available in some packages. When VTT termination is not required, or used to provide the common mode termination voltage (VCMT), these pins can be left unconnected on the device. If the internal or external VCMT function for differential input termination is used, the VTT pins should be unconnected and allowed to float.

There are further restrictions on the use of  $V_{TT}$  pins, for additional details refer to technical information at the end of this data sheet.

VDDAX25 needs to be connected independent of the use of the SERDES. This supply is used to control the SERDES CML I/O regardless of the SERDES being used in the design.

#### Supported Source Synchronous Interfaces

The LatticeSC devices contain a variety of hardware, such as delay elements, DDR registers and PLLs, to simplify the implementation of Source Synchronous interfaces. Table 2-11 lists Source Synchronous and DDR/QDR standards supported in the LatticeSC. For additional detail refer to technical information at the end of the data sheet.

Source Synchronous Standard Clocking Speeds (MHz) Data Rate (Mbps) RapidIO DDR 500 1000 SPI4.2 (POS-PHY4)/NPSI DDR 1000 500 DDR 334 667 SFI4/XSBI SDR 667 DDR XGMII 156.25 312 CSIX SDR 250 250 QDRII/QDRII+ memory interface DDR 300 600 DDR memory interface DDR 240 480 DDR 333 667 DDRII memory interface DDR 400 800 **RLDRAM** memory interface

#### Table 2-11. Source Synchronous Standards Table<sup>1</sup>

1. Memory width is dependent on the system design and limited by the number of I/Os in the device.

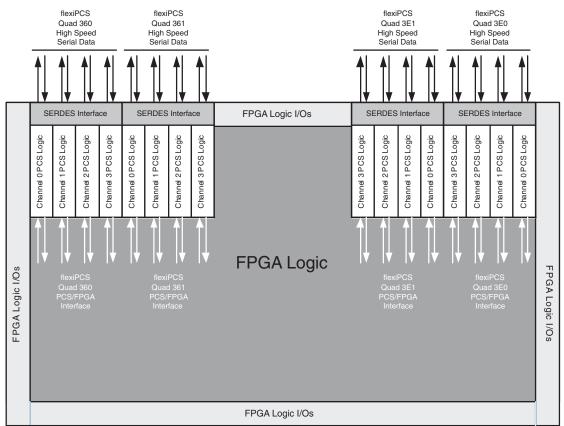

### flexiPCS<sup>™</sup> (Physical Coding Sublayer Block)

#### flexiPCS Functionality

The LatticeSC family combines a high-performance FPGA fabric, high-performance I/Os and large embedded RAM in a single industry leading architecture. LatticeSC devices also feature up to 32 channels of embedded SERDES with associated Physical Coding Sublayer (PCS) logic. The flexiPCS logic can be configured to support numerous industry standard high-speed data transfer protocols.

Each channel of flexiPCS logic contains dedicated transmit and receive SERDES for high-speed, full-duplex serial data transfers at data rates up to 3.8 Gbps. The PCS logic in each channel can be configured to support an array of popular data protocols including SONET (STS-12/STS-12c, STS-48/STS-48c, and TFI-5 support of 10 Gbps or above), Gigabit Ethernet (compliant to the IEEE 1000BASE-X specification), 1.02 or 2.04 Gbps Fibre Channel, PCI-Express, and Serial RapidIO. In addition, the protocol based logic can be fully or partially bypassed in a number of configurations to allow users flexibility in designing their own high-speed data interface.

Protocols requiring data rates above 3.8 Gbps can be accommodated by dedicating either one pair or all four channels in one flexiPCS quad block to one data link. One quad can support full-duplex serial data transfers at data rates up to 15.2 Gbps. A single flexiPCS quad can be configured to support 10Gb Ethernet (with a fully compliant XAUI interface), 10Gb Fibre Channel, and x4 PCI-Express and 4x RapidIO.

The flexiPCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic which can also be geared to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic. Each SERDES pin can be DC coupled independently and can allow for both high-speed and low-speed operation down to DC rates on the same SERDES pin, as required by some Serial Digital Video applications.

The ispLEVER design tools from Lattice support all modes of the flexiPCS. Most modes are dedicated to applications associated with a specific industry standard data protocol. Other more general purpose modes allow a user to define their own operation. With ispLEVER, the user can define the mode for each quad in a design. Nine modes are currently supported by the ispLEVER design flow:

- 8-bit SERDES Only

- 10-bit SERDES Only

- SONET (STS-12/STS-48)

- Gigabit Ethernet

- Fibre Channel

- XAUI

- Serial RapidIO

- PCI-Express

- Generic 8b10b

### flexiPCS Quad

The flexiPCS logic is arranged in quads containing logic for four independent full-duplex data channels. Each device in the LatticeSC family has up to eight quads of flexiPCS logic. The LatticeSC Family Selection Guide table on the first page of this data sheet contains the number of flexiPCS channels present on the chip. Note that in some packages (particularly lower pin count packages), not all channels from all quads on a given device may be bonded to package pins.

Each quad supports up to four channels of full-duplex data and can be programmed into any one of several protocol based modes. Each quad requires its own reference clock which can be sourced externally or from the FPGA logic. The user can utilize between one and four channels in a quad, depending on the application.

Figure 2-30 shows an example of four flexiPCS quads in a LatticeSC device. Quads are labeled according to the address of their software controlled registers.

#### Figure 2-30. LatticeSC flexiPCS

Since each quad has its own reference clock, different quads can support different standards on the same chip. This feature makes the LatticeSC family of devices ideal for bridging between different standards.

# LatticeSC/M Family Data Sheet **DC and Switching Characteristics**

December 2011

Data Sheet DS1004

### **Absolute Maximum Ratings**

| Supply Voltage V <sub>CC,</sub> V <sub>CC12,</sub> V <sub>DDIB,</sub> V <sub>DDOB</sub> 0.5 to 1.6V |

|-----------------------------------------------------------------------------------------------------|

| Supply Voltage V <sub>CCAUX</sub> , V <sub>DDAX25</sub> , V <sub>TT</sub> 0.5 to 2.75V              |

| Supply Voltage V <sub>CCJ</sub> 0.5 to 3.6V                                                         |

| Supply Voltage V <sub>CCIO</sub> (Banks 1, 4, 5)0.5 to 3.6V                                         |

| Supply Voltage V <sub>CCIO</sub> (Banks 2, 3, 6, 7)                                                 |

| Input or I/O Tristate Voltage Applied (Banks 1, 4, 5)                                               |

| Input or I/O Tristate Voltage Applied (Banks 2, 3, 6, 7)                                            |

| Storage Temperature (Ambient)                                                                       |

| Junction Temperature Under Bias (Tj)+125°C                                                          |

#### Notes:

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- 2. Compliance with the Lattice Thermal Management document is required.

- 3. All voltages referenced to GND.

4. Undershoot and overshoot of -2V to (VIHMAX +2) volts is permitted for a duration of <20ns.

### **Recommended Operating Conditions**

| Symbol                                  | Parameter                                                                                                                                       | Min.  | Max.                     | Units |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------|-------|

| V <sub>CC</sub> ⁵                       | Core Supply Voltage (Nominal 1.2V Operation)                                                                                                    | 0.95  | 1.26                     | V     |

| V <sub>CCAUX</sub> <sup>6</sup>         | Programmable I/O Auxiliary Supply Voltage                                                                                                       | 2.375 | 2.625                    | V     |

| V <sub>CCIO</sub> <sup>1, 2, 5, 6</sup> | Programmable I/O Driver Supply Voltage (Banks 1, 4, 5)                                                                                          | 1.14  | 3.45                     | V     |

| V <sub>CCIO</sub> <sup>1, 2, 5, 6</sup> | Programmable I/O Driver Supply Voltage (Banks 2, 3, 6, 7)                                                                                       | 1.14  | 2.625                    | V     |

| V <sub>CC12</sub> <sup>4, 5</sup>       | Internal 1.2V Power Supply Voltage for Configuration Logic and<br>FPGA PLL, SERDES PLL Power Supply Voltage and SERDES<br>Analog Supply Voltage | 1.14  | 1.26                     | V     |

| V <sub>DDIB</sub>                       | SERDES Input Buffer Supply Voltage                                                                                                              |       | 1.575                    | V     |

| V <sub>DDOB</sub>                       | SERDES Output Buffer Supply Voltage                                                                                                             |       | 1.575                    | V     |

| V <sub>DDAX25</sub>                     | SERDES Termination Auxiliary Supply Voltage                                                                                                     | 2.375 | 2.625                    | V     |

| V <sub>CCJ</sub> <sup>1, 5</sup>        | Supply Voltage for IEEE 1149.1 Test Access Port                                                                                                 | 1.71  | 3.45                     | V     |

| V <sub>TT</sub> <sup>2, 3</sup>         | Programmable I/O Termination Power Supply                                                                                                       |       | V <sub>CCAUX</sub> - 0.5 | V     |

| t <sub>JCOM</sub>                       | Junction Temperature, Commercial Operation                                                                                                      |       | +85                      | С     |

| t <sub>JIND</sub>                       | Junction Temperature, Industrial Operation                                                                                                      | -40   | 105                      | С     |

1. If  $V_{CCIO}$  or  $V_{CCJ}$  is set to 2.5V, they must be connected to the same power supply as  $V_{CCAUX}$ .

2. See recommended voltages by I/O standard in subsequent table.

<sup>3.</sup> When V<sub>TT</sub> termination is not required, or used to provide the common mode termination voltage (V<sub>CMT</sub>), these pins can be left unconnected on the device.

<sup>4.</sup> V<sub>CC12</sub> cannot be lower than V<sub>CC</sub> at any time. For 1.2V operation, it is recommended that the V<sub>CC</sub> and V<sub>CC12</sub> supplies be tied together with proper noise decoupling between the digital VCC and analog VCC12 supplies.

<sup>5.</sup>  $V_{CC,} V_{CCIO}$  (all banks),  $V_{CC12}$  and  $V_{CCJ}$  must reach their minimum values before configuration will proceed. 6. If  $V_{CCIO}$  for a bank is nominally 1.2V/1.5V/1.8V, then  $V_{CCAUX}$  must always be higher than  $V_{CCIO}$  during power up.

<sup>© 2011</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### **Power Supply Ramp Rates**

| Symbol | Parameter                                        | Condition              | Min. | Тур. | Max | Units |

|--------|--------------------------------------------------|------------------------|------|------|-----|-------|

| t      | I Power Subdiv ramp rates for all power subdiles | Over process, voltage, | 3.45 | -    |     | mV/μs |

| 'RAMP  |                                                  | temperature            |      |      | 75  | ms    |

1. See the Power-up and Power-Down requirements section for more details on power sequencing.

2. From 0.5V to minimum operating voltage.

### Hot Socketing Specifications<sup>1</sup>

| Symbol            | Parameter                                                                            | Condition                                     | Min. | Тур. | Max   | Units |

|-------------------|--------------------------------------------------------------------------------------|-----------------------------------------------|------|------|-------|-------|

|                   | Programmable and dedicated Input or I/O leakage current <sup>2, 3, 4, 5, 6</sup>     | 0 <= V <sub>IN</sub> <= V <sub>IH</sub> (MAX) | _    | _    | ±1500 | μΑ    |

| I <sub>HDIN</sub> | SERDES average input current when device powered down and inputs driven <sup>7</sup> |                                               |      | _    | 4     | mA    |

1. See Hot Socket power up/down information in Chapter 2 of this document.

2. Assumes monotonic rise/fall rates for all power supplies.

3. Sensitive to power supply sequencing as described in hot socketing section.

4. Assumes power supplies are between 0 and maximum recommended operations conditions.

5. IDK is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ .

6. Represents DC conditions. For the first 20ns after hot insertion, current specification is 8 mA.

7. Assumes that the device is powered down with all supplies grounded, both P and N inputs driven by a CML driver with maximum allowed VDDOB of 1.575V, 8b/10b data and internal AC coupling.

### **DC Electrical Characteristics<sup>5</sup>**

#### **Over Recommended Operating Conditions**

| Symbol             | Parameter                                   | Condition                                  | Min. <sup>3</sup>                                     | Тур. | Max.                  | Units |

|--------------------|---------------------------------------------|--------------------------------------------|-------------------------------------------------------|------|-----------------------|-------|

| $I_{IL,} I_{IH}^1$ | Input or I/O Low leakage                    | $0 \le V_{IN} \le V_{IH}$ (MAX)            | —                                                     | _    | 10                    | μΑ    |

| I <sub>PU</sub>    | I/O Active Pull-up Current                  | $0 \le V_{IN} \le 0.7 V_{CCIO}$            | -30                                                   | _    | -210                  | μΑ    |

| I <sub>PD</sub>    | I/O Active Pull-down Cur-<br>rent           | $V_{IL} (MAX) \le V_{IN} \le V_{IH} (MAX)$ | 30                                                    | _    | 210                   | μA    |

| I <sub>BHLS</sub>  | Bus Hold Low Sustaining<br>Current          | V <sub>IN</sub> = V <sub>IL</sub> (MAX)    | 30                                                    | _    | _                     | μA    |

| I <sub>BHHS</sub>  | Bus Hold High Sustaining<br>Current         | V <sub>IN</sub> = 0.7V <sub>CCIO</sub>     | -30                                                   | _    | _                     | μA    |

| I <sub>BHLO</sub>  | Bus Hold Low Overdrive<br>Current           | $0 \le V_{IN} \le V_{IH}$ (MAX)            | —                                                     | _    | 210                   | μA    |

| I <sub>BHLH</sub>  | Bus Hold High Overdrive<br>Current          | $0 \le V_{IN} \le V_{IH}$ (MAX)            | —                                                     | _    | -210                  | μA    |

| I <sub>CL</sub>    | PCI Low Clamp Current                       | -3 < V <sub>IN</sub> ≤ -1                  | -25 + (V <sub>IN</sub> + 1)/0.015                     | _    | —                     | mA    |

| I <sub>CH</sub>    | PCI High Clamp Current                      | $V_{CC} + 4 > V_{IN} \ge V_{CC} + 1$       | 25 + (V <sub>IN</sub> - V <sub>CC</sub> -1)/<br>0.015 | _    | —                     | mA    |

| V <sub>BHT</sub>   | Bus Hold trip Points                        | $0 \le V_{IN} \le V_{IH}$ (MAX)            | V <sub>IL</sub> (MAX)                                 | _    | V <sub>IH</sub> (MIN) | V     |

| C1                 | I/O Capacitance <sup>2</sup>                |                                            | _                                                     | 8    | _                     | pf    |

| C3 <sup>2</sup>    | Dedicated Input<br>Capacitance <sup>2</sup> |                                            | _                                                     | 6    | _                     | pf    |

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25°C, f = 1.0MHz

3. I<sub>PU</sub>, I<sub>PD</sub>, I<sub>BHLS</sub> and I<sub>BHHS</sub> have minimum values of 15 or -15µA if V<sub>CCIO</sub> is set to 1.2V nominal.

4. This table does not apply to SERDES pins.

5. For programmable I/Os.

### **Differential HSTL and SSTL**

Differential HSTL and SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

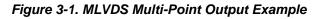

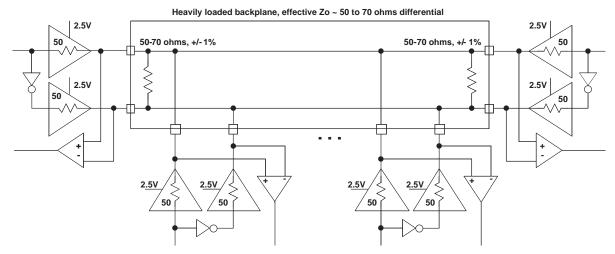

### MLVDS

The LatticeSC devices support the MLVDS standard. This industry standard is emulated using controlled impedance complementary LVCMOS outputs in conjunction with a parallel external resistor across the driver outputs. MLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-1 is one possible solution for bi-directional multi-point differential signals.

| Table | 3-1.  | ML | VDS | DC | Conditions <sup>1</sup> |

|-------|-------|----|-----|----|-------------------------|

| lance | • • • |    |     |    | 0011410110              |

|                     | Nominal                     |         |         |       |

|---------------------|-----------------------------|---------|---------|-------|

| Symbol              | Description                 | Zo = 50 | Zo = 70 | Units |

| Z <sub>OUT</sub>    | Output impedance            | 50      | 50      | ohm   |

| R <sub>TLEFT</sub>  | Left end termination        | 50      | 70      | ohm   |

| R <sub>TRIGHT</sub> | Right end termination       | 50      | 70      | ohm   |

| V <sub>OH</sub>     | Output high voltage         | 1.50    | 1.575   | V     |

| V <sub>OL</sub>     | Output low voltage          | 1.00    | 0.925   | V     |

| V <sub>OD</sub>     | Output differential voltage | 0.50    | 0.65    | V     |

| V <sub>CM</sub>     | Output common mode voltage  | 1.25    | 1.25    | V     |

| I <sub>DC</sub>     | DC output current           | 20.0    | 18.5    | mA    |

1. For input buffer, see LVDS table.

### sysCLOCK PLL Timing

| Parameter            | Description                                                                          | Conditions                                     | Min.   | Тур     | Max. | Units |

|----------------------|--------------------------------------------------------------------------------------|------------------------------------------------|--------|---------|------|-------|

| f <sub>IN</sub>      | Input Clock Frequency (CLKI, CLKFB)                                                  |                                                | 2      | —       | 1000 | MHz   |

| f <sub>OUT</sub>     | Output Clock Frequency (CLKOP,<br>CLKOS)                                             |                                                | 1.5625 | —       | 1000 | MHz   |

| f <sub>VCO</sub>     | PLL VCO Frequency                                                                    |                                                | 100    | —       | 1000 | MHz   |

| f <sub>PFD</sub>     | Phase Detector Input Frequency                                                       |                                                | 2      | —       | 700  | MHz   |

| AC Charac            | teristics                                                                            |                                                | •      |         |      |       |

| t <sub>DT</sub>      | Output Clock Duty Cycle                                                              | Default duty cycle selected (at 50% levels)    | 45     | —       | 55   | %     |

| <b>↓</b> 1           | Output Clock Pariod litter                                                           | $2 \text{ MHz} \le f_{PFD} \le 10 \text{ MHz}$ | —      | —       | 200  | ps    |

| t <sub>OPJIT</sub> 1 | Output Clock Period Jitter                                                           | f <sub>PFD</sub> > 10 MHz                      | —      | —       | 100  | ps    |

| t <sub>CPJIT</sub> 1 | Output Clock Cycle-to-Cycle Jitter                                                   |                                                | —      | —       | 100  | ps    |

| t <sub>SKEW</sub>    | Output Clock-to-Clock Skew (Between<br>Two Outputs with the Same Phase Set-<br>ting) |                                                | _      | _       | 20   | ps    |

| t <sub>LOCK</sub>    | PLL Lock-in Time                                                                     |                                                | —      | —       | 1    | ms    |

| t <sub>IPJIT</sub>   | Input Clock Period Jitter                                                            |                                                | —      | —       | ±250 | ps    |

| t <sub>HI</sub>      | Input Clock High Time                                                                | At 80% level                                   | 350    | —       | _    | ps    |

| t <sub>LO</sub>      | Input Clock Low Time                                                                 | At 20% level                                   | 350    | —       | —    | ps    |

| t <sub>RSWA</sub>    | Analog Reset Signal Pulse Width                                                      |                                                | 100    | —       | —    | ns    |

| t <sub>RSWD</sub>    | Digital Reset Signal Pulse Width                                                     |                                                | 3      | —       | _    | ns    |

| t <sub>DEL</sub>     | Timeshift Delay Step Size                                                            |                                                | 40     | 80      | 120  | ps    |

| t <sub>RANGE</sub>   | Timeshift Delay Range                                                                |                                                | —      | +/- 560 | —    | ps    |

| f <sub>SS</sub>      | Spread Spectrum Modulation Frequency                                                 |                                                | 30     | —       | 500  | KHz   |

| % Spread             | Percentage Downspread for SS Mode                                                    |                                                | 0.5    | —       | 1.5  | %     |

|                      | VCO Clock Phase Adjustment Accuracy                                                  |                                                | -5     | —       | 5    | 0     |

### **Over Recommended Operating Conditions**

1. Values are measured with FPGA logic active, no additional I/Os toggling and REFCLK total jitter = 30 ps

# LatticeSC/M Family Data Sheet Pinout Information

January 2008

Data Sheet DS1004

### **Signal Descriptions**

| Signal Name                            | I/O | Description                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                        |     |                                                                                                                                                                                                                                                                                                                                                                              |

|                                        |     | [Edge] indicates the edge of the device on which the pad is located.<br>Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                                                                                                                                |

|                                        |     | [Row/Column Number] indicates the PIC row or the column of the device on which the PIC exists. When Edge is T (Top) or (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                                                                                                                                    |

| P[Edge] [Row/Column Number*]_[A/B/C/D] | I/O | [A/B/C/D] indicates the PIO within the PIC to which the pad is connected.                                                                                                                                                                                                                                                                                                    |

|                                        |     | Some of these user programmable pins are shared with special func-<br>tion pins. These pin when not used as special purpose pins can be<br>programmed as I/Os for user logic.                                                                                                                                                                                                |

|                                        |     | During configuration the user-programmable I/Os are tri-stated with an internal pull-up resistor enabled. If any pin is not used (or not bonded to a package pin), it is also tri-stated with an internal pull-up resistor enabled after configuration.                                                                                                                      |

| VREF1_x, VREF2_x                       | _   | The reference supply pins for I/O bank x. Any I/O pin in a bank can be assigned as a reference supply pin, but software defaults use designated pin.                                                                                                                                                                                                                         |

| NC                                     | _   | No connect. NC pins should not be connected to any active signals, VCC or GND.                                                                                                                                                                                                                                                                                               |

| Non-SERDES Power Supplies              |     |                                                                                                                                                                                                                                                                                                                                                                              |

| VCCIOx                                 | —   | VCCIO - The power supply pins for I/O bank x. Dedicated pins.                                                                                                                                                                                                                                                                                                                |

| VCC121                                 | _   | 1.2V supply for configuration logic, PLLs and SERDES Rx, Tx and PLL. All VCC12 pins must be connected. As VCC12 supplies power for analog circuitry, VCC12 should be quiet and isolated from noisy digital board supplies.                                                                                                                                                   |

| VTT_x                                  | _   | Termination voltage for bank x. When VTT termination is not required, or used to provide the common mode termination voltage (VCMT), these pins can be left unconnected on the device. VCMT function is not used in the bank. If the internal or external VCMT function for differential input termination is used, the VTT pins should be unconnected and allowed to float. |

| GND                                    | _   | GND - Ground. Dedicated pins. All grounds must be electrically con-<br>nected at the board level.                                                                                                                                                                                                                                                                            |

| VCC                                    |     | VCC - The power supply pins for core logic. Dedicated pins (1.2V/ 1.0V).                                                                                                                                                                                                                                                                                                     |

| VCCAUX                                 | _   | VCCAUX - Auxiliary power supply pin - powers all differential and referenced input buffers. Dedicated pins (2.5V).                                                                                                                                                                                                                                                           |

| VCCJ                                   |     | VCCJ - The power supply pin for JTAG Test Access Port.                                                                                                                                                                                                                                                                                                                       |

| PROBE_VCC                              | _   | VCC signal - Connected to internal VCC node. Can be used for feed-<br>back to control an external board power converter. Can be uncon-<br>nected if not used.                                                                                                                                                                                                                |

<sup>© 2008</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# LFSC/M15 Logic Signal Connections: 256 fpBGA<sup>1,2</sup>

|             | LFSC/M15      |            |                             |  |  |  |

|-------------|---------------|------------|-----------------------------|--|--|--|

| Ball Number | Ball Function | VCCIO Bank | Dual Function               |  |  |  |

| E4          | A_VDDAX25_L   | -          |                             |  |  |  |

| B1          | A_REFCLKP_L   | -          |                             |  |  |  |

| C1          | A_REFCLKN_L   | -          |                             |  |  |  |

| D2          | RESP_ULC      | -          |                             |  |  |  |

| F5          | RESETN        | 1          |                             |  |  |  |

| D1          | DONE          | 1          |                             |  |  |  |

| E1          | INITN         | 1          |                             |  |  |  |

| E2          | MO            | 1          |                             |  |  |  |

| E3          | M1            | 1          |                             |  |  |  |

| E5          | M2            | 1          |                             |  |  |  |

| E6          | M3            | 1          |                             |  |  |  |

| F2          | PL15A         | 7          | ULC_PLLT_IN_A/ULC_PLLT_FB_I |  |  |  |

| F1          | PL15B         | 7          | ULC_PLLC_IN_A/ULC_PLLC_FB_  |  |  |  |

| F3          | PL17A         | 7          | ULC_DLLT_IN_C/ULC_DLLT_FB_  |  |  |  |

| G1          | PL17B         | 7          | ULC_DLLC_IN_C/ULC_DLLC_FB_  |  |  |  |

| G4          | PL18D         | 7          | VREF2_7                     |  |  |  |

| H3          | PL22A         | 7          |                             |  |  |  |

| H2          | PL22B         | 7          |                             |  |  |  |

| H5          | PL22C         | 7          | VREF1_7                     |  |  |  |

| G5          | PL22D         | 7          | DIFFR_7                     |  |  |  |

| H1          | PL23A         | 7          | PCLKT7_1                    |  |  |  |

| J1          | PL23B         | 7          | PCLKC7_1                    |  |  |  |

| J2          | PL24A         | 7          | PCLKT7_0                    |  |  |  |

| J3          | PL24B         | 7          | PCLKC7_0                    |  |  |  |

| H4          | PL24C         | 7          | PCLKT7_2                    |  |  |  |

| H6          | PL24D         | 7          | PCLKC7_2                    |  |  |  |

| J4          | PL26A         | 6          | PCLKT6_0                    |  |  |  |

| K5          | PL26B         | 6          | PCLKC6_0                    |  |  |  |

| J5          | PL26C         | 6          | PCLKT6_1                    |  |  |  |

| J6          | PL26D         | 6          | PCLKC6_1                    |  |  |  |

| K1          | PL28A         | 6          |                             |  |  |  |

| L1          | PL28B         | 6          |                             |  |  |  |

| L4          | PL28C         | 6          | PCLKT6_2                    |  |  |  |

| K4          | PL28D         | 6          | PCLKC6_2                    |  |  |  |

| L2          | PL31C         | 6          | VREF1_6                     |  |  |  |

| L3          | PL35A         | 6          |                             |  |  |  |

| M3          | PL35B         | 6          |                             |  |  |  |

| M2          | PL35D         | 6          | DIFFR_6                     |  |  |  |

| M1          | PL37A         | 6          |                             |  |  |  |

| N1          | PL37B         | 6          |                             |  |  |  |

| P2          | PL41D         | 6          | VREF2_6                     |  |  |  |

| M5          | PL43A         | 6          |                             |  |  |  |

# LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup>

|                |               | LFSC/M15      |                             |               |               | LFSC/M25                    |  |

|----------------|---------------|---------------|-----------------------------|---------------|---------------|-----------------------------|--|

| Ball<br>Number | Ball Function | VCCIO<br>Bank | Dual Function               | Ball Function | VCCIO<br>Bank | Dual Function               |  |

| F7             | A_VDDAX25_L   | -             |                             | A_VDDAX25_L   | -             |                             |  |

| B1             | A_REFCLKP_L   | -             |                             | A_REFCLKP_L   | -             |                             |  |

| C1             | A_REFCLKN_L   | -             |                             | A_REFCLKN_L   | -             |                             |  |

| D5             | VCC12         | -             |                             | VCC12         | -             |                             |  |

| A2             | RESP_ULC      | -             |                             | RESP_ULC      | -             |                             |  |

| E5             | VCC12         | -             |                             | VCC12         | -             |                             |  |

| D4             | VCC12         | -             |                             | VCC12         | -             |                             |  |

| H5             | RESETN        | 1             |                             | RESETN        | 1             |                             |  |

| H6             | TSALLN        | 1             |                             | TSALLN        | 1             |                             |  |

| G6             | DONE          | 1             |                             | DONE          | 1             |                             |  |

| G5             | INITN         | 1             |                             | INITN         | 1             |                             |  |

| F5             | MO            | 1             |                             | MO            | 1             |                             |  |

| F6             | M1            | 1             |                             | M1            | 1             |                             |  |

| F4             | M2            | 1             |                             | M2            | 1             |                             |  |

| E4             | M3            | 1             |                             | MЗ            | 1             |                             |  |

| D3             | PL15A         | 7             | ULC_PLLT_IN_A/ULC_PLLT_FB_B | PL16A         | 7             | ULC_PLLT_IN_A/ULC_PLLT_FB_B |  |

| D2             | PL15B         | 7             | ULC_PLLC_IN_A/ULC_PLLC_FB_B | PL16B         | 7             | ULC_PLLC_IN_A/ULC_PLLC_FB_B |  |

| J6             | PL15C         | 7             |                             | PL16C         | 7             |                             |  |

| J5             | PL15D         | 7             |                             | PL16D         | 7             |                             |  |

| E3             | PL17A         | 7             | ULC_DLLT_IN_C/ULC_DLLT_FB_D | PL17A         | 7             | ULC_DLLT_IN_C/ULC_DLLT_FB_D |  |

| E2             | PL17B         | 7             | ULC_DLLC_IN_C/ULC_DLLC_FB_D | PL17B         | 7             | ULC_DLLC_IN_C/ULC_DLLC_FB_D |  |

| K4             | PL17C         | 7             | ULC_PLLT_IN_B/ULC_PLLT_FB_A | PL17C         | 7             | ULC_PLLT_IN_B/ULC_PLLT_FB_A |  |

| J4             | PL17D         | 7             | ULC_PLLC_IN_B/ULC_PLLC_FB_A | PL17D         | 7             | ULC_PLLC_IN_B/ULC_PLLC_FB_A |  |

| F3             | PL18A         | 7             | ULC_DLLT_IN_D/ULC_DLLT_FB_C | PL18A         | 7             | ULC_DLLT_IN_D/ULC_DLLT_FB_C |  |

| G3             | PL18B         | 7             | ULC_DLLC_IN_D/ULC_DLLC_FB_C | PL18B         | 7             | ULC_DLLC_IN_D/ULC_DLLC_FB_C |  |

| K5             | PL18C         | 7             |                             | PL18C         | 7             |                             |  |

| K6             | PL18D         | 7             | VREF2_7                     | PL18D         | 7             | VREF2_7                     |  |

| F2             | PL19A         | 7             |                             | PL22A         | 7             |                             |  |

| F1             | PL19B         | 7             |                             | PL22B         | 7             |                             |  |

| E1             | PL19C         | 7             |                             | PL22C         | 7             |                             |  |

| D1             | PL19D         | 7             |                             | PL22D         | 7             |                             |  |

| K3             | PL22A         | 7             |                             | PL25A         | 7             |                             |  |

| L3             | PL22B         | 7             |                             | PL25B         | 7             |                             |  |

| L6             | PL22C         | 7             | VREF1_7                     | PL25C         | 7             | VREF1_7                     |  |

| M6             | PL22D         | 7             | DIFFR_7                     | PL25D         | 7             | DIFFR_7                     |  |

| J1             | PL23A         | 7             | PCLKT7_1                    | PL26A         | 7             | PCLKT7_1                    |  |

| K1             | PL23B         | 7             | PCLKC7_1                    | PL26B         | 7             | PCLKC7_1                    |  |

| L1             | PL24A         | 7             | PCLKT7_0                    | PL27A         | 7             | PCLKT7_0                    |  |

| M1             | PL24B         | 7             | PCLKC7_0                    | PL27B         | 7             | PCLKC7_0                    |  |

| P8             | PL24C         | 7             | PCLKT7_2                    | PL27C         | 7             | PCLKT7_2                    |  |

| R8             | PL24D         | 7             | PCLKC7_2                    | PL27D         | 7             | PCLKC7_2                    |  |

| N2             | PL26A         | 6             | PCLKT6_0                    | PL29A         | 6             | PCLKT6_0                    |  |

| N1             | PL26B         | 6             | PCLKC6_0                    | PL29B         | 6             | PCLKC6_0                    |  |

| R7             | PL26C         | 6             | PCLKT6_1                    | PL29C         | 6             | PCLKT6_1                    |  |

| R6             | PL26D         | 6             | PCLKC6_1                    | PL29D         | 6             | PCLKC6_1                    |  |

# LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup> (Cont.)

|                |               |               | С/М15                |               |               | SC/M25        |

|----------------|---------------|---------------|----------------------|---------------|---------------|---------------|

| Ball<br>Number | Ball Function | VCCIO<br>Bank | <b>Dual Function</b> | Ball Function | VCCIO<br>Bank | Dual Function |

| AB10           | VCC           | -             |                      | VCC           | -             |               |

| AB21           | VCC           | -             |                      | VCC           | -             |               |

| J10            | VCC           | -             |                      | VCC           | -             |               |

| J21            | VCC           | -             |                      | VCC           | -             |               |

| K10            | VCC           | -             |                      | VCC           | -             |               |

| K11            | VCC           | -             |                      | VCC           | -             |               |

| K12            | VCC           | -             |                      | VCC           | -             |               |

| K13            | VCC           | -             |                      | VCC           | -             |               |

| K14            | VCC           | -             |                      | VCC           | -             |               |

| K17            | VCC           | -             |                      | VCC           | -             |               |

| K18            | VCC           | -             |                      | VCC           | -             |               |

| K19            | VCC           | -             |                      | VCC           | -             |               |

| K20            | VCC           | -             |                      | VCC           | -             |               |

| K21            | VCC           | -             |                      | VCC           | -             |               |

| K22            | VCC           | -             |                      | VCC           | -             |               |

| K9             | VCC           | -             |                      | VCC           | -             |               |

| L10            | VCC           | -             |                      | VCC           | -             |               |

| L21            | VCC           | -             |                      | VCC           | -             |               |

| M10            | VCC           | -             |                      | VCC           | -             |               |

| M21            | VCC           | -             |                      | VCC           | -             |               |

| N10            | VCC           | -             |                      | VCC           | -             |               |

| N21            | VCC           | -             |                      | VCC           | -             |               |

| P10            | VCC           | -             |                      | VCC           | -             |               |

| P21            | VCC           | -             |                      | VCC           | -             |               |

| U10            | VCC           | -             |                      | VCC           | -             |               |

| U21            | VCC           | -             |                      | VCC           | -             |               |

| V10            | VCC           | -             |                      | VCC           | -             |               |

| V21            | VCC           | -             |                      | VCC           | -             |               |

| W10            | VCC           | -             |                      | VCC           | -             |               |

| W21            | VCC           | -             |                      | VCC           | -             |               |

| Y10            | VCC           | -             |                      | VCC           | -             |               |

| Y21            | VCC           | -             |                      | VCC           | -             |               |

| H11            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| H12            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| H19            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| H20            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| M23            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| M24            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| N23            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| N24            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| U23            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| U24            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| V23            | VCCAUX        | -             |                      | VCCAUX        | -             |               |

| V24            | VCCAUX        | -             |                      | VCCAUX        |               |               |

| V24            |               |               |                      |               |               |               |

### LFSC/M40, LFSC/M80 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup> (Cont.)

|                |                  |               | С/М40         |                  | LFSC/M80      |               |  |  |

|----------------|------------------|---------------|---------------|------------------|---------------|---------------|--|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual Function | Ball<br>Function | VCCIO<br>Bank | Dual Function |  |  |

| AL11           | GND              | -             |               | GND              | -             |               |  |  |

| AL17           | GND              | -             |               | GND              | -             |               |  |  |

| AL21           | GND              | -             |               | GND              | -             |               |  |  |

| AL27           | GND              | -             |               | GND              | -             |               |  |  |

| AL5            | GND              | -             |               | GND              | -             |               |  |  |

| AM14           | GND              | -             |               | GND              | -             |               |  |  |

| AM18           | GND              | -             |               | GND              | -             |               |  |  |

| AM24           | GND              | -             |               | GND              | -             |               |  |  |

| AM30           | GND              | -             |               | GND              | -             |               |  |  |

| AM8            | GND              | -             |               | GND              | -             |               |  |  |

| AN1            | GND              | -             |               | GND              | -             |               |  |  |

| AN34           | GND              | -             |               | GND              | -             |               |  |  |

| AP2            | GND              | -             |               | GND              | -             |               |  |  |

| AP33           | GND              | -             |               | GND              | -             |               |  |  |

| B1             | GND              | -             |               | GND              | -             |               |  |  |

| B34            | GND              | -             |               | GND              | -             |               |  |  |

| C11            | GND              | -             |               | GND              | -             |               |  |  |

| C12            | GND              | -             |               | GND              | -             |               |  |  |

| C13            | GND              | -             |               | GND              | -             |               |  |  |

| C14            | GND              | -             |               | GND              | -             |               |  |  |

| C17            | GND              | -             |               | GND              | -             |               |  |  |

| C21            | GND              | -             |               | GND              | -             |               |  |  |

| C22            | GND              | -             |               | GND              | -             |               |  |  |

| C23            | GND              | -             |               | GND              | -             |               |  |  |

| C24            | GND              | -             |               | GND              | -             |               |  |  |

| C26            | GND              | -             |               | GND              | -             |               |  |  |

| C27            | GND              | -             |               | GND              | -             |               |  |  |

| C30            | GND              | -             |               | GND              | -             |               |  |  |

| C31            | GND              | -             |               | GND              | -             |               |  |  |

| C4             | GND              | -             |               | GND              | -             |               |  |  |

| C5             | GND              | -             |               | GND              | -             |               |  |  |

| C8             | GND              | -             |               | GND              | -             |               |  |  |

| C9             | GND              | -             |               | GND              | -             |               |  |  |

| D18            | GND              | -             |               | GND              | -             |               |  |  |

| E32            | GND              | -             |               | GND              | -             |               |  |  |

| E4             | GND              | -             |               | GND              | -             |               |  |  |

| F19            | GND              | -             |               | GND              | -             |               |  |  |

| G16            | GND              | -             |               | GND              | -             |               |  |  |

| G29            | GND              | -             |               | GND              | -             |               |  |  |

| G7             | GND              | -             |               | GND              | -             |               |  |  |

| H3             | GND              | -             |               | GND              | -             |               |  |  |

| H31            | GND              | -             |               | GND              | -             |               |  |  |

| J10            | GND              | -             |               | GND              | -             |               |  |  |

| J15            | GND              | -             |               | GND              | -             |               |  |  |

| J26            | GND              | -             |               | GND              | -             |               |  |  |

### LFSC/M40, LFSC/M80 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup> (Cont.)

|                |                  |               | LFSC/M40      | 1                |               |               |

|----------------|------------------|---------------|---------------|------------------|---------------|---------------|

|                |                  |               |               |                  |               | LFSC/M80      |

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual Function | Ball<br>Function | VCCIO<br>Bank | Dual Function |

| AC19           | VTT_5            | 5             |               | VTT_5            | 5             |               |

| AC20           | VTT_5            | 5             |               | VTT_5            | 5             |               |

| AD22           | VTT_5            | 5             |               | VTT_5            | 5             |               |

| AB24           | VTT_6            | 6             |               | VTT_6            | 6             |               |

| W23            | VTT_6            | 6             |               | VTT_6            | 6             |               |

| Y23            | VTT_6            | 6             |               | VTT_6            | 6             |               |

| N24            | VTT_7            | 7             |               | VTT_7            | 7             |               |

| R23            | VTT_7            | 7             |               | VTT_7            | 7             |               |

| T23            | VTT_7            | 7             |               | VTT_7            | 7             |               |

| M12            | VDDAX25_R        | -             |               | VDDAX25_R        | -             |               |

| M23            | VDDAX25_L        | -             |               | VDDAX25_L        | -             |               |

| Y16            | GND              | -             |               | GND              | -             |               |

| Y14            | GND              | -             |               | GND              | -             |               |

| N21            | VCC12            | -             |               | VCC12            | -             |               |

| P22            | VCC12            | -             |               | VCC12            | -             |               |

| AA22           | VCC12            | -             |               | VCC12            | -             |               |

| AB21           | VCC12            | -             |               | VCC12            | -             |               |

| AB14           | VCC12            | -             |               | VCC12            | -             |               |

| AA13           | VCC12            | -             |               | VCC12            | -             |               |

| P13            | VCC12            | -             |               | VCC12            | -             |               |

| N14            | VCC12            | -             |               | VCC12            | -             |               |

| G26            | NC               | -             |               | NC               | -             |               |

| G9             | NC               | -             |               | NC               | -             |               |

| J12            | NC               | -             |               | NC               | -             |               |

| H12            | NC               | -             |               | NC               | -             |               |

| H23            | NC               | -             |               | NC               | -             |               |

| J23            | NC               | -             |               | NC               | -             |               |

1. Differential pair grouping within a PCI is A (True) and B (complement) and C (True) and D (Complement).

2. The LatticeSC/M40 and LatticeSC/M80 in an 1152-pin package support a 32-bit MPI interface.

# LFSC/M115 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup>

|            |               | LFSC/M115  |               |  |  |  |  |  |

|------------|---------------|------------|---------------|--|--|--|--|--|

| all Number | Ball Function | VCCIO Bank | Dual Function |  |  |  |  |  |

| W30        | PL69B         | 6          |               |  |  |  |  |  |

| W27        | PL69C         | 6          | VREF1_6       |  |  |  |  |  |

| Y27        | PL69D         | 6          |               |  |  |  |  |  |

| Т33        | PL70A         | 6          |               |  |  |  |  |  |

| U33        | PL70B         | 6          |               |  |  |  |  |  |

| V25        | PL70C         | 6          |               |  |  |  |  |  |

| W25        | PL70D         | 6          |               |  |  |  |  |  |

| U34        | PL71A         | 6          |               |  |  |  |  |  |

| V34        | PL71B         | 6          |               |  |  |  |  |  |

| V26        | PL71C         | 6          |               |  |  |  |  |  |

| W26        | PL71D         | 6          |               |  |  |  |  |  |

| V33        | PL74A         | 6          |               |  |  |  |  |  |

| W33        | PL74B         | 6          |               |  |  |  |  |  |

| V24        | PL74C         | 6          |               |  |  |  |  |  |

| W24        | PL74D         | 6          |               |  |  |  |  |  |

| W31        | PL77A         | 6          |               |  |  |  |  |  |

| Y31        | PL77B         | 6          |               |  |  |  |  |  |

| Y29        | PL77C         | 6          |               |  |  |  |  |  |

| AA29       | PL77D         | 6          |               |  |  |  |  |  |

| Y33        | PL79A         | 6          |               |  |  |  |  |  |

| AA33       | PL79B         | 6          |               |  |  |  |  |  |

| Y28        | PL79C         | 6          |               |  |  |  |  |  |

| AA28       | PL79D         | 6          |               |  |  |  |  |  |

| AB32       | PL90A         | 6          |               |  |  |  |  |  |

| AC32       | PL90B         | 6          |               |  |  |  |  |  |

| AA26       | PL90C         | 6          |               |  |  |  |  |  |

| AA27       | PL90D         | 6          | DIFFR_6       |  |  |  |  |  |

| AB31       | PL91A         | 6          |               |  |  |  |  |  |

| AC31       | PL91B         | 6          |               |  |  |  |  |  |

| Y24        | PL91C         | 6          |               |  |  |  |  |  |

| AA24       | PL91D         | 6          |               |  |  |  |  |  |

| AE34       | PL92A         | 6          |               |  |  |  |  |  |

| AF34       | PL92B         | 6          |               |  |  |  |  |  |

| AB30       | PL92C         | 6          |               |  |  |  |  |  |

| AC30       | PL92D         | 6          |               |  |  |  |  |  |

| AD33       | PL94A         | 6          |               |  |  |  |  |  |

| AE33       | PL94B         | 6          |               |  |  |  |  |  |

| AD30       | PL94C         | 6          |               |  |  |  |  |  |

| AE30       | PL94D         | 6          |               |  |  |  |  |  |

| AE32       | PL96A         | 6          |               |  |  |  |  |  |

| AF32       | PL96B         | 6          |               |  |  |  |  |  |

| AA25       | PL96C         | 6          |               |  |  |  |  |  |

| AB25       | PL96D         | 6          |               |  |  |  |  |  |

### LFSC/M115 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup>

|             |               | LFSC/M115  |                    |

|-------------|---------------|------------|--------------------|

| Ball Number | Ball Function | VCCIO Bank | Dual Function      |

| F25         | B_HDINN0_L    | -          | PCS 361 CH 0 IN N  |

| E25         | B_HDINP0_L    | -          | PCS 361 CH 0 IN P  |

| D28         | B_VDDIB0_L    | -          |                    |

| G25         | VCC12         | -          |                    |

| D29         | A_VDDIB3_L    | -          |                    |

| C25         | VCC12         | -          |                    |

| A25         | A_HDINP3_L    | -          | PCS 360 CH 3 IN P  |

| B25         | A_HDINN3_L    | -          | PCS 360 CH 3 IN N  |

| A26         | A_HDOUTP3_L   | -          | PCS 360 CH 3 OUT P |

| E27         | VCC12         | -          |                    |

| B26         | A_HDOUTN3_L   | -          | PCS 360 CH 3 OUT N |

| F26         | A_VDDOB3_L    | -          |                    |

| B27         | A_HDOUTN2_L   | -          | PCS 360 CH 2 OUT N |

| F27         | A_VDDOB2_L    | -          |                    |

| A27         | A_HDOUTP2_L   | -          | PCS 360 CH 2 OUT P |

| E28         | VCC12         | -          |                    |

| B28         | A_HDINN2_L    | -          | PCS 360 CH 2 IN N  |

| A28         | A_HDINP2_L    | -          | PCS 360 CH 2 IN P  |

| D30         | A_VDDIB2_L    | -          |                    |

| C28         | VCC12         | -          |                    |

| D31         | A_VDDIB1_L    | -          |                    |

| C29         | VCC12         | -          |                    |

| A29         | A_HDINP1_L    | -          | PCS 360 CH 1 IN P  |

| B29         | A_HDINN1_L    | -          | PCS 360 CH 1 IN N  |

| A30         | A_HDOUTP1_L   | -          | PCS 360 CH 1 OUT P |

| E29         | VCC12         | -          |                    |

| B30         | A_HDOUTN1_L   | -          | PCS 360 CH 1 OUT N |

| F28         | A_VDDOB1_L    | -          |                    |

| B31         | A_HDOUTN0_L   | -          | PCS 360 CH 0 OUT N |

| F29         | A_VDDOB0_L    | -          |                    |

| A31         | A_HDOUTP0_L   | -          | PCS 360 CH 0 OUT P |

| E30         | VCC12         | -          |                    |

| B32         | A_HDINN0_L    | -          | PCS 360 CH 0 IN N  |

| A32         | A_HDINP0_L    | -          | PCS 360 CH 0 IN P  |

| D32         | A_VDDIB0_L    | -          |                    |

| C32         | VCC12         | -          |                    |

| E34         | PL30A         | 7          |                    |

| F34         | PL30B         | 7          |                    |

| F33         | PL34A         | 7          |                    |

| G33         | PL34B         | 7          |                    |

| K30         | PL38A         | 7          |                    |

| L30         | PL38B         | 7          |                    |

| G34         | PL40A         | 7          |                    |

# LFSC/M80, LFSC/M115 Logic Signal Connections: 1704 fcBGA<sup>1, 2</sup> (Cont.)

|                |                  | L             | _FSC/M80         | LFSC/M115        |               |                  |  |

|----------------|------------------|---------------|------------------|------------------|---------------|------------------|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function | Ball<br>Function | VCCIO<br>Bank | Dual<br>Function |  |

| W33            | PL42C            | 7             |                  | PL56C            | 7             |                  |  |

| Y33            | PL42D            | 7             |                  | PL56D            | 7             |                  |  |

| W37            | PL43A            | 7             |                  | PL57A            | 7             |                  |  |

| Y37            | PL43B            | 7             |                  | PL57B            | 7             |                  |  |

| Y32            | PL43C            | 7             |                  | PL57C            | 7             |                  |  |

| AA32           | PL43D            | 7             |                  | PL57D            | 7             |                  |  |

| U38            | PL46A            | 7             |                  | PL60A            | 7             |                  |  |

| V38            | PL46B            | 7             |                  | PL60B            | 7             |                  |  |