Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                    |

|--------------------------------|------------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                           |

| Number of LABs/CLBs            | 6250                                                                               |

| Number of Logic Elements/Cells | 25000                                                                              |

| Total RAM Bits                 | 1966080                                                                            |

| Number of I/O                  | 476                                                                                |

| Number of Gates                | -                                                                                  |

| Voltage - Supply               | 0.95V ~ 1.26V                                                                      |

| Mounting Type                  | Surface Mount                                                                      |

| Operating Temperature          | -40°C ~ 105°C (TJ)                                                                 |

| Package / Case                 | 1020-BBGA, FCBGA                                                                   |

| Supplier Device Package        | 1020-OFCBGA (33x33)                                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfscm3ga25ep1-5ffn1020i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

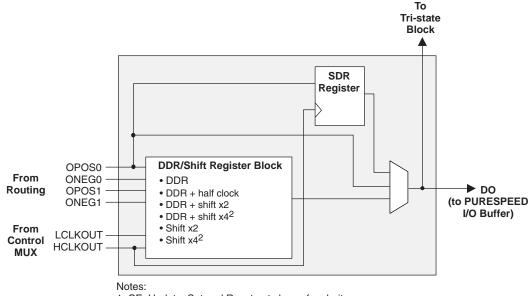

Figure 2-22. Output Register Block<sup>1</sup>

- 1. CE, Update, Set and Reset not shown for clarity.

- 2. By four shift modes utilizes DDR/Shift register block from paired PIO.

- 3. DDR/Shift register block shared with tristate block.

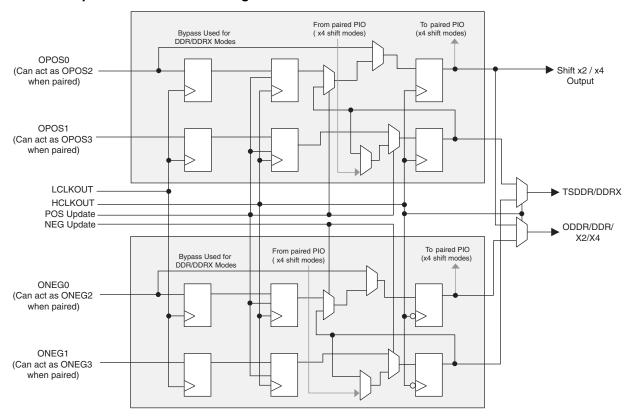

Figure 2-23. Output/Tristate DDR/Shift Register Block

#### 3. Bottom Side (Banks 4 and 5)

These buffers can support LVCMOS standards up to 3.3V, including PCI33, PCI-X33 and SSTL-33. Differential receivers are provided on all PIO pairs but true HLVDS and RSDS differential drivers are not available. Adaptive input logic is available on PIOs A or C.

Table 2-8 lists the standards supported by each side.

Table 2-8. I/O Standards Supported by Different Banks

| Description                   | Top Side                                                                                                                                                                                                                                                                                    | Right Side                                                                                                                                                                                                           | Bottom Side                                                                                                                                                                                                                                                                                   | Left Side                                                                                                                                                                                                            |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | Banks 1                                                                                                                                                                                                                                                                                     | Banks 2-3                                                                                                                                                                                                            | Banks 4-5                                                                                                                                                                                                                                                                                     | Banks 6-7                                                                                                                                                                                                            |

| I/O Buffer Type               | Single-ended,<br>Differential Receiver                                                                                                                                                                                                                                                      | Single-ended, Differential Receiver and Driver                                                                                                                                                                       | Single-ended,<br>Differential Receiver                                                                                                                                                                                                                                                        | Single-ended, Differential Receiver and Driver                                                                                                                                                                       |

| Output Standards<br>Supported | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 SSTL18_I, II SSTL25_ I, II SSTL33_ I, II HSTL15_I, II, III¹, IV¹ HSTL18_I, II, III¹, IV¹ SSTL18D_I, II SSTL25D_I, II SSTL33D_I, II HSTL15D_I, II HSTL15D_I, II HSTL15D_I, II PCI33 PCIX15 PCIX33 AGP1X33 AGP2X33 MLVDS/BLVDS GTL², GTL+² | LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 SSTL18_I, II SSTL25_ I, II HSTL15_I,III HSTL18_I,II,III PCIX15 SSTL18D_I, II SSTL25D_I, II HSTL15D_I, II HSTL15D_I, II HSTL18D_I, II LVDS/RSDS Mini-LVDS MLVDS/BLVDS GTL², GTL+² | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 SSTL18_I, II SSTL25_ I, II SSTL33_ I, II HSTL15_I, II, IIII¹, IV¹ HSTL18_I, II, IIII¹, IV¹ SSTL18D_I, II SSTL25D_I, II SSTL33D_I, II HSTL15D_I, II HSTL15D_I, II HSTL15D_I, II PCI33 PCIX15 PCIX33 AGP1X33 AGP2X33 MLVDS/BLVDS GTL², GTL+² | LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 SSTL18_I, II SSTL25_ I, II HSTL15_I,III HSTL18_I,II,III PCIX15 SSTL18D_I, II SSTL25D_I, II HSTL15D_I, II HSTL15D_I, II HSTL15D_I, II LVDS/RSDS Mini-LVDS MLVDS/BLVDS GTL², GTL+² |

| Input Standards               | Single-ended,                                                                                                                                                                                                                                                                               | Single-ended,                                                                                                                                                                                                        | Single-ended,                                                                                                                                                                                                                                                                                 | Single-ended,                                                                                                                                                                                                        |

| Supported                     | Differential                                                                                                                                                                                                                                                                                | Differential                                                                                                                                                                                                         | Differential                                                                                                                                                                                                                                                                                  | Differential                                                                                                                                                                                                         |

| Clock Inputs                  | Single-ended,                                                                                                                                                                                                                                                                               | Single-ended,                                                                                                                                                                                                        | Single-ended,                                                                                                                                                                                                                                                                                 | Single-ended,                                                                                                                                                                                                        |

|                               | Differential                                                                                                                                                                                                                                                                                | Differential                                                                                                                                                                                                         | Differential                                                                                                                                                                                                                                                                                  | Differential                                                                                                                                                                                                         |

| Differential Output           | LVDS/MLVDS/BLVDS/                                                                                                                                                                                                                                                                           | MLVDS/BLVDS/                                                                                                                                                                                                         | LVDS/MLVDS/BLVDS/                                                                                                                                                                                                                                                                             | MLVDS/BLVDS/                                                                                                                                                                                                         |

| Support via Emulation         | LVPECL                                                                                                                                                                                                                                                                                      | LVPECL                                                                                                                                                                                                               | LVPECL                                                                                                                                                                                                                                                                                        | LVPECL                                                                                                                                                                                                               |

| AIL Support                   | No                                                                                                                                                                                                                                                                                          | Yes                                                                                                                                                                                                                  | Yes                                                                                                                                                                                                                                                                                           | Yes                                                                                                                                                                                                                  |

<sup>1.</sup> Input only.

### **Supported Standards**

The LatticeSC PURESPEED I/O buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL and other standards. The buffers support the LVTTL, LVC-MOS 12, 15, 18, 25 and 33 standards. In the LVCMOS and LVTTL modes, the buffer has individually configurable options for drive strength, termination resistance, bus maintenance (weak pull-up, weak pull-down, or a bus-keeper latch) and open drain. Other single-ended standards supported include SSTL, HSTL, GTL (input only), GTL+ (input only), PCI33, PCIX33, PCIX15, AGP-1X33 and AGP-2X33. Differential standards supported include LVDS, RSDS, BLVDS, MLVDS, LVPECL, differential SSTL and differential HSTL. Tables 12 and 13 show the I/O standards (together with their supply and reference voltages) supported by the LatticeSC devices. The tables also provide the available internal termination schemes. For further information on utilizing the PURESPEED I/O buffer to support a variety of standards please see details of additional technical documentation at the end of this data sheet.

<sup>2.</sup> Input only. Outputs supported by bussing multiple outputs together.

Table 2-9. Supported Input Standards

| Input Standard                         | V <sub>REF</sub> (Nom.) | V <sub>CCIO</sub> ¹ (Nom.) | On-chip Termination                                                                                                                                |

|----------------------------------------|-------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Single Ended Interfaces                | •                       |                            |                                                                                                                                                    |

| LVTTL33 <sup>3</sup>                   | _                       | 3.3                        | None                                                                                                                                               |

| LVCMOS 33, 25, 18, 15, 12 <sup>3</sup> | _                       | 3.3/2.5/1.8/1.5/1.2        | None                                                                                                                                               |

| PCI33, PCIX33, AGP1X33 <sup>3</sup>    | _                       | 3.3                        | None                                                                                                                                               |

| PCIX15                                 | 0.75                    | 1.5 <sup>2</sup>           | None / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210                                                                           |

| AGP2X33                                | 1.32                    | _                          | None                                                                                                                                               |

| HSTL18_I, II                           | 0.9                     | 1.8 <sup>2</sup>           | None / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210                                                                           |

| HSTL18_III, IV                         | 1.08                    | 1.8 <sup>2</sup>           | None / V <sub>CCIO</sub> : 50                                                                                                                      |

| HSTL15_I, II                           | 0.75                    | 1.5 <sup>2</sup>           | None / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210                                                                           |

| HSTL15_III, IV                         | 0.9                     | 1.5 <sup>2</sup>           | None / V <sub>CCIO</sub> : 50                                                                                                                      |

| SSTL33_I, II                           | 1.5                     | 3.3                        | None                                                                                                                                               |

| SSTL25_I, II                           | 1.25                    | 2.5 <sup>2</sup>           | None / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210                                                                           |

| SSTL18_I, II                           | 0.9                     | 1.8 <sup>2</sup>           | None / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210                                                                           |

| GTL+, GTL                              | 1.0 / 0.8               | 1.5 / 1.2 <sup>2</sup>     | None / V <sub>CCIO</sub> : 50                                                                                                                      |

| Differential Interfaces                |                         |                            |                                                                                                                                                    |

| SSTL18D_I, II                          | _                       | 1.8 <sup>2</sup>           | None / Diff: 120, 150, 220, 420/ Diff to V <sub>CMT</sub> : 120, 150, 220, 420 / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210 |

| SSTL25D_I, II                          | _                       | 2.5 <sup>2</sup>           | None / Diff: 120, 150, 220, 420/ Diff to V <sub>CMT</sub> : 120, 150, 220, 420 / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210 |

| SSTL33D_I, II                          | _                       | 3.3                        | None                                                                                                                                               |

| HSTL15D_I, II                          | _                       | 1.5²                       | None / Diff: 120, 150, 220, 420/ Diff to V <sub>CMT</sub> : 120, 150, 220, 420 / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210 |

| HSTL18D_I, II                          | _                       | 1.8 <sup>2</sup>           | None / Diff: 120, 150, 220, 420/ Diff to V <sub>CMT</sub> : 120, 150, 220, 420 / V <sub>CCIO</sub> / 2: 50, 60/ V <sub>TT</sub> : 60, 75, 120, 210 |

| LVDS                                   | _                       | _                          | None / Diff: 120, 150, 220, 240/ Diff to V <sub>CMT</sub> : 120, 150, 220, 240                                                                     |

| Mini-LVDS                              | _                       | _                          | None / Diff: 120, 150 / Diff to V <sub>CMT</sub> : 120, 150                                                                                        |

| BLVDS25                                | _                       | _                          | None                                                                                                                                               |

| MLVDS25                                | _                       | _                          | None                                                                                                                                               |

| RSDS                                   | _                       | _                          | None / Diff: 120, 150, 220, 240/ Diff to V <sub>CMT</sub> : 120, 150, 220, 240                                                                     |

| LVPECL33                               | _                       | ≤2.5                       | None / Diff: 120, 150, 220, 240/ Diff to V <sub>CMT</sub> : 120, 150, 220, 240                                                                     |

When not specified V<sub>CCIO</sub> can be set anywhere in the valid operating range.

V<sub>CCIO</sub> needed for on-chip termination to V<sub>CCIO</sub>/2 or V<sub>CCIO</sub> only. V<sub>CCIO</sub> is not specified for off-chip termination or V<sub>TT</sub> termination.

All ratioed input buffers and dedicated pin input buffers include hysteresis with a typical value of 50mV.

this allows for easy integration with the rest of the system. These capabilities make the LatticeSC ideal for many multiple power supply and hot-swap applications. The maximum current during hot socketing is 4mA. See Hot Socketing Specifications in Chapter 3 of this data sheet.

### **Power-Up Requirements**

To prevent high power supply and input pin currents, each VCC, VCC12, VCCAUX, VCCIO and VCCJ power supplies must have a monotonic ramp up time of 75 ms or less to reach its minimum operating voltage. Apart from VCC and VCC12, which have an additional requirement, and VCCIO and VCCAUX, which also have an additional requirement, the VCC, VCC12, VCCAUX, VCCIO and VCCJ power supplies can ramp up in any order, with no restriction on the time between them. However, the ramp time for each must be 75 ms or less. Configuration of the device will not proceed until the last power supply has reached its minimum operating voltage.

#### Additional Requirement for VCC and VCC12:

VCC12 must always be higher than VCC. This condition must be maintained at ALL times, including during powerup and power-down. Note that for 1.2V only operation, it is advisable to source both of these supplies from the same power supply.

#### Additional Requirement for VCCIO and VCCAUX:

If any VCCIOs are 1.2/1.5/1.8V, then VCCAUX MUST be applied before them. If any VCCIO is 1.2/1.5/1.8V and is powered up before VCCAUX, then when VCCAUX is powered up, it may drag VCCIO up with it as it crosses through the VCCIO value. (Note: If the VCCIO supply is capable of sinking current, as well as the more usual sourcing capability, this behavior is eliminated. However, the amount of current that the supply needs to sink is unknown and is likely to be in the hundreds of milliamps range).

### **Power-Down Requirements**

To prevent high power supply and input pin currents, power must be removed monotonically from either VCC or VCCAUX (and must reach the power-down trip point of 0.5V for VCC, 0.95V for VCCAUX) before power is removed monotonically from VCC12, any of the VCCIOs, or VCCJ. Note that VCC12 can be removed at the same time as VCC, but it cannot be removed earlier. In many applications, VCC and VCC12 will be sourced from the same power supply and so will be removed together. For systems where disturbance of the user pins is a don't care condition, the power supplies can be removed in any order as long as they power down monotonically within 200ms of each other.

Additionally, if any banks have VCCIO=3.3V nominal (potentially banks 1, 4, 5) then VCCIO for those banks must not be lower than VCCAUX during power-down. The normal variation in ramp-up times of power supplies and voltage regulators is not a concern here.

Note: The SERDES power supplies are NOT included in these requirements and have no specific sequencing requirements. However, when using the SERDES with VDDIB or VDDOB that is greater than 1.2V (1.5V nominal for example), the SERDES should not be left in a steady state condition with the 1.5V power applied and the 1.2V power not applied. Both the 1.2V and 1.5V power should be applied to the SERDES at nominally the same time. The normal variation in the ramp-up times of power supplies and voltage regulators is not a concern here.

### **SERDES Power Supply Sequencing Requirements**

When using the SERDES with 1.5V VDDIB or VDDOB supplies, the SERDES should not be left in a steady state condition with the 1.5V power applied and the 1.2V power not applied. Both the 1.2V and the 1.5V power should be applied to the SERDES at nominally the same time. The normal variation in ramp-up times of power supples and voltage regulators is not a concern.

#### Additional Requirement for SERDES Power Supply

All VCC12 pins need to be connected on all devices independent of functionality used on the device. This analog supply is used by both the RX and TX portions of the SERDES and is used to control the core SERDES logic regardless of the SERDES being used in the design. VDDIB and VDDOB are used as supplies for the terminations on the CML input and output buffers. If a particular channel is not used, these can be UNCONNECTED (floating).

# LatticeSC/M Family Data Sheet **DC and Switching Characteristics**

December 2011 Data Sheet DS1004

# **Absolute Maximum Ratings**

| Supply Voltage V <sub>CC</sub> , V <sub>CC12</sub> , V <sub>DDIB</sub> , V <sub>DDOB</sub> | 0.5 to 1.6V   |

|--------------------------------------------------------------------------------------------|---------------|

| Supply Voltage V <sub>CCAUX</sub> , V <sub>DDAX25</sub> , V <sub>TT</sub>                  | -0.5 to 2.75V |

| Supply Voltage V <sub>CCJ</sub>                                                            | 0.5 to 3.6V   |

| Supply Voltage V <sub>CCIO</sub> (Banks 1, 4, 5)                                           | 0.5 to 3.6V   |

| Supply Voltage V <sub>CCIO</sub> (Banks 2, 3, 6, 7)                                        | -0.5 to 2.75V |

| Input or I/O Tristate Voltage Applied (Banks 1, 4, 5)                                      | 0.5 to 3.6V   |

| Input or I/O Tristate Voltage Applied (Banks 2, 3, 6, 7)                                   | -0.5 to 2.75V |

| Storage Temperature (Ambient)                                                              | -65 to 150°C  |

| Junction Temperature Under Bias (Tj)                                                       | +125°C        |

- 1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- 2. Compliance with the Lattice Thermal Management document is required.

- 3. All voltages referenced to GND.

- 4. Undershoot and overshoot of -2V to (VIHMAX +2) volts is permitted for a duration of <20ns.

# **Recommended Operating Conditions**

| Symbol                                  | Parameter                                                                                                                                 |       | Max.                     | Units |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------|-------|

| V <sub>CC</sub> <sup>5</sup>            | Core Supply Voltage (Nominal 1.2V Operation)                                                                                              | 0.95  | 1.26                     | V     |

| V <sub>CCAUX</sub> <sup>6</sup>         | Programmable I/O Auxiliary Supply Voltage                                                                                                 | 2.375 | 2.625                    | V     |

| V <sub>CCIO</sub> <sup>1, 2, 5, 6</sup> | Programmable I/O Driver Supply Voltage (Banks 1, 4, 5)                                                                                    | 1.14  | 3.45                     | V     |

| V <sub>CCIO</sub> <sup>1, 2, 5, 6</sup> | Programmable I/O Driver Supply Voltage (Banks 2, 3, 6, 7)                                                                                 | 1.14  | 2.625                    | V     |

| V <sub>CC12</sub> <sup>4, 5</sup>       | Internal 1.2V Power Supply Voltage for Configuration Logic and FPGA PLL, SERDES PLL Power Supply Voltage and SERDES Analog Supply Voltage | 1.14  | 1.26                     | V     |

| $V_{\rm DDIB}$                          | SERDES Input Buffer Supply Voltage                                                                                                        | 1.14  | 1.575                    | V     |

| $V_{DDOB}$                              | SERDES Output Buffer Supply Voltage                                                                                                       | 1.14  | 1.575                    | V     |

| V <sub>DDAX25</sub>                     | SERDES Termination Auxiliary Supply Voltage                                                                                               | 2.375 | 2.625                    | V     |

| V <sub>CCJ</sub> <sup>1, 5</sup>        | Supply Voltage for IEEE 1149.1 Test Access Port                                                                                           | 1.71  | 3.45                     | V     |

| V <sub>TT</sub> <sup>2, 3</sup>         | Programmable I/O Termination Power Supply                                                                                                 | 0.5   | V <sub>CCAUX</sub> - 0.5 | V     |

| t <sub>JCOM</sub>                       | Junction Temperature, Commercial Operation                                                                                                | 0     | +85                      | С     |

| t <sub>JIND</sub>                       | Junction Temperature, Industrial Operation                                                                                                | -40   | 105                      | С     |

- 1. If  $V_{CCIO}$  or  $V_{CCJ}$  is set to 2.5V, they must be connected to the same power supply as  $V_{CCAUX}$ .

- 2. See recommended voltages by I/O standard in subsequent table.

- 3. When V<sub>TT</sub> termination is not required, or used to provide the common mode termination voltage (V<sub>CMT</sub>), these pins can be left unconnected

- 4. V<sub>CC12</sub> cannot be lower than V<sub>CC</sub> at any time. For 1.2V operation, it is recommended that the V<sub>CC</sub> and V<sub>CC12</sub> supplies be tied together with proper noise decoupling between the digital VCC and analog VCC12 supplies.

- 5.  $V_{CC,}$   $V_{CCIO}$  (all banks),  $V_{CC12}$  and  $V_{CCJ}$  must reach their minimum values before configuration will proceed.

6. If  $V_{CCIO}$  for a bank is nominally 1.2V/1.5V/1.8V, then  $V_{CCAUX}$  must always be higher than  $V_{CCIO}$  during power up.

### **Differential HSTL and SSTL**

Differential HSTL and SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

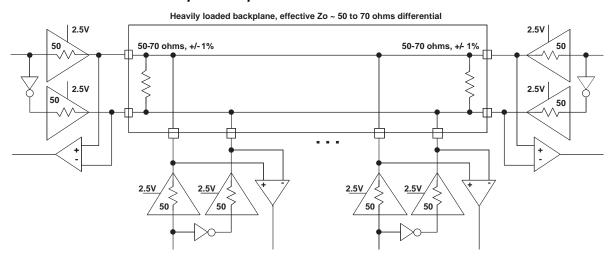

#### **MLVDS**

The LatticeSC devices support the MLVDS standard. This industry standard is emulated using controlled impedance complementary LVCMOS outputs in conjunction with a parallel external resistor across the driver outputs. MLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-1 is one possible solution for bi-directional multi-point differential signals.

Figure 3-1. MLVDS Multi-Point Output Example

Table 3-1. MLVDS DC Conditions<sup>1</sup>

#### **Over Recommended Operating Conditions**

|                     |                             | Nominal |         |       |

|---------------------|-----------------------------|---------|---------|-------|

| Symbol              | Description                 | Zo = 50 | Zo = 70 | Units |

| Z <sub>OUT</sub>    | Output impedance            | 50      | 50      | ohm   |

| R <sub>TLEFT</sub>  | Left end termination        | 50      | 70      | ohm   |

| R <sub>TRIGHT</sub> | Right end termination       | 50      | 70      | ohm   |

| V <sub>OH</sub>     | Output high voltage         | 1.50    | 1.575   | V     |

| V <sub>OL</sub>     | Output low voltage          | 1.00    | 0.925   | V     |

| V <sub>OD</sub>     | Output differential voltage | 0.50    | 0.65    | V     |

| V <sub>CM</sub>     | Output common mode voltage  | 1.25    | 1.25    | V     |

| I <sub>DC</sub>     | DC output current           | 20.0    | 18.5    | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

#### **LVPECL**

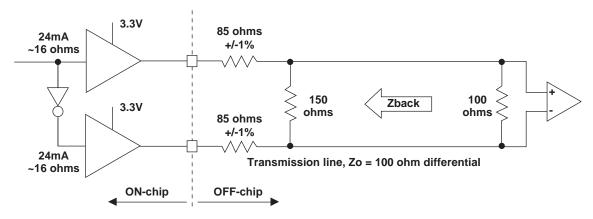

The LatticeSC devices support differential LVPECL standard. This standard is emulated using controlled impedance complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

Figure 3-3. Differential LVPECL

Table 3-3. LVPECL DC Conditions1

### **Over Recommended Operating Conditions**

| Symbol            | Description                 | Nominal | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 16      | ohm   |

| R <sub>S</sub>    | Driver series resistor      | 85      | ohm   |

| R <sub>P</sub>    | Driver parallel resistor    | 150     | ohm   |

| R <sub>T</sub>    | Receiver termination        | 100     | ohm   |

| V <sub>OH</sub>   | Output high voltage         | 2.03    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.27    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.76    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.65    | V     |

| Z <sub>BACK</sub> | Back impedance              | 86      | ohm   |

| I <sub>DC</sub>   | DC output current           | 12.6    | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

For further information on LVPECL, BLVDS, MLVDS and other differential interfaces please see details of additional technical documentation at the end of this data sheet.

### **On-die Differential Common Mode Termination**

| Symbol           | Description                         | Min. | Тур. | Max. | Units |

|------------------|-------------------------------------|------|------|------|-------|

| C <sub>CMT</sub> | Capacitance V <sub>CMT</sub> to GND | _    | 40   | _    | pF    |

# Input Delay Block/AIL Timing

| Parameter         | Description          | Min.                                                        | Тур. | Max. | Units |

|-------------------|----------------------|-------------------------------------------------------------|------|------|-------|

| t <sub>FDEL</sub> | Fine delay time      | 35                                                          | 45   | 80   | ps    |

| t <sub>CDEL</sub> | Coarse delay time    | 1120                                                        | 1440 | 2560 | ps    |

| jt <sub>AIL</sub> | AIL jitter tolerance | 1- ((N <sup>1</sup> * t <sub>FDEL</sub> ) / (Clock Period)) |      |      | UI    |

<sup>1.</sup> N = number of fine delays used in a particular AIL setting

# **GSR Timing**

|                             |                                           |       | -7   |      | -    | -5   |      |      |       |

|-----------------------------|-------------------------------------------|-------|------|------|------|------|------|------|-------|

| Parameter                   | Description                               | vcc   | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| Maximum operating frequency |                                           | 1.14V | _    | 438  | _    | 417  | _    | 398  | MHz   |

| <sup>I</sup> SYNC_GSR_MAX   | synchronous GSR                           | 0.95V | _    | 378  | _    | 355  | _    | 337  | MHz   |

| tasync_gsr_mpw              | Minimum pulse width of asynchronous input | _     | _    | _    | _    | _    | 3.3  | _    | ns    |

Note: Synchronous GSR goes out of reset in two cycles from the clock edge where the setup time of the FF was met.

# **Internal System Bus Timing**

|                   |                                                           | -7   |      | -6   |      | -5   |      |       |

|-------------------|-----------------------------------------------------------|------|------|------|------|------|------|-------|

| Parameter         | Description                                               | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| t <sub>HCLK</sub> | Maximum operating frequency for internal system bus HCLK. | _    | 200  | _    | 200  | _    | 200  | MHz   |

Note: There is no minimum frequency. If HCLK is sourced from the embedded oscillator, the minimum frequency limitation of the oscillator/divider is about 0.3 MHz. Refer to the osciallator data for missing configuration modes.

# **Timing Diagrams**

# **PFU Timing Diagrams**

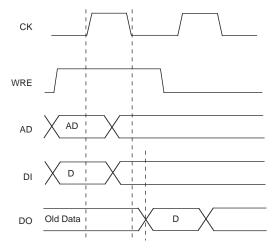

Figure 3-4. Slice Single/Dual Port Write Cycle Timing

#### Notes:

- Rising Edge for latching WREN, WAD and DATAIN.

- WREN must continue past falling edge clock.

- Data output occurs on negative edge.

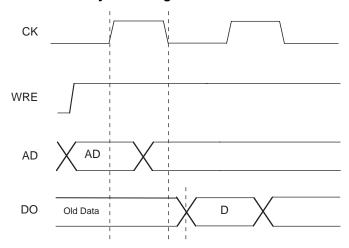

Figure 3-5. Slice Single/Dual Port Read Cycle Timing

# LFSC/M15 Logic Signal Connections: 256 fpBGA<sup>1,2</sup>

|             |               | LFSC/M15   |                             |  |  |  |

|-------------|---------------|------------|-----------------------------|--|--|--|

| Ball Number | Ball Function | VCCIO Bank | Dual Function               |  |  |  |

| E4          | A_VDDAX25_L   | -          |                             |  |  |  |

| B1          | A_REFCLKP_L   | -          |                             |  |  |  |

| C1          | A_REFCLKN_L   | -          |                             |  |  |  |

| D2          | RESP_ULC      | -          |                             |  |  |  |

| F5          | RESETN        | 1          |                             |  |  |  |

| D1          | DONE          | 1          |                             |  |  |  |

| E1          | INITN         | 1          |                             |  |  |  |

| E2          | MO            | 1          |                             |  |  |  |

| E3          | M1            | 1          |                             |  |  |  |

| E5          | M2            | 1          |                             |  |  |  |

| E6          | M3            | 1          |                             |  |  |  |

| F2          | PL15A         | 7          | ULC_PLLT_IN_A/ULC_PLLT_FB_B |  |  |  |

| F1          | PL15B         | 7          | ULC_PLLC_IN_A/ULC_PLLC_FB_B |  |  |  |

| F3          | PL17A         | 7          | ULC_DLLT_IN_C/ULC_DLLT_FB_D |  |  |  |

| G1          | PL17B         | 7          | ULC_DLLC_IN_C/ULC_DLLC_FB_D |  |  |  |

| G4          | PL18D         | 7          | VREF2_7                     |  |  |  |

| H3          | PL22A         | 7          |                             |  |  |  |

| H2          | PL22B         | 7          |                             |  |  |  |

| H5          | PL22C         | 7          | VREF1_7                     |  |  |  |

| G5          | PL22D         | 7          | DIFFR_7                     |  |  |  |

| H1          | PL23A         | 7          | PCLKT7_1                    |  |  |  |

| J1          | PL23B         | 7          | PCLKC7_1                    |  |  |  |

| J2          | PL24A         | 7          | PCLKT7_0                    |  |  |  |

| J3          | PL24B         | 7          | PCLKC7_0                    |  |  |  |

| H4          | PL24C         | 7          | PCLKT7_2                    |  |  |  |

| H6          | PL24D         | 7          | PCLKC7_2                    |  |  |  |

| J4          | PL26A         | 6          | PCLKT6_0                    |  |  |  |

| K5          | PL26B         | 6          | PCLKC6_0                    |  |  |  |

| J5          | PL26C         | 6          | PCLKT6_1                    |  |  |  |

| J6          | PL26D         | 6          | PCLKC6_1                    |  |  |  |

| K1          | PL28A         | 6          |                             |  |  |  |

| L1          | PL28B         | 6          |                             |  |  |  |

| L4          | PL28C         | 6          | PCLKT6_2                    |  |  |  |

| K4          | PL28D         | 6          | PCLKC6_2                    |  |  |  |

| L2          | PL31C         | 6          | VREF1_6                     |  |  |  |

| L3          | PL35A         | 6          |                             |  |  |  |

| M3          | PL35B         | 6          |                             |  |  |  |

| M2          | PL35D         | 6          | DIFFR_6                     |  |  |  |

| M1          | PL37A         | 6          |                             |  |  |  |

| N1          | PL37B         | 6          |                             |  |  |  |

| P2          | PL41D         | 6          | VREF2_6                     |  |  |  |

| M5          | PL43A         | 6          |                             |  |  |  |

# LFSC/M15 Logic Signal Connections: 256 fpBGA<sup>1,2</sup> (Cont.)

| Ball Number | Ball Function | VCCIO Bank | Dual Function               |  |  |

|-------------|---------------|------------|-----------------------------|--|--|

| N12         | PB39C         | 4          |                             |  |  |

| T15         | PB40A         | 4          | PCLKT4_3                    |  |  |

| R16         | PB40B         | 4          | PCLKC4_3                    |  |  |

| L12         | PB43A         | 4          |                             |  |  |

| M12         | PB43B         | 4          |                             |  |  |

| P16         | PB44A         | 4          |                             |  |  |

| N16         | PB44B         | 4          |                             |  |  |

| R14         | PB47C         | 4          | VREF1_4                     |  |  |

| P15         | PB48A         | 4          | LRC_DLLT_IN_C/LRC_DLLT_FB_D |  |  |

| M13         | PB48B         | 4          | LRC_DLLC_IN_C/LRC_DLLC_FB_D |  |  |

| N13         | PB49A         | 4          | LRC_PLLT_IN_A/LRC_PLLT_FB_B |  |  |

| P14         | PB49B         | 4          | LRC_PLLC_IN_A/LRC_PLLC_FB_B |  |  |

| M16         | PR45B         | 3          | LRC_DLLC_IN_F/LRC_DLLC_FB_E |  |  |

| L16         | PR45A         | 3          | LRC_DLLT_IN_F/LRC_DLLT_FB_E |  |  |

| M14         | PR43B         | 3          |                             |  |  |

| M15         | PR43A         | 3          |                             |  |  |

| K16         | PR41D         | 3          | VREF2_3                     |  |  |

| J16         | PR37B         | 3          |                             |  |  |

| H16         | PR37A         | 3          |                             |  |  |

| L13         | PR35D         | 3          | DIFFR_3                     |  |  |

| L14         | PR35B         | 3          |                             |  |  |

| L15         | PR35A         | 3          |                             |  |  |

| K12         | PR31C         | 3          | VREF1_3                     |  |  |

| J13         | PR28D         | 3          | PCLKC3_2                    |  |  |

| K13         | PR28C         | 3          | PCLKT3_2                    |  |  |

| H15         | PR28B         | 3          |                             |  |  |

| F16         | PR28A         | 3          |                             |  |  |

| J11         | PR26D         | 3          | PCLKC3_1                    |  |  |

| J12         | PR26C         | 3          | PCLKT3_1                    |  |  |

| J15         | PR26B         | 3          | PCLKC3_0                    |  |  |

| J14         | PR26A         | 3          | PCLKT3_0                    |  |  |

| E16         | PR24D         | 2          | PCLKC2_2                    |  |  |

| D16         | PR24C         | 2          | PCLKT2_2                    |  |  |

| H11         | PR24B         | 2          | PCLKC2_0                    |  |  |

| H12         | PR24A         | 2          | PCLKT2_0                    |  |  |

| H13         | PR23B         | 2          | PCLKC2_1                    |  |  |

| H14         | PR23A         | 2          | PCLKT2_1                    |  |  |

| G12         | PR22D         | 2          | DIFFR_2                     |  |  |

| G13         | PR22C         | 2          | VREF1_2                     |  |  |

| F8          | PR22B         | 2          |                             |  |  |

| F9          | PR22A         | 2          |                             |  |  |

| G16         | PR18D         | 2          | VREF2_2                     |  |  |

| F15         | PR17B         | 2          | URC_DLLC_IN_C/URC_DLLC_FB_D |  |  |

# LFSC/M15 Logic Signal Connections: 256 fpBGA<sup>1,2</sup> (Cont.)

|             | LFSC/M15      |            |                             |  |  |

|-------------|---------------|------------|-----------------------------|--|--|

| Ball Number | Ball Function | VCCIO Bank | Dual Function               |  |  |

| F14         | PR17A         | 2          | URC_DLLT_IN_C/URC_DLLT_FB_D |  |  |

| E15         | PR15B         | 2          | URC_PLLC_IN_A/URC_PLLC_FB_B |  |  |

| E14         | PR15A         | 2          | URC_PLLT_IN_A/URC_PLLT_FB_B |  |  |

| D9          | VCCJ          | -          |                             |  |  |

| C16         | TDO           | -          | TDO                         |  |  |

| B15         | TMS           | -          |                             |  |  |

| B16         | TCK           | -          |                             |  |  |

| E13         | TDI           | -          |                             |  |  |

| C14         | PROGRAMN      | 1          |                             |  |  |

| C15         | CCLK          | 1          |                             |  |  |

| A15         | PT43D         | 1          | HDC/SI                      |  |  |

| A14         | PT43C         | 1          | LDCN/SCS                    |  |  |

| B14         | PT41A         | 1          | CS1                         |  |  |

| E12         | PT39B         | 1          | CS0N                        |  |  |

| D13         | PT39A         | 1          | RDN                         |  |  |

| D12         | PT37D         | 1          | WRN                         |  |  |

| E10         | PT37C         | 1          | D7                          |  |  |

| C11         | PT37B         | 1          | D6                          |  |  |

| D10         | PT37A         | 1          | D5                          |  |  |

| A13         | PT36D         | 1          | D4                          |  |  |

| B12         | PT36C         | 1          | D3                          |  |  |

| A12         | PT35B         | 1          | D2                          |  |  |

| C12         | PT35A         | 1          | D1                          |  |  |

| A11         | PT33B         | 1          | D0                          |  |  |

| B11         | PT33A         | 1          | QOUT/CEON                   |  |  |

| E9          | PT32D         | 1          | VREF2_1                     |  |  |

| E8          | PT32B         | 1          | DOUT                        |  |  |

| D8          | PT28C         | 1          | BUSYN/RCLK/SCK              |  |  |

| A10         | PT27B         | 1          | PCLKC1_0                    |  |  |

| C10         | PT27A         | 1          | PCLKT1_0                    |  |  |

| E7          | PT21C         | 1          | VREF1_1                     |  |  |

| C9          | A_VDDIB3_L    | -          |                             |  |  |

| A9          | A_HDINP3_L    | -          | PCS 360 CH 3 IN P           |  |  |

| В9          | A_HDINN3_L    | -          | PCS 360 CH 3 IN N           |  |  |

| A8          | A_HDOUTP3_L   | -          | PCS 360 CH 3 OUT P          |  |  |

| B8          | A_HDOUTN3_L   | -          | PCS 360 CH 3 OUT N          |  |  |

| C8          | A_VDDOB3_L    | -          |                             |  |  |

| B7          | A_HDOUTN2_L   | -          | PCS 360 CH 2 OUT N          |  |  |

| C7          | A_VDDOB2_L    | -          |                             |  |  |

| A7          | A_HDOUTP2_L   | -          | PCS 360 CH 2 OUT P          |  |  |

| B6          | A_HDINN2_L    | -          | PCS 360 CH 2 IN N           |  |  |

| A6          | A_HDINP2_L    | -          | PCS 360 CH 2 IN P           |  |  |

| C6          | A_VDDIB2_L    | -          |                             |  |  |

# LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup> (Cont.)

|                | LFSC/M15      |               |                             | LFSC/M25      |               |                             |  |

|----------------|---------------|---------------|-----------------------------|---------------|---------------|-----------------------------|--|

| Ball<br>Number | Ball Function | VCCIO<br>Bank | Dual Function               | Ball Function | VCCIO<br>Bank | Dual Function               |  |

| AF4            | PB3C          | 5             | LLC_DLLT_IN_C/LLC_DLLT_FB_D | PB3C          | 5             | LLC_DLLT_IN_C/LLC_DLLT_FB_D |  |

| AE5            | PB3D          | 5             | LLC_DLLC_IN_C/LLC_DLLC_FB_D | PB3D          | 5             | LLC_DLLC_IN_C/LLC_DLLC_FB_D |  |

| AG3            | PB4A          | 5             | LLC_DLLT_IN_D/LLC_DLLT_FB_C | PB4A          | 5             | LLC_DLLT_IN_D/LLC_DLLT_FB_C |  |

| AH2            | PB4B          | 5             | LLC_DLLC_IN_D/LLC_DLLC_FB_C | PB4B          | 5             | LLC_DLLC_IN_D/LLC_DLLC_FB_C |  |

| AD6            | PB4C          | 5             |                             | PB4C          | 5             |                             |  |

| AJ2            | PB5A          | 5             |                             | PB5A          | 5             |                             |  |

| AK2            | PB5B          | 5             |                             | PB5B          | 5             |                             |  |

| AD7            | PB5C          | 5             |                             | PB5C          | 5             |                             |  |

| AD8            | PB5D          | 5             | VREF1_5                     | PB5D          | 5             | VREF1_5                     |  |

| AH3            | PB7A          | 5             |                             | PB11A         | 5             |                             |  |

| AJ3            | PB7B          | 5             |                             | PB11B         | 5             |                             |  |

| AF9            | PB7C          | 5             |                             | PB11C         | 5             |                             |  |

| AE10           | PB7D          | 5             |                             | PB11D         | 5             |                             |  |

| AK3            | PB8A          | 5             |                             | PB12A         | 5             |                             |  |

| AJ4            | PB8B          | 5             |                             | PB12B         | 5             |                             |  |

| AE11           | PB9A          | 5             |                             | PB13A         | 5             |                             |  |

| AF10           | PB9B          | 5             |                             | PB13B         | 5             |                             |  |

| AK4            | PB11A         | 5             |                             | PB16A         | 5             |                             |  |

| AK5            | PB11B         | 5             |                             | PB16B         | 5             |                             |  |

| AH10           | PB12A         | 5             | PCLKT5_3                    | PB20A         | 5             | PCLKT5_3                    |  |

| AH11           | PB12B         | 5             | PCLKC5_3                    | PB20B         | 5             | PCLKC5_3                    |  |

| AF13           | PB12C         | 5             | PCLKT5_4                    | PB20C         | 5             | PCLKT5_4                    |  |

| AE14           | PB12D         | 5             | PCLKC5_4                    | PB20D         | 5             | PCLKC5_4                    |  |

| AK6            | PB13A         | 5             | PCLKT5_5                    | PB21A         | 5             | PCLKT5_5                    |  |

| AK7            | PB13B         | 5             | PCLKC5_5                    | PB21B         | 5             | PCLKC5_5                    |  |

| AF14           | PB13C         | 5             |                             | PB21C         | 5             |                             |  |

| AJ11           | PB15A         | 5             | PCLKT5_0                    | PB23A         | 5             | PCLKT5_0                    |  |

| AJ12           | PB15B         | 5             | PCLKC5_0                    | PB23B         | 5             | PCLKC5_0                    |  |

| AH13           | PB15D         | 5             | VREF2_5                     | PB23D         | 5             | VREF2_5                     |  |

| AK8            | PB16A         | 5             | PCLKT5_1                    | PB24A         | 5             | PCLKT5_1                    |  |

| AK9            | PB16B         | 5             | PCLKC5_1                    | PB24B         | 5             | PCLKC5_1                    |  |

| AH14           | PB17A         | 5             | PCLKT5_2                    | PB25A         | 5             | PCLKT5_2                    |  |

| AG14           | PB17B         | 5             | PCLKC5_2                    | PB25B         | 5             | PCLKC5_2                    |  |

| AK10           | PB19A         | 5             |                             | PB28A         | 5             |                             |  |

| AK11           | PB19B         | 5             |                             | PB28B         | 5             |                             |  |

| AH15           | PB20A         | 5             |                             | PB29A         | 5             |                             |  |

| AG15           | PB20B         | 5             |                             | PB29B         | 5             |                             |  |

| AH12           | PB21A         | 5             |                             | PB31A         | 5             |                             |  |

| AJ13           | PB21B         | 5             |                             | PB31B         | 5             |                             |  |

| AD15           | PB21C         | 5             |                             | PB31C         | 5             |                             |  |

| AE15           | PB21D         | 5             |                             | PB31D         | 5             |                             |  |

| AK12           | PB23A         | 5             |                             | PB32A         | 5             |                             |  |

| AK13           | PB23B         | 5             |                             | PB32B         | 5             |                             |  |

| AJ14           | PB24A         | 5             |                             | PB33A         | 5             |                             |  |

| AJ15           | PB24B         | 5             |                             | PB33B         | 5             |                             |  |

# LFSC/M15, LFSC/M25 Logic Signal Connections: 900 fpBGA<sup>1, 2</sup> (Cont.)

|                | LFSC/M15    |   |                    | LFSC/M25      |               |                    |  |

|----------------|-------------|---|--------------------|---------------|---------------|--------------------|--|

| Ball<br>Number |             |   | Dual Function      | Ball Function | VCCIO<br>Bank | Dual Function      |  |

| A29            | RESP_URC    | - |                    | RESP_URC      | -             |                    |  |

| D26            | VCC12       | - |                    | VCC12         | -             |                    |  |

| C30            | A_REFCLKN_R | - |                    | A_REFCLKN_R   | -             |                    |  |

| B30            | A_REFCLKP_R | - |                    | A_REFCLKP_R   | -             |                    |  |

| F24            | A_VDDAX25_R | - |                    | A_VDDAX25_R   | -             |                    |  |

| D25            | VCC12       | - |                    | VCC12         | -             |                    |  |

| C28            | A_VDDIB0_R  | - |                    | A_VDDIB0_R    | -             |                    |  |

| B28            | A_HDINP0_R  | - | PCS 3E0 CH 0 IN P  | A_HDINP0_R    | -             | PCS 3E0 CH 0 IN P  |  |

| B27            | A_HDINN0_R  | - | PCS 3E0 CH 0 IN N  | A_HDINN0_R    | -             | PCS 3E0 CH 0 IN N  |  |

| E25            | VCC12       | - |                    | VCC12         | -             |                    |  |

| A28            | A_HDOUTP0_R | - | PCS 3E0 CH 0 OUT P | A_HDOUTP0_R   | -             | PCS 3E0 CH 0 OUT P |  |

| C27            | A_VDDOB0_R  | - |                    | A_VDDOB0_R    | -             |                    |  |

| A27            | A_HDOUTN0_R | - | PCS 3E0 CH 0 OUT N | A_HDOUTN0_R   | -             | PCS 3E0 CH 0 OUT N |  |

| C26            | A_VDDOB1_R  | - |                    | A_VDDOB1_R    | -             |                    |  |

| A26            | A_HDOUTN1_R | - | PCS 3E0 CH 1 OUT N | A_HDOUTN1_R   | -             | PCS 3E0 CH 1 OUT N |  |

| D24            | VCC12       | - |                    | VCC12         | -             |                    |  |

| A25            | A_HDOUTP1_R | - | PCS 3E0 CH 1 OUT P | A_HDOUTP1_R   | -             | PCS 3E0 CH 1 OUT P |  |

| B26            | A_HDINN1_R  | - | PCS 3E0 CH 1 IN N  | A_HDINN1_R    | -             | PCS 3E0 CH 1 IN N  |  |

| B25            | A_HDINP1_R  | - | PCS 3E0 CH 1 IN P  | A_HDINP1_R    | -             | PCS 3E0 CH 1 IN P  |  |

| E24            | VCC12       | - |                    | VCC12         | -             |                    |  |

| C25            | A_VDDIB1_R  | - |                    | A_VDDIB1_R    | -             |                    |  |

| D23            | VCC12       | - |                    | VCC12         | -             |                    |  |

| C24            | A_VDDIB2_R  | - |                    | A_VDDIB2_R    | -             |                    |  |

| B24            | A_HDINP2_R  | - | PCS 3E0 CH 2 IN P  | A_HDINP2_R    | -             | PCS 3E0 CH 2 IN P  |  |

| B23            | A_HDINN2_R  | - | PCS 3E0 CH 2 IN N  | A_HDINN2_R    | -             | PCS 3E0 CH 2 IN N  |  |

| E23            | VCC12       | - |                    | VCC12         | -             |                    |  |

| A24            | A_HDOUTP2_R | - | PCS 3E0 CH 2 OUT P | A_HDOUTP2_R   | -             | PCS 3E0 CH 2 OUT P |  |

| C23            | A_VDDOB2_R  | - |                    | A_VDDOB2_R    | -             |                    |  |

| A23            | A_HDOUTN2_R | = | PCS 3E0 CH 2 OUT N | A_HDOUTN2_R   | -             | PCS 3E0 CH 2 OUT N |  |

| C22            | A_VDDOB3_R  | - |                    | A_VDDOB3_R    | -             |                    |  |

| A22            | A_HDOUTN3_R | = | PCS 3E0 CH 3 OUT N | A_HDOUTN3_R   | -             | PCS 3E0 CH 3 OUT N |  |

| D22            | VCC12       | - |                    | VCC12         | -             |                    |  |

| A21            | A_HDOUTP3_R | - | PCS 3E0 CH 3 OUT P | A_HDOUTP3_R   | -             | PCS 3E0 CH 3 OUT P |  |

| B22            | A_HDINN3_R  | - | PCS 3E0 CH 3 IN N  | A_HDINN3_R    | -             | PCS 3E0 CH 3 IN N  |  |

| B21            | A_HDINP3_R  | - | PCS 3E0 CH 3 IN P  | A_HDINP3_R    | -             | PCS 3E0 CH 3 IN P  |  |

| E22            | VCC12       | - |                    | VCC12         | -             |                    |  |

| C21            | A_VDDIB3_R  | - |                    | A_VDDIB3_R    | -             |                    |  |

| G22            | PT43D       | 1 | HDC/SI             | PT49D         | 1             | HDC/SI             |  |

| F22            | PT43C       | 1 | LDCN/SCS           | PT49C         | 1             | LDCN/SCS           |  |

| B20            | PT41B       | 1 | D8/MPI_DATA8       | PT49B         | 1             | D8/MPI_DATA8       |  |

| B19            | PT41A       | 1 | CS1/MPI_CS1        | PT49A         | 1             | CS1/MPI_CS1        |  |

| A20            | PT40D       | 1 | D9/MPI_DATA9       | PT47D         | 1             | D9/MPI_DATA9       |  |

| A19            | PT40C       | 1 | D10/MPI_DATA10     | PT47C         | 1             | D10/MPI_DATA10     |  |

| D19            | PT39B       | 1 | CS0N/MPI_CS0N      | PT47B         | 1             | CS0N/MPI_CS0N      |  |

| D18            | PT39A       | 1 | RDN/MPI_STRB_N     | PT47A         | 1             | RDN/MPI_STRB_N     |  |

# LFSC/M40, LFSC/M80 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup> (Cont.)

|                | LFSC/M40         |               |               |                  | LFSC/M80      |               |  |  |

|----------------|------------------|---------------|---------------|------------------|---------------|---------------|--|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual Function | Ball<br>Function | VCCIO<br>Bank | Dual Function |  |  |

| AH27           | PB5C             | 5             |               | PB5C             | 5             |               |  |  |

| AH26           | PB5D             | 5             | VREF1_5       | PB5D             | 5             | VREF1_5       |  |  |

| AN32           | PB7A             | 5             |               | PB7A             | 5             |               |  |  |

| AP32           | PB7B             | 5             |               | PB7B             | 5             |               |  |  |

| AF25           | PB7C             | 5             |               | PB7C             | 5             |               |  |  |

| AE25           | PB7D             | 5             |               | PB7D             | 5             |               |  |  |

| AN31           | PB8A             | 5             |               | PB9A             | 5             |               |  |  |

| AN30           | PB8B             | 5             |               | PB9B             | 5             |               |  |  |

| AK29           | PB8C             | 5             |               | PB9C             | 5             |               |  |  |

| AK28           | PB8D             | 5             |               | PB9D             | 5             |               |  |  |

| AP31           | PB9A             | 5             |               | PB11A            | 5             |               |  |  |

| AP30           | PB9B             | 5             |               | PB11B            | 5             |               |  |  |

| AD24           | PB9C             | 5             |               | PB11C            | 5             |               |  |  |

| AE24           | PB9D             | 5             |               | PB11D            | 5             |               |  |  |

| AM29           | PB11A            | 5             |               | PB13A            | 5             |               |  |  |

| AM28           | PB11B            | 5             |               | PB13B            | 5             |               |  |  |

| AJ27           | PB11C            | 5             |               | PB13C            | 5             |               |  |  |

| AJ26           | PB11D            | 5             |               | PB13D            | 5             |               |  |  |

| AP29           | PB13A            | 5             |               | PB15A            | 5             |               |  |  |

| AP28           | PB13B            | 5             |               | PB15B            | 5             |               |  |  |

| AK27           | PB13C            | 5             |               | PB15C            | 5             |               |  |  |

| AK26           | PB13D            | 5             |               | PB15D            | 5             |               |  |  |

| AN29           | PB15A            | 5             |               | PB17A            | 5             |               |  |  |

| AN28           | PB15B            | 5             |               | PB17B            | 5             |               |  |  |

| AG25           | PB15C            | 5             |               | PB17C            | 5             |               |  |  |

| AG24           | PB15D            | 5             |               | PB17D            | 5             |               |  |  |

| AL26           | PB17A            | 5             |               | PB19A            | 5             |               |  |  |

| AL25           | PB17B            | 5             |               | PB19B            | 5             |               |  |  |

| AG23           | PB17C            | 5             |               | PB19C            | 5             |               |  |  |

| AG22           | PB17D            | 5             |               | PB19D            | 5             |               |  |  |

| AN27           | PB19A            | 5             |               | PB21A            | 5             |               |  |  |

| AN26           | PB19B            | 5             |               | PB21B            | 5             |               |  |  |

| AF24           | PB19C            | 5             |               | PB21C            | 5             |               |  |  |

| AF23           | PB19D            | 5             |               | PB21D            | 5             |               |  |  |

| AP27           | PB22A            | 5             |               | PB24A            | 5             |               |  |  |

| AP26           | PB22B            | 5             |               | PB24B            | 5             |               |  |  |

| AK25           | PB22C            | 5             |               | PB24C            | 5             |               |  |  |

| AK24           | PB22D            | 5             |               | PB24D            | 5             |               |  |  |

| AN25           | PB25A            | 5             |               | PB27A            | 5             |               |  |  |

| AN24           | PB25B            | 5             |               | PB27B            | 5             |               |  |  |

| AE22           | PB25C            | 5             |               | PB27C            | 5             |               |  |  |

| AE21           | PB25D            | 5             |               | PB27D            | 5             |               |  |  |

| AM26           | PB26A            | 5             |               | PB29A            | 5             |               |  |  |

| AM25           | PB26B            | 5             |               | PB29B            | 5             |               |  |  |

| AF22           | PB26C            | 5             |               | PB29C            | 5             |               |  |  |

# LFSC/M40, LFSC/M80 Logic Signal Connections: 1152 fcBGA<sup>1, 2</sup> (Cont.)

|                | LFSC/M40         |               |                         | LFSC/M80         |               |                         |  |

|----------------|------------------|---------------|-------------------------|------------------|---------------|-------------------------|--|

| Ball<br>Number | Ball<br>Function | VCCIO<br>Bank | Dual Function           | Ball<br>Function | VCCIO<br>Bank | Dual Function           |  |

| H21            | PT38D            | 1             | D28/PCLKC1_6/MPI_DATA28 | PT57D            | 1             | D28/PCLKC1_6/MPI_DATA28 |  |

| J21            | PT38C            | 1             | D29/PCLKT1_6/MPI_DATA29 | PT57C            | 1             | D29/PCLKT1_6/MPI_DATA29 |  |

| A19            | PT38B            | 1             | A9/MPI_ADDR23           | PT57B            | 1             | A9/MPI_ADDR23           |  |

| B19            | PT38A            | 1             | A10/MPI_ADDR24          | PT57A            | 1             | A10/MPI_ADDR24          |  |

| H22            | PT37D            | 1             | D30/PCLKC1_7/MPI_DATA30 | PT56D            | 1             | D30/PCLKC1_7/MPI_DATA30 |  |

| J22            | PT37C            | 1             | D31/PCLKT1_7/MPI_DATA31 | PT56C            | 1             | D31/PCLKT1_7/MPI_DATA31 |  |

| F20            | PT37B            | 1             | A11/MPI_ADDR25          | PT56B            | 1             | A11/MPI_ADDR25          |  |

| G20            | PT37A            | 1             | A12/MPI_ADDR26          | PT56A            | 1             | A12/MPI_ADDR26          |  |

| K21            | PT35D            | 1             | D11/MPI_DATA11          | PT55D            | 1             | D11/MPI_DATA11          |  |

| K22            | PT35C            | 1             | D12/MPI_DATA12          | PT55C            | 1             | D12/MPI_DATA12          |  |

| A20            | PT35B            | 1             | A13/MPI_ADDR27          | PT55B            | 1             | A13/MPI_ADDR27          |  |

| B20            | PT35A            | 1             | A14/MPI_ADDR28          | PT55A            | 1             | A14/MPI_ADDR28          |  |

| L21            | PT33D            | 1             | A16/MPI_ADDR30          | PT53D            | 1             | A16/MPI_ADDR30          |  |

| L20            | PT33C            | 1             | D13/MPI_DATA13          | PT53C            | 1             | D13/MPI_DATA13          |  |

| D20            | PT33B            | 1             | A15/MPI_ADDR29          | PT53B            | 1             | A15/MPI_ADDR29          |  |

| E20            | PT33A            | 1             | A17/MPI_ADDR31          | PT53A            | 1             | A17/MPI_ADDR31          |  |

| L19            | PT30D            | 1             | A19/MPI_TSIZ1           | PT52D            | 1             | A19/MPI_TSIZ1           |  |

| K19            | PT30C            | 1             | A20/MPI_BDIP            | PT52C            | 1             | A20/MPI_BDIP            |  |

| D21            | PT30B            | 1             | A18/MPI_TSIZ0           | PT52B            | 1             | A18/MPI_TSIZ0           |  |

| E21            | PT30A            | 1             | MPI_TEA                 | PT52A            | 1             | MPI_TEA                 |  |

| M20            | PT28D            | 1             | D14/MPI_DATA14          | PT51D            | 1             | D14/MPI_DATA14          |  |

| M19            | PT28C            | 1             | DP1/MPI_PAR1            | PT51C            | 1             | DP1/MPI_PAR1            |  |

| F21            | PT27B            | 1             | A21/MPI_BURST           | PT51B            | 1             | A21/MPI_BURST           |  |

| G21            | PT27A            | 1             | D15/MPI_DATA15          | PT51A            | 1             | D15/MPI_DATA15          |  |

| H24            | B_REFCLKP_L      | -             |                         | B_REFCLKP_L      | -             |                         |  |

| J24            | B_REFCLKN_L      | -             |                         | B_REFCLKN_L      | -             |                         |  |

| L22            | VCC12            | -             |                         | VCC12            | -             |                         |  |

| E26            | B_VDDIB3_L       | -             |                         | B_VDDIB3_L       | -             |                         |  |

| G22            | VCC12            | -             |                         | VCC12            | -             |                         |  |

| E22            | B_HDINP3_L       | -             | PCS 361 CH 3 IN P       | B_HDINP3_L       | -             | PCS 361 CH 3 IN P       |  |

| F22            | B_HDINN3_L       | -             | PCS 361 CH 3 IN N       | B_HDINN3_L       | -             | PCS 361 CH 3 IN N       |  |

| A21            | B_HDOUTP3_L      | -             | PCS 361 CH 3 OUT P      | B_HDOUTP3_L      | -             | PCS 361 CH 3 OUT P      |  |

| L24            | VCC12            | -             |                         | VCC12            | -             |                         |  |

| B21            | B_HDOUTN3_L      | -             | PCS 361 CH 3 OUT N      | B_HDOUTN3_L      | -             | PCS 361 CH 3 OUT N      |  |

| D22            | B_VDDOB3_L       | -             |                         | B_VDDOB3_L       | -             |                         |  |

| B22            | B_HDOUTN2_L      | -             | PCS 361 CH 2 OUT N      | B_HDOUTN2_L      | -             | PCS 361 CH 2 OUT N      |  |

| D23            | B_VDDOB2_L       | -             |                         | B_VDDOB2_L       | -             |                         |  |

| A22            | B_HDOUTP2_L      | -             | PCS 361 CH 2 OUT P      | B_HDOUTP2_L      | -             | PCS 361 CH 2 OUT P      |  |

| K24            | VCC12            | -             |                         | VCC12            | 2 -           |                         |  |