# E·XFL

#### NXP USA Inc. - PK20N512VLL100 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Detailo                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                   |

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 100MHz                                                                     |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 66                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                               |

| Data Converters            | A/D 25x16b; D/A 1x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-LQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/pk20n512vll100     |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol               | Description                                             | Min. | Тур. | Max. | Unit | Notes |

|----------------------|---------------------------------------------------------|------|------|------|------|-------|

| I <sub>DD_VBAT</sub> | Average current when CPU is not accessing RTC registers |      |      |      |      | 10    |

|                      | • @ 1.8V                                                |      |      |      |      |       |

|                      | • @ -40 to 25°C                                         | _    | 0.71 | 0.81 | μA   |       |

|                      | • @ 70°C                                                | _    | 1.01 | 1.3  | μA   |       |

|                      | • @ 105°C                                               |      | 2.82 | 4.3  | μA   |       |

|                      | • @ 3.0V                                                |      |      |      |      |       |

|                      | • @ -40 to 25°C                                         | _    | 0.84 | 0.94 | μA   |       |

|                      | • @ 70°C                                                |      | 1.17 | 1.5  | μΑ   |       |

|                      | • @ 105°C                                               | _    | 3.16 | 4.6  | μA   |       |

#### Table 6. Power consumption operating behaviors (continued)

- 1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 2. 100MHz core and system clock, 50MHz bus and FlexBus clock, and 25MHz flash clock . MCG configured for FEI mode. All peripheral clocks disabled.

- 3. 100MHz core and system clock, 50MHz bus and FlexBus clock, and 25MHz flash clock. MCG configured for FEI mode. All peripheral clocks enabled.

- 4. Max values are measured with CPU executing DSP instructions.

- 5. 25MHz core and system clock, 25MHz bus clock, and 12.5MHz FlexBus and flash clock. MCG configured for FEI mode.

- 6. 2 MHz core, system, FlexBus, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. Code executing from flash.

- 7. 2 MHz core, system, FlexBus, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks enabled but peripherals are not in active operation. Code executing from flash.

- 8. 2 MHz core, system, FlexBus, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

- 9. Data reflects devices with 128 KB of RAM. For devices with 64 KB of RAM, power consumption is reduced by 2 µA.

- 10. Includes 32kHz oscillator current and RTC operation.

## 5.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE mode for 50 MHz and lower frequencies. MCG in FEE mode at greater than 50 MHz frequencies.

- USB regulator disabled

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFL

- 2.  $V_{DD} = 3.3 \text{ V}, T_A = 25 \text{ °C}, f_{OSC} = 12 \text{ MHz} \text{ (crystal)}, f_{SYS} = 96 \text{ MHz}, f_{BUS} = 48 \text{ MHz}$

- 3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions TEM Cell and Wideband TEM Cell Method

## 5.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

## 5.2.8 Capacitance attributes

#### Table 8. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | —    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | —    | 7    | pF   |

## 5.3 Switching specifications

## 5.3.1 Device clock specifications

### Table 9. Device clock specifications

| Symbol               | Description                                            | Min. | Max. | Unit | Notes |

|----------------------|--------------------------------------------------------|------|------|------|-------|

|                      | Normal run mod                                         | e    |      |      |       |

| f <sub>SYS</sub>     | System and core clock                                  | _    | 100  | MHz  |       |

| f <sub>SYS_USB</sub> | System and core clock when Full Speed USB in operation | 20   | _    | MHz  |       |

| f <sub>BUS</sub>     | Bus clock                                              | _    | 50   | MHz  |       |

| FB_CLK               | FlexBus clock                                          | _    | 50   | MHz  |       |

| f <sub>FLASH</sub>   | Flash clock                                            | _    | 25   | MHz  |       |

| f <sub>LPTMR</sub>   | LPTMR clock                                            | _    | 25   | MHz  |       |

## 6.1 Core modules

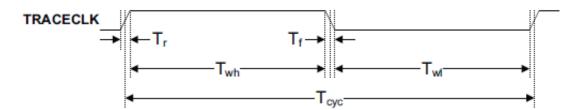

## 6.1.1 Debug trace timing specifications

Table 12.

Debug trace operating behaviors

| Symbol           | Description              | Min.      | Max. | Unit |

|------------------|--------------------------|-----------|------|------|

| T <sub>cyc</sub> | Clock period             | Frequency | MHz  |      |

| T <sub>wl</sub>  | Low pulse width          | 2         |      | ns   |

| T <sub>wh</sub>  | High pulse width         | 2         |      | ns   |

| Tr               | Clock and data rise time |           | 3    | ns   |

| T <sub>f</sub>   | Clock and data fall time |           | 3    | ns   |

| Ts               | Data setup               | 3         | _    | ns   |

| T <sub>h</sub>   | Data hold                | 2         | _    | ns   |

Figure 3. TRACE\_CLKOUT specifications

Figure 4. Trace data specifications

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | —    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | —    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) |      | V <sub>DD</sub> | _    | V    |       |

Table 16. Oscillator DC electrical specifications (continued)

- 1.  $V_{DD}$ =3.3 V, Temperature =25 °C

- 2. See crystal or resonator manufacturer's recommendation

- 3. C<sub>x</sub>,C<sub>y</sub> can be provided by using either the integrated capacitors or by using external components.

- 4. When low power mode is selected, R<sub>F</sub> is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

#### 6.3.2.2 Oscillator frequency specifications Table 17. Oscillator frequency spe

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low frequency mode (MCG_C2[RANGE]=00)                     | 32   |      | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (low range)<br>(MCG_C2[RANGE]=01)  | 3    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (high range)<br>(MCG_C2[RANGE]=1x) |      | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           | —    | —    | 50   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency,<br>low-power mode (HGO=0)                                | _    | 750  | -    | ms   | 3, 4  |

|                       | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                                | _    | 250  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0)          | _    | 0.6  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1)          | _    | 1    | _    | ms   |       |

- 1. Other frequency limits may apply when external clock is being used as a reference for the FLL or PLL.

- 2. When transitioning from FBE to FEI mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

- 3. Proper PC board layout procedures must be followed to achieve specifications.

#### Symbol Description Min. Unit Notes Typ. Max. Swap Control execution time control code 0x01 200 μs t<sub>swapx01</sub> control code 0x02 70 150 μs t<sub>swapx02</sub> control code 0x04 70 150 t<sub>swapx04</sub> μs control code 0x08 30 μs t<sub>swapx08</sub> Program Partition for EEPROM execution time 256 KB FlexNVM ms t<sub>pgmpart64k</sub> 450 tpgmpart256k Set FlexRAM Function execution time: Control Code 0xFF 70 μs tsetramff 32 KB EEPROM backup 0.8 1.2 t<sub>setram32k</sub> ms • 64 KB EEPROM backup 1.3 1.9 ms t<sub>setram64k</sub> 256 KB EEPROM backup 4.5 5.5 ms t<sub>setram256k</sub> Byte-write to FlexRAM for EEPROM operation Byte-write to erased FlexRAM location execution 175 3 260 μs t<sub>eewr8bers</sub> time Byte-write to FlexRAM execution time: 32 KB EEPROM backup 385 1800 μs teewr8b32k 64 KB EEPROM backup 475 2000 teewr8b64k μs 128 KB EEPROM backup 650 2400 μs teewr8b128k 256 KB EEPROM backup 1000 3200 μs teewr8b256k Word-write to FlexRAM for EEPROM operation Word-write to erased FlexRAM location 175 260 μs teewr16bers execution time Word-write to FlexRAM execution time: 32 KB EEPROM backup 385 1800 μs t<sub>eewr16b32k</sub> 2000 64 KB EEPROM backup 475 teewr16b64k μs 128 KB EEPROM backup 650 2400 teewr16b128k μs 256 KB EEPROM backup 1000 3200 μs teewr16b256k Longword-write to FlexRAM for EEPROM operation Longword-write to erased FlexRAM location 360 540 t<sub>eewr32bers</sub> μs execution time Longword-write to FlexRAM execution time: 32 KB EEPROM backup 630 2050 teewr32b32k μs 2250 64 KB EEPROM backup 810 teewr32b64k μs teewr32b128k 128 KB EEPROM backup 1200 2675 μs 256 KB EEPROM backup 1900 3500 μs t<sub>eewr32b256k</sub>

#### Table 21. Flash command timing specifications (continued)

## 6.4.1.5 Write endurance to FlexRAM for EEPROM

When the FlexNVM partition code is not set to full data flash, the EEPROM data set size can be set to any of several non-zero values.

The bytes not assigned to data flash via the FlexNVM partition code are used by the flash memory module to obtain an effective endurance increase for the EEPROM data. The built-in EEPROM record management system raises the number of program/erase cycles that can be attained prior to device wear-out by cycling the EEPROM data through a larger EEPROM NVM storage space.

While different partitions of the FlexNVM are available, the intention is that a single choice for the FlexNVM partition code and EEPROM data set size is used throughout the entire lifetime of a given application. The EEPROM endurance equation and graph shown below assume that only one configuration is ever used.

$Writes\_subsystem = \frac{EEPROM - 2 \times EEESPLIT \times EEESIZE}{EEESPLIT \times EEESIZE} \times Write\_efficiency \times n_{nvmcycd}$

where

- Writes\_subsystem minimum number of writes to each FlexRAM location for subsystem (each subsystem can have different endurance)

- EEPROM allocated FlexNVM for each EEPROM subsystem based on DEPART; entered with the Program Partition command

- EEESPLIT FlexRAM split factor for subsystem; entered with the Program Partition command

- EEESIZE allocated FlexRAM based on DEPART; entered with the Program Partition command

- Write\_efficiency

- 0.25 for 8-bit writes to FlexRAM

- 0.50 for 16-bit or 32-bit writes to FlexRAM

- n<sub>nvmcycd</sub> data flash cycling endurance (the following graph assumes 10,000 cycles)

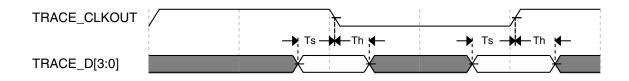

Figure 10. EzPort Timing Diagram

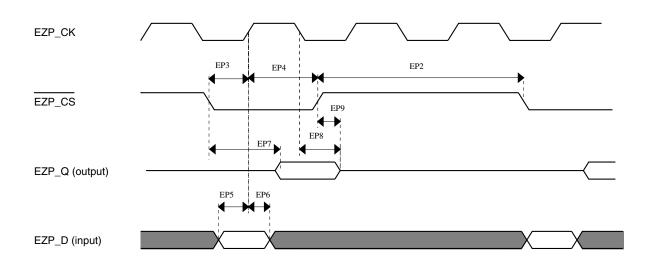

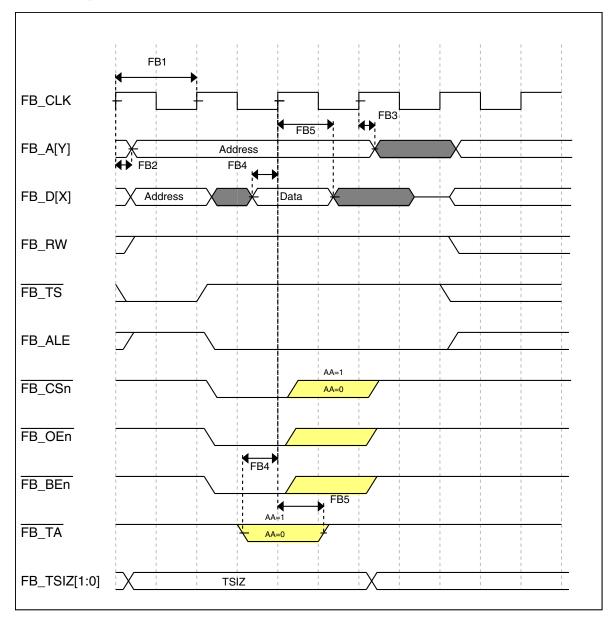

## 6.4.3 Flexbus Switching Specifications

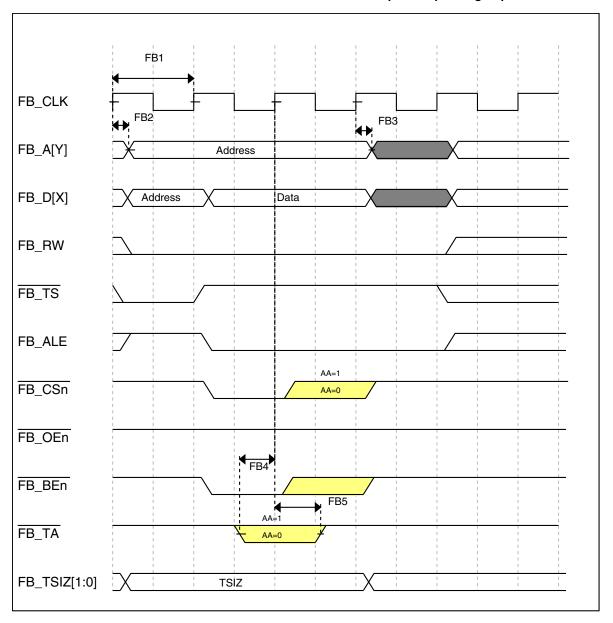

All processor bus timings are synchronous; input setup/hold and output delay are given in respect to the rising edge of a reference clock, FB\_CLK. The FB\_CLK frequency may be the same as the internal system bus frequency or an integer divider of that frequency.

The following timing numbers indicate when data is latched or driven onto the external bus, relative to the Flexbus output clock (FB\_CLK). All other timing relationships can be derived from these values.

| Num | Description                             | Min. | Max.   | Unit | Notes |

|-----|-----------------------------------------|------|--------|------|-------|

|     | Operating voltage                       | 2.7  | 3.6    | V    |       |

|     | Frequency of operation                  | _    | FB_CLK | MHz  |       |

| FB1 | Clock period                            | 20   | —      | ns   |       |

| FB2 | Address, data, and control output valid | —    | 11.5   | ns   | 1     |

| FB3 | Address, data, and control output hold  | 0.5  | _      | ns   | 1     |

| FB4 | Data and FB_TA input setup              | 8.5  | _      | ns   | 2     |

| FB5 | Data and FB_TA input hold               | 0.5  | _      | ns   | 2     |

Table 25. Flexbus limited voltage range switching specifications

1. Specification is valid for all FB\_AD[31:0], FB\_BE/BWEn, FB\_CSn, FB\_OE, FB\_R/W, FB\_TBST, FB\_TSIZ[1:0], FB\_ALE, and FB\_TS.

Figure 11. FlexBus read timing diagram

Peripheral operating requirements and behaviors

Figure 12. FlexBus write timing diagram

## 6.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

## 6.6 Analog

| Symbol              | Description            | Conditions <sup>1</sup>                         | Min. | Typ. <sup>2</sup>      | Max. | Unit  | Notes                                                                     |

|---------------------|------------------------|-------------------------------------------------|------|------------------------|------|-------|---------------------------------------------------------------------------|

| EIL                 | Input leakage<br>error |                                                 |      | $I_{In} \times R_{AS}$ |      | mV    | I <sub>In</sub> =<br>leakage<br>current                                   |

|                     |                        |                                                 |      |                        |      |       | (refer to<br>the MCU's<br>voltage<br>and current<br>operating<br>ratings) |

|                     | Temp sensor<br>slope   | Across the full temperature range of the device | 1.55 | 1.62                   | 1.69 | mV/°C |                                                                           |

| V <sub>TEMP25</sub> | Temp sensor<br>voltage | 25 °C                                           | 706  | 716                    | 726  | mV    |                                                                           |

1. All accuracy numbers assume the ADC is calibrated with  $V_{REFH} = V_{DDA}$

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and the ADLPC bit (low power). For lowest power operation the ADLPC bit must be set, the HSC bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

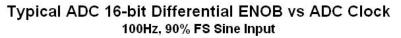

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

Peripheral operating requirements and behaviors

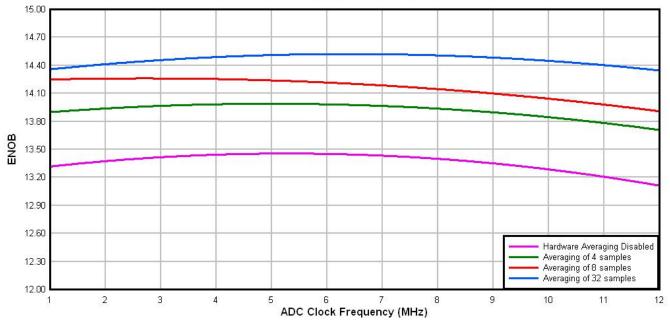

Figure 17. Typical hysteresis vs. Vin level (VDD=3.3V, PMODE=1)

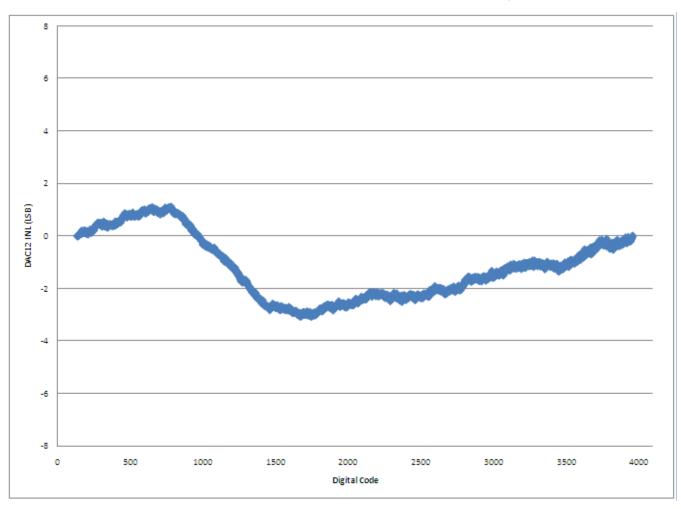

## 6.6.3 12-bit DAC electrical characteristics

## 6.6.3.1 12-bit DAC operating requirements Table 32. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min.                                         | Max. | Unit | Notes |

|-------------------|-------------------------|----------------------------------------------|------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          | 1.71                                         | 3.6  | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13                                         | 3.6  | V    | 1     |

| T <sub>A</sub>    | Temperature             | Operating temperature<br>range of the device |      | °C   |       |

| CL                | Output load capacitance | _                                            | 100  | pF   | 2     |

| ١L                | Output load current     | —                                            | 1    | mA   |       |

1. The DAC reference can be selected to be V<sub>DDA</sub> or the voltage output of the VREF module (VREF\_OUT)

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC

Peripheral operating requirements and behaviors

Figure 18. Typical INL error vs. digital code

| Symbol              | Description                                                                         | Min.   | Тур.  | Max.   | Unit | Notes |

|---------------------|-------------------------------------------------------------------------------------|--------|-------|--------|------|-------|

| V <sub>out</sub>    | Voltage reference output with factory trim at nominal $V_{DDA}$ and temperature=25C | 1.1915 | 1.195 | 1.1977 | V    |       |

| V <sub>out</sub>    | Voltage reference output — factory trim                                             | 1.1584 | —     | 1.2376 | V    |       |

| V <sub>step</sub>   | Voltage reference trim step                                                         | _      | 0.5   | —      | mV   |       |

| V <sub>tdrift</sub> | Temperature drift (Vmax -Vmin across the full temperature range)                    | _      | _     | 80     | mV   |       |

| I <sub>bg</sub>     | Bandgap only current                                                                | —      | —     | 80     | μA   | 1     |

| I <sub>lp</sub>     | Low-power buffer current                                                            | _      | —     | 360    | uA   | 1     |

| I <sub>hp</sub>     | High-power buffer current                                                           | _      | —     | 1      | mA   | 1     |

| $\Delta V_{LOAD}$   | Load regulation                                                                     |        |       |        | mV   | 1, 2  |

|                     | • current = + 1.0 mA                                                                | _      | 2     | _      |      |       |

|                     | • current = - 1.0 mA                                                                | _      | 5     | _      |      |       |

| T <sub>stup</sub>   | Buffer startup time                                                                 |        |       | 100    | μs   |       |

| V <sub>vdrift</sub> | Voltage drift (Vmax -Vmin across the full voltage range)                            | —      | 2     | —      | mV   | 1     |

Table 35. VREF full-range operating behaviors

1. See the chip's Reference Manual for the appropriate settings of the VREF Status and Control register.

2. Load regulation voltage is the difference between the VREF\_OUT voltage with no load vs. voltage with defined load

### Table 36. VREF limited-range operating requirements

| Symbol         | Description | Min. | Max. | Unit | Notes |

|----------------|-------------|------|------|------|-------|

| T <sub>A</sub> | Temperature | 0    | 50   | °C   |       |

### Table 37. VREF limited-range operating behaviors

| Symbol           | Description                                | Min.  | Max.  | Unit | Notes |

|------------------|--------------------------------------------|-------|-------|------|-------|

| V <sub>out</sub> | Voltage reference output with factory trim | 1.173 | 1.225 | V    |       |

## 6.7 Timers

See General switching specifications.

## 6.8 Communication interfaces

## 6.8.1 USB electrical specifications

The USB electricals for the USB On-the-Go module conform to the standards documented by the Universal Serial Bus Implementers Forum. For the most up-to-date standards, visit **usb.org**.

## 6.8.2 USB DCD electrical specifications

| Symbol               | Description                                        | Min.  | Тур. | Max. | Unit |

|----------------------|----------------------------------------------------|-------|------|------|------|

| V <sub>DP_SRC</sub>  | USB_DP source voltage (up to 250 µA)               | 0.5   | —    | 0.7  | V    |

| V <sub>LGC</sub>     | Threshold voltage for logic high                   | 0.8   | —    | 2.0  | V    |

| I <sub>DP_SRC</sub>  | USB_DP source current                              | 7     | 10   | 13   | μA   |

| I <sub>DM_SINK</sub> | USB_DM sink current                                | 50    | 100  | 150  | μA   |

| R <sub>DM_DWN</sub>  | D- pulldown resistance for data pin contact detect | 14.25 | —    | 24.8 | kΩ   |

| V <sub>DAT_REF</sub> | Data detect voltage                                | 0.25  | 0.33 | 0.4  | V    |

## 6.8.3 USB VREG electrical specifications

Table 39. USB VREG electrical specifications

| Symbol                | Description                                                                                                                                           | Min. | Typ. <sup>1</sup> | Max. | Unit     | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|------|----------|-------|

| VREGIN                | Input supply voltage                                                                                                                                  | 2.7  | _                 | 5.5  | V        |       |

| I <sub>DDon</sub>     | Quiescent current — Run mode, load current<br>equal zero, input supply (VREGIN) > 3.6 V                                                               | —    | 120               | 186  | μA       |       |

| I <sub>DDstby</sub>   | Quiescent current — Standby mode, load current equal zero                                                                                             | —    | 1.27              | 30   | μA       |       |

| I <sub>DDoff</sub>    | <ul> <li>Quiescent current — Shutdown mode</li> <li>VREGIN = 5.0 V and temperature=25 °C</li> <li>Across operating voltage and temperature</li> </ul> | _    | 650<br>—          | 4    | nA<br>μA |       |

| I <sub>LOADrun</sub>  | Maximum load current — Run mode                                                                                                                       |      | —                 | 120  | mA       |       |

| I <sub>LOADstby</sub> | Maximum load current — Standby mode                                                                                                                   |      | _                 | 1    | mA       |       |

| V <sub>Reg33out</sub> | Regulator output voltage — Input supply<br>(VREGIN) > 3.6 V                                                                                           |      |                   |      |          |       |

|                       | Run mode                                                                                                                                              | 3    | 3.3               | 3.6  | v        |       |

|                       | Standby mode                                                                                                                                          | 2.1  | 2.8               | 3.6  | V        |       |

| V <sub>Reg33out</sub> | Regulator output voltage — Input supply<br>(VREGIN) < 3.6 V, pass-through mode                                                                        | 2.1  |                   | 3.6  | V        | 2     |

| C <sub>OUT</sub>      | External output capacitor                                                                                                                             | 1.76 | 2.2               | 8.16 | μF       |       |

| ESR                   | External output capacitor equivalent series resistance                                                                                                | 1    | —                 | 100  | mΩ       |       |

Table continues on the next page...

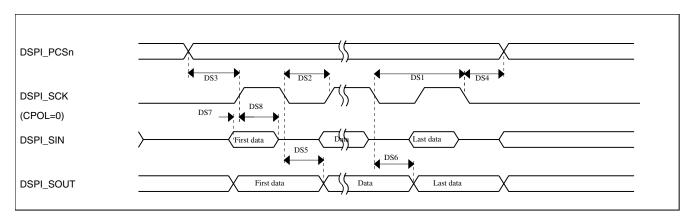

## 6.8.6 DSPI switching specifications (full voltage range)

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provides DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                     | Unit | Notes |

|-----|-------------------------------------|-------------------------------|--------------------------|------|-------|

|     | Operating voltage                   | 1.71                          | 3.6                      | V    | 1     |

|     | Frequency of operation              | _                             | 12.5                     | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 4 x t <sub>BUS</sub>          | _                        | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) - 4     | (t <sub>SCK/2)</sub> + 4 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>4 | _                        | ns   | 2     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>4 | _                        | ns   | 3     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | _                             | 10                       | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -4.5                          | —                        | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 20.5                          | —                        | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             | —                        | ns   |       |

### Table 42. Master mode DSPI timing (full voltage range)

1. The DSPI module can operate across the entire operating voltage for the processor, but to run across the full voltage range the maximum frequency of operation is reduced.

2. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

3. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

### Figure 22. DSPI classic SPI timing — master mode

Table 43. Slave mode DSPI timing (full voltage range)

| Num | Description            | Min. | Max. | Unit |

|-----|------------------------|------|------|------|

|     | Operating voltage      | 1.71 | 3.6  | V    |

|     | Frequency of operation | —    | 6.25 | MHz  |

Table continues on the next page...

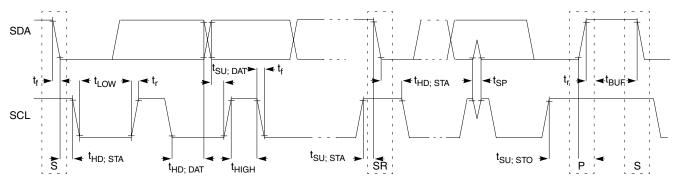

| Characteristic                                                       | Symbol                | Standard Mode |         | Fast Mode                          |         | Unit |

|----------------------------------------------------------------------|-----------------------|---------------|---------|------------------------------------|---------|------|

|                                                                      |                       | Minimum       | Maximum | Minimum                            | Maximum |      |

| Fall time of SDA and SCL signals                                     | t <sub>f</sub>        | —             | 300     | 20 +0.1C <sub>b</sub> <sup>5</sup> | 300     | ns   |

| Set-up time for STOP condition                                       | t <sub>SU</sub> ; STO | 4             | _       | 0.6                                |         | μs   |

| Bus free time between STOP and<br>START condition                    | t <sub>BUF</sub>      | 4.7           | _       | 1.3                                | —       | μs   |

| Pulse width of spikes that must be<br>suppressed by the input filter | t <sub>SP</sub>       | N/A           | N/A     | 0                                  | 50      | ns   |

#### Table 44. I<sup>2</sup>C timing (continued)

- The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves

acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and SCL

lines.

- 2. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 3. Input signal Slew = 10ns and Output Load = 50pf

- 4. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 5. A Fast mode l<sup>2</sup>C bus device can be used in a Standard mode l2C bus system, but the requirement t<sub>SU; DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, then it must output the next data bit to the SDA line t<sub>max</sub> + t<sub>SU; DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode l<sup>2</sup>C bus specification) before the SCL line is released.

- 6.  $C_b = total capacitance of the one bus line in pF.$

Figure 24. Timing definition for fast and standard mode devices on the I<sup>2</sup>C bus

## 6.8.8 UART switching specifications

See General switching specifications.

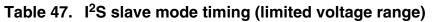

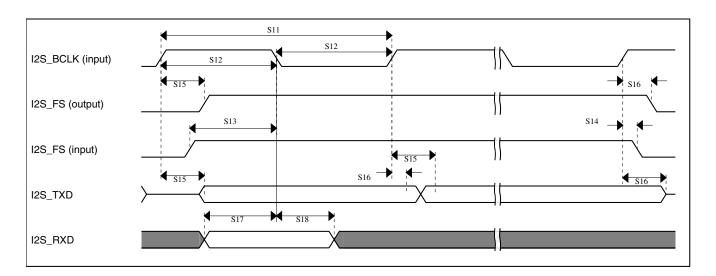

| Num | Description                               | Min.                 | Max. | Unit        |

|-----|-------------------------------------------|----------------------|------|-------------|

|     | Operating voltage                         | 2.7                  | 3.6  | V           |

| S11 | I2S_BCLK cycle time (input)               | 8 x t <sub>SYS</sub> | —    | ns          |

| S12 | I2S_BCLK pulse width high/low (input)     | 45%                  | 55%  | MCLK period |

| S13 | I2S_FS input setup before I2S_BCLK        | 10                   |      | ns          |

| S14 | I2S_FS input hold after I2S_BCLK          | 3                    | —    | ns          |

| S15 | I2S_BCLK to I2S_TXD/I2S_FS output valid   | —                    | 20   | ns          |

| S16 | I2S_BCLK to I2S_TXD/I2S_FS output invalid | 0                    |      | ns          |

| S17 | I2S_RXD setup before I2S_BCLK             | 10                   | —    | ns          |

| S18 | I2S_RXD hold after I2S_BCLK               | 2                    | —    | ns          |

## Figure 27. I<sup>2</sup>S timing — slave modes

## Table 48. I<sup>2</sup>S master mode timing (full voltage range)

| Num | Description                                | Min.                 | Max. | Unit        |

|-----|--------------------------------------------|----------------------|------|-------------|

|     | Operating voltage                          | 1.71                 | 3.6  | V           |

| S1  | I2S_MCLK cycle time                        | 2 x t <sub>SYS</sub> |      | ns          |

| S2  | I2S_MCLK pulse width high/low              | 45%                  | 55%  | MCLK period |

| S3  | I2S_BCLK cycle time                        | 5 x t <sub>SYS</sub> | _    | ns          |

| S4  | I2S_BCLK pulse width high/low              | 45%                  | 55%  | BCLK period |

| S5  | I2S_BCLK to I2S_FS output valid            | —                    | 15   | ns          |

| S6  | I2S_BCLK to I2S_FS output invalid          | -4.3                 | _    | ns          |

| S7  | I2S_BCLK to I2S_TXD valid                  | —                    | 15   | ns          |

| S8  | I2S_BCLK to I2S_TXD invalid                | -4.6                 | _    | ns          |

| S9  | I2S_RXD/I2S_FS input setup before I2S_BCLK | 23.9                 | _    | ns          |

| S10 | I2S_RXD/I2S_FS input hold after I2S_BCLK   | 0                    | _    | ns          |

|             |                                                  |                                                  |                                                  |                  |           |             |            |      |            |      | Pin   |

|-------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------|-----------|-------------|------------|------|------------|------|-------|

| 100<br>LQFP | Pin Name                                         | Default                                          | ALTO                                             | ALT1             | ALT2      | ALT3        | ALT4       | ALT5 | ALT6       | ALT7 | EzPor |

| 2           | PTE1/<br>LLWU_P0                                 | ADC1_SE5a                                        | ADC1_SE5a                                        | PTE1/<br>LLWU_P0 | SPI1_SOUT | UART1_RX    | SDHC0_D0   |      | I2C1_SCL   |      |       |

| 3           | PTE2/<br>LLWU_P1                                 | ADC1_SE6a                                        | ADC1_SE6a                                        | PTE2/<br>LLWU_P1 | SPI1_SCK  | UART1_CTS_b | SDHC0_DCLK |      |            |      |       |

| 4           | PTE3                                             | ADC1_SE7a                                        | ADC1_SE7a                                        | PTE3             | SPI1_SIN  | UART1_RTS_b | SDHC0_CMD  |      |            |      |       |

| 5           | PTE4/<br>LLWU_P2                                 | DISABLED                                         |                                                  | PTE4/<br>LLWU_P2 | SPI1_PCS0 | UART3_TX    | SDHC0_D3   |      |            |      |       |

| 6           | PTE5                                             | DISABLED                                         |                                                  | PTE5             | SPI1_PCS2 | UART3_RX    | SDHC0_D2   |      |            |      |       |

| 7           | PTE6                                             | DISABLED                                         |                                                  | PTE6             | SPI1_PCS3 | UART3_CTS_b | I2S0_MCLK  |      | I2S0_CLKIN |      |       |

| 8           | VDD                                              | VDD                                              | VDD                                              |                  |           |             |            |      |            |      |       |

| 9           | VSS                                              | VSS                                              | VSS                                              |                  |           |             |            |      |            |      |       |

| 10          | USB0_DP                                          | USB0_DP                                          | USB0_DP                                          |                  |           |             |            |      |            |      |       |

| 11          | USB0_DM                                          | USB0_DM                                          | USB0_DM                                          |                  |           |             |            |      |            |      |       |

| 12          | VOUT33                                           | VOUT33                                           | VOUT33                                           |                  |           |             |            |      |            |      |       |

| 13          | VREGIN                                           | VREGIN                                           | VREGIN                                           |                  |           |             |            |      |            |      |       |

| 14          | ADC0_DP1                                         | ADC0_DP1                                         | ADC0_DP1                                         |                  |           |             |            |      |            |      |       |

| 15          | ADC0_DM1                                         | ADC0_DM1                                         | ADC0_DM1                                         |                  |           |             |            |      |            |      |       |

| 16          | ADC1_DP1                                         | ADC1_DP1                                         | ADC1_DP1                                         |                  |           |             |            |      |            |      |       |

| 17          | ADC1_DM1                                         | ADC1_DM1                                         | ADC1_DM1                                         |                  |           |             |            |      |            |      |       |

| 18          | PGA0_DP/<br>ADC0_DP0/<br>ADC1_DP3                | PGA0_DP/<br>ADC0_DP0/<br>ADC1_DP3                | PGA0_DP/<br>ADC0_DP0/<br>ADC1_DP3                |                  |           |             |            |      |            |      |       |

| 19          | PGA0_DM/<br>ADC0_DM0/<br>ADC1_DM3                | PGA0_DM/<br>ADC0_DM0/<br>ADC1_DM3                | PGA0_DM/<br>ADC0_DM0/<br>ADC1_DM3                |                  |           |             |            |      |            |      |       |

| 20          | PGA1_DP/<br>ADC1_DP0/<br>ADC0_DP3                | PGA1_DP/<br>ADC1_DP0/<br>ADC0_DP3                | PGA1_DP/<br>ADC1_DP0/<br>ADC0_DP3                |                  |           |             |            |      |            |      |       |

| 21          | PGA1_DM/<br>ADC1_DM0/<br>ADC0_DM3                | PGA1_DM/<br>ADC1_DM0/<br>ADC0_DM3                | PGA1_DM/<br>ADC1_DM0/<br>ADC0_DM3                |                  |           |             |            |      |            |      |       |

| 22          | VDDA                                             | VDDA                                             | VDDA                                             |                  |           |             |            |      |            |      |       |

| 23          | VREFH                                            | VREFH                                            | VREFH                                            |                  |           |             |            |      |            |      |       |

| 24          | VREFL                                            | VREFL                                            | VREFL                                            |                  |           |             |            |      |            |      |       |

| 25          | VSSA                                             | VSSA                                             | VSSA                                             |                  |           |             |            |      |            |      |       |

| 26          | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 |                  |           |             |            |      |            |      |       |

| 27          | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              |                  |           |             |            |      |            |      |       |

| 28          | XTAL32                                           | XTAL32                                           | XTAL32                                           |                  |           |             |            |      |            |      |       |

| 29          | EXTAL32                                          | EXTAL32                                          | EXTAL32                                          |                  |           |             |            |      |            |      | L     |

| 30          | VBAT                                             | VBAT                                             | VBAT                                             |                  |           |             |            |      |            |      |       |

#### K20 Sub-Family Data Sheet Data Sheet, Rev. 7, 02/2013.

UART4\_TX

CAN1\_TX

ADC0\_SE17

ADC0\_SE17

PTE24

PTE24

31

EWM\_OUT\_b

| 100<br>LQFP | Pin Name          | Default                            | ALTO                               | ALT1              | ALT2        | ALT3        | ALT4       | ALT5     | ALT6            | ALT7                   | EzPort   |

|-------------|-------------------|------------------------------------|------------------------------------|-------------------|-------------|-------------|------------|----------|-----------------|------------------------|----------|

| 32          | PTE25             | ADC0_SE18                          | ADC0_SE18                          | PTE25             | CAN1_RX     | UART4_RX    |            |          | EWM_IN          |                        |          |

| 33          | PTE26             | DISABLED                           |                                    | PTE26             |             | UART4_CTS_b |            |          | RTC_CLKOUT      | USB_CLKIN              |          |

| 34          | PTA0              | JTAG_TCLK/<br>SWD_CLK/<br>EZP_CLK  | TSI0_CH1                           | PTA0              | UARTO_CTS_b | FTM0_CH5    |            |          |                 | JTAG_TCLK/<br>SWD_CLK  | EZP_CLK  |

| 35          | PTA1              | JTAG_TDI/<br>EZP_DI                | TSI0_CH2                           | PTA1              | UARTO_RX    | FTM0_CH6    |            |          |                 | JTAG_TDI               | EZP_DI   |

| 36          | PTA2              | JTAG_TDO/<br>TRACE_SWO/<br>EZP_DO  | TSI0_CH3                           | PTA2              | UARTO_TX    | FTM0_CH7    |            |          |                 | JTAG_TDO/<br>TRACE_SWO | EZP_DO   |

| 37          | PTA3              | JTAG_TMS/<br>SWD_DIO               | TSI0_CH4                           | PTA3              | UART0_RTS_b | FTM0_CH0    |            |          |                 | JTAG_TMS/<br>SWD_DIO   |          |

| 38          | PTA4/<br>LLWU_P3  | NMI_b/<br>EZP_CS_b                 | TSI0_CH5                           | PTA4/<br>LLWU_P3  |             | FTM0_CH1    |            |          |                 | NMI_b                  | EZP_CS_b |

| 39          | PTA5              | DISABLED                           |                                    | PTA5              |             | FTM0_CH2    |            | CMP2_OUT | I2S0_RX_BCLK    | JTAG_TRST              |          |

| 40          | VDD               | VDD                                | VDD                                |                   |             |             |            |          |                 |                        |          |

| 41          | VSS               | VSS                                | VSS                                |                   |             |             |            |          |                 |                        |          |

| 42          | PTA12             | CMP2_IN0                           | CMP2_IN0                           | PTA12             | CAN0_TX     | FTM1_CH0    |            |          | I2S0_TXD        | FTM1_QD_<br>PHA        |          |

| 43          | PTA13/<br>LLWU_P4 | CMP2_IN1                           | CMP2_IN1                           | PTA13/<br>LLWU_P4 | CAN0_RX     | FTM1_CH1    |            |          | I2S0_TX_FS      | FTM1_QD_<br>PHB        |          |

| 44          | PTA14             | DISABLED                           |                                    | PTA14             | SPI0_PCS0   | UART0_TX    |            |          | I2S0_TX_BCLK    |                        |          |

| 45          | PTA15             | DISABLED                           |                                    | PTA15             | SPI0_SCK    | UART0_RX    |            |          | I2S0_RXD        |                        |          |

| 46          | PTA16             | DISABLED                           |                                    | PTA16             | SPI0_SOUT   | UART0_CTS_b |            |          | I2S0_RX_FS      |                        |          |

| 47          | PTA17             | ADC1_SE17                          | ADC1_SE17                          | PTA17             | SPI0_SIN    | UART0_RTS_b |            |          | I2S0_MCLK       | I2S0_CLKIN             |          |

| 48          | VDD               | VDD                                | VDD                                |                   |             |             |            |          |                 |                        |          |

| 49          | VSS               | VSS                                | VSS                                |                   |             |             |            |          |                 |                        |          |

| 50          | PTA18             | EXTAL                              | EXTAL                              | PTA18             |             | FTM0_FLT2   | FTM_CLKIN0 |          |                 |                        |          |

| 51          | PTA19             | XTAL                               | XTAL                               | PTA19             |             | FTM1_FLT0   | FTM_CLKIN1 |          | LPT0_ALT1       |                        |          |

| 52          | RESET_b           | RESET_b                            | RESET_b                            |                   |             |             |            |          |                 |                        |          |

| 53          | PTB0/<br>LLWU_P5  | ADC0_SE8/<br>ADC1_SE8/<br>TSI0_CH0 | ADC0_SE8/<br>ADC1_SE8/<br>TSI0_CH0 | PTB0/<br>LLWU_P5  | 12C0_SCL    | FTM1_CH0    |            |          | FTM1_QD_<br>Pha |                        |          |

| 54          | PTB1              | ADC0_SE9/<br>ADC1_SE9/<br>TSI0_CH6 | ADC0_SE9/<br>ADC1_SE9/<br>TSI0_CH6 | PTB1              | I2C0_SDA    | FTM1_CH1    |            |          | FTM1_QD_<br>PHB |                        |          |

| 55          | PTB2              | ADC0_SE12/<br>TSI0_CH7             | ADC0_SE12/<br>TSI0_CH7             | PTB2              | I2C0_SCL    | UARTO_RTS_b |            |          | FTM0_FLT3       |                        |          |

| 56          | PTB3              | ADC0_SE13/<br>TSI0_CH8             | ADC0_SE13/<br>TSI0_CH8             | PTB3              | I2C0_SDA    | UARTO_CTS_b |            |          | FTM0_FLT0       |                        |          |

| 57          | PTB9              |                                    |                                    | PTB9              | SPI1_PCS1   | UART3_CTS_b |            | FB_AD20  |                 |                        |          |

| 58          | PTB10             | ADC1_SE14                          | ADC1_SE14                          | PTB10             | SPI1_PCS0   | UART3_RX    |            | FB_AD19  | FTM0_FLT1       |                        |          |

| 59          | PTB11             | ADC1_SE15                          | ADC1_SE15                          | PTB11             | SPI1_SCK    | UART3_TX    |            | FB_AD18  | FTM0_FLT2       |                        |          |

| 60          | VSS               | VSS                                | VSS                                |                   |             |             |            |          |                 |                        |          |

| 61          | VDD               | VDD                                | VDD                                |                   |             |             |            |          |                 |                        |          |

nevision History

| Rev. No. | Date   | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 3        | 3/2011 | Added sections that were inadvertently removed in previous revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 4        | 3/2011 | Reworded I <sub>IC</sub> footnote in "Voltage and Current Operating Requirements" table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|          |        | Added paragraph to "Peripheral operating requirements and behaviors" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|          |        | Added "JTAG full voltage range electricals" table to the "JTAG electricals" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 5        | 6/2011 | <ul> <li>Added 51AG full voltage range electricals table for the 51AG electricals section.</li> <li>Changed <i>DC injection current</i> specs in "Voltage and current operating requirements" table</li> <li>Changed <i>Input leakage current</i> and <i>internal pullup/pulldown resistor</i> specs in "Voltage and current operating behaviors" table</li> <li>Split <i>Low power stop mode current</i> specs by temperature range in "Power consumption operating behaviors" table</li> <li>Changed typical <i>I<sub>DD</sub></i>, <i>V<sub>BAT</sub></i> spec in "Power consumption operating behaviors" table</li> <li>Added LPTIME clock specs to "Device clock specifications" table</li> <li>Changed <i>PLL operating current</i> in "MCG specifications" table</li> <li>Changed <i>PLL operating current</i> in "MCG specifications" table</li> <li>Changed <i>Supply current</i> in "Oscillator DC electrical specifications" table</li> <li>Changed <i>Crystal startup time</i> in "Cscillator frequency specifications" table</li> <li>Changed <i>Operating voltage</i> in "EzPort switching specifications" table</li> <li>Changed <i>Crystal startup time</i> in "Cscillator frequency specifications" table</li> <li>Changed <i>Crystal startup time</i> in "Cscillator sections" table</li> <li>Changed <i>Crystal startup time</i> in "Cscillator frequency specifications" table</li> <li>Changed <i>Crystal startup time</i> in "Cscillator frequency specifications" table</li> <li>Changed <i>Alog Casynchronous clock source</i> specs in "16-bit ADC characteristics" table</li> <li>Changed <i>Alog Casynchronous clock source</i> specs in "16-bit ADC with PGA characteristics" table</li> <li>Changed <i>Analog comparator initialization delay</i> in "Comparator and 6-bit DAC electrical specifications" table</li> <li>Changed <i>Analog comparator initialization delay</i> in "Comparator and 6-bit DAC electrical specifications" table</li> <li>Changed <i>Analog comparator initialization delay</i> in "Comparator and 6-bit DAC electrical specifications" table</li> <li>Changed <i>Analog comparator initialization delay</i></li></ul> |  |  |  |  |  |

Table 51. Revision History (continued)

Table continues on the next page...