Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFl

| Product Status          | Obsolete                                                             |

|-------------------------|----------------------------------------------------------------------|

| Туре                    | Fixed Point                                                          |

| Interface               | CAN, EBI/EMI, SD/SDIO, SPI, SPORT, TWI, UART/USART, USB OTG          |

| Clock Rate              | 533MHz                                                               |

| Non-Volatile Memory     | External                                                             |

| On-Chip RAM             | 260kB                                                                |

| Voltage - I/O           | 3.30V                                                                |

| Voltage - Core          | 1.19V                                                                |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                    |

| Mounting Type           | Surface Mount                                                        |

| Package / Case          | 400-LFBGA, CSPBGA                                                    |

| Supplier Device Package | 400-CSPBGA (17x17)                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adbf549wbbcz5m03 |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The ADSP-BF54x Blackfin processors are completely code- and pin-compatible. They differ only with respect to their performance, on-chip memory, and selection of I/O peripherals. Specific performance, memory, and feature configurations are shown in Table 1.

By integrating a rich set of industry-leading system peripherals and memory, Blackfin processors are the platform of choice for next-generation applications that require RISC-like programmability, multimedia support, and leading-edge signal processing in one integrated package.

#### LOW POWER ARCHITECTURE

Blackfin processors provide world-class power management and performance. Blackfin processors are designed in a low power and low voltage design methodology and feature on-chip dynamic power management, the ability to vary both the voltage and frequency of operation to significantly lower overall power consumption. Reducing both voltage and frequency can result in a substantial reduction in power consumption as compared to reducing only the frequency of operation. This translates into longer battery life for portable appliances.

#### SYSTEM INTEGRATION

The ADSP-BF54x Blackfin processors are highly integrated system-on-a-chip solutions for the next generation of embedded network connected applications. By combining industrystandard interfaces with a high performance signal processing core, users can develop cost-effective solutions quickly without the need for costly external components. The system peripherals include a high speed USB OTG (On-the-Go) controller with integrated PHY, CAN 2.0B controllers, TWI controllers, UART ports, SPI ports, serial ports (SPORTs), ATAPI controller, SD/SDIO controller, a real-time clock, a watchdog timer, LCD controller, and multiple enhanced parallel peripheral interfaces.

### **BLACKFIN PROCESSOR PERIPHERALS**

The ADSP-BF54x processors contain a rich set of peripherals connected to the core via several high bandwidth buses, providing flexibility in system configuration as well as excellent overall system performance (see Figure 1 on Page 1). The generalpurpose peripherals include functions such as UARTs, SPI, TWI, timers with pulse width modulation (PWM) and pulse measurement capability, general-purpose I/O pins, a real-time clock, and a watchdog timer. This set of functions satisfies a wide variety of typical system support needs and is augmented by the system expansion capabilities of the part. The ADSP-BF54x processors contain dedicated network communication modules and high speed serial and parallel ports, an interrupt controller for flexible management of interrupts from the onchip peripherals or external sources, and power management control functions to tailor the performance and power characteristics of the processor and system to many application scenarios.

All of the peripherals, except for general-purpose I/O, CAN, TWI, real-time clock, and timers, are supported by a flexible DMA structure. There are also separate memory DMA channels dedicated to data transfers between the processor's various memory spaces, including external DDR (either standard or mobile, depending on the device) and asynchronous memory. Multiple on-chip buses running at up to 133 MHz provide enough bandwidth to keep the processor core running along with activity on all of the on-chip and external peripherals.

The ADSP-BF54x Blackfin processors include an on-chip voltage regulator in support of the dynamic power management capability. The voltage regulator provides a range of core voltage levels when supplied from  $V_{DDEXT}$ . The voltage regulator can be bypassed at the user's discretion.

#### **BLACKFIN PROCESSOR CORE**

As shown in Figure 2 on Page 5, the Blackfin processor core contains two 16-bit multipliers, two 40-bit accumulators, two 40-bit ALUs, four video ALUs, and a 40-bit shifter. The computation units process 8-, 16-, or 32-bit data from the register file.

The compute register file contains eight 32-bit registers. When performing compute operations on 16-bit operand data, the register file operates as 16 independent 16-bit registers. All operands for compute operations come from the multiported register file and instruction constant fields.

Each MAC can perform a 16-bit by 16-bit multiply in each cycle, accumulating the results into the 40-bit accumulators. Signed and unsigned formats, rounding, and saturation are supported.

The ALUs perform a traditional set of arithmetic and logical operations on 16- or 32-bit data. In addition, many special instructions are included to accelerate various signal processing tasks. These include bit operations such as field extract and population count, modulo  $2^{32}$  multiply, divide primitives, saturation and rounding, and sign/exponent detection. The set of video instructions include byte alignment and packing operations, 16-bit and 8-bit adds with clipping, 8-bit average operations, and 8-bit subtract/absolute value/accumulate (SAA) operations. Also provided are the compare/select and vector search instructions.

For certain instructions, two 16-bit ALU operations can be performed simultaneously on register pairs (a 16-bit high half and 16-bit low half of a compute register). By also using the second ALU, quad 16-bit operations are possible.

The 40-bit shifter can perform shifts and rotates and is used to support normalization, field extract, and field deposit instructions.

The program sequencer controls the flow of instruction execution, including instruction alignment and decoding. For program flow control, the sequencer supports PC relative and indirect conditional jumps (with static branch prediction), and subroutine calls. Hardware is provided to support zero-overhead looping. The architecture is fully interlocked, meaning that the programmer need not manage the pipeline when executing instructions with data dependencies.

The address arithmetic unit provides two addresses for simultaneous dual fetches from memory. It contains a multiported register file consisting of four sets of 32-bit index, modify,

The controller provides support for five different types of events:

- Emulation. An emulation event causes the processor to enter emulation mode, allowing command and control of the processor via the JTAG interface.

- Reset. This event resets the processor.

- Non-maskable interrupt (NMI). The NMI event can be generated by the software watchdog timer or by the NMI input signal to the processor. The NMI event is frequently used as a power-down indicator to initiate an orderly shutdown of the system.

- Exceptions. Events that occur synchronously to program flow (that is, the exception is taken before the instruction is allowed to complete). Conditions such as data alignment violations and undefined instructions cause exceptions.

- Interrupts. Events that occur asynchronously to program flow. They are caused by input pins, timers, and other peripherals, as well as by an explicit software instruction.

Each event type has an associated register to hold the return address and an associated return-from-event instruction. When an event is triggered, the state of the processor is saved on the supervisor stack.

The ADSP-BF54x Blackfin processor event controller consists of two stages, the core event controller (CEC) and the system interrupt controller (SIC). The core event controller works with the system interrupt controller to prioritize and control all system events. Conceptually, interrupts from the peripherals enter into the SIC and are then routed directly into the general-purpose interrupts of the CEC.

### Core Event Controller (CEC)

The CEC supports nine general-purpose interrupts (IVG15–7), in addition to the dedicated interrupt and exception events. Of these general-purpose interrupts, the two lowest-priority interrupts (IVG15–14) are recommended to be reserved for software interrupt handlers, leaving seven prioritized interrupt inputs to support the peripherals of the ADSP-BF54x Blackfin processors. Table 3 describes the inputs to the CEC, identifies their names in the event vector table (EVT), and lists their priorities.

### System Interrupt Controller (SIC)

The system interrupt controller provides the mapping and routing of events from the many peripheral interrupt sources to the prioritized general-purpose interrupt inputs of the CEC. Although the ADSP-BF54x Blackfin processors provide a default mapping, the user can alter the mappings and priorities of interrupt events by writing the appropriate values into the interrupt assignment registers (SIC\_IARx). The *ADSP-BF54x Hardware Reference Manual*, "System Interrupts" chapter describes the inputs into the SIC and the default mappings into the CEC.

| Priority       |                        |                  |

|----------------|------------------------|------------------|

| (0 is Highest) | Event Class            | <b>EVT Entry</b> |

| 0              | Emulation/Test Control | EMU              |

| 1              | Reset                  | RST              |

| 2              | Nonmaskable Interrupt  | NMI              |

| 3              | Exception              | EVX              |

| 4              | Reserved               | —                |

| 5              | Hardware Error         | IVHW             |

| 5              | Core Timer             | IVTMR            |

| 7              | General Interrupt 7    | IVG7             |

| 3              | General Interrupt 8    | IVG8             |

| )              | General Interrupt 9    | IVG9             |

| 0              | General Interrupt 10   | IVG10            |

| 11             | General Interrupt 11   | IVG11            |

| 2              | General Interrupt 12   | IVG12            |

| 3              | General Interrupt 13   | IVG13            |

| 4              | General Interrupt 14   | IVG14            |

| 15             | General Interrupt 15   | IVG15            |

#### **Event Control**

The ADSP-BF54x Blackfin processors provide the user with a very flexible mechanism to control the processing of events. In the CEC, three registers are used to coordinate and control events. Each register is 16 bits wide:

- CEC interrupt latch register (ILAT). The ILAT register indicates when events have been latched. The appropriate bit is set when the processor has latched the event and cleared when the event has been accepted into the system. This register is updated automatically by the controller, but it may be written only when its corresponding IMASK bit is cleared.

- CEC interrupt mask register (IMASK). The IMASK register controls the masking and unmasking of individual events. When a bit is set in the IMASK register, that event is unmasked and is processed by the CEC when asserted. A cleared bit in the IMASK register masks the event, preventing the processor from servicing the event even though the event may be latched in the ILAT register. This register may be read or written while in supervisor mode. Note that general-purpose interrupts can be globally enabled and disabled with the STI and CLI instructions, respectively.

- CEC interrupt pending register (IPEND). The IPEND register keeps track of all nested events. A set bit in the IPEND register indicates that the event is currently active or nested at some level. This register is updated automatically by the controller but may be read while in supervisor mode.

The SIC allows further control of event processing by providing three 32-bit interrupt control and status registers. Each register contains a bit corresponding to each of the peripheral interrupt events shown in the *ADSP-BF54x Hardware Reference Manual*, "System Interrupts" chapter.

Table 3. Core Event Controller (CEC)

The USB clock (USB\_XI) is provided through a dedicated external crystal or crystal oscillator. See Table 62 for related timing requirements. If using a fundamental mode crystal to provide the USB clock, connect the crystal between USB\_XI and USB\_XO with a circuit similar to that shown in Figure 7. Use a parallel-resonant, fundamental mode, microprocessor-grade crystal. If a third-overtone crystal is used, follow the circuit guidelines outlined in Clock Signals on Page 17 for third-overtone crystals.

The USB On-the-Go dual-role device controller includes a Phase Locked Loop with programmable multipliers to generate the necessary internal clocking frequency for USB. The multiplier value should be programmed based on the USB\_XI clock frequency to achieve the necessary 480 MHz internal clock for USB high speed operation. For example, for a USB\_XI crystal frequency of 24 MHz, the USB\_PLLOSC\_CTRL register should be programmed with a multiplier value of 20 to generate a 480 MHz internal clock.

### **ATA/ATAPI-6 INTERFACE**

The ATAPI interface connects to CD/DVD and HDD drives and is ATAPI-6 compliant. The controller implements the peripheral I/O mode, the multi-DMA mode, and the Ultra DMA mode. The DMA modes enable faster data transfer and reduced host management. The ATAPI controller supports PIO, multi-DMA, and ultra DMA ATAPI accesses. Key features include:

- Supports PIO modes 0, 1, 2, 3, 4

- Supports multiword DMA modes 0, 1, 2

- Supports ultra DMA modes 0, 1, 2, 3, 4, 5 (up to UDMA 100)

- Programmable timing for ATA interface unit

- Supports CompactFlash cards using true IDE mode

By default, the ATAPI\_A0-2 address signals and the ATA-PI\_D0-15 data signals are shared on the asynchronous memory interface with the asynchronous memory and NAND flash controllers. The data and address signals can be remapped to GPIO ports F and G, respectively, by setting PORTF\_MUX[1:0] to b#01.

### **KEYPAD INTERFACE**

The keypad interface is a 16-pin interface module that is used to detect the key pressed in a  $8 \times 8$  (maximum) keypad matrix. The size of the input keypad matrix is programmable. The interface is capable of filtering the bounce on the input pins, which is common in keypad applications. The width of the filtered bounce is programmable. The module is capable of generating an interrupt request to the core once it identifies that any key has been pressed.

The interface supports a press-release-press mode and infrastructure for a press-hold mode. The former mode identifies a press, release and press of a key as two consecutive presses of the same key, whereas the latter mode checks the input key's state in periodic intervals to determine the number of times the same key is meant to be pressed. It is possible to detect when multiple keys are pressed simultaneously and to provide limited key resolution capability when this happens.

### SECURE DIGITAL (SD)/SDIO CONTROLLER

The SD/SDIO controller is a serial interface that stores data at a data rate of up to 10M bytes per second using a 4-bit data line.

The SD/SDIO controller supports the SD memory mode only. The interface supports all the power modes and performs error checking by CRC.

### **CODE SECURITY**

An OTP/security system, consisting of a blend of hardware and software, provides customers with a flexible and rich set of code security features with Lockbox<sup>®</sup> secure technology. Key features include:

- OTP memory

- Unique chip ID

- Code authentication

- Secure mode of operation

The security scheme is based upon the concept of authentication of digital signatures using standards-based algorithms and provides a secure processing environment in which to execute code and protect assets. See Lockbox Secure Technology Disclaimer on Page 23.

### **MEDIA TRANSCEIVER MAC LAYER (MXVR)**

The ADSP-BF549 Blackfin processors provide a media transceiver (MXVR) MAC layer, allowing the processor to be connected directly to a MOST<sup>® 1</sup> network through an FOT. See Figure 5 on Page 15 for an example of a MXVR MOST connection.

The MXVR is fully compatible with industry-standard standalone MOST controller devices, supporting 22.579 Mbps or 24.576 Mbps data transfer. It offers faster lock times, greater jitter immunity, and a sophisticated DMA scheme for data transfers. The high speed internal interface to the core and L1 memory allows the full bandwidth of the network to be utilized. The MXVR can operate as either the network master or as a network slave.

The MXVR supports synchronous data, asynchronous packets, and control messages using dedicated DMA channels that operate autonomously from the processor core moving data to and from L1 and/or L2 memory. Synchronous data is transferred to or from the synchronous data physical channels on the MOST bus through eight programmable DMA channels. The synchronous data DMA channels can operate in various modes including modes that trigger DMA operation when data patterns are detected in the receive data stream. Furthermore, two DMA channels support asynchronous traffic, and two others support control message traffic.

<sup>&</sup>lt;sup>1</sup>MOST is a registered trademark of Standard Microsystems, Corp.

#### Table 11. Pin Descriptions (Continued)

| Pin Name                      | I/O <sup>1</sup> | Function (First/Second/Third/Fourth)                                                                      | Drive<br>Type <sup>2</sup> |

|-------------------------------|------------------|-----------------------------------------------------------------------------------------------------------|----------------------------|

| DDR Memory Interface          |                  |                                                                                                           |                            |

| DA0-12                        | 0                | DDR Address Bus                                                                                           | D                          |

| DBA0-1                        | 0                | DDR Bank Active Strobe                                                                                    | D                          |

| DQ0-15                        | I/O              | DDR Data Bus                                                                                              | D                          |

| DQS0-1                        | I/O              | DDR Data Strobe                                                                                           | D                          |

| DQM0-1                        | о                | DDR Data Mask for Reads and Writes                                                                        | D                          |

| DCLK0-1                       | о                | DDR Output Clock                                                                                          | D                          |

| DCLK0-1                       | о                | DDR Complementary Output Clock                                                                            | D                          |

| DCS0-1                        | 0                | DDR Chip Selects                                                                                          | D                          |

| DCLKE <sup>9</sup>            | 0                | DDR Clock Enable (Requires a pull-down if hibernate with DDR self-<br>refresh is used.)                   | D                          |

| DRAS                          | о                | DDR Row Address Strobe                                                                                    | D                          |

| DCAS                          | о                | DDR Column Address Strobe                                                                                 | D                          |

| DWE                           | о                | DDR Write Enable                                                                                          | D                          |

| DDR_VREF                      | I                | DDR Voltage Reference                                                                                     |                            |

| DDR_VSSR                      | I                | DDR Voltage Reference Shield (Must be connected to GND.)                                                  |                            |

| Asynchronous Memory Interface |                  |                                                                                                           |                            |

| A1-3                          | О                | Address Bus for Async and ATAPI Addresses                                                                 | А                          |

| D0-15/ND_D0-15/ATAPI_D0-15    | I/O              | Data Bus for Async, NAND and ATAPI Accesses                                                               | А                          |

| AMS0-3                        | 0                | Bank Selects (Pull high with a resistor when used as chip select. Require pull-ups if hibernate is used.) | A                          |

| ABEO / ND_CLE                 | 0                | Byte Enables:Data Masks for Asynchronous Access/NAND Command<br>Latch Enable                              | A                          |

| ABE1/ND_ALE                   | 0                | Byte Enables : Data Masks for Asynchronous Access/NAND Address Latch<br>Enable                            | A                          |

| AOE/NR_ADV                    | 0                | Output Enable/NOR Address Data Valid                                                                      | А                          |

| ĀRĒ                           | 0                | Read Enable / NOR Output Enable                                                                           | А                          |

| ĀWE                           | 0                | Write Enable                                                                                              | А                          |

| ATAPI Controller Pins         |                  |                                                                                                           |                            |

| ATAPI_PDIAG                   | I                | Determines if an 80-pin cable is connected to the host. (Pull high or low when unused.)                   |                            |

| High Speed USB OTG Pins       | 1                |                                                                                                           |                            |

| USB_DP                        | I/O              | USB D+ Pin (Pull low when unused.)                                                                        |                            |

| USB_DM                        | I/O              | USB D– Pin (Pull low when unused.)                                                                        |                            |

| USB_XI                        | с                | Clock XTAL Input (Pull high or low when unused.)                                                          |                            |

| USB_XO                        | с                | Clock XTAL Output (Leave unconnected when unused.)                                                        |                            |

| USB_ID <sup>10</sup>          | I                | USB OTG ID Pin (Pull high when unused.)                                                                   |                            |

#### Table 11. Pin Descriptions (Continued)

| Pin Name                         | I/O <sup>1</sup> | Function (First/Second/Third/Fourth)                                                                                                                 | Driver<br>Type <sup>2</sup> |

|----------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Supplies                         |                  |                                                                                                                                                      |                             |

| V <sub>DDINT</sub>               | Р                | Internal Power Supply                                                                                                                                |                             |

| V <sub>DDEXT</sub> <sup>12</sup> | Р                | External Power Supply                                                                                                                                |                             |

| V <sub>DDDDR</sub> <sup>12</sup> | Р                | External DDR Power Supply                                                                                                                            |                             |

| V <sub>DDUSB</sub> <sup>12</sup> | Р                | External USB Power Supply                                                                                                                            |                             |

| V <sub>DDRTC</sub> <sup>12</sup> | Р                | RTC Clock Supply                                                                                                                                     |                             |

| V <sub>DDVR</sub> <sup>13</sup>  | Р                | Internal Voltage Regulator Power Supply (Connect to $V_{DDEXT}$ when unused.)                                                                        |                             |

| GND                              | G                | Ground                                                                                                                                               |                             |

| V <sub>DDMP</sub> <sup>12</sup>  | Р                | MXVR PLL Power Supply. (Must be driven to same level as $V_{\text{DDINT}}$ . Connect to $V_{\text{DDINT}}$ when unused or when MXVR is not present.) |                             |

| GND <sub>MP</sub> <sup>12</sup>  | G                | MXVR PLL Ground (Connect to GND when unused or when MXVR is not present.)                                                                            |                             |

<sup>1</sup>I = Input, O = Output, P = Power, G = Ground, C = Crystal, A = Analog.

<sup>2</sup>Refer to Table 62 on Page 88 through Table 71 on Page 89 for driver types.

<sup>3</sup>To use the SPI memory boot, SPI0SCK should have a pulldown, SPI0MISO should have a pullup, and SPI0SEL1 is used as the CS with a pullup.

<sup>4</sup>HWAIT/HWAITA should be pulled high or low to configure polarity. See Booting Modes on Page 18.

${}^{5}\overline{\text{GPW}}$  functionality is available when MXVR is not present or unused.

<sup>6</sup> This pin should not be used as GPIO if booting in mode 1.

<sup>7</sup>This pin should always be enabled as ND\_CE in software and pulled high with a resistor when using NAND flash.

<sup>8</sup> This pin should always be enabled as BR in software and pulled high to enable asynchronous access.

<sup>9</sup> This pin must be pulled low through a 10kOhm resistor if self-refresh mode is desired during hibernate state or deep-sleep mode.

<sup>10</sup>If the USB is used in device mode only, the USB\_ID pin should be either pulled high or left unconnected.

<sup>11</sup>This pin is an output only during initialization of USB OTG session request pulses in peripheral mode. Therefore, host mode or OTG type A mode requires that an external voltage source of 5 V, at 8 mA or more per the OTG specification, be applied to this pin. Other OTG modes require that this external voltage be disabled.

<sup>12</sup>To ensure proper operation, the power pins should be driven to their specified level even if the associated peripheral is not used in the application.

<sup>13</sup>This pin must always be connected. If the internal voltage regulator is not being used, this pin may be connected to V<sub>DDEXT</sub>. Otherwise it should be powered according to the VDDVR specification. For automotive grade models, the internal voltage regulator must not be used and this pin must be tied to V<sub>DDEXT</sub>.

<sup>10</sup>Parameter value applies to USB\_DP, USB\_DM, and USB\_VBUS pins. See Absolute Maximum Ratings on Page 40.

<sup>11</sup>Parameter value applies to all input and bidirectional pins, except PB1-0, PE15-14, PG15-11, and PH7-6.

<sup>12</sup>Parameter value applies to pins PG15-11 and PH7-6.

<sup>13</sup>Parameter value applies to pins PB1-0 and PE15-14. Consult the I<sup>2</sup>C specification version 2.1 for the proper resistor value and other open drain pin electrical parameters.

$^{14}$ T<sub>J</sub> must be in the range: 0°C < T<sub>J</sub> < 55°C during OTP memory programming operations.

Table 12 and Table 15 describe the voltage/frequency requirements for the ADSP-BF54x Blackfin processors' clocks. Take care in selecting MSEL, SSEL, and CSEL ratios so as not to exceed the maximum core clock and system clock. Table 14 describes the phase-locked loop operating conditions.

#### Table 12. Core Clock (CCLK) Requirements—533 MHz and 600 MHz Speed Grade<sup>1</sup>

| _                 |                      |                        |                                         | Max CCLK  |      |

|-------------------|----------------------|------------------------|-----------------------------------------|-----------|------|

| Parameter         |                      | Min V <sub>DDINT</sub> | Internal Regulator Setting <sup>2</sup> | Frequency | Unit |

| f <sub>CCLK</sub> | Core Clock Frequency | 1.30 V                 | N/A <sup>2</sup>                        | 600       | MHz  |

|                   |                      | 1.188 V                | 1.25 V                                  | 533       | MHz  |

|                   |                      | 1.14 V                 | 1.20 V                                  | 500       | MHz  |

|                   |                      | 1.045 V                | 1.10 V                                  | 444       | MHz  |

|                   |                      | 0.95 V                 | 1.00 V                                  | 400       | MHz  |

|                   |                      | 0.90 V                 | 0.95 V                                  | 333       | MHz  |

<sup>1</sup>See the Ordering Guide on Page 101.

<sup>2</sup> Use of an internal voltage regulator is not supported on automotive grade and 600 MHz speed grade models. Internal regulator setting should be used as recommended nominal V<sub>DDINT</sub> for external regulator.

#### Table 13. Core Clock (CCLK) Requirements—400 MHz Speed Grade<sup>1</sup>

| Parameter         |                      | Min V <sub>DDINT</sub> | Internal Regulator Setting | Max CCLK<br>g <sup>2</sup> Frequency | Unit |

|-------------------|----------------------|------------------------|----------------------------|--------------------------------------|------|

| f <sub>cclk</sub> | Core Clock Frequency | 1.14 V                 | 1.20 V                     | 400                                  | MHz  |

|                   |                      | 1.045 V                | 1.10 V                     | 364                                  | MHz  |

|                   |                      | 0.95 V                 | 1.00 V                     | 333                                  | MHz  |

|                   |                      | 0.90 V                 | 0.95 V                     | 300                                  | MHz  |

<sup>1</sup>See Ordering Guide on Page 101.

<sup>2</sup> Use of an internal voltage regulator is not supported on automotive grade models. Internal regulator setting should be used as recommended nominal V<sub>DDINT</sub> for external regulator.

#### **Table 14. Phase-Locked Loop Operating Conditions**

| Parameter        |                                               | Min | Max                       | Unit |

|------------------|-----------------------------------------------|-----|---------------------------|------|

| f <sub>VCO</sub> | Voltage Controlled Oscillator (VCO) Frequency | 50  | Maximum f <sub>CCLK</sub> | MHz  |

#### Table 15. System Clock Requirements

|                   |                                                                     | DDR SDRAM Models | Mobile DDR SD    | ORAM Models      |      |

|-------------------|---------------------------------------------------------------------|------------------|------------------|------------------|------|

| Parameter         | Condition                                                           | Max              | Min              | Max              | Unit |

| f <sub>SCLK</sub> | $V_{DDINT} \ge 1.14 V^1$ , Non-extended temperature grades          | 133 <sup>2</sup> | 120 <sup>3</sup> | 133 <sup>2</sup> | MHz  |

| f <sub>SCLK</sub> | $V_{DDINT}$ < 1.14 V <sup>1</sup> , Non-extended temperature grades | 100              | N/A <sup>4</sup> | N/A <sup>4</sup> | MHz  |

| f <sub>SCLK</sub> | $V_{DDINT} \ge 1.0 V^1$ , Extended temperature grade                | 100              | N/A              | N/A              | MHz  |

$^1\,f_{SCLK}$  must be less than or equal to  $f_{CCLK}.$

<sup>2</sup>Rounded number. Actual test specification is SCLK period of 7.5 ns. See Table 25 on Page 43.

<sup>3</sup>Rounded number. Actual test specification is SCLK period of 8.33 ns.

<sup>4</sup>V<sub>DDINT</sub> must be greater than or equal to 1.14 V for mobile DDR SDRAM models. See Operating Conditions on Page 34.

### **ELECTRICAL CHARACTERISTICS**

|                                |                                                                   |                                                                                                                                                                    | Nonaut | tomotive 40     | 00 MHz <sup>1</sup> | All  | Other Devi      | ces <sup>2</sup> |      |

|--------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|---------------------|------|-----------------|------------------|------|

| Parameter                      |                                                                   | Test Conditions                                                                                                                                                    | Min    | Тур             | Max                 | Min  | Тур             | Max              | Unit |

| V <sub>OH</sub>                | High Level Output<br>Voltage for 3.3 V I/O <sup>3</sup>           | $V_{\text{DDEXT}} = 2.7 \text{ V},$<br>$I_{\text{OH}} = -0.5 \text{ mA}$                                                                                           | 2.4    |                 |                     | 2.4  |                 |                  | V    |

|                                | High Level Output<br>Voltage for 2.5 V I/O <sup>3</sup>           | $V_{\text{DDEXT}} = 2.25 \text{ V},$<br>$I_{\text{OH}} = -0.5 \text{ mA}$                                                                                          | 2.0    |                 |                     | 2.0  |                 |                  | V    |

| V <sub>OHDDR</sub>             | High Level Output<br>Voltage for DDR<br>SDRAM <sup>4</sup>        | $V_{DDDDR} = 2.5 V,$<br>$I_{OH} = -8.1 mA$                                                                                                                         | 1.74   |                 |                     | 1.74 |                 |                  | V    |

|                                | High Level Output<br>Voltage for Mobile<br>DDR SDRAM <sup>4</sup> | $V_{DDDDR} = 1.8 V,$<br>$I_{OH} = -0.1 mA$                                                                                                                         | 1.62   |                 |                     | 1.62 |                 |                  | V    |

| V <sub>OL</sub>                | Low Level Output<br>Voltage for 3.3 V I/O <sup>3</sup>            | $V_{DDEXT} = 2.7 V,$<br>$I_{OL} = 2.0 mA$                                                                                                                          |        |                 | 0.4                 |      |                 | 0.4              | V    |

|                                | Low Level Output<br>Voltage for 2.5 V I/O <sup>3</sup>            | $V_{DDEXT} = 2.25 V,$<br>$I_{OL} = 2.0 mA$                                                                                                                         |        |                 | 0.4                 |      |                 | 0.4              | V    |

| V <sub>OLDDR</sub>             | Low Level Output<br>Voltage for DDR<br>SDRAM <sup>4</sup>         | $V_{DDDDR} = 2.5 V,$<br>$I_{OL} = 8.1 mA$                                                                                                                          |        |                 | 0.56                |      |                 | 0.56             | v    |

|                                | Low Level Output<br>Voltage for Mobile<br>DDR SDRAM <sup>4</sup>  | $V_{DDDDR} = 1.8 V,$<br>$I_{OL} = 0.1 mA$                                                                                                                          |        |                 | 0.18                |      |                 | 0.18             | V    |

| I <sub>IH</sub>                | High Level Input<br>Current⁵                                      | $V_{DDEXT} = 3.6 V,$<br>$V_{IN} = V_{IN} Max$                                                                                                                      |        |                 | 10.0                |      |                 | 10.0             | μΑ   |

| I <sub>IHP</sub>               | High Level Input<br>Current <sup>6</sup>                          | $V_{DDEXT} = 3.6 V,$<br>$V_{IN} = V_{IN} Max$                                                                                                                      |        |                 | 50.0                |      |                 | 50.0             | μΑ   |

| I <sub>IHDDR_VREF</sub>        | High Level Input<br>Current for DDR<br>SDRAM <sup>7</sup>         | $V_{DDDDR} = 2.7 \text{ V},$<br>$V_{IN} = 0.51 \times V_{DDDDR}$                                                                                                   |        |                 | 30.0                |      |                 | 30.0             | μΑ   |

|                                | High Level Input<br>Current for Mobile<br>DDR SDRAM <sup>7</sup>  | $V_{DDDDR} = 1.95 \text{ V},$<br>$V_{IN} = 0.51 \times V_{DDDDR}$                                                                                                  |        |                 | 30.0                |      |                 | 30.0             | μA   |

| III <sup>8</sup>               | Low Level Input<br>Current                                        | $V_{DDEXT} = 3.6 \text{ V}, \text{ V}_{IN} = 0 \text{ V}$                                                                                                          |        |                 | 10.0                |      |                 | 10.0             | μΑ   |

| I <sub>OZH</sub> 9             | Three-State Leakage<br>Current <sup>10</sup>                      | $V_{DDEXT} = 3.6 V,$<br>$V_{IN} = V_{IN} Max$                                                                                                                      |        |                 | 10.0                |      |                 | 10.0             | μA   |

| I <sub>OZL</sub> <sup>11</sup> | Three-State Leakage<br>Current <sup>10</sup>                      | $V_{DDEXT} = 3.6 V, V_{IN} = 0 V$                                                                                                                                  |        |                 | 10.0                |      |                 | 10.0             | μA   |

| C <sub>IN</sub>                | Input Capacitance <sup>12</sup>                                   | $\label{eq:final_states} \begin{split} f_{\text{IN}} &= 1 \text{ MHz}, \\ T_{\text{AMBIENT}} &= 25^{\circ}\text{C}, \\ V_{\text{IN}} &= 2.5 \text{ V} \end{split}$ |        | 4 <sup>12</sup> | 8 <sup>12</sup>     |      | 4 <sup>12</sup> | 8 <sup>12</sup>  | pF   |

| I <sub>DDDEEPSLEEP</sub> 13    | V <sub>DDINT</sub> Current in Deep<br>Sleep Mode                  |                                                                                                                                                                    |        | 22              |                     |      | 37              |                  | mA   |

| I <sub>DDSLEEP</sub>           | V <sub>DDINT</sub> Current in Sleep<br>Mode                       | $\begin{split} V_{DDINT} &= 1.0 \text{ V}, \\ f_{SCLK} &= 25 \text{ MHz}, \\ T_J &= 25^{\circ}\text{C} \end{split}$                                                |        | 35              |                     |      | 50              |                  | mA   |

| I <sub>DD-IDLE</sub>           | V <sub>DDINT</sub> Current in Idle                                | $V_{DDINT} = 1.0 V,$<br>$f_{CCLK} = 50 MHz,$<br>$T_{J} = 25^{\circ}C,$<br>ASF = 0.47                                                                               |        | 44              |                     |      | 59              |                  | mA   |

<sup>13</sup>See the ADSP-BF54x Blackfin Processor Hardware Reference Manual for definition of sleep, deep sleep, and hibernate operating modes.

<sup>14</sup>Includes current on V<sub>DDEXT</sub>, V<sub>DDUSB</sub>, V<sub>DDVR</sub>, and V<sub>DDDDR</sub> supplies. Clock inputs are tied high or low.

<sup>15</sup>Guaranteed maximum specifications.

Total power dissipation has two components:

- Static, including leakage current

- Dynamic, due to transistor switching characteristics

Many operating conditions can also affect power dissipation, including temperature, voltage, operating frequency, and processor activity. Electrical Characteristics on Page 36 shows the current dissipation for internal circuitry ( $V_{DDINT}$ ). I<sub>DDDEEPSLEEP</sub> specifies static power dissipation as a function of voltage ( $V_{DDINT}$ ) and temperature (see Table 16 and Table 17), and

$I_{DDINT}$  specifies the total power specification for the listed test conditions, including the dynamic component as a function of voltage ( $V_{DDINT}$ ) and frequency (Table 19).

There are two parts to the dynamic component. The first part is due to transistor switching in the core clock (CCLK) domain. This part is subject to an activity scaling factor (ASF) which represents application code running on the processor core and L1/L2 memories (Table 18). The ASF is combined with the CCLK frequency and  $V_{DDINT}$  dependent data in Table 19 to calculate this part. The second part is due to transistor switching in the system clock (SCLK) domain, which is included in the I<sub>DDINT</sub> specification equation.

Table 16. Static Current—Low Power Process (mA)<sup>1</sup>

|                              |        |        |        |        |        | Vo     | ltage (V <sub>D</sub> | DINT) <sup>2</sup> |        |        |        |        |        |

|------------------------------|--------|--------|--------|--------|--------|--------|-----------------------|--------------------|--------|--------|--------|--------|--------|

| ° <b>C</b> ) <sup>2</sup> رT | 0.90 V | 0.95 V | 1.00 V | 1.05 V | 1.10 V | 1.15 V | 1.20 V                | 1.25 V             | 1.30 V | 1.35 V | 1.38 V | 1.40 V | 1.43 V |

| -40                          | 11.9   | 13.5   | 15.5   | 17.7   | 20.3   | 23.3   | 26.8                  | 30.6               | 35.0   | 39.9   | 43.2   | 45.5   | 49.5   |

| 0                            | 20.1   | 22.3   | 24.7   | 27.8   | 31.1   | 34.9   | 39.3                  | 44.2               | 49.6   | 55.7   | 59.8   | 62.5   | 67.2   |

| 25                           | 31.2   | 34.2   | 37.5   | 41.3   | 45.6   | 50.3   | 55.7                  | 61.7               | 68.2   | 75.4   | 80.3   | 83.6   | 88.6   |

| 45                           | 47.0   | 51.0   | 55.5   | 60.6   | 66.0   | 72.0   | 78.8                  | 86.1               | 94.2   | 102.9  | 108.9  | 112.8  | 118.2  |

| 55                           | 58.6   | 63.1   | 68.3   | 74.1   | 80.3   | 87.1   | 94.9                  | 103.0              | 112.0  | 122.0  | 128.4  | 132.8  | 140.0  |

| 70                           | 80.7   | 86.6   | 93.0   | 100.2  | 108.1  | 116.7  | 125.9                 | 136.0              | 146.8  | 158.7  | 166.4  | 171.6  | 179.5  |

| 85                           | 107.0  | 114.3  | 122.5  | 131.5  | 141.2  | 151.7  | 163.1                 | 175.3              | 188.5  | 202.7  | 211.8  | 218.0  | 226.7  |

| 100                          | 153.9  | 163.0  | 173.3  | 184.8  | 197.0  | 210.0  | 224.1                 | 239.0              | 255.1  | 272.4  | 283.4  | 290.8  | 300.6  |

| 105                          | 171.7  | 181.5  | 192.7  | 205.1  | 218.3  | 232.4  | 247.5                 | 263.6              | 280.9  | 299.3  | 308.7  | 314.9  | 325.7  |

| 115                          | 210.1  | 221.4  | 234.2  | 248.6  | 263.7  | 279.9  | 297.3                 | 311.0              | 331.1  | 352.5  | 366.3  | N/A    | N/A    |

| 125                          | 257.9  | 270.9  | 285.9  | 302.5  | 314.6  | 334.0  | 354.3                 | 375.7              | 399.2  | 423.8  | 439.6  | N/A    | N/A    |

<sup>1</sup>Values are guaranteed maximum I<sub>DDDEEPSLEEP</sub> for 400 MHz speed-grade devices.

<sup>2</sup>Valid temperature and voltage ranges are model-specific. See Operating Conditions on Page 34.

Table 17. Static Current—Automotive 400 MHz and All 533 MHz/600 MHz Speed Grade Devices (mA)<sup>1</sup>

|                                  |        | Voltage (V <sub>DDINT</sub> ) <sup>2</sup> |        |        |        |        |        |        |        |        |        |        |        |

|----------------------------------|--------|--------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Τ <sub>J</sub> (°C) <sup>2</sup> | 0.90 V | 0.95 V                                     | 1.00 V | 1.05 V | 1.10 V | 1.15 V | 1.20 V | 1.25 V | 1.30 V | 1.35 V | 1.38 V | 1.40 V | 1.43 V |

| -40                              | 19.7   | 22.1                                       | 24.8   | 27.9   | 31.4   | 35.4   | 39.9   | 45.0   | 50.6   | 57.0   | 61.2   | 64.0   | 70.4   |

| 0                                | 45.2   | 49.9                                       | 55.2   | 61.3   | 67.9   | 75.3   | 83.5   | 92.6   | 102.6  | 113.6  | 121.0  | 125.8  | 135.0  |

| 25                               | 80.0   | 87.5                                       | 96.2   | 105.8  | 116.4  | 127.9  | 140.4  | 154.1  | 169.2  | 185.4  | 196.1  | 203.3  | 218.0  |

| 45                               | 124.2  | 134.8                                      | 147.1  | 160.7  | 175.3  | 191.2  | 208.6  | 227.3  | 247.6  | 269.6  | 284.0  | 293.6  | 312.0  |

| 55                               | 154.6  | 167.2                                      | 181.7  | 197.7  | 214.9  | 233.8  | 254.2  | 276.1  | 299.7  | 325.9  | 343.1  | 354.6  | 374.0  |

| 70                               | 209.8  | 225.6                                      | 243.9  | 264.1  | 285.8  | 309.4  | 334.8  | 363.5  | 394.3  | 427.7  | 449.4  | 463.9  | 489.0  |

| 85                               | 281.8  | 301.3                                      | 323.5  | 350.2  | 378.5  | 408.9  | 442.1  | 477.9  | 516.5  | 557.5  | 584.2  | 602.0  | 629.0  |

| 100                              | 366.5  | 390.5                                      | 419.4  | 452.1  | 486.9  | 524.4  | 564.8  | 608.2  | 654.8  | 704.7  | 737.0  | 758.5  | 793.0  |

| 105                              | 403.8  | 428.3                                      | 459.5  | 494.3  | 531.7  | 571.9  | 614.9  | 661.5  | 711.1  | 763.9  | 798.5  | 821.6  | 864.0  |

<sup>1</sup>Values are guaranteed maximum I<sub>DDDEEPSLEEP</sub> for automotive 400 MHz and all 533 MHz and 600 MHz speed grade devices.

<sup>2</sup>Valid temperature and voltage ranges are model-specific. See Operating Conditions on Page 34.

<sup>&</sup>lt;sup>16</sup>Unit for V<sub>DDINT</sub> is V (volts). Unit for  $f_{SCLK}$  is MHz. Example: 1.2 V, 133 MHz would be  $0.77 \times 1.2 \times 133 = 122.9$  mA added to  $I_{DDDEEPSLEEP}$ . <sup>17</sup>See Table 18 for the list of  $I_{DDINT}$  power vectors covered.

| IDDINT Power Vector  | Activity Scaling Factor (ASF) |

|----------------------|-------------------------------|

| I <sub>DD-PEAK</sub> | 1.29                          |

| I <sub>DD-HIGH</sub> | 1.24                          |

| I <sub>DD-TYP</sub>  | 1.00                          |

| I <sub>DD-APP</sub>  | 0.87                          |

| I <sub>DD-NOP</sub>  | 0.74                          |

| I <sub>DD-IDLE</sub> | 0.47                          |

#### Table 18. Activity Scaling Factors<sup>1</sup>

<sup>1</sup>See Estimating Power for ADSP-BF534/BF536/BF537 Blackfin Processors (*EE-297*). The power vector information also applies to the ADSP-BF542/ADSP-BF544/ADSP-BF547/ADSP-BF548/ADSP-BF549 processors.

#### Table 19. Dynamic Current in CCLK Domain (mA, with ASF = 1.0)<sup>1</sup>

|                                         |        | Voltage (V <sub>DDINT</sub> ) <sup>2</sup> |        |        |        |        |        |        |        |        |        |        |        |

|-----------------------------------------|--------|--------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| f <sub>ccLK</sub><br>(MHz) <sup>2</sup> | 0.90 V | 0.95 V                                     | 1.00 V | 1.05 V | 1.10 V | 1.15 V | 1.20 V | 1.25 V | 1.30 V | 1.35 V | 1.38 V | 1.40 V | 1.43 V |

| 100                                     | 29.7   | 31.6                                       | 33.9   | 35.7   | 37.9   | 40.5   | 42.9   | 45.5   | 48.2   | 50.8   | 52.0   | 53.5   | 54.6   |

| 200                                     | 55.3   | 58.9                                       | 62.5   | 66.0   | 70.0   | 74.0   | 78.3   | 82.5   | 86.7   | 91.3   | 93.3   | 95.6   | 97.6   |

| 300                                     | 80.8   | 85.8                                       | 91.0   | 96.0   | 101.3  | 107.0  | 112.8  | 118.7  | 124.6  | 130.9  | 133.8  | 137.0  | 140.0  |

| 400                                     | N/A    | 112.2                                      | 119.4  | 125.5  | 132.4  | 139.6  | 146.9  | 154.6  | 162.3  | 170.0  | 173.8  | 177.8  | 181.6  |

| 500                                     | N/A    | N/A                                        | N/A    | N/A    | N/A    | 171.9  | 180.6  | 189.9  | 199.1  | 205.7  | 210.3  | 213.0  | 217.6  |

| 533                                     | N/A    | N/A                                        | N/A    | N/A    | N/A    | N/A    | 191.9  | 201.6  | 211.5  | 218.0  | 222.8  | 225.7  | 230.5  |

| 600                                     | N/A    | N/A                                        | N/A    | N/A    | N/A    | N/A    | N/A    | N/A    | 233.1  | 241.4  | 246.7  | 252.7  | 258.1  |

<sup>1</sup> The values are not guaranteed as stand-alone maximum specifications. They must be combined with static current per the equations of Electrical Characteristics on Page 36. <sup>2</sup>Valid frequency and voltage ranges are model-specific. See Operating Conditions on Page 34.

### **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed in Table 20 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Table 21 details the maximum duty cycle for input transient voltage.

#### Table 20. Absolute Maximum Ratings

| Internal (Core) Supply Voltage (V <sub>DDINT</sub> )                 | –0.3 V to +1.43 V                                  |

|----------------------------------------------------------------------|----------------------------------------------------|

| External (I/O) Supply Voltage (V <sub>DDEXT</sub> )                  | –0.3 V to +3.8 V                                   |

| Input Voltage <sup>1, 2, 3</sup>                                     | –0.5 V to +3.6 V                                   |

| Output Voltage Swing                                                 | –0.5 V to V <sub>DDEXT</sub> +0.5 V<br>40 mA (max) |

| I <sub>OH</sub> /I <sub>OL</sub> Current per Single Pin <sup>4</sup> | 40 mA (max)                                        |

| I <sub>OH</sub> /I <sub>OL</sub> Current per Pin Group <sup>4</sup>  | 80 mA (max)                                        |

| Storage Temperature Range                                            | –65°C to +150°C                                    |

| Junction Temperature Underbias                                       | +125°C                                             |

<sup>1</sup>Applies to all bidirectional and input only pins except PB1-0, PE15-14, PG15-11, and PH7-6, where the absolute maximum input voltage range is -0.5 V to +5.5 V.

$^2$  Pins USB\_DP, USB\_DM, and USB\_VBUS are 5 V-tolerant when VDDUSB is powered according to the operating conditions table. If VDDUSB supply voltage does not meet the specification in the operating conditions table, these pins could suffer long-term damage when driven to +5 V. If this condition is seen in the application, it can be corrected with additional circuitry to use the external host to power only the V<sub>DDUSB</sub> pins. Contact factory for application detail and reliability information.

$^3Applies only when V_{DDEXT}$  is within specifications. When  $V_{DDEXT}$  is outside specifications, the range is  $V_{DDEXT}\pm0.2~V.$

<sup>4</sup>For more information, see description preceding Table 22.

### Table 21. Maximum Duty Cycle for Input<sup>1</sup> Transient Voltage

| V <sub>IN</sub> Max (V) <sup>2</sup> | V <sub>IN</sub> Min (V) | Maximum Duty Cycle |

|--------------------------------------|-------------------------|--------------------|

| 3.63                                 | -0.33                   | 100%               |

| 3.80                                 | -0.50                   | 48%                |

| 3.90                                 | -0.60                   | 30%                |

| 4.00                                 | -0.70                   | 20%                |

| 4.10                                 | -0.80                   | 10%                |

| 4.20                                 | -0.90                   | 8%                 |

| 4.30                                 | -1.00                   | 5%                 |

<sup>1</sup> Does not apply to CLKIN. Absolute maximum for pins PB1-0, PE15-14, PG15-11, and PH7-6 is +5.5V.

<sup>2</sup> Only one of the listed options can apply to a particular design.

The Absolute Maximum Ratings table specifies the maximum total source/sink ( $I_{OH}/I_{OL}$ ) current for a group of pins. Permanent damage can occur if this value is exceeded. To understand this specification, if pins PA4, PA3, PA2, PA1 and PA0 from group 1 in the Total Current Pin Groups table were sourcing or sinking 2 mA each, the total current for those pins would be 10 mA. This would allow up to 70 mA total that could be sourced or sunk by the remaining pins in the group without damaging the device. For a list of all groups and their pins, see

the Total Current Pin Groups table. Note that the  $V_{OL}$  and  $V_{OH}$  specifications have separate per-pin maximum current requirements, see the Electrical Characteristics table.

|  | Table 22. | Total | Current | Pin | Groups |  |

|--|-----------|-------|---------|-----|--------|--|

|--|-----------|-------|---------|-----|--------|--|

| Group | Pins in Group                                                             |

|-------|---------------------------------------------------------------------------|

| 1     | PA0, PA1, PA2, PA3, PA4, PA5, PA6, PA7, PA8, PA9, PA10,<br>PA11           |

| 2     | PA12, PA13, PA14, PA15, PB8, PB9, PB10, PB11, PB12,<br>PB13, PB14         |

| 3     | PB0, PB1, PB2, PB3, PB4, PB5, PB6, PB7, BMODE0,<br>BMODE1, BMODE2, BMODE3 |

| 4     | TCK, TDI, TDO, TMS, TRST, PD14, EMU                                       |

| 5     | PD8, PD9, PD10, PD11, PD12, PD13, PD15                                    |

| 6     | PD0, PD1, PD2, PD3, PD4, PD5, PD6, PD7                                    |

| 7     | PE11, PE12, PE13, PF12, PF13, PF14, PF15, PG3, PG4                        |

| 8     | PF4, PF5, PF6, PF7, PF8, PF9, PF10, PF11                                  |

| 9     | PF0, PF1, PF2, PF3, PG0, PG1, PG2                                         |

| 10    | PC0, PC1, PC2, PC3, PC4, PC5, PC6, PC7                                    |

| 11    | PH5, PH6, PH7                                                             |

| 12    | A1, A2, A3                                                                |

| 13    | PH8, PH9, PH10, PH11, PH12, PH13                                          |

| 14    | PIO, PI1, PI2, PI3, PI4, PI5, PI6, PI7                                    |

| 15    | PI8, PI9, PI10, PI11, PI12, PI13, PI14, PI15                              |

| 16    | AMS0, AMS1, AMS2, AMS3, AOE, CLKBUF, NMI                                  |

| 17    | CLKIN, XTAL, RESET, RTXI, RTXO, ARE, AWE                                  |

| 18    | D0, D1, D2, D3, D4, D5, D6, D7                                            |

| 19    | D8, D9, D10, D11, D12                                                     |

| 20    | D13, D14, D15, ABE0, ABE1                                                 |

| 21    | EXT_WAKE, CLKOUT, PJ11, PJ12, PJ13                                        |

| 22    | PJ0, PJ1, PJ2, PJ3, PJ4, PJ5, PJ6, PJ7, ATAPI_PDIAG                       |

| 23    | PJ8, PJ9, PJ10, PE7, PG12, PG13                                           |

| 24    | PE0, PE1, PE2, PE4, PE5, PE6, PE8, PE9, PE10, PH3, PH4                    |

| 25    | PH0, PH2, PE14, PE15, PG5, PG6, PG7, PG8, PG9, PG10, PG11                 |

| 26    | PC8, PC9, PC10, PC11, PC12, PC13, PE3, PG14, PG15, PH1                    |

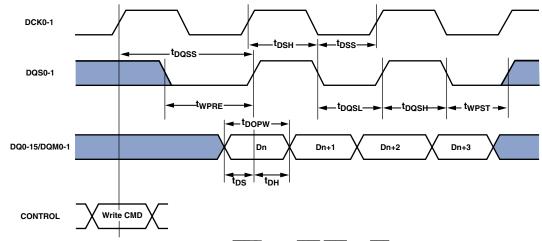

#### DDR SDRAM/Mobile DDR SDRAM Write Cycle Timing

Table 33 and Figure 20 describe DDR SDRAM/mobile DDRSDRAM write cycle timing.

#### Table 33. DDR SDRAM/Mobile DDR SDRAM Write Cycle Timing

|                   |                                                 | DDR SDRA | M    | Mobile DD | R SDRAM |                 |

|-------------------|-------------------------------------------------|----------|------|-----------|---------|-----------------|

| Parameter         |                                                 | Min      | Max  | Min       | Max     | Unit            |

| Switching         | g Characteristics                               |          |      |           |         |                 |

| t <sub>DQSS</sub> | Write CMD to First DQS0-1                       | 0.75     | 1.25 | 0.75      | 1.25    | t <sub>CK</sub> |

| t <sub>DS</sub>   | DQ0-15/DQM0-1 Setup to DQS0-1                   | 0.90     |      | 0.90      |         | ns              |

| t <sub>DH</sub>   | DQ0-15/DQM0-1 Hold to DQS0-1                    | 0.90     |      | 0.90      |         | ns              |

| t <sub>DSS</sub>  | DQS0-1 Falling to DCK0-1 Rising (DQS0-1 Setup)  | 0.20     |      | 0.20      |         | t <sub>CK</sub> |

| t <sub>DSH</sub>  | DQS0-1 Falling from DCK0-1 Rising (DQS0-1 Hold) | 0.20     |      | 0.20      |         | t <sub>CK</sub> |

| t <sub>DQSH</sub> | DQS0-1 High Pulse Width                         | 0.35     |      | 0.40      | 0.60    | t <sub>CK</sub> |

| t <sub>DQSL</sub> | DQS0-1 Low Pulse Width                          | 0.35     |      | 0.40      | 0.60    | t <sub>CK</sub> |

| t <sub>WPRE</sub> | DQS0-1 Write Preamble                           | 0.25     |      | 0.25      |         | t <sub>CK</sub> |

| t <sub>WPST</sub> | DQS0-1 Write Postamble                          | 0.40     | 0.60 | 0.40      | 0.60    | t <sub>CK</sub> |

| t <sub>DOPW</sub> | DQ0-15 and DQM0-1 Output Pulse Width (for Each) | 1.75     |      | 1.75      |         | ns              |

NOTE: CONTROL = DCS0-1, DCLKE, DRAS, DCAS, AND DWE.

Figure 20. DDR SDRAM / Mobile DDR SDRAM Controller Write Cycle Timing

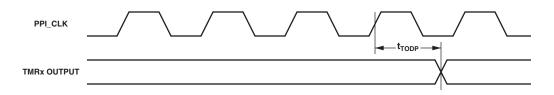

#### **Timer Clock Timing**

Table 47 and Figure 41 describe timer clock timing.

#### Table 47. Timer Clock Timing

| Parameter         |                                              | Min | Max | Unit |

|-------------------|----------------------------------------------|-----|-----|------|

| Switching C       | Tharacteristic                               |     |     |      |

| t <sub>TODP</sub> | Timer Output Update Delay After PPI_CLK High |     | 15  | ns   |

Figure 41. Timer Clock Timing

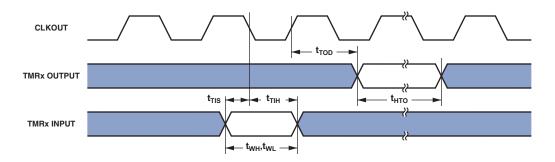

#### **Timer Cycle Timing**

Table 48 and Figure 42 describe timer expired operations. The input signal is asynchronous in "width capture mode" and "external clock mode" and has an absolute maximum input frequency of ( $f_{SCLK}/2$ ) MHz.

#### Table 48. Timer Cycle Timing

| Parameter        | r                                                     | Min                 | Мах                            | Unit |

|------------------|-------------------------------------------------------|---------------------|--------------------------------|------|

| Timing Cha       | aracteristics                                         |                     |                                |      |

| t <sub>WL</sub>  | Timer Pulse Width Input Low <sup>1</sup>              | $1 \times t_{SCLK}$ |                                | ns   |

| t <sub>WH</sub>  | Timer Pulse Width Input High <sup>1</sup>             | $1 \times t_{SCLK}$ |                                | ns   |

| t <sub>TIS</sub> | Timer Input Setup Time Before CLKOUT Low <sup>2</sup> | 6.5                 |                                | ns   |

| t <sub>TIH</sub> | Timer Input Hold Time After CLKOUT Low <sup>2</sup>   | -1                  |                                | ns   |

| Switching (      | Characteristics                                       |                     |                                |      |

| t <sub>HTO</sub> | Timer Pulse Width Output                              | $1 \times t_{SCLK}$ | $(2^{32} - 1) \times t_{SCLK}$ | ns   |

| t <sub>TOD</sub> | Timer Output Delay After CLKOUT High                  |                     | 6                              | ns   |

<sup>1</sup>The minimum pulse widths apply for TMRx signals in width capture and external clock modes.

<sup>2</sup> Either a valid setup and hold time or a valid pulse width is sufficient. There is no need to resynchronize timer flag inputs.

Figure 42. Timer Cycle Timing

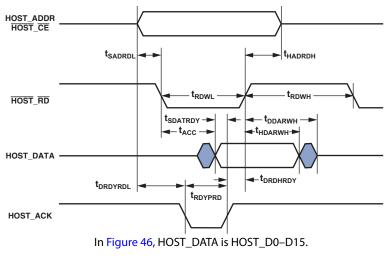

#### HOSTDP A/C Timing-Host Read Cycle

Table 54 and Figure 46 describe the HOSTDP A/C host read cycle timing requirements.

#### Table 54. Host Read Cycle Timing Requirements

| Paramet              | ter                                                              | Min                                      | Max                   | Unit |

|----------------------|------------------------------------------------------------------|------------------------------------------|-----------------------|------|

| Timing R             | equirements                                                      |                                          |                       |      |

| t <sub>SADRDL</sub>  | HOST_ADDR and HOST_CE Setup Before HOST_RD Falling Edge          | 4                                        |                       | ns   |

| t <sub>HADRDH</sub>  | HOST_ADDR and HOST_CE Hold After HOST_RD Rising Edge             | 2.5                                      |                       | ns   |

| t <sub>RDWL</sub>    | HOST_RD Pulse Width Low (ACK Mode)                               | $t_{DRDYRDL} + t_{RDYPRD} + t_{DRDHRDY}$ | (                     | ns   |

|                      | HOST_RD Pulse Width Low (INT Mode)                               | 1.5 × t <sub>SCLK</sub> + 8.7            |                       | ns   |

| t <sub>RDWH</sub>    | HOST_RD Pulse Width High or Time Between HOST_RD Rising Edge and | $2 \times t_{SCLK}$                      |                       | ns   |

|                      | HOST_WR Falling Edge                                             |                                          |                       |      |

| t <sub>DRDHRDY</sub> | HOST_RD Rising Edge Delay After HOST_ACK Rising Edge (ACK Mode)  | 0                                        |                       | ns   |

| Switching            | g Characteristics                                                |                                          |                       |      |

| t <sub>sdatrdy</sub> | HOST_D15–0 Valid Prior HOST_ACK Rising Edge (ACK Mode)           | t <sub>SCLK</sub> – 4.0                  |                       | ns   |

| t <sub>DRDYRDL</sub> | HOST_ACK Falling Edge After HOST_CE (ACK Mode)                   |                                          | 11.25                 | ns   |

| t <sub>RDYPRD</sub>  | HOST_ACK Low Pulse-Width for Read Access (ACK Mode)              |                                          | NM <sup>1</sup>       | ns   |

| t <sub>DDARWH</sub>  | HOST_D15-0 Disable After HOST_RD                                 |                                          | 8.0                   | ns   |

| t <sub>ACC</sub>     | HOST_D15–0 Valid After HOST_RD Falling Edge (INT Mode)           |                                          | $1.5 \times t_{SCLK}$ | ns   |

| t <sub>HDARWH</sub>  | HOST_D15–0 Hold After HOST_RD Rising Edge                        | 1.0                                      |                       | ns   |

<sup>1</sup>NM (Not Measured) — This parameter is based on t<sub>SCLK</sub>. It is not measured because the number of SCLK cycles for which HOST\_ACK remains low depends on the Host DMA FIFO status. This is system design dependent.

Figure 46. HOSTDP A/C—Host Read Cycle

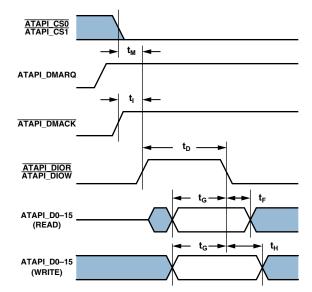

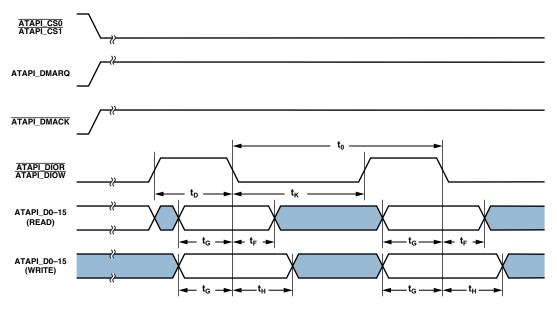

Note that in Figure 49 an alternate ATAPI\_D0–15 port bus is ATAPI\_D0–15A.

Figure 49. Initiating a Multiword DMA Data Burst

Figure 50. Sustained Multiword DMA Data Burst

#### **TEST CONDITIONS**

All timing parameters appearing in this data sheet were measured under the conditions described in this section. Figure 72 shows the measurement point for AC measurements (except output enable/disable). The measurement point  $V_{\text{MEAS}}$  is  $V_{\text{DDEXT}}/2$  or  $V_{\text{DDDDR}}/2$ , depending on the pin under test.

Figure 72. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable)

#### **Output Enable Time**

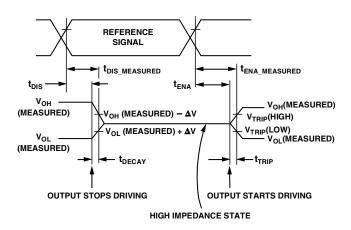

Output pins are considered to be enabled when they have made a transition from a high-impedance state to the point when they start driving. The output enable time  $t_{ENA}$  is the interval from the point when a reference signal reaches a high or low voltage level to the point when the output starts driving as shown in the output enable/disable diagram (Figure 73). The time,  $t_{ENA\_MEA}$ . SURED, is the interval from the point when the reference signal switches to the point when the output voltage reaches either 1.75 V (output high) or 1.25 V (output low). Time  $t_{TRIP}$  is the interval from when the output starts driving to when the output reaches the 1.25 V or 1.75 V trip voltage. Time  $t_{ENA}$  is calculated as shown in the equation:

$$t_{ENA} = t_{ENA\_MEASURED} - t_{TRIP}$$

If multiple pins (such as the data bus) are enabled, the measurement value is that of the first pin to start driving.

### **Output Disable Time**

Output pins are considered to be disabled when they stop driving, go into a high-impedance state, and start to decay from their output high or low voltage. The time for the voltage on the bus to decay by  $\Delta V$  is dependent on the capacitive load,  $C_L$  and the load current,  $I_L$ . This decay time can be approximated by the equation:

$$t_{DECAY} = (C_L \Delta V) / I_L$$

The output disable time  $t_{DIS}$  is the difference between  $t_{DIS\_MEA}$ . <sub>SURED</sub> and  $t_{DECAY}$  as shown in Figure 73. The time  $t_{DIS\_MEASURED}$  is the interval from when the reference signal switches to when the output voltage decays  $\Delta V$  from the measured output high or output low voltage. The time  $t_{DECAY}$  is calculated with test loads  $C_L$  and  $I_L$ , and with  $\Delta V$  equal to 0.25 V.

Figure 73. Output Enable/Disable

#### **Example System Hold Time Calculation**

To determine the data output hold time in a particular system, first calculate  $t_{DECAY}$  using the equation given above. Choose  $\Delta V$  to be the difference between the ADSP-BF54x Blackfin processors' output voltage and the input threshold for the device requiring the hold time. A typical  $\Delta V$  will be 0.4 V.  $C_L$  is the total bus capacitance (per data line), and  $I_L$  is the total leakage or three-state current (per data line). The hold time will be  $t_{DECAY}$  plus the minimum disable time (for example,  $t_{DDAT}$  for an asynchronous memory write cycle).

### **CAPACITIVE LOADING**

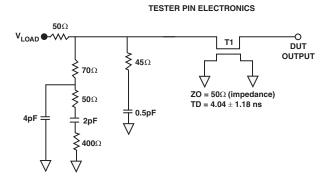

Output delays and holds are based on standard capacitive loads of an average of 6 pF on all balls (see Figure 74).

$V_{\text{LOAD}}$  is equal to  $V_{\text{DDEXT}}/2$  or  $V_{\text{DDDDR}}/2,$  depending on the pin under test.

NOTES:

THE WORST-CASE TRANSMISSION LINE DELAY IS SHOWN AND CAN BE USED FOR THE OUTPUT TIMING ANALYSIS TO REFELECT THE TRANSMISSION LINE EFFECT AND MUST BE CONSIDERED. THE TRANSMISSION LINE (TD), IS FOR LOAD ONLY AND DOES NOT AFFECT THE DATA SHEET TIMING SPECIFICATIONS.

ANALOG DEVICES RECOMMENDS USING THE IBIS MODEL TIMING FOR A GIVEN SYSTEM REQUIREMENT. IF NECESSARY, A SYSTEM MAY INCORPORATE EXTERNAL DRIVERS TO COMPENSATE FOR ANY TIMING DIFFERENCES.

Figure 74. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

#### **TYPICAL RISE AND FALL TIMES**

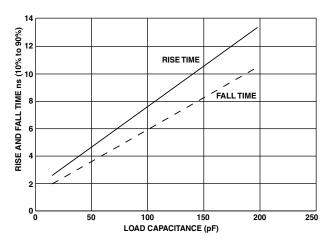

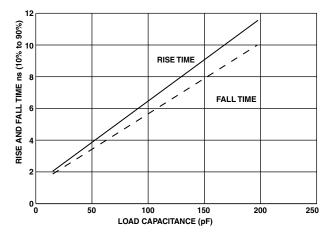

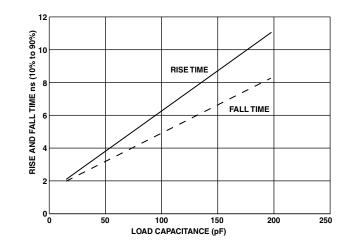

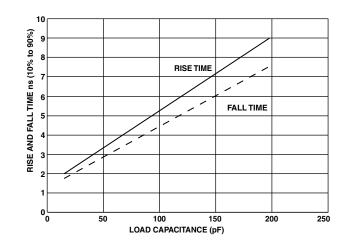

Figure 75 through Figure 86 on Page 93 show how output rise time varies with capacitance. The delay and hold specifications given should be derated by a factor derived from these figures. The graphs in these figures may not be linear outside the ranges shown.

Figure 75. Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance for Driver A at V<sub>DDEXT</sub> = 2.25 V

Figure 76. Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance for Driver A at V<sub>DDEXT</sub> = 3.65 V

Figure 77. Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance for Driver B at V<sub>DDEXT</sub> = 2.25 V

Figure 78. Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance for Driver B at V<sub>DDEXT</sub> = 3.65 V

| Signal             | Ball No. |

|--------------------|----------|--------------------|----------|--------------------|----------|--------------------|----------|

| ТСК                | V3       | V <sub>DDDDR</sub> | J14      | V <sub>DDEXT</sub> | N5       | V <sub>DDINT</sub> | G13      |

| TDI                | V5       | V <sub>DDDDR</sub> | J15      | V <sub>DDEXT</sub> | N15      | V <sub>DDINT</sub> | J6       |

| TDO                | V4       | V <sub>DDDDR</sub> | K14      | V <sub>DDEXT</sub> | P15      | V <sub>DDINT</sub> | J13      |

| TMS                | U5       | V <sub>DDDDR</sub> | K15      | V <sub>DDEXT</sub> | R6       | V <sub>DDINT</sub> | L6       |

| TRST               | T5       | V <sub>DDEXT</sub> | E5       | V <sub>DDEXT</sub> | R7       | V <sub>DDINT</sub> | L15      |

| USB_DM             | E2       | V <sub>DDEXT</sub> | E9       | V <sub>DDEXT</sub> | R8       | V <sub>DDINT</sub> | P6       |

| USB_DP             | E1       | V <sub>DDEXT</sub> | E10      | V <sub>DDEXT</sub> | R15      | V <sub>DDINT</sub> | P7       |

| USB_ID             | G3       | V <sub>DDEXT</sub> | E11      | V <sub>DDEXT</sub> | T7       | V <sub>DDINT</sub> | P14      |

| USB_RSET           | D3       | V <sub>DDEXT</sub> | E12      | V <sub>DDEXT</sub> | T8       | V <sub>DDINT</sub> | R10      |

| USB_VBUS           | D2       | V <sub>DDEXT</sub> | F7       | V <sub>DDEXT</sub> | Т9       | V <sub>DDINT</sub> | R11      |

| USB_VREF           | B1       | V <sub>DDEXT</sub> | F8       | V <sub>DDEXT</sub> | T10      | V <sub>DDINT</sub> | R12      |

| USB_XI             | F1       | V <sub>DDEXT</sub> | F13      | V <sub>DDEXT</sub> | T11      | V <sub>DDINT</sub> | U9       |

| USB_XO             | F2       | V <sub>DDEXT</sub> | G5       | V <sub>DDEXT</sub> | T12      | V <sub>DDMP</sub>  | E8       |

| V <sub>DDDDR</sub> | F10      | V <sub>DDEXT</sub> | G6       | V <sub>DDEXT</sub> | T13      | V <sub>DDRTC</sub> | E13      |

| V <sub>DDDDR</sub> | F11      | V <sub>DDEXT</sub> | G7       | V <sub>DDEXT</sub> | T14      | V <sub>DDUSB</sub> | F5       |

| V <sub>DDDDR</sub> | F12      | V <sub>DDEXT</sub> | G14      | V <sub>DDEXT</sub> | T15      | V <sub>DDUSB</sub> | G4       |

| V <sub>DDDDR</sub> | G15      | V <sub>DDEXT</sub> | H5       | V <sub>DDEXT</sub> | T16      | V <sub>DDVR</sub>  | F15      |

| V <sub>DDDDR</sub> | H13      | V <sub>DDEXT</sub> | H6       | V <sub>DDINT</sub> | F9       | VR <sub>OUT0</sub> | A18      |

| V <sub>DDDDR</sub> | H14      | V <sub>DDEXT</sub> | K6       | V <sub>DDINT</sub> | G8       | VR <sub>OUT1</sub> | A19      |

| V <sub>DDDDR</sub> | H15      | V <sub>DDEXT</sub> | M15      | V <sub>DDINT</sub> | G12      | XTAL               | A12      |

Table 65. 400-Ball CSP\_BGA Ball Assignment (Alphabetical by Signal) (Continued)

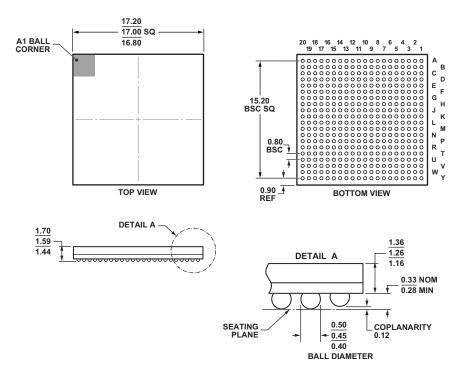

### **OUTLINE DIMENSIONS**

Dimensions for the 17 mm  $\times$  17 mm CSP\_BGA package in Figure 88 are shown in millimeters.

COMPLIANT TO JEDEC STANDARDS MO-275-MMAB-1.

Figure 88. 400-Ball, 17 mm × 17 mm CSP\_BGA (Chip Scale Package Ball Grid Array) (BC-400-1)

### SURFACE-MOUNT DESIGN

Table 67 is provided as an aid to PCB design. For industry-stan-dard design recommendations, refer to IPC-7351, GenericRequirements for Surface-Mount Design and Land PatternStandard.

#### Table 67. BGA Data for Use with Surface-Mount Design