Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

### Details

E·XFl

| Product Status          | Active                                                                |

|-------------------------|-----------------------------------------------------------------------|

| Туре                    | Fixed Point                                                           |

| Interface               | CAN, SPI, SSP, TWI, UART                                              |

| Clock Rate              | 533MHz                                                                |

| Non-Volatile Memory     | External                                                              |

| On-Chip RAM             | 196kB                                                                 |

| Voltage - I/O           | 2.50V, 3.30V                                                          |

| Voltage - Core          | 1.25V                                                                 |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                     |

| Mounting Type           | Surface Mount                                                         |

| Package / Case          | 400-LFBGA, CSPBGA                                                     |

| Supplier Device Package | 400-CSPBGA (17x17)                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf544bbcz-5a |

|                         |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The DDR memory controller can gluelessly manage up to two banks of double-rate synchronous dynamic memory (DDR and mobile DDR SDRAM). The 16-bit interface operates at the SCLK frequency, enabling a maximum throughput of 532M bytes/s. The DDR and mobile DDR controller is augmented with a queuing mechanism that performs efficient bursts into the DDR and mobile DDR. The controller is an industry standard DDR and mobile DDR SDRAM controller with each bank supporting from 64M bit to 512M bit device sizes and 4-, 8-, or 16-bit widths. The controller supports up to 256M bytes per external bank. With 2 external banks, the controller supports up to 512M bytes total. Each bank is independently programmable and is contiguous with adjacent banks regardless of the sizes of the different banks or their placement.

Traditional 16-bit asynchronous memories, such as SRAM, EPROM, and flash devices, can be connected to one of the four 64M byte asynchronous memory banks, represented by four memory select strobes. Alternatively, these strobes can function as bank-specific read or write strobes preventing further glue logic when connecting to asynchronous FIFO devices. See the Ordering Guide on Page 101 for a list of specific products that provide support for DDR memory.

In addition, the external bus can connect to advanced flash device technologies, such as:

- Page-mode NOR flash devices

- Synchronous burst-mode NOR flash devices

- NAND flash devices

Customers should consult the Ordering Guide when selecting a specific ADSP-BF54x component for the intended application. Products that provide support for mobile DDR memory are noted in the ordering guide footnotes.

### NAND Flash Controller (NFC)

The ADSP-BF54x Blackfin processors provide a NAND Flash Controller (NFC) as part of the external bus interface. NAND flash devices provide high-density, low-cost memory. However, NAND flash devices also have long random access times, invalid blocks, and lower reliability over device lifetimes. Because of this, NAND flash is often used for read-only code storage. In this case, all DSP code can be stored in NAND flash and then transferred to a faster memory (such as DDR or SRAM) before execution. Another common use of NAND flash is for storage of multimedia files or other large data segments. In this case, a software file system may be used to manage reading and writing of the NAND flash device. The file system selects memory segments for storage with the goal of avoiding bad blocks and equally distributing memory accesses across all address locations. Hardware features of the NFC include:

- Support for page program, page read, and block erase of NAND flash devices, with accesses aligned to page boundaries.

- Error checking and correction (ECC) hardware that facilitates error detection and correction.

- A single 8-bit or 16-bit external bus interface for commands, addresses, and data.

- Support for SLC (single level cell) NAND flash devices unlimited in size, with page sizes of 256 bytes and 512 bytes. Larger page sizes can be supported in software.

- The ability to release external bus interface pins during long accesses.

- Support for internal bus requests of 16 bits or 32 bits.

- A DMA engine to transfer data between internal memory and a NAND flash device.

### **One-Time-Programmable Memory**

The ADSP-BF54x Blackfin processors have 64K bits of onetime-programmable (OTP) non-volatile memory that can be programmed by the developer only one time. It includes the array and logic to support read access and programming. Additionally, its pages can be write protected.

OTP enables developers to store both public and private data on-chip. In addition to storing public and private key data for applications requiring security, it also allows developers to store completely user-definable data such as a customer ID, product ID, or a MAC address. By using this feature, generic parts can be shipped, which are then programmed and protected by the developer within this non-volatile memory. The OTP memory can be accessed through an API provided by the on-chip ROM.

### I/O Memory Space

The ADSP-BF54x Blackfin processors do not define a separate I/O space. All resources are mapped through the flat 32-bit address space. On-chip I/O devices have their control registers mapped into memory-mapped registers (MMRs) at addresses near the top of the 4G byte address space. These are separated into two smaller blocks, one containing the control MMRs for all core functions and the other containing the registers needed for setup and control of the on-chip peripherals outside of the core. The MMRs are accessible only in supervisor mode and appear as reserved space to on-chip peripherals.

### Booting

The ADSP-BF54x Blackfin processors contain a small on-chip boot kernel, which configures the appropriate peripheral for booting. If the ADSP-BF54x Blackfin processors are configured to boot from boot ROM memory space, the processor starts executing from the on-chip boot ROM. For more information, see Booting Modes on Page 18.

### **Event Handling**

The event controller on the ADSP-BF54x Blackfin processors handles all asynchronous and synchronous events to the processors. The ADSP-BF54x Blackfin processors provide event handling that supports both nesting and prioritization. Nesting allows multiple event service routines to be active simultaneously. Prioritization ensures that servicing of a higher-priority event takes precedence over servicing of a lower-priority event.

### Host DMA Port Interface

The host DMA port (HOSTDP) facilitates a host device external to the ADSP-BF54x Blackfin processors to be a DMA master and transfer data back and forth. The host device always masters the transactions, and the processor is always a DMA slave device.

The HOSTDP is enabled through the peripheral access bus. Once the port has been enabled, the transactions are controlled by the external host. The external host programs standard DMA configuration words in order to send/receive data to any valid internal or external memory location. The host DMA port controller includes the following features:

- Allows an external master to configure DMA read/write data transfers and read port status

- Uses a flexible asynchronous memory protocol for its external interface

- Allows an 8- or 16-bit external data interface to the host device

- Supports half-duplex operation

- · Supports little/big endian data transfers

- Acknowledge mode allows flow control on host transactions

- Interrupt mode guarantees a burst of FIFO depth host transactions

### **REAL-TIME CLOCK**

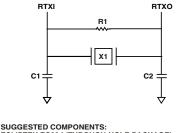

The ADSP-BF54x Blackfin processors' real-time clock (RTC) provides a robust set of digital watch features, including current time, stopwatch, and alarm. The RTC is clocked by a 32.768 kHz crystal external to the ADSP-BF54x Blackfin processors. The RTC peripheral has dedicated power supply pins so that it can remain powered up and clocked even when the rest of the processor is in a low-power state. The RTC provides several programmable interrupt options, including interrupt per second, minute, hour, or day clock ticks, interrupt on programmable stopwatch countdown, or interrupt at a programmed alarm time.

The 32.768 kHz input clock frequency is divided down to a 1 Hz signal by a prescaler. The counter function of the timer consists of four counters: a 60-second counter, a 60-minute counter, a 24-hour counter, and a 32,768-day counter.

When enabled, the alarm function generates an interrupt when the output of the timer matches the programmed value in the alarm control register. There are two alarms. The first alarm is for a time of day. The second alarm is for a day and time of that day.

The stopwatch function counts down from a programmed value with one-second resolution. When the stopwatch is enabled and the counter underflows, an interrupt is generated.

Like the other peripherals, the RTC can wake up the ADSP-BF54x processor from sleep mode upon generation of any RTC wakeup event. Additionally, an RTC wakeup event can wake up the ADSP-BF54x processors from deep sleep mode, and it can wake up the on-chip internal voltage regulator from the hibernate state.

Connect RTC pins RTXI and RTXO with external components as shown in Figure 4.

ECLIPTEK EC38J (THROUGH-HOLE PACKAGE) EPSON MC405 12 pF LOAD (SURFACE-MOUNT PACKAGE) C1 = 22 pF C2 = 22 pF R1 = 10 M $\Omega$ NOTE: C1 AND C2 ARE SPECIFIC TO CRYSTAL SPECIFIED FOR X1. CONTACT CRYSTAL MANUFACTURER FOR DETAILS. C1 AND C2 SPECIFICATIONS ASSUME BOARD TRACE CAPACITANCE OF 3 pF.

Figure 4. External Components for RTC

### WATCHDOG TIMER

The ADSP-BF54x processors include a 32-bit timer that can be used to implement a software watchdog function. A software watchdog can improve system reliability by forcing the processor to a known state through generation of a hardware reset, non-maskable interrupt (NMI), or general-purpose interrupt if the timer expires before being reset by software. The programmer initializes the count value of the timer, enables the appropriate interrupt, and then enables the timer. Thereafter, the software must reload the counter before it counts to zero from the programmed value. This protects the system from remaining in an unknown state where software, which would normally reset the timer, has stopped running due to an external noise condition or software error.

If configured to generate a hardware reset, the watchdog timer resets both the core and the ADSP-BF54x processors' peripherals. After a reset, software can determine if the watchdog was the source of the hardware reset by interrogating a status bit in the watchdog timer control register.

The timer is clocked by the system clock (SCLK) at a maximum frequency of  $\mathbf{f}_{\text{SCLK}}$

## TIMERS

There are up to two timer units in the ADSP-BF54x Blackfin processors. One unit provides eight general-purpose programmable timers, and the other unit provides three. Each timer has an external pin that can be configured either as a pulse width modulator (PWM) or timer output, as an input to clock the timer, or as a mechanism for measuring pulse widths and periods of external events. These timers can be synchronized to an external clock input on the TMRx pins, an external clock TMRCLK input pin, or to the internal SCLK.

- Boot from 16-bit asynchronous FIFO (BMODE = 0x2)—In this mode, the boot kernel starts booting from address 0x2030 0000. Every 16-bit word that the boot kernel has to read from the FIFO must be requested by a low pulse on the DMAR1 pin.

- Boot from serial SPI memory, EEPROM or flash (BMODE = 0x3)—8-, 16-, 24- or 32-bit addressable devices are supported. The processor uses the PE4 GPIO pin to select a single SPI EEPROM or flash device and uses SPI0 to submit a read command and successive address bytes (0x00) until a valid 8-, 16-, 24-, or 32-bit addressable device is detected. Pull-up resistors are required on the SPI0SEL1 and SPI0MISO pins. By default, a value of 0x85 is written to the SPI0\_BAUD register.

- Boot from SPI host device (BMODE = 0x4)—The processor operates in SPI slave mode (using SPI0) and is configured to receive the bytes of the .LDR file from an SPI host (master) agent. The HWAIT signal must be interrogated by the host before every transmitted byte. A pull-up resistor is required on the SPI0SS input. A pull-down resistor on the serial clock (SPI0SCK) may improve signal quality and booting robustness.

- Boot from serial TWI memory, EEPROM or flash (BMODE = 0x5)—The processor operates in master mode (using TWI0) and selects the TWI slave with the unique ID 0xA0. The processor submits successive read commands to the memory device starting at two-byte internal address 0x0000 and begins clocking data into the processor. The TWI memory device should comply with Philips I<sup>2</sup>C Bus Specification version 2.1 and have the capability to autoincrement its internal address counter such that the contents of the memory device can be read sequentially. By default, a prescale value of 0xA and CLKDIV value of 0x0811 is used. Unless altered by OTP settings, an I<sup>2</sup>C memory that takes two address bytes is assumed. Development tools ensure that data that is booted to memories that cannot be accessed by the Blackfin core is written to an intermediate storage place and then copied to the final destination via memory DMA.

- Boot from TWI host (BMODE = 0x6)—The TWI host agent selects the slave with the unique ID 0x5F. The processor (using TWI0) replies with an acknowledgement, and the host can then download the boot stream. The TWI host agent should comply with Philips I<sup>2</sup>C Bus Specification version 2.1. An I<sup>2</sup>C multiplexer can be used to select one processor at a time when booting multiple processors from a single TWI.

- Boot from UART host (BMODE = 0x7)—In this mode, the processor uses UART1 as the booting source. Using an autobaud handshake sequence, a boot-stream-formatted program is downloaded by the host. The host agent selects a bit rate within the UART's clocking capabilities.

When performing the autobaud, the UART expects an "@" (0x40) character (eight data bits, one start bit, one stop bit, no parity bit) on the UART1RX pin to determine the bit rate. It then replies with an acknowledgement, which is

composed of four bytes (0xBF, the value of UART1\_DLL, the value of UART1\_DLH, and finally 0x00). The host can then download the boot stream. The processor deasserts the UART1RTS output to hold off the host; UART1CTS functionality is not enabled at boot time.

- Boot from (DDR) SDRAM (BMODE = 0xA)—In this mode, the boot kernel starts booting from address 0x0000 0010. This is a warm boot scenario only. The SDRAM is expected to contain a valid boot stream and the SDRAM controller must have been configured by the OTP settings.

- Boot from 8-bit and 16-bit external NAND flash memory (BMODE = 0xD)—In this mode, auto detection of the NAND flash device is performed. The processor configures PORTJ GPIO pins PJ1 and PJ2 to enable the ND\_CE and ND\_RB signals, respectively. For correct device operation, pull-up resistors are required on both ND\_CE (PJ1) and ND\_RB (PJ2) signals. By default, a value of 0x0033 is written to the NFC\_CTL register. The booting procedure always starts by booting from byte 0 of block 0 of the NAND flash device. In this boot mode, the HWAIT signal does not toggle. The respective GPIO pin remains in the high-impedance state.

NAND flash boot supports the following features:

- Device auto detection

- Error detection and correction for maximum reliability

- No boot stream size limitation

- Peripheral DMA via channel 22, providing efficient transfer of all data (excluding the ECC parity data)

- Software-configurable boot mode for booting from boot streams expanding multiple blocks, including bad blocks

- Software-configurable boot mode for booting from multiple copies of the boot stream allowing for handling of bad blocks and uncorrectable errors

- Configurable timing via OTP memory

Small page NAND flash devices must have a 512-byte page size, 32 pages per block, a 16-byte spare area size and a bus configuration of eight bits. By default, all read requests from the NAND flash are followed by four address cycles. If the NAND flash device requires only three address cycles, then the device must be capable of ignoring the additional address cycle.

The small page NAND flash device must comply with the following command set:

| Reset: 0xFF                   |  |

|-------------------------------|--|

| Read lower half of page: 0x00 |  |

| Read upper half of page: 0x01 |  |

| Read spare area: 0x50         |  |

### Table 11. Pin Descriptions (Continued)

| Pin Name                                      | <b>I/O</b> <sup>1</sup> | Function (First/Second/Third/Fourth)                             | Driver<br>Type <sup>2</sup> |

|-----------------------------------------------|-------------------------|------------------------------------------------------------------|-----------------------------|

| Port C: GPIO/SPORT0/SD Controller/MXVR (MOST) |                         |                                                                  |                             |

| PC0/TFS0                                      | I/O                     | GPIO / SPORT0 Transmit Frame Sync                                | С                           |

| PC1/DT0SEC/MMCLK                              | I/O                     | GPIO/SPORT0 Transmit Data Secondary/MXVR Master Clock            | С                           |

| PC2/DT0PRI                                    | I/O                     | GPIO/SPORT0 Transmit Data Primary                                | С                           |

| PC3/TSCLK0                                    | I/O                     | GPIO/SPORT0 Transmit Serial Clock                                | А                           |

| PC4/RFS0                                      | I/O                     | GPIO/SPORT0 Receive Frame Sync                                   | С                           |

| PC5/DR0SEC/MBCLK                              | I/O                     | GPIO/SPORT0 Receive Data Secondary/MXVR Bit Clock                | С                           |

| PC6/DR0PRI                                    | I/O                     | GPIO / SPORT0 Receive Data Primary                               | С                           |

| PC7/RSCLK0                                    | I/O                     | GPIO/SPORT0 Receive Serial Clock                                 | С                           |

| PC8/SD_D0                                     | I/O                     | GPIO/SD Data Bus                                                 | А                           |

| PC9/SD_D1                                     | I/O                     | GPIO/SD Data Bus                                                 | А                           |

| PC10/SD_D2                                    | I/O                     | GPIO/SD Data Bus                                                 | А                           |

| PC11/SD_D3                                    | I/O                     | GPIO/SD Data Bus                                                 | А                           |

| PC12/SD_CLK                                   | I/O                     | GPIO/SD Clock Output                                             | А                           |

| PC13/SD_CMD                                   | I/O                     | GPIO/SD Command                                                  | А                           |

| Port D: GPIO/PPI0-2/SPORT 1/Keypad/Host DMA   |                         |                                                                  |                             |

| PD0/PPI1_D0/HOST_D8/TFS1/PPI0_D18             | I/O                     | GPIO/PPI1 Data/Host DMA/SPORT1 Transmit Frame Sync/PPI0 Data     | С                           |

| PD1/PPI1_D1/HOST_D9/DT1SEC/PPI0_D19           | I/O                     | GPIO/PPI1 Data/Host DMA/SPORT1 Transmit Data Secondary/PPI0 Data | C                           |

| PD2/PPI1_D2/HOST_D10/DT1PRI/PPI0_D20          | I/O                     | GPIO/PPI1 Data/Host DMA/SPORT1 Transmit Data Primary/PPI0 Data   | С                           |

| PD3/PPI1_D3/HOST_D11/ TSCLK1/PPI0_D21         | I/O                     | GPIO/PPI1 Data/Host DMA/SPORT1 Transmit Serial Clock/PPI0 Data   | А                           |

| PD4/PPI1_D4/HOST_D12/RFS1/PPI0_D22            | I/O                     | GPIO/PPI1 Data/Host DMA/SPORT1 Receive Frame Sync/PPI0 Data      | С                           |

| PD5/PPI1_D5/HOST_D13/DR1SEC/PPI0_D23          | I/O                     | GPIO/PPI1 Data/Host DMA/SPORT1 Receive Data Secondary/PPI0 Data  | С                           |

| PD6/PPI1_D6/HOST_D14/DR1PRI                   | I/O                     | GPIO/PPI1 Data/Host DMA/SPORT1 Receive Data Primary              | С                           |

| PD7/PPI1_D7/HOST_D15/RSCLK1                   | I/O                     | GPIO/PPI1 Data / Host DMA/SPORT1 Receive Serial Clock            | А                           |

| PD8/PPI1_D8/HOST_D0/PPI2_D0/KEY_ROW0          | I/O                     | GPIO/PPI1 Data/Host DMA/PPI2 Data/Keypad Row Input               | А                           |

| PD9/PPI1_D9/HOST_D1/PPI2_D1/KEY_ROW1          | I/O                     | GPIO/PPI1 Data/Host DMA/PPI2 Data/Keypad Row Input               | А                           |

| PD10/PPI1_D10/HOST_D2/PPI2_D2/KEY_ROW2        | I/O                     | GPIO/PPI1 Data/Host DMA/PPI2 Data/Keypad Row Input               | А                           |

| PD11/PPI1_D11/HOST_D3/PPI2_D3/KEY_ROW3        | I/O                     | GPIO/PPI1 Data/Host DMA/PPI2 Data/Keypad Row Input               | А                           |

| PD12/PPI1_D12/HOST_D4/PPI2_D4/KEY_COL0        | I/O                     | GPIO/PPI1 Data/Host DMA/PPI2 Data/Keypad Column Output           | A                           |

| PD13/PPI1_D13/HOST_D5/PPI2_D5/KEY_COL1        | I/O                     | GPIO/PPI1 Data/Host DMA/PPI2 Data/Keypad Column Output           | A                           |

| PD14/PPI1_D14/HOST_D6/PPI2_D6/KEY_COL2        | I/O                     | GPIO/PPI1 Data/Host DMA/PPI2 Data/Keypad Column Output           | A                           |

| PD15/PPI1_D15/HOST_D7/PPI2_D7/KEY_COL3        | I/O                     | GPIO/PPI1 Data/Host DMA/PPI2 Data/Keypad Column Output           | А                           |

### Table 11. Pin Descriptions (Continued)

| Pin Name                         |     | Function (First/Second/Third/Fourth)           | Driver<br>Type <sup>2</sup> |

|----------------------------------|-----|------------------------------------------------|-----------------------------|

| Port I: GPIO/AMC                 |     |                                                |                             |

| PI0/ <i>A10</i> <sup>6</sup>     | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI1/A11 <sup>6</sup>             | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI2/A12 <sup>6</sup>             | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI3/A13 <sup>6</sup>             | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI4/ <i>A14</i> <sup>6</sup>     | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI5/A15 <sup>6</sup>             | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI6/A16 <sup>6</sup>             | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI7/ <i>A17</i> <sup>6</sup>     | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI8/ <i>A18</i> <sup>6</sup>     | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI9/ <i>A19</i> 6                | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI10/A20 <sup>6</sup>            | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI11/ <i>A21</i> <sup>6</sup>    | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI12/A22 <sup>6</sup>            | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI13/A23 <sup>6</sup>            | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI14/ <i>A24</i> <sup>6</sup>    | I/O | GPIO / Address Bus for Async Access            | А                           |

| PI15/A25/NR_CLK <sup>6</sup>     | I/O | GPIO / Address Bus for Async Access/ NOR clock | А                           |

| Port J: GPIO/AMC/ATAPI           |     |                                                |                             |

| PJ0/ARDY/WAIT                    | I/O | GPIO/ Async Ready/NOR Wait                     | А                           |

| PJ1/ <u>ND_CE</u> <sup>7</sup>   | I/O | GPIO/NAND Chip Enable                          | А                           |

| PJ2/ND_RB                        | I/O | GPIO / NAND Ready Busy                         | А                           |

| PJ3/ATAPI_DIOR                   | I/O | GPIO / ATAPI Read                              | А                           |

| PJ4/ATAPI_DIOW                   | I/O | GPIO/ATAPI Write                               | А                           |

| PJ5/ATAPI_CS0                    | I/O | GPIO / ATAPI Chip Select/Command Block         | А                           |

| PJ6/ATAPI_CS1                    | I/O | GPIO / ATAPI Chip Select                       | А                           |

| PJ7/ATAPI_DMACK                  | I/O | GPIO / ATAPI DMA Acknowledge                   | А                           |

| PJ8/ATAPI_DMARQ                  | I/O | GPIO / ATAPI DMA Request                       | А                           |

| PJ9/ATAPI_INTRQ                  | I/O | GPIO / Interrupt Request from the Device       | А                           |

| PJ10/ATAPI_IORDY                 | I/O | GPIO / ATAPI Ready Handshake                   | А                           |

| PJ11/ <i>BR</i> <sup>8</sup>     | I/O | GPIO/Bus Request                               | А                           |

| PJ12/ <del>BG</del> <sup>6</sup> | I/O | GPIO / Bus Grant                               | А                           |

| PJ13/ <i>BGH</i> <sup>6</sup>    | I/O | GPIO / Bus Grant Hang                          | А                           |

### Table 11. Pin Descriptions (Continued)

| Pin Name                                 | <b>I/O</b> <sup>1</sup> | Function (First/Second/Third/Fourth)                                                                             | Driver<br>Type <sup>2</sup> |

|------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------|

| USB_VBUS <sup>11</sup>                   | I/O                     | USB VBUS Pin (Pull high or low when unused.)                                                                     |                             |

| USB_VREF                                 | A                       | USB Voltage Reference (Connect to GND through a 0.1 $\mu\text{F}$ capacitor or leave unconnected when not used.) |                             |

| USB_RSET                                 | A                       | USB Resistance Set (Connect to GND through an unpopulated resistor pad.)                                         |                             |

| MXVR (MOST) Interface                    |                         |                                                                                                                  |                             |

| MFS                                      | 0                       | MXVR Frame Sync (Leave unconnected when unused.)                                                                 | С                           |

| MLF_P                                    | А                       | MXVR Loop Filter Plus (Leave unconnected when unused.)                                                           |                             |

| MLF_M                                    | А                       | MXVR Loop Filter Minus (Leave unconnected when unused.)                                                          |                             |

| MXI                                      | С                       | MXVR Crystal Input (Pull high or low when unused.)                                                               |                             |

| МХО                                      | С                       | MXVR Crystal Output (Pull high or low when unused.)                                                              |                             |

| Mode Control Pins                        |                         |                                                                                                                  |                             |

| BMODE0-3                                 | I                       | Boot Mode Strap 0–3                                                                                              |                             |

| JTAG Port Pins                           |                         |                                                                                                                  |                             |

| TDI                                      | I                       | JTAG Serial Data In                                                                                              |                             |

| TDO                                      | 0                       | JTAG Serial Data Out                                                                                             | С                           |

| TRST                                     | I                       | JTAG Reset (Pull low when unused.)                                                                               |                             |

| TMS                                      | I                       | JTAG Mode Select                                                                                                 |                             |

| тск                                      | I                       | JTAG Clock                                                                                                       |                             |

| EMU                                      | 0                       | Emulation Output                                                                                                 | С                           |

| Voltage Regulator                        |                         |                                                                                                                  |                             |

| VR <sub>OUT</sub> 0, VR <sub>OUT</sub> 1 | 0                       | External FET/BJT Drivers (Always connect together to reduce signal impedance.)                                   |                             |

| Real Time Clock                          |                         |                                                                                                                  |                             |

| RTXO                                     | С                       | RTC Crystal Output (Leave unconnected when unused. Does not three-<br>state during hibernate.)                   |                             |

| RTXI                                     | С                       | RTC Crystal Input (Pull high or low when unused.)                                                                |                             |

| Clock (PLL) Pins                         |                         |                                                                                                                  |                             |

| CLKIN                                    | С                       | Clock/Crystal Input                                                                                              |                             |

| CLKOUT                                   | 0                       | Clock Output                                                                                                     | В                           |

| XTAL                                     | С                       | Crystal Output (If CLKBUF is enabled, does not three-state during hibernate.)                                    |                             |

| CLKBUF                                   | 0                       | Buffered Oscillator Output (If enabled, does not three-state during hibernate.)                                  | с                           |

| EXT_WAKE                                 | 0                       | External Wakeup from Hibernate Output (Does not three-state during hibernate.)                                   | A                           |

| RESET                                    | I                       | Reset                                                                                                            |                             |

| NMI                                      | I                       | Non-maskable Interrupt (Pull high when unused.)                                                                  |                             |

#### Table 11. Pin Descriptions (Continued)

| Pin Name                         | I/O <sup>1</sup> | Function (First/Second/Third/Fourth)                                                                                                                 | Driver<br>Type <sup>2</sup> |

|----------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Supplies                         |                  |                                                                                                                                                      |                             |

| V <sub>DDINT</sub>               | Р                | Internal Power Supply                                                                                                                                |                             |

| V <sub>DDEXT</sub> <sup>12</sup> | Р                | External Power Supply                                                                                                                                |                             |

| V <sub>DDDDR</sub> <sup>12</sup> | Р                | External DDR Power Supply                                                                                                                            |                             |

| V <sub>DDUSB</sub> <sup>12</sup> | Р                | External USB Power Supply                                                                                                                            |                             |

| V <sub>DDRTC</sub> <sup>12</sup> | Р                | RTC Clock Supply                                                                                                                                     |                             |

| V <sub>DDVR</sub> <sup>13</sup>  | Р                | Internal Voltage Regulator Power Supply (Connect to $V_{DDEXT}$ when unused.)                                                                        |                             |

| GND                              | G                | Ground                                                                                                                                               |                             |

| V <sub>DDMP</sub> <sup>12</sup>  | Р                | MXVR PLL Power Supply. (Must be driven to same level as $V_{\text{DDINT}}$ . Connect to $V_{\text{DDINT}}$ when unused or when MXVR is not present.) |                             |

| GND <sub>MP</sub> <sup>12</sup>  | G                | MXVR PLL Ground (Connect to GND when unused or when MXVR is not present.)                                                                            |                             |

<sup>1</sup>I = Input, O = Output, P = Power, G = Ground, C = Crystal, A = Analog.

<sup>2</sup>Refer to Table 62 on Page 88 through Table 71 on Page 89 for driver types.

<sup>3</sup>To use the SPI memory boot, SPI0SCK should have a pulldown, SPI0MISO should have a pullup, and SPI0SEL1 is used as the CS with a pullup.

<sup>4</sup>HWAIT/HWAITA should be pulled high or low to configure polarity. See Booting Modes on Page 18.

${}^{5}\overline{\text{GPW}}$  functionality is available when MXVR is not present or unused.

<sup>6</sup> This pin should not be used as GPIO if booting in mode 1.

<sup>7</sup>This pin should always be enabled as ND\_CE in software and pulled high with a resistor when using NAND flash.

<sup>8</sup> This pin should always be enabled as BR in software and pulled high to enable asynchronous access.

<sup>9</sup> This pin must be pulled low through a 10kOhm resistor if self-refresh mode is desired during hibernate state or deep-sleep mode.

<sup>10</sup>If the USB is used in device mode only, the USB\_ID pin should be either pulled high or left unconnected.

<sup>11</sup>This pin is an output only during initialization of USB OTG session request pulses in peripheral mode. Therefore, host mode or OTG type A mode requires that an external voltage source of 5 V, at 8 mA or more per the OTG specification, be applied to this pin. Other OTG modes require that this external voltage be disabled.

<sup>12</sup>To ensure proper operation, the power pins should be driven to their specified level even if the associated peripheral is not used in the application.

<sup>13</sup>This pin must always be connected. If the internal voltage regulator is not being used, this pin may be connected to V<sub>DDEXT</sub>. Otherwise it should be powered according to the VDDVR specification. For automotive grade models, the internal voltage regulator must not be used and this pin must be tied to V<sub>DDEXT</sub>.

# **SPECIFICATIONS**

### **OPERATING CONDITIONS**

| Parameter                          |                                              | Conditions                                               | Min                     | Nominal                 | Max                     | Unit |

|------------------------------------|----------------------------------------------|----------------------------------------------------------|-------------------------|-------------------------|-------------------------|------|

| V <sub>DDINT</sub> <sup>1, 2</sup> | Internal Supply Voltage                      | Nonautomotive grade models                               | 0.9                     |                         | 1.43                    | V    |

|                                    | Internal Supply Voltage                      | Automotive and extended temp                             | 1.0                     |                         | 1.38                    | V    |

|                                    |                                              | grade models                                             |                         |                         |                         |      |

|                                    | Internal Supply Voltage                      | Mobile DDR SDRAM models                                  | 1.14                    |                         | 1.31                    | V    |

| V <sub>DDEXT</sub> <sup>3</sup>    | External Supply Voltage                      | Nonautomotive 3.3 V I/O                                  | 2.7                     | 3.3                     | 3.6                     | V    |

|                                    | External Supply Voltage                      | Nonautomotive 2.5 V I/O                                  | 2.25                    | 2.5                     | 2.75                    | V    |

|                                    | External Supply Voltage                      | Automotive and extended temp                             | 2.7                     | 3.3                     | 3.6                     | V    |

|                                    |                                              | grade models                                             |                         |                         |                         |      |

| V <sub>DDUSB</sub>                 | USB External Supply Voltage                  |                                                          | 3.0                     | 3.3                     | 3.6                     | V    |

| V <sub>DDMP</sub>                  | MXVR PLL Supply Voltage                      | Nonautomotive grade models                               | 0.9                     |                         | 1.43                    | V    |

|                                    | MXVR PLL Supply Voltage                      | Automotive and extended temp grade models                | 1.0                     |                         | 1.38                    | V    |

| V <sub>DDRTC</sub>                 | Real Time Clock Supply Voltage               | Nonautomotive grade models                               | 2.25                    |                         | 3.6                     | V    |

|                                    | Real Time Clock Supply Voltage               | Automotive and extended temp                             | 2.7                     | 3.3                     | 3.6                     | V    |

|                                    |                                              | grade models                                             |                         |                         |                         |      |

| V <sub>DDDDR</sub>                 | DDR Memory Supply Voltage                    | DDR SDRAM models                                         | 2.5                     | 2.6                     | 2.7                     | V    |

|                                    | DDR Memory Supply Voltage                    | Mobile DDR SDRAM models                                  | 1.8                     | 1.875                   | 1.95                    | V    |

| V <sub>DDVR</sub> <sup>4</sup>     | Internal Voltage Regulator<br>Supply Voltage |                                                          | 2.7                     | 3.3                     | 3.6                     | V    |

| V <sub>IH</sub>                    | High Level Input Voltage <sup>5, 6</sup>     | V <sub>DDEXT</sub> = maximum                             | 2.0                     |                         | 3.6                     | V    |

| VIHDDR                             | High Level Input Voltage <sup>7</sup>        | DDR SDRAM models                                         | $V_{DDR_VREF} + 0.15$   |                         | $V_{DDDDR} + 0.3$       | V    |

|                                    | High Level Input Voltage <sup>7</sup>        | Mobile DDR SDRAM models                                  | $V_{DDR_VREF} + 0.125$  |                         | $V_{DDDDR} + 0.3$       | V    |

| V <sub>IH5V</sub> <sup>12</sup>    | High Level Input Voltage <sup>8</sup>        | V <sub>DDEXT</sub> = maximum                             | 2.0                     |                         | 5.5                     | V    |

| VIHTWI                             | High Level Input Voltage <sup>9, 13</sup>    | V <sub>DDEXT</sub> = maximum                             | $0.7 \times V_{DDEXT}$  |                         | 5.5                     | V    |

| V <sub>IHUSB</sub>                 | High Level Input Voltage <sup>10</sup>       |                                                          |                         |                         | 5.25                    | V    |

| V <sub>IL</sub>                    | Low Level Input Voltage <sup>5, 11</sup>     | V <sub>DDEXT</sub> = minimum                             | -0.3                    |                         | 0.6                     | V    |

| V <sub>IL5V</sub>                  | Low Level Input Voltage <sup>12</sup>        | 3.3 V I/O, V <sub>DDEXT</sub> = minimum                  | -0.3                    |                         | 0.8                     | V    |

|                                    | Low Level Input Voltage <sup>12</sup>        | 2.5 V I/O, V <sub>DDEXT</sub> = minimum                  | -0.3                    |                         | 0.6                     | V    |

| VILDDR                             | Low Level Input Voltage <sup>7</sup>         | DDR SDRAM models                                         | -0.3                    |                         | $V_{DDR_VREF} - 0.15$   | V    |

|                                    | Low Level Input Voltage <sup>7</sup>         | Mobile DDR SDRAM models                                  | -0.3                    |                         | $V_{DDR_VREF} - 0.125$  | V    |

| V <sub>ILTWI</sub>                 | Low Level Input Voltage <sup>9, 13</sup>     |                                                          | -0.3                    |                         | $0.3 \times V_{DDEXT}$  | V    |

| V <sub>DDR_VREF</sub>              | DDR_VREF Pin Input Voltage                   |                                                          | $0.49 \times V_{DDDDR}$ | $0.50 \times V_{DDDDR}$ | $0.51 \times V_{DDDDR}$ | v    |

| T <sub>J</sub> <sup>14</sup>       | Junction Temperature<br>(400/533 MHz)        | 400-Ball CSP_BGA $@T_{AMBIENT} = -40^{\circ}C$ to +85°C  | -40                     |                         | +105                    | °C   |

|                                    | Junction Temperature<br>(600 MHz)            | 400-Ball CSP_BGA @T <sub>AMBIENT</sub> =<br>0°C to +70°C | 0                       |                         | +90                     | °C   |

|                                    | Junction Temperature<br>(400 MHz)            | 400-Ball CSP_BGA $@T_{AMBIENT} =$<br>-40°C to +105°C     | -40                     |                         | +125                    | °C   |

<sup>1</sup>See Table 12 on Page 35 for frequency/voltage specifications.

<sup>2</sup> V<sub>DDINT</sub> maximum is 1.10 V during one-time-programmable (OTP) memory programming operations.

<sup>3</sup>V<sub>DDEXT</sub> minimum is 3.0 V and maximum is 3.6 V during OTP memory programming operations.

<sup>4</sup> Use of the internal voltage regulator is not supported on 600 MHz speed grade models or on automotive grade models. An external voltage regulator must be used.

<sup>5</sup> Bidirectional pins (D15–0, PA15–0, PB14–0, PC15–0, PD15–0, PE15–0, PF15–0, PG15–0, PH13–0, PI14–0) and input pins (ATAPI\_PDIAG, USB\_ID, TCK, TDI, TMS, TRST, CLKIN, RESET, NMI, and BMODE3–0) of the ADSP-BF54x Blackfin processors are 3.3 V-tolerant (always accept up to 3.6 V maximum V<sub>IH</sub>). Voltage compliance (on outputs, V<sub>OH</sub>) is limited by the V<sub>DDEXT</sub> supply voltage. The regulator can generate V<sub>DDINT</sub> at levels of 0.90 V to 1.30 V with -5% to +5% tolerance.

<sup>6</sup> Parameter value applies to all input and bidirectional pins except PB1-0, PE15-14, PG15-11, PH7-6, DQ0-15, and DQS0-1.

<sup>7</sup> Parameter value applies to pins DQ0-15 and DQS0-1.

<sup>8</sup> PB1-0, PE15-14, PG15-11, and PH7-6 are 5.0 V-tolerant (always accept up to 5.5 V maximum V<sub>IH</sub> when power is applied to V<sub>DDEXT</sub> pins). Voltage compliance (on output V<sub>OH</sub>) is limited by V<sub>DDEXT</sub> supply voltage.

<sup>9</sup> SDA and SCL are 5.0 V tolerant (always accept up to 5.5 V maximum V<sub>IH</sub>). Voltage compliance on outputs (V<sub>OH</sub>) is limited by the <sub>VDDEXT</sub> supply voltage.

<sup>13</sup>See the ADSP-BF54x Blackfin Processor Hardware Reference Manual for definition of sleep, deep sleep, and hibernate operating modes.

<sup>14</sup>Includes current on V<sub>DDEXT</sub>, V<sub>DDUSB</sub>, V<sub>DDVR</sub>, and V<sub>DDDDR</sub> supplies. Clock inputs are tied high or low.

<sup>15</sup>Guaranteed maximum specifications.

Total power dissipation has two components:

- Static, including leakage current

- Dynamic, due to transistor switching characteristics

Many operating conditions can also affect power dissipation, including temperature, voltage, operating frequency, and processor activity. Electrical Characteristics on Page 36 shows the current dissipation for internal circuitry ( $V_{DDINT}$ ). I<sub>DDDEEPSLEEP</sub> specifies static power dissipation as a function of voltage ( $V_{DDINT}$ ) and temperature (see Table 16 and Table 17), and

$I_{DDINT}$  specifies the total power specification for the listed test conditions, including the dynamic component as a function of voltage ( $V_{DDINT}$ ) and frequency (Table 19).

There are two parts to the dynamic component. The first part is due to transistor switching in the core clock (CCLK) domain. This part is subject to an activity scaling factor (ASF) which represents application code running on the processor core and L1/L2 memories (Table 18). The ASF is combined with the CCLK frequency and  $V_{DDINT}$  dependent data in Table 19 to calculate this part. The second part is due to transistor switching in the system clock (SCLK) domain, which is included in the I<sub>DDINT</sub> specification equation.

Table 16. Static Current—Low Power Process (mA)<sup>1</sup>

|                                       |        | Voltage (V <sub>DDINT</sub> ) <sup>2</sup> |        |        |        |        |        |        |        |        |        |        |        |

|---------------------------------------|--------|--------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| <b>۲</b> ر (° <b>C</b> ) <sup>2</sup> | 0.90 V | 0.95 V                                     | 1.00 V | 1.05 V | 1.10 V | 1.15 V | 1.20 V | 1.25 V | 1.30 V | 1.35 V | 1.38 V | 1.40 V | 1.43 V |

| -40                                   | 11.9   | 13.5                                       | 15.5   | 17.7   | 20.3   | 23.3   | 26.8   | 30.6   | 35.0   | 39.9   | 43.2   | 45.5   | 49.5   |

| 0                                     | 20.1   | 22.3                                       | 24.7   | 27.8   | 31.1   | 34.9   | 39.3   | 44.2   | 49.6   | 55.7   | 59.8   | 62.5   | 67.2   |

| 25                                    | 31.2   | 34.2                                       | 37.5   | 41.3   | 45.6   | 50.3   | 55.7   | 61.7   | 68.2   | 75.4   | 80.3   | 83.6   | 88.6   |

| 45                                    | 47.0   | 51.0                                       | 55.5   | 60.6   | 66.0   | 72.0   | 78.8   | 86.1   | 94.2   | 102.9  | 108.9  | 112.8  | 118.2  |

| 55                                    | 58.6   | 63.1                                       | 68.3   | 74.1   | 80.3   | 87.1   | 94.9   | 103.0  | 112.0  | 122.0  | 128.4  | 132.8  | 140.0  |

| 70                                    | 80.7   | 86.6                                       | 93.0   | 100.2  | 108.1  | 116.7  | 125.9  | 136.0  | 146.8  | 158.7  | 166.4  | 171.6  | 179.5  |

| 85                                    | 107.0  | 114.3                                      | 122.5  | 131.5  | 141.2  | 151.7  | 163.1  | 175.3  | 188.5  | 202.7  | 211.8  | 218.0  | 226.7  |

| 100                                   | 153.9  | 163.0                                      | 173.3  | 184.8  | 197.0  | 210.0  | 224.1  | 239.0  | 255.1  | 272.4  | 283.4  | 290.8  | 300.6  |

| 105                                   | 171.7  | 181.5                                      | 192.7  | 205.1  | 218.3  | 232.4  | 247.5  | 263.6  | 280.9  | 299.3  | 308.7  | 314.9  | 325.7  |

| 115                                   | 210.1  | 221.4                                      | 234.2  | 248.6  | 263.7  | 279.9  | 297.3  | 311.0  | 331.1  | 352.5  | 366.3  | N/A    | N/A    |

| 125                                   | 257.9  | 270.9                                      | 285.9  | 302.5  | 314.6  | 334.0  | 354.3  | 375.7  | 399.2  | 423.8  | 439.6  | N/A    | N/A    |

<sup>1</sup>Values are guaranteed maximum I<sub>DDDEEPSLEEP</sub> for 400 MHz speed-grade devices.

<sup>2</sup>Valid temperature and voltage ranges are model-specific. See Operating Conditions on Page 34.

Table 17. Static Current—Automotive 400 MHz and All 533 MHz/600 MHz Speed Grade Devices (mA)<sup>1</sup>

|                                  |        | Voltage (V <sub>DDINT</sub> ) <sup>2</sup> |        |        |        |        |        |        |        |        |        |        |        |

|----------------------------------|--------|--------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Τ <sub>J</sub> (°C) <sup>2</sup> | 0.90 V | 0.95 V                                     | 1.00 V | 1.05 V | 1.10 V | 1.15 V | 1.20 V | 1.25 V | 1.30 V | 1.35 V | 1.38 V | 1.40 V | 1.43 V |

| -40                              | 19.7   | 22.1                                       | 24.8   | 27.9   | 31.4   | 35.4   | 39.9   | 45.0   | 50.6   | 57.0   | 61.2   | 64.0   | 70.4   |

| 0                                | 45.2   | 49.9                                       | 55.2   | 61.3   | 67.9   | 75.3   | 83.5   | 92.6   | 102.6  | 113.6  | 121.0  | 125.8  | 135.0  |

| 25                               | 80.0   | 87.5                                       | 96.2   | 105.8  | 116.4  | 127.9  | 140.4  | 154.1  | 169.2  | 185.4  | 196.1  | 203.3  | 218.0  |

| 45                               | 124.2  | 134.8                                      | 147.1  | 160.7  | 175.3  | 191.2  | 208.6  | 227.3  | 247.6  | 269.6  | 284.0  | 293.6  | 312.0  |

| 55                               | 154.6  | 167.2                                      | 181.7  | 197.7  | 214.9  | 233.8  | 254.2  | 276.1  | 299.7  | 325.9  | 343.1  | 354.6  | 374.0  |

| 70                               | 209.8  | 225.6                                      | 243.9  | 264.1  | 285.8  | 309.4  | 334.8  | 363.5  | 394.3  | 427.7  | 449.4  | 463.9  | 489.0  |

| 85                               | 281.8  | 301.3                                      | 323.5  | 350.2  | 378.5  | 408.9  | 442.1  | 477.9  | 516.5  | 557.5  | 584.2  | 602.0  | 629.0  |

| 100                              | 366.5  | 390.5                                      | 419.4  | 452.1  | 486.9  | 524.4  | 564.8  | 608.2  | 654.8  | 704.7  | 737.0  | 758.5  | 793.0  |

| 105                              | 403.8  | 428.3                                      | 459.5  | 494.3  | 531.7  | 571.9  | 614.9  | 661.5  | 711.1  | 763.9  | 798.5  | 821.6  | 864.0  |

<sup>1</sup>Values are guaranteed maximum I<sub>DDDEEPSLEEP</sub> for automotive 400 MHz and all 533 MHz and 600 MHz speed grade devices.

<sup>2</sup>Valid temperature and voltage ranges are model-specific. See Operating Conditions on Page 34.

<sup>&</sup>lt;sup>16</sup>Unit for V<sub>DDINT</sub> is V (volts). Unit for  $f_{SCLK}$  is MHz. Example: 1.2 V, 133 MHz would be  $0.77 \times 1.2 \times 133 = 122.9$  mA added to  $I_{DDDEEPSLEEP}$ . <sup>17</sup>See Table 18 for the list of  $I_{DDINT}$  power vectors covered.

| Table 28. Asynchrono | ous Memory Read | l Cycle Timing with | Asynchronous ARDY      |

|----------------------|-----------------|---------------------|------------------------|

| rabic 20. risynchion | us memory near  | a Cycle I ming with | r risynem onous ritter |

| Parameter         |                                                    | Min | Мах                       | Unit              |

|-------------------|----------------------------------------------------|-----|---------------------------|-------------------|

| Timing Req        | uirements                                          |     |                           |                   |

| t <sub>SDAT</sub> | DATA15-0 Setup Before CLKOUT                       | 5.0 |                           | ns                |

| t <sub>HDAT</sub> | DATA15-0 Hold After CLKOUT                         | 0.8 |                           | ns                |

| t <sub>DANR</sub> | ARDY Negated Delay from AMSx Asserted <sup>1</sup> |     | $(S + RA - 2) \times t_s$ | <sub>CLK</sub> ns |

| t <sub>HAA</sub>  | ARDY Asserted Hold After ARE Negated               | 0.0 |                           | ns                |

| Switching C       | haracteristics                                     |     |                           |                   |

| t <sub>DO</sub>   | Output Delay After CLKOUT <sup>2</sup>             |     | 6.0                       | ns                |

| t <sub>HO</sub>   | Output Hold After CLKOUT <sup>2</sup>              | 0.3 |                           | ns                |

<sup>1</sup>S = number of programmed setup cycles, RA = number of programmed read access cycles.

<sup>2</sup> Output pins include  $\overline{AMS3-0}$ ,  $\overline{ABE1-0}$ , ADDR19-1,  $\overline{AOE}$ , and  $\overline{ARE}$ .

Figure 14. Asynchronous Memory Read Cycle Timing with Asynchronous ARDY

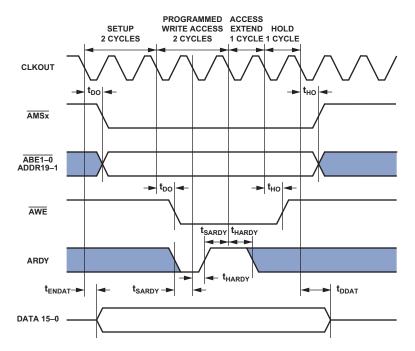

#### Asynchronous Memory Write Cycle Timing

Table 29 and Table 30 on Page 47 and Figure 15 and Figure 16 on Page 47 describe asynchronous memory write cycle operations for synchronous and for asynchronous ARDY.

#### Table 29. Asynchronous Memory Write Cycle Timing with Synchronous ARDY

| Parameter           |                                              | Min | Max | Unit |  |  |  |

|---------------------|----------------------------------------------|-----|-----|------|--|--|--|

| Timing Requirements |                                              |     |     |      |  |  |  |

| t <sub>SARDY</sub>  | ARDY Setup Before the Falling Edge of CLKOUT | 5.0 |     | ns   |  |  |  |

| t <sub>HARDY</sub>  | ARDY Hold After the Falling Edge of CLKOUT   | 0.0 |     | ns   |  |  |  |

| Switching Cl        | haracteristics                               |     |     |      |  |  |  |

| t <sub>DDAT</sub>   | DATA15-0 Disable After CLKOUT                |     | 6.0 | ns   |  |  |  |

| t <sub>ENDAT</sub>  | DATA15-0 Enable After CLKOUT                 | 0.0 |     | ns   |  |  |  |

| t <sub>DO</sub>     | Output Delay After CLKOUT <sup>1</sup>       |     | 6.0 | ns   |  |  |  |

| t <sub>HO</sub>     | Output Hold After CLKOUT <sup>1</sup>        | 0.3 |     | ns   |  |  |  |

<sup>1</sup>Output pins include  $\overline{AMS3-0}$ ,  $\overline{ABE1-0}$ , ADDR19-1, and  $\overline{AWE}$ .

Figure 15. Asynchronous Memory Write Cycle Timing with Synchronous ARDY

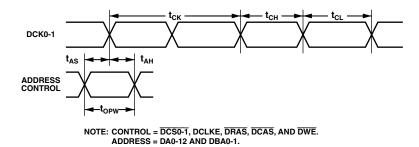

### DDR SDRAM/Mobile DDR SDRAM Clock and Control Cycle Timing

Table 31 and Figure 17 describe DDR SDRAM/mobile DDRSDRAM clock and control cycle timing.

#### Table 31. DDR SDRAM/Mobile DDR SDRAM Clock and Control Cycle Timing

|                                  |                                                      | DDR SDR | АМ   | Mobile D | OR SDRAM |                 |

|----------------------------------|------------------------------------------------------|---------|------|----------|----------|-----------------|

| Parameter                        |                                                      | Min     | Мах  | Min      | Max      | Unit            |

| Switching                        | Characteristics                                      |         |      |          |          |                 |

| t <sub>CK</sub> <sup>1</sup>     | DCK0-1 Period, Non-Extended Temperature Grade Models | 7.50    |      | 7.50     | 8.33     | ns              |

|                                  | DCK0-1 Period, Extended Temperature Grade Models     | 10.00   |      | N/A      | N/A      | ns              |

| t <sub>CH</sub>                  | DCK0-1 High Pulse Width                              | 0.45    | 0.55 | 0.45     | 0.55     | t <sub>CK</sub> |

| t <sub>CL</sub>                  | DCK0-1 Low Pulse Width                               | 0.45    | 0.55 | 0.45     | 0.55     | t <sub>CK</sub> |

| t <sub>AS</sub> <sup>2, 3</sup>  | Address and Control Output SETUP Time Relative to CK | 1.00    |      | 1.00     |          | ns              |

| t <sub>AH</sub> <sup>2, 3</sup>  | Address and Control Output HOLD Time Relative to CK  | 1.00    |      | 1.00     |          | ns              |

| t <sub>OPW</sub> <sup>2, 3</sup> | Address and Control Output Pulse Width               | 2.20    |      | 2.30     |          | ns              |

$^{\rm 1}$  The  $t_{\rm CK}$  specification does not account for the effects of jitter.

<sup>2</sup>Address pins include DA0-12 and DBA0-1.

<sup>3</sup>Control pins include DCS0-1, DCLKE, DRAS, DCAS, and DWE.

Figure 17. DDR SDRAM / Mobile DDR SDRAM Clock and Control Cycle Timing

#### **External Port Bus Request and Grant Cycle Timing**

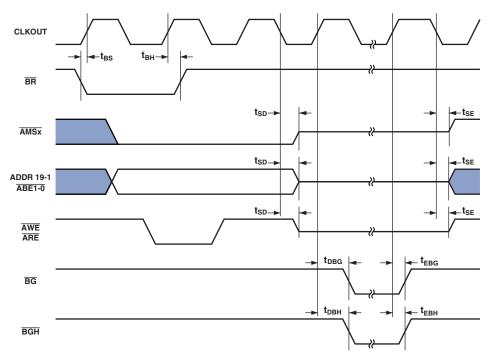

Table 34 and Table 35 on Page 52 and Figure 21 and Figure 22 on Page 52 describe external port bus request and grant cycle operations for synchronous and for asynchronous BR.

### Table 34. External Port Bus Request and Grant Cycle Timing with Synchronous BR

| Paramete            | r                                                | Min | Мах | Unit |  |  |

|---------------------|--------------------------------------------------|-----|-----|------|--|--|

| Timing Requirements |                                                  |     |     |      |  |  |

| t <sub>BS</sub>     | BR Asserted to CLKOUT Low Setup                  | 5.0 |     | ns   |  |  |

| t <sub>BH</sub>     | CLKOUT Low to BR Deasserted Hold Time            | 0.0 |     | ns   |  |  |

| Switching (         | Characteristics                                  |     |     |      |  |  |

| t <sub>sD</sub>     | CLKOUT Low to AMSx, Address, and ARE/AWE Disable |     | 5.0 | ns   |  |  |

| t <sub>SE</sub>     | CLKOUT Low to AMSx, Address, and ARE/AWE Enable  |     | 5.0 | ns   |  |  |

| t <sub>DBG</sub>    | CLKOUT Low to BG Asserted Output Delay           |     | 4.0 | ns   |  |  |

| t <sub>EBG</sub>    | CLKOUT Low to BG Deasserted Output Hold          |     | 4.0 | ns   |  |  |

| t <sub>DBH</sub>    | CLKOUT Low to BGH Asserted Output Delay          |     | 3.6 | ns   |  |  |

| t <sub>EBH</sub>    | CLKOUT Low to BGH Deasserted Output Hold         |     | 3.6 | ns   |  |  |

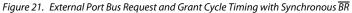

### Synchronous Burst AC Timing

Table 37 and Figure 28 on Page 57 describe Synchronous BurstAC operations.

#### Table 37. Synchronous Burst AC Timing

| Parameter           |                                                                 | Min  | Мах | Unit |

|---------------------|-----------------------------------------------------------------|------|-----|------|

| Timing Requirements |                                                                 |      |     |      |

| t <sub>NDS</sub>    | DATA15-0 Setup Before NR_CLK                                    | 4.0  |     | ns   |

| t <sub>NDH</sub>    | DATA15-0 Hold After NR_CLK                                      | 2.0  |     | ns   |

| t <sub>NWS</sub>    | WAIT Setup Before NR_CLK                                        | 8.0  |     | ns   |

| t <sub>NWH</sub>    | WAIT Hold After NR_CLK                                          | 0.0  |     | ns   |

| Switching C         | haracteristics                                                  |      |     |      |

| t <sub>NDO</sub>    | AMSx, ABE1-0, ADDR19-1, NR_ADV, NR_OE Output Delay After NR_CLK | 6.0  |     | ns   |

| t <sub>NHO</sub>    | ABE1-0, ADDR19-1 Output Hold After NR_CLK                       | -3.0 |     | ns   |

NOTE: NR\_CLK dotted line represents a free running version of NR\_CLK that is not visible on the NR\_CLK pin.

Figure 28. Synchronous Burst AC Interface Timing

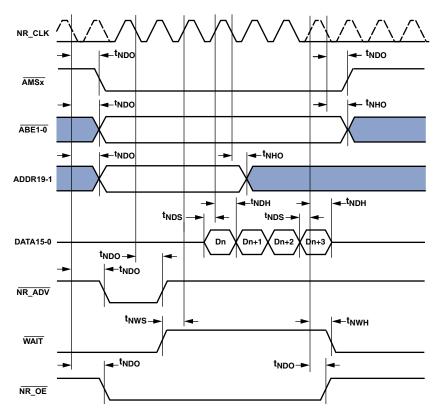

#### Table 42. Serial Ports—Enable and Three-State

| Parameter          |                                                            |    | Max | Unit |

|--------------------|------------------------------------------------------------|----|-----|------|

| Switching C        | haracteristics                                             |    |     |      |

| t <sub>DTENE</sub> | Data Enable Delay from External TSCLKx <sup>1</sup>        | 0  |     | ns   |

| t <sub>DDTTE</sub> | Data Disable Delay from External TSCLKx <sup>1, 2, 3</sup> |    | 10  | ns   |

| t <sub>DTENI</sub> | Data Enable Delay from Internal TSCLKx <sup>1</sup>        | -2 |     | ns   |

| t <sub>DDTTI</sub> | Data Disable Delay from Internal TSCLKx <sup>1, 2, 3</sup> |    | 3   | ns   |

<sup>1</sup>Referenced to drive edge.

<sup>2</sup> Applicable to multichannel mode only.

<sup>3</sup>TSCLKx is tied to RSCLKx.

Figure 36. Serial Ports—Enable and Three-State

#### Table 43. Serial Ports—External Late Frame Sync

| Parameter             |                                                                                                  | Min | Мах  | Unit |

|-----------------------|--------------------------------------------------------------------------------------------------|-----|------|------|

| Switching Cha         |                                                                                                  |     |      |      |

| t <sub>DDTLFSE</sub>  | Data Delay from Late External TFSx or External RFSx in multi-channel mode with $MFD = 01^{1, 2}$ |     | 10.0 | ns   |

| t <sub>DTENLFSE</sub> | Data Enable from External RFSx in multi-channel mode with MFD = $0^{1,2}$                        | 0   |      | ns   |

$^1$  In multichannel mode, TFSx enable and TFSx valid follow  $t_{\text{DTENLFS}}$  and  $t_{\text{DDTLFSE}}$

$^{2}$  If external RFS/TFS setup to RSCLK/TSCLK > t<sub>SCLKE</sub>/2, then t<sub>DDTE/A</sub> and t<sub>DTENE/A</sub> apply; otherwise t<sub>DDTLFSE</sub> and t<sub>DTENLFS</sub> apply.

#### **Register and PIO**

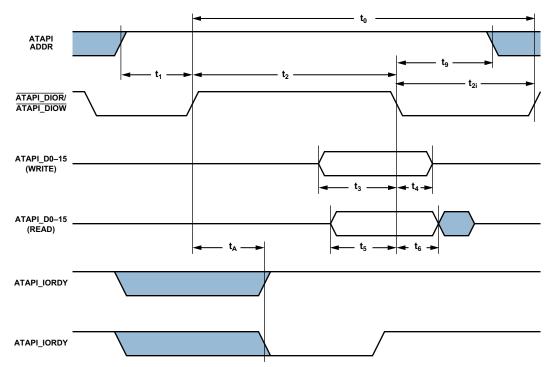

Table 58 and Figure 48 describe the ATAPI register and the PIO data transfer timing. The material in this figure is adapted from ATAPI-6 (INCITS 361-2002[R2007] and is used with permission of the American National Standards Institute (ANSI) on

behalf of the Information Technology Industry Council ("ITIC"). Copies of ATAPI-6 (INCITS 361-2002 [R2007] can be purchased from ANSI.

#### Table 58. ATAPI Register and PIO Data Transfer Timing

| ΑΤΑΡΙ Ρ         | arameter/Description                               | ATAPI_REG/PIO_TIM_x Timing Register<br>Setting <sup>1</sup> | Timing Equation                                                                     |

|-----------------|----------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------|

| t <sub>0</sub>  | Cycle time                                         | T2_PIO, TEOC_PIO                                            | $(T2_PIO + TEOC_PIO) \times t_{SCLK}$                                               |

| t <sub>1</sub>  | ATAPI_ADDR valid to<br>ATAPI_DIOR/ATAPI_DIOW setup | Τ1                                                          | $T1 \times t_{SCLK} - (t_{SK1} + t_{SK2} + t_{SK4})$                                |

| t <sub>2</sub>  | ATAPI_DIOR/ATAPI_DIOW pulse width                  | T2_PIO                                                      | T2_PIO $\times$ t <sub>SCLK</sub>                                                   |

| t <sub>2i</sub> | ATAPI_DIOR/ATAPI_DIOW recovery time                | TEOC_PIO                                                    | $TEOC_PIO \times t_{SCLK}$                                                          |

| t <sub>3</sub>  | ATAPI_DIOW data setup                              | T2_PIO                                                      | $T2\_PIO \times t_{SCLK} - (t_{SK1} + t_{SK2} + t_{SK4})$                           |

| t <sub>4</sub>  | ATAPI_DIOW data hold                               | Τ4                                                          | $T4 \times t_{SCLK} - (t_{SK1} + t_{SK2} + t_{SK4})$                                |

| t <sub>5</sub>  | ATAPI_DIOR data setup                              | N/A                                                         | $t_{OD} + t_{SUD} + 2 \times t_{BD} + t_{CDD} + t_{CDC}$                            |

| t <sub>6</sub>  | ATAPI_DIOR data hold                               | N/A                                                         | 0                                                                                   |

| t <sub>9</sub>  | ATAPI_DIOR/ATAPI_DIOW to ATAPI_ADDR valid hold     | TEOC_PIO                                                    | $TEOC\_PIO \times t_{SCLK} - (t_{SK1} + t_{SK2} + t_{SK4})$                         |

| t <sub>A</sub>  | ATAPI_IORDY setup time                             | T2_PIO                                                      | $T2\_PIO \times t_{SCLK} - (t_{OD} + t_{SUI} + 2 \times t_{CDC} + 2 \times t_{BD})$ |

<sup>1</sup>ATAPI timing register setting should be programmed with a value that guarantees parameter compliance with the ATA ANSI specification for the ATA device mode of operation.

Note that in Figure 48 ATAPI\_ADDR pins include A1-3, ATA-PI\_CSO, and ATAPI\_CS1. Alternate ATAPI port ATAPI\_ADDR pins include ATAPI\_A0A, ATAPI\_A1A, ATA-PI\_A2A, ATAPI\_CSO, and ATAPI\_CS1. Note that an alternate ATAPI\_D0-15 port bus is ATAPI\_D0-15A.

Figure 48. REG and PIO Data Transfer Timing

#### USB On-The-Go-Dual-Role Device Controller Timing

Table 62 describes the USB On-The-Go Dual-Role Device Controller timing requirements.

#### Table 62. USB On-The-Go Dual-Role Device Controller Timing Requirements

| Parameter         |                                  | Min | Мах  | Unit |

|-------------------|----------------------------------|-----|------|------|

| Timing Require    | ements                           |     |      |      |

| f <sub>USB</sub>  | USB_XI frequency                 | 9   | 33.3 | MHz  |

| FS <sub>USB</sub> | USB_XI Clock Frequency Stability | -50 | +50  | ppm  |

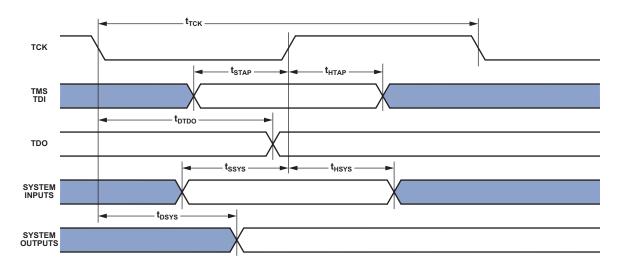

#### JTAG Test And Emulation Port Timing

Table 63 and Figure 61 describe JTAG port operations.

#### Table 63. JTAG Port Timing

| Parameter          |                                                        | Min | Мах  | Unit             |

|--------------------|--------------------------------------------------------|-----|------|------------------|

| Timing Requ        | uirements                                              |     |      |                  |

| t <sub>TCK</sub>   | TCK Period                                             | 20  |      | ns               |

| t <sub>STAP</sub>  | TDI, TMS Setup Before TCK High                         | 4   |      | ns               |

| t <sub>HTAP</sub>  | TDI, TMS Hold After TCK High                           | 4   |      | ns               |

| t <sub>ssys</sub>  | System Inputs Setup Before TCK High <sup>1</sup>       | 4   |      | ns               |

| t <sub>HSYS</sub>  | System Inputs Hold After TCK High <sup>1</sup>         | 11  |      | ns               |

| t <sub>TRSTW</sub> | TRST Pulse-Width <sup>2</sup> (measured in TCK cycles) | 4   |      | t <sub>TCK</sub> |

| Switching Cl       | haracteristics                                         |     |      |                  |

| t <sub>DTDO</sub>  | TDO Delay from TCK Low                                 |     | 10   | ns               |

| t <sub>DSYS</sub>  | System Outputs Delay After TCK Low <sup>3</sup>        | 0   | 16.5 | ns               |

<sup>1</sup> System inputs = PA15–0, PB14–0, PC13–0, PD15–0, PE15–0, PG15–0, PH13–0, PH13–0, PJ13–0, DQ15–0, DQS1–0, D15–0, ATAPI\_PDIAG, RESET, NMI, and BMODE3–0.

<sup>2</sup> 50 MHz Maximum.

<sup>3</sup> System outputs = PA15–0, PB14–0, PC13–0, PD15–0, PE15–0, PF15–0, PG15–0, PH13–0, PI15–0, PJ13–0, DQ15–0, DQS1–0, DD5–0, DA12–0, DBA1–0, DQM1–0, DCLK0-1, DCLK0–1, DCS1–0, DCLKE, DRAS, DCAS, DWE, AMS3–0, ABE1–0, AOE, ARE, AWE, CLKOUT, A3–1, and MFS.

Figure 61. JTAG Port Timing

Table 66 lists the CSP\_BGA package by ball number for the ADSP-BF549. Table 65 on Page 94 lists the CSP\_BGA package by signal.

| Ball No. | Signal                    | Ball No. | Signal   | Ball No. | Signal             | Ball No. | Signal             |

|----------|---------------------------|----------|----------|----------|--------------------|----------|--------------------|

| A1       | GND                       | C1       | МХО      | E1       | USB_DP             | G1       | PC5                |

| A2       | A2                        | C2       | MXI      | E2       | USB_DM             | G2       | PC4                |

| A3       | PIO                       | C3       | PH5      | E3       | GND                | G3       | USB_ID             |

| A4       | PI2                       | C4       | PH9      | E4       | MLF_P              | G4       | V <sub>DDUSB</sub> |

| A5       | PI4                       | C5       | PH11     | E5       | V <sub>DDEXT</sub> | G5       | V <sub>DDEXT</sub> |

| 46       | PI6                       | C6       | PH13     | E6       | MFS                | G6       | V <sub>DDEXT</sub> |

| 47       | PI8                       | C7       | PH10     | E7       | GND <sub>MP</sub>  | G7       | V <sub>DDEXT</sub> |

| 48       | PI11                      | C8       | PI9      | E8       | V <sub>DDMP</sub>  | G8       | V <sub>DDINT</sub> |

| ۹۷       | PI12                      | С9       | PI13     | E9       | V <sub>DDEXT</sub> | G9       | GND                |

| A10      | AMS0                      | C10      | AOE      | E10      | V <sub>DDEXT</sub> | G10      | GND                |

| A11      | CLKIN                     | C11      | NMI      | E11      | V <sub>DDEXT</sub> | G11      | GND                |

| A12      | XTAL                      | C12      | RESET    | E12      | V <sub>DDEXT</sub> | G12      | V <sub>DDINT</sub> |

| 13       | GND                       | C13      | D1       | E13      | V <sub>DDRTC</sub> | G13      | V <sub>DDINT</sub> |

| A14      | RTXI                      | C14      | D8       | E14      | D14                | G14      | V <sub>DDEXT</sub> |

| 15       | D4                        | C15      | D9       | E15      | D13                | G15      | V <sub>DDDDR</sub> |

| 16       | D6                        | C16      | ABE1     | E16      | DCLK0              | G16      | DA4                |

| 17       | D10                       | C17      | ABEO     | E17      | DRAS               | G17      | DA1                |

| 18       | <b>VROUT</b> <sub>0</sub> | C18      | DCLK1    | E18      | DWE                | G18      | DA3                |

| 19       | <b>VROUT</b> <sub>1</sub> | C19      | DCS0     | E19      | DA9                | G19      | DA0                |

| 20       | GND                       | C20      | DA7      | E20      | DA2                | G20      | DQM0               |

| 31       | USB_VREF                  | D1       | GND      | F1       | USB_XI             | H1       | PC3                |

| 32       | A1                        | D2       | USB_VBUS | F2       | USB_XO             | H2       | PC0                |