Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 90                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                             |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 112-LFBGA                                                                |

| Supplier Device Package    | 112-LFBGA (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32wg290f128-bga112t |

|                            |                                                                          |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1.3 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the EFM32WG microcontroller. The flash memory is readable and writable from both the Cortex-M4 and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block. Additionally, the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in the energy modes EM0 and EM1.

# 2.1.4 Direct Memory Access Controller (DMA)

The Direct Memory Access (DMA) controller performs memory operations independently of the CPU. This has the benefit of reducing the energy consumption and the workload of the CPU, and enables the system to stay in low energy modes when moving for instance data from the USART to RAM or from the External Bus Interface to a PWM-generating timer. The DMA controller uses the PL230  $\mu$ DMA controller licensed from ARM.

# 2.1.5 Reset Management Unit (RMU)

The RMU is responsible for handling the reset functionality of the EFM32WG.

## 2.1.6 Energy Management Unit (EMU)

The Energy Management Unit (EMU) manage all the low energy modes (EM) in EFM32WG microcontrollers. Each energy mode manages if the CPU and the various peripherals are available. The EMU can also be used to turn off the power to unused SRAM blocks.

# 2.1.7 Clock Management Unit (CMU)

The Clock Management Unit (CMU) is responsible for controlling the oscillators and clocks on-board the EFM32WG. The CMU provides the capability to turn on and off the clock on an individual basis to all peripheral modules in addition to enable/disable and configure the available oscillators. The high degree of flexibility enables software to minimize energy consumption in any specific application by not wasting power on peripherals and oscillators that are inactive.

# 2.1.8 Watchdog (WDOG)

The purpose of the watchdog timer is to generate a reset in case of a system failure, to increase application reliability. The failure may e.g. be caused by an external event, such as an ESD pulse, or by a software failure.

# 2.1.9 Peripheral Reflex System (PRS)

The Peripheral Reflex System (PRS) system is a network which lets the different peripheral module communicate directly with each other without involving the CPU. Peripheral modules which send out Reflex signals are called producers. The PRS routes these reflex signals to consumer peripherals which apply actions depending on the data received. The format for the Reflex signals is not given, but edge triggers and other functionality can be applied by the PRS.

# 2.1.10 External Bus Interface (EBI)

The External Bus Interface provides access to external parallel interface devices such as SRAM, FLASH, ADCs and LCDs. The interface is memory mapped into the address bus of the Cortex-M4. This enables seamless access from software without manually manipulating the IO settings each time a read or write is performed. The data and address lines are multiplexed in order to reduce the number of pins required to interface the external devices. The timing is adjustable to meet specifications of the external devices. The interface is limited to asynchronous devices.

# 2.1.27 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface (LESENSE<sup>TM</sup>), is a highly configurable sensor interface with support for up to 16 individually configurable sensors. By controlling the analog comparators and DAC, LESENSE is capable of supporting a wide range of sensors and measurement schemes, and can for instance measure LC sensors, resistive sensors and capacitive sensors. LESENSE also includes a programmable FSM which enables simple processing of measurement results without CPU intervention. LESENSE is available in energy mode EM2, in addition to EM0 and EM1, making it ideal for sensor monitoring in applications with a strict energy budget.

## 2.1.28 Backup Power Domain

The backup power domain is a separate power domain containing a Backup Real Time Counter, BURTC, and a set of retention registers, available in all energy modes. This power domain can be configured to automatically change power source to a backup battery when the main power drains out. The backup power domain enables the EFM32WG290 to keep track of time and retain data, even if the main power source should drain out.

# 2.1.29 Advanced Encryption Standard Accelerator (AES)

The AES accelerator performs AES encryption and decryption with 128-bit or 256-bit keys. Encrypting or decrypting one 128-bit data block takes 52 HFCORECLK cycles with 128-bit keys and 75 HFCORECLK cycles with 256-bit keys. The AES module is an AHB slave which enables efficient access to the data and key registers. All write accesses to the AES module must be 32-bit operations, i.e. 8- or 16-bit operations are not supported.

# 2.1.30 General Purpose Input/Output (GPIO)

In the EFM32WG290, there are 90 General Purpose Input/Output (GPIO) pins, which are divided into ports with up to 16 pins each. These pins can individually be configured as either an output or input. More advanced configurations like open-drain, filtering and drive strength can also be configured individually for the pins. The GPIO pins can also be overridden by peripheral pin connections, like Timer PWM outputs or USART communication, which can be routed to several locations on the device. The GPIO supports up to 16 asynchronous external pin interrupts, which enables interrupts from any pin on the device. Also, the input value of a pin can be routed through the Peripheral Reflex System to other peripherals.

# **2.2 Configuration Summary**

The features of the EFM32WG290 is a subset of the feature set described in the EFM32WG Reference Manual. Table 2.1 (p. 7) describes device specific implementation of the features.

| Module    | Configuration      | Pin Connections                  |

|-----------|--------------------|----------------------------------|

| Cortex-M4 | Full configuration | NA                               |

| DBG       | Full configuration | DBG_SWCLK, DBG_SWDIO,<br>DBG_SWO |

| MSC       | Full configuration | NA                               |

| DMA       | Full configuration | NA                               |

| RMU       | Full configuration | NA                               |

| EMU       | Full configuration | NA                               |

| СМU       | Full configuration | CMU_OUT0, CMU_OUT1               |

| WDOG      | Full configuration | NA                               |

#### Table 2.1. Configuration Summary

# **3 Electrical Characteristics**

# **3.1 Test Conditions**

## 3.1.1 Typical Values

The typical data are based on  $T_{AMB}$ =25°C and  $V_{DD}$ =3.0 V, as defined in Table 3.2 (p. 10), by simulation and/or technology characterisation unless otherwise specified.

### 3.1.2 Minimum and Maximum Values

The minimum and maximum values represent the worst conditions of ambient temperature, supply voltage and frequencies, as defined in Table 3.2 (p. 10), by simulation and/or technology characterisation unless otherwise specified.

# **3.2 Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings, and functional operation under such conditions are not guaranteed. Stress beyond the limits specified in Table 3.1 (p. 10) may affect the device reliability or cause permanent damage to the device. Functional operating conditions are given in Table 3.2 (p. 10).

| Symbol             | Parameter                         | Condition                              | Min  | Тур | Max                  | Unit |

|--------------------|-----------------------------------|----------------------------------------|------|-----|----------------------|------|

| T <sub>STG</sub>   | Storage tempera-<br>ture range    |                                        | -40  |     | 150 <sup>1</sup>     | °C   |

| Τ <sub>S</sub>     | Maximum soldering temperature     | Latest IPC/JEDEC J-STD-020<br>Standard |      |     | 260                  | °C   |

| V <sub>DDMAX</sub> | External main sup-<br>ply voltage |                                        | 0    |     | 3.8                  | V    |

| V <sub>IOPIN</sub> | Voltage on any I/O pin            |                                        | -0.3 |     | V <sub>DD</sub> +0.3 | V    |

#### Table 3.1. Absolute Maximum Ratings

<sup>1</sup>Based on programmed devices tested for 10000 hours at 150°C. Storage temperature affects retention of preprogrammed calibration values stored in flash. Please refer to the Flash section in the Electrical Characteristics for information on flash data retention for different temperatures.

# **3.3 General Operating Conditions**

# 3.3.1 General Operating Conditions

#### Table 3.2. General Operating Conditions

| Symbol            | Parameter                    | Min  | Тур | Max | Unit |

|-------------------|------------------------------|------|-----|-----|------|

| T <sub>AMB</sub>  | Ambient temperature range    | -40  |     | 85  | °C   |

| V <sub>DDOP</sub> | Operating supply voltage     | 1.98 |     | 3.8 | V    |

| f <sub>APB</sub>  | Internal APB clock frequency |      |     | 48  | MHz  |

| f <sub>AHB</sub>  | Internal AHB clock frequency |      |     | 48  | MHz  |

| Symbol           | Parameter         | Condition                                                                                                                | Min | Тур               | Max              | Unit       |

|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------|-----|-------------------|------------------|------------|

|                  |                   | 1.2 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =25°C                                         |     | 271               | 286              | μΑ/<br>MHz |

|                  |                   | 1.2 MHz HFRCO, all peripheral clocks disabled, $V_{\text{DD}}\text{=}$ 3.0 V, $T_{\text{AMB}}\text{=}85^{\circ}\text{C}$ |     | 275               |                  | μΑ/<br>MHz |

|                  |                   | 48 MHz HFXO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =25°C                                           |     | 63                | 75               | μΑ/<br>MHz |

|                  |                   | 48 MHz HFXO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C                                           |     | 65                | 76               | μΑ/<br>MHz |

|                  |                   | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =25°C                                          |     | 64                | 75               | μΑ/<br>MHz |

|                  |                   | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C                                          |     | 65                | 77               | μΑ/<br>MHz |

|                  |                   | 21 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                                  |     | 65                | 76               | μΑ/<br>MHz |

|                  |                   | 21 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C                                  |     | 66                | 78               | μΑ/<br>MHz |

|                  | EM1 current (Pro- | 14 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                                  |     | 67                | 79               | μΑ/<br>MHz |

| I <sub>EM1</sub> | tion = 14 MHz)    | 14 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C                                  |     | 68                | 82               | μΑ/<br>MHz |

|                  |                   | 11 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                                  |     | 68                | 81               | µA/<br>MHz |

|                  |                   | 11 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C                                  |     | 70                | 83               | µA/<br>MHz |

|                  |                   | 6.6 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                                 |     | 74                | 87               | µA/<br>MHz |

|                  |                   | 6.6 MHz HFRCO, all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =85°C                                 |     | 76                | 89               | µA/<br>MHz |

|                  |                   | 1.2 MHz HFRCO. all peripher-<br>al clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =25°C                                    |     | 106               | 120              | µA/<br>MHz |

|                  |                   | 1.2 MHz HFRCO. all peripheral clocks disabled, $V_{DD}$ = 3.0 V, $T_{AMB}$ =85°C                                         |     | 112               | 129              | μΑ/<br>MHz |

| I <sub>EM2</sub> | EM2 current       | EM2 current with RTC<br>prescaled to 1 Hz, 32.768<br>kHz LFRCO, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C                     |     | 0.95 <sup>1</sup> | 1.7 <sup>1</sup> | μA         |

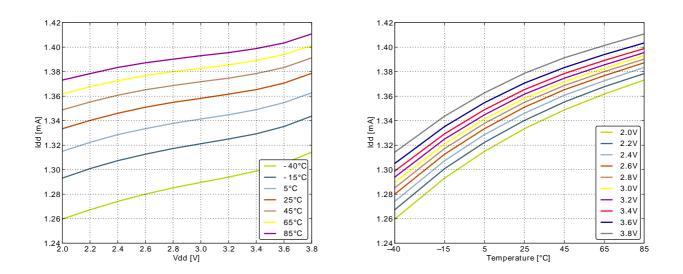

*Figure 3.3. EM1 Current consumption with all peripheral clocks disabled and HFRCO running at 21MHz*

Figure 3.4. EM1 Current consumption with all peripheral clocks disabled and HFRCO running at 14MHz

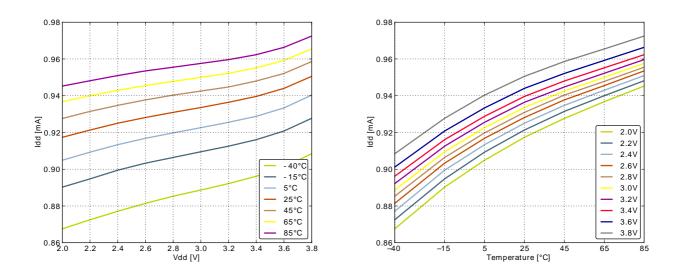

#### Figure 3.12. Typical High-Level Output Current, 2V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

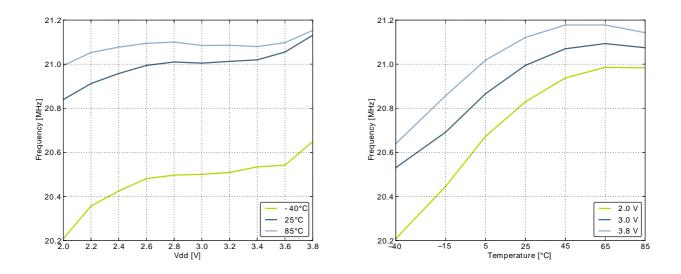

Figure 3.22. Calibrated HFRCO 21 MHz Band Frequency vs Supply Voltage and Temperature

Figure 3.23. Calibrated HFRCO 28 MHz Band Frequency vs Supply Voltage and Temperature

| Symbol                  | Parameter                                                   | Condition                                                                                       | Min | Тур  | Max             | Unit                  |

|-------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|------|-----------------|-----------------------|

|                         | erence voltage on<br>channel 6                              |                                                                                                 |     |      |                 |                       |

| V <sub>ADCCMIN</sub>    | Common mode in-<br>put range                                |                                                                                                 | 0   |      | V <sub>DD</sub> | V                     |

| I <sub>ADCIN</sub>      | Input current                                               | 2pF sampling capacitors                                                                         |     | <100 |                 | nA                    |

| CMRR <sub>ADC</sub>     | Analog input com-<br>mon mode rejection<br>ratio            |                                                                                                 |     | 65   |                 | dB                    |

|                         |                                                             | 1 MSamples/s, 12 bit, external reference                                                        |     | 351  |                 | μA                    |

|                         |                                                             | 10 kSamples/s 12 bit, internal<br>1.25 V reference, WARMUP-<br>MODE in ADCn_CTRL set to<br>0b00 |     | 67   |                 | μΑ                    |

| I <sub>ADC</sub>        | Average active cur-<br>rent                                 | 10 kSamples/s 12 bit, internal<br>1.25 V reference, WARMUP-<br>MODE in ADCn_CTRL set to<br>0b01 |     | 63   |                 | μA                    |

|                         |                                                             | 10 kSamples/s 12 bit, internal<br>1.25 V reference, WARMUP-<br>MODE in ADCn_CTRL set to<br>0b10 |     | 64   |                 | μA                    |

| I <sub>ADCREF</sub>     | Current consump-<br>tion of internal volt-<br>age reference | Internal voltage reference                                                                      |     | 65   |                 | μA                    |

|                         | Input capacitance                                           |                                                                                                 |     | 2    |                 | pF                    |

| R <sub>ADCIN</sub>      | Input ON resistance                                         |                                                                                                 | 1   |      |                 | MOhm                  |

| R <sub>ADCFILT</sub>    | Input RC filter resis-<br>tance                             |                                                                                                 |     | 10   |                 | kOhm                  |

| C <sub>ADCFILT</sub>    | Input RC filter/de-<br>coupling capaci-<br>tance            |                                                                                                 |     | 250  |                 | fF                    |

| f <sub>ADCCLK</sub>     | ADC Clock Fre-<br>quency                                    |                                                                                                 |     |      | 13              | MHz                   |

|                         |                                                             | 6 bit                                                                                           | 7   |      |                 | ADC-<br>CLK<br>Cycles |

| t <sub>ADCCONV</sub>    | Conversion time                                             | 8 bit                                                                                           | 11  |      |                 | ADC-<br>CLK<br>Cycles |

|                         |                                                             | 12 bit                                                                                          | 13  |      |                 | ADC-<br>CLK<br>Cycles |

| t <sub>ADCACQ</sub>     | Acquisition time                                            | Programmable                                                                                    | 1   |      | 256             | ADC-<br>CLK<br>Cycles |

| t <sub>ADCACQVDD3</sub> | Required acquisi-<br>tion time for VDD/3<br>reference       |                                                                                                 | 2   |      |                 | μs                    |

| t <sub>ADCSTART</sub>   | Startup time of ref-<br>erence generator                    |                                                                                                 |     | 5    |                 | μs                    |

| Symbol                 | Parameter                          | Condition                                                                | Min | Тур | Мах | Unit |

|------------------------|------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

|                        |                                    | 500 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 58  |     | dB   |

|                        |                                    | 500 kSamples/s, 12 bit, differential, $V_{DD}$ reference                 |     | 59  |     | dB   |

|                        |                                    | 500 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |     | 57  |     | dB   |

|                        | Signal to Noise-                   | 500 kSamples/s, 12 bit, single ended, internal 2.5V reference            |     | 54  |     | dB   |

| SNDR <sub>DAC</sub>    | pulse Distortion Ra-<br>tio (SNDR) | 500 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |     | 56  |     | dB   |

|                        |                                    | 500 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 53  |     | dB   |

|                        |                                    | 500 kSamples/s, 12 bit, differential, $V_{DD}$ reference                 |     | 55  |     | dB   |

|                        | Spurious-Free                      | 500 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |     | 62  |     | dBc  |

|                        |                                    | 500 kSamples/s, 12 bit, single ended, internal 2.5V reference            |     | 56  |     | dBc  |

| SFDR <sub>DAC</sub>    | Dynamic<br>Range(SFDR)             | 500 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |     | 61  |     | dBc  |

|                        |                                    | 500 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 55  |     | dBc  |

|                        |                                    | 500 kSamples/s, 12 bit, differential, $V_{DD}$ reference                 |     | 60  |     | dBc  |

| N/                     | Offeet veltage                     | After calibration, single ended                                          |     | 2   | 9   | mV   |

| V <sub>DACOFFSET</sub> | Offset voltage                     | After calibration, differential                                          |     | 2   |     | mV   |

| DNL <sub>DAC</sub>     | Differential non-lin-<br>earity    |                                                                          |     | ±1  |     | LSB  |

| INL <sub>DAC</sub>     | Integral non-lineari-<br>ty        |                                                                          |     | ±5  |     | LSB  |

| MC <sub>DAC</sub>      | No missing codes                   |                                                                          |     | 12  |     | bits |

<sup>1</sup>Measured with a static input code and no loading on the output.

# 3.12 Operational Amplifier (OPAMP)

The electrical characteristics for the Operational Amplifiers are based on simulations.

#### Table 3.17. OPAMP

| Symbol             | Parameter      | Condition                                                | Min | Тур | Мах | Unit |

|--------------------|----------------|----------------------------------------------------------|-----|-----|-----|------|

| I <sub>OPAMP</sub> |                | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0, Unity<br>Gain |     | 370 | 460 | μA   |

|                    | Active Current | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1, Unity<br>Gain |     | 95  | 135 | μA   |

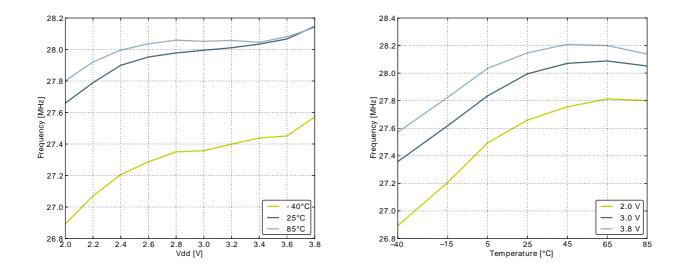

Figure 3.40. EBI Read Enable Related Output Timing

Table 3.22. EBI Read Enable Related Output Timing

| Symbol                       | Parameter                                                                                                  | Min                                                                 | Тур | Max | Unit |

|------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----|-----|------|

| t <sub>OH_REn 1234</sub>     | Output hold time, from trailing EBI_REn/<br>EBI_NANDREn edge to EBI_AD, EBI_A, EBI_CSn,<br>EBI_BLn invalid | -10.00 + (RDHOLD *<br>t <sub>HFCORECLK</sub> )                      |     |     | ns   |

| tosu_REn <sup>12345</sup>    | Output setup time, from EBI_AD, EBI_A, EBI_CSn,<br>EBI_BLn valid to leading EBI_REn/EBI_NANDREn<br>edge    | -10.00 + (RDSETUP<br>* t <sub>HFCORECLK</sub> )                     |     |     | ns   |

| twidth_REn <sup>123456</sup> | EBI_REn pulse width                                                                                        | -9.00 + ((RD-<br>STRB+1) * t <sub>HFCORE-</sub><br><sub>CLK</sub> ) |     |     | ns   |

<sup>1</sup>Applies for all addressing modes (figure only shows D8A8. Output timing for EBI\_AD only applies to multiplexed addressing modes D8A24ALE and D16A16ALE)

<sup>2</sup>Applies for both EBI\_REn and EBI\_NANDREn (figure only shows EBI\_REn)

<sup>3</sup>Applies for all polarities (figure only shows active low signals)

$^4\text{Measurement}$  done at 10% and 90% of  $V_{\text{DD}}$  (figure shows 50% of  $_{\text{VDD}})$

<sup>5</sup>The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFRE=0. The leading edge of EBI\_REn can be moved to the right by setting HALFRE=1. This decreases the length of  $t_{WIDTH_REn}$  and increases the length of  $t_{OSU_REn}$  by 1/2 \*  $t_{HFCLKNODIV}$ .

<sup>6</sup>When page mode is used, RDSTRB is replaced by RDPA for page hits.

| Symbol                                 | Parameter                                                          | Min                                | Тур | Max | Unit |

|----------------------------------------|--------------------------------------------------------------------|------------------------------------|-----|-----|------|

| t <sub>H_ARDY</sub> <sup>1 2 3 4</sup> | Hold time, from trailing EBI_REn, EBI_WEn edge to EBI_ARDY invalid | -1 + (3 * t <sub>HFCORECLK</sub> ) |     |     | ns   |

<sup>1</sup>Applies for all addressing modes (figure only shows D16A8.)

<sup>2</sup>Applies for EBI\_REn, EBI\_WEn (figure only shows EBI\_REn)

<sup>3</sup>Applies for all polarities (figure only shows active low signals)

$^4\text{Measurement}$  done at 10% and 90% of  $V_{\text{DD}}$  (figure shows 50% of  $_{\text{VDD}})$

# 3.16 I2C

#### Table 3.25. I2C Standard-mode (Sm)

| Symbol              | Parameter                                               | Min | Тур | Max                 | Unit |

|---------------------|---------------------------------------------------------|-----|-----|---------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                                     | 0   |     | 100 <sup>1</sup>    | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                                      | 4.7 |     |                     | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                                     | 4.0 |     |                     | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                         | 250 |     |                     | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                           | 8   |     | 3450 <sup>2,3</sup> | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time                    | 4.7 |     |                     | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time                    | 4.0 |     |                     | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                              | 4.0 |     |                     | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and a START condi-<br>tion | 4.7 |     |                     | μs   |

<sup>1</sup>For the minimum HFPERCLK frequency required in Standard-mode, see the I2C chapter in the EFM32WG Reference Manual. <sup>2</sup>The maximum SDA hold time ( $t_{HD,DAT}$ ) needs to be met only when the device does not stretch the low time of SCL ( $t_{LOW}$ ). <sup>3</sup>When transmitting data, this number is guaranteed only when I2Cn\_CLKDIV < ((3450\*10<sup>-9</sup> [s] \* f<sub>HFPERCLK</sub> [Hz]) - 4).

#### Table 3.26. I2C Fast-mode (Fm)

| Symbol              | Parameter                                               | Min | Тур | Max                | Unit |

|---------------------|---------------------------------------------------------|-----|-----|--------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                                     | 0   |     | 400 <sup>1</sup>   | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                                      | 1.3 |     |                    | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                                     | 0.6 |     |                    | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                         | 100 |     |                    | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                           | 8   |     | 900 <sup>2,3</sup> | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time                    | 0.6 |     |                    | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time                    | 0.6 |     |                    | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                              | 0.6 |     |                    | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and a START condi-<br>tion | 1.3 |     |                    | μs   |

<sup>1</sup>For the minimum HFPERCLK frequency required in Fast-mode, see the I2C chapter in the EFM32WG Reference Manual.

<sup>2</sup>The maximum SDA hold time ( $t_{HD,DAT}$ ) needs to be met only when the device does not stretch the low time of SCL ( $t_{LOW}$ ). <sup>3</sup>When transmitting data, this number is guaranteed only when I2Cn\_CLKDIV < ((900\*10<sup>-9</sup> [s] \*  $f_{HEPERCLK}$  [Hz]) - 4).

#### Table 3.29. SPI Master Timing with SSSEARLY and SMSDELAY

| Symbol                             | Parameter       | Condition     | Min                            | Тур | Мах  | Unit |

|------------------------------------|-----------------|---------------|--------------------------------|-----|------|------|

| t <sub>SCLK</sub> <sup>12</sup>    | SCLK period     |               | 2 * t <sub>HFPER-</sub><br>CLK |     |      | ns   |

| t <sub>CS_MO</sub> <sup>12</sup>   | CS to MOSI      |               | -2.00                          |     | 2.00 | ns   |

| t <sub>SCLK_MO</sub> <sup>12</sup> | SCLK to MOSI    |               | -1.00                          |     | 3.00 | ns   |

| t <sub>SU_MI</sub> 12              | MISO setup time | IOVDD = 3.0 V | -32.00                         |     |      | ns   |

| t <sub>H_MI</sub> 12               | MISO hold time  |               | 63.00                          |     |      | ns   |

<sup>1</sup>Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0)

$^2\text{Measurement}$  done at 10% and 90% of  $\text{V}_\text{DD}$  (figure shows 50% of  $_\text{VDD})$

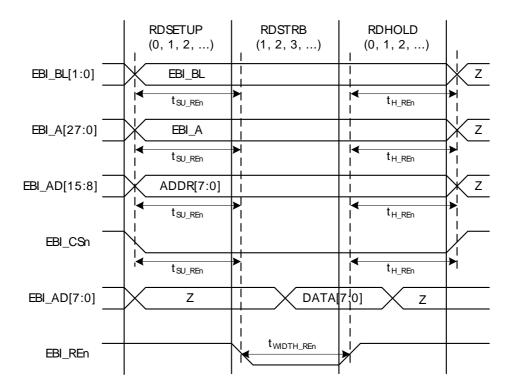

#### Figure 3.44. SPI Slave Timing

#### Table 3.30. SPI Slave Timing

| Symbol                               | Parameter          | Min                                | Тур | Мах                               | Unit |

|--------------------------------------|--------------------|------------------------------------|-----|-----------------------------------|------|

| t <sub>SCLK_sl</sub> <sup>12</sup>   | SCKL period        | 6 * t <sub>HFPER-</sub><br>CLK     |     |                                   | ns   |

| t <sub>SCLK_hi</sub> <sup>12</sup>   | SCLK high period   | 3 * t <sub>HFPER-</sub><br>CLK     |     |                                   | ns   |

| t <sub>SCLK_lo</sub> <sup>12</sup>   | SCLK low period    | 3 * t <sub>HFPER-</sub><br>CLK     |     |                                   | ns   |

| t <sub>CS_ACT_MI</sub> <sup>12</sup> | CS active to MISO  | 5.00                               |     | 35.00                             | ns   |

| t <sub>CS_DIS_MI</sub> <sup>12</sup> | CS disable to MISO | 5.00                               |     | 35.00                             | ns   |

| t <sub>SU_MO</sub> <sup>12</sup>     | MOSI setup time    | 5.00                               |     |                                   | ns   |

| t <sub>H_MO</sub> <sup>1 2</sup>     | MOSI hold time     | 2 + 2 * t <sub>HF-</sub><br>PERCLK |     |                                   | ns   |

| t <sub>SCLK_MI</sub> <sup>12</sup>   | SCLK to MISO       | 7 + t <sub>HFPER-</sub><br>CLK     |     | 42 + 2 *<br>t <sub>HFPERCLK</sub> | ns   |

<sup>1</sup>Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0)  $^{2}$ Measurement done at 10% and 90% of V<sub>DD</sub> (figure shows 50% of V<sub>DD</sub>)

#### Table 3.31. SPI Slave Timing with SSSEARLY and SMSDELAY

| Symbol                  | Parameter   | Min                     | Тур | Мах | Unit |

|-------------------------|-------------|-------------------------|-----|-----|------|

| t <sub>SCLK_sl</sub> 12 | SCKL period | 6 * t <sub>HFPER-</sub> |     |     | ns   |

|                         |             | CLK                     |     |     |      |

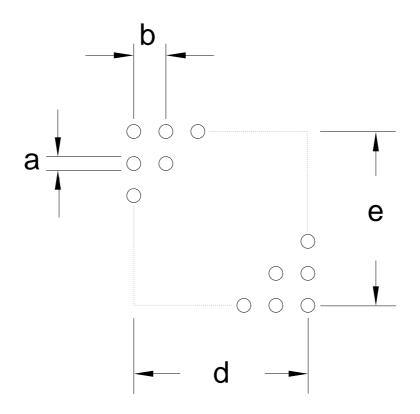

# **4 Pinout and Package**

#### Note

Please refer to the application note "AN0002 EFM32 Hardware Design Considerations" for guidelines on designing Printed Circuit Boards (PCB's) for the EFM32WG290.

## 4.1 Pinout

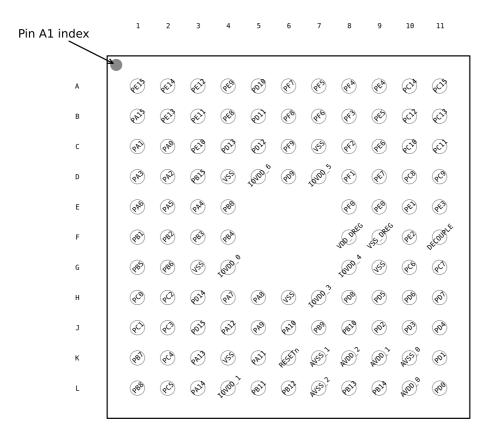

The *EFM32WG290* pinout is shown in Figure 4.1 (p. 57) and Table 4.1 (p. 57). Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

#### Figure 4.1. EFM32WG290 Pinout (top view, not to scale)

#### Table 4.1. Device Pinout

|       | GA112 Pin#<br>and Name | Pin Alternate Functionality / Description |                 |             |                                        |                              |  |  |

|-------|------------------------|-------------------------------------------|-----------------|-------------|----------------------------------------|------------------------------|--|--|

| Pin # | Pin Name               | Analog                                    | EBI             | Timers      | Communication                          | Other                        |  |  |

| A1    | PE15                   |                                           | EBI_AD07 #0/1/2 | TIM3_CC1 #0 | LEU0_RX #2                             |                              |  |  |

| A2    | PE14                   |                                           | EBI_AD06 #0/1/2 | TIM3_CC0 #0 | LEU0_TX #2                             |                              |  |  |

| A3    | PE12                   |                                           | EBI_AD04 #0/1/2 | TIM1_CC2 #1 | US0_RX #3<br>US0_CLK #0<br>I2C0_SDA #6 | CMU_CLK1 #2<br>LES_ALTEX6 #0 |  |  |

|       | GA112 Pin#<br>and Name | Pin Alternate Functionality / Description |                              |                               |                                          |                                   |  |  |  |  |

|-------|------------------------|-------------------------------------------|------------------------------|-------------------------------|------------------------------------------|-----------------------------------|--|--|--|--|

| Pin # | Pin Name               | Analog                                    | EBI                          | Timers                        | Communication                            | Other                             |  |  |  |  |

|       |                        |                                           |                              |                               |                                          | ETM_TD1 #3                        |  |  |  |  |

| D2    | PA2                    |                                           | EBI_AD11 #0/1/2              | TIM0_CC2 #0/1                 |                                          | CMU_CLK0 #0<br>ETM_TD0 #3         |  |  |  |  |

| D3    | PB15                   |                                           |                              |                               |                                          | ETM_TD2 #1                        |  |  |  |  |

| D4    | VSS                    | Ground                                    | I                            | 1                             | 1                                        | 1                                 |  |  |  |  |

| D5    | IOVDD_6                | Digital IO power supply                   | 6.                           |                               |                                          |                                   |  |  |  |  |

| D6    | PD9                    |                                           | EBI_CS0 #0/1/2               |                               |                                          |                                   |  |  |  |  |

| D7    | IOVDD_5                | Digital IO power supply                   | 5.                           | 1                             | 1                                        | ]                                 |  |  |  |  |

| D8    | PF1                    |                                           |                              | TIM0_CC1 #5<br>LETIM0_OUT1 #2 | US1_CS #2<br>LEU0_RX #3<br>I2C0_SCL #5   | DBG_SWDIO #0/1/2/3<br>GPIO_EM4WU3 |  |  |  |  |

| D9    | PE7                    |                                           | EBI_A14 #0/1/2               |                               | US0_TX #1                                |                                   |  |  |  |  |

| D10   | PC8                    | ACMP1_CH0                                 | EBI_A15 #0/1/2               | TIM2_CC0 #2                   | US0_CS #2                                | LES_CH8 #0                        |  |  |  |  |

| D11   | PC9                    | ACMP1_CH1                                 | EBI_A09 #1/2                 | TIM2_CC1 #2                   | US0_CLK #2                               | LES_CH9 #0<br>GPIO_EM4WU2         |  |  |  |  |

| E1    | PA6                    |                                           | EBI_AD15 #0/1/2              |                               | LEU1_RX #1                               | ETM_TCLK #3<br>GPIO_EM4WU1        |  |  |  |  |

| E2    | PA5                    |                                           | EBI_AD14 #0/1/2              | TIM0_CDTI2 #0                 | LEU1_TX #1                               | LES_ALTEX4 #0<br>ETM_TD3 #3       |  |  |  |  |

| E3    | PA4                    |                                           | EBI_AD13 #0/1/2              | TIM0_CDTI1 #0                 | U0_RX #2                                 | LES_ALTEX3 #0<br>ETM_TD2 #3       |  |  |  |  |

| E4    | PB0                    |                                           | EBI_A16 #0/1/2               | TIM1_CC0 #2                   |                                          |                                   |  |  |  |  |

| E8    | PF0                    |                                           |                              | TIM0_CC0 #5<br>LETIM0_OUT0 #2 | US1_CLK #2<br>LEU0_TX #3<br>I2C0_SDA #5  | DBG_SWCLK #0/1/2/3                |  |  |  |  |

| E9    | PE0                    |                                           | EBI_A07 #0/1/2               | TIM3_CC0 #1<br>PCNT0_S0IN #1  | U0_TX #1<br>I2C1_SDA #2                  |                                   |  |  |  |  |

| E10   | PE1                    |                                           | EBI_A08 #0/1/2               | TIM3_CC1 #1<br>PCNT0_S1IN #1  | U0_RX #1<br>I2C1_SCL #2                  |                                   |  |  |  |  |

| E11   | PE3                    | BU_STAT                                   | EBI_A10 #0                   |                               | U1_RX #3                                 | ACMP1_O #1                        |  |  |  |  |

| F1    | PB1                    |                                           | EBI_A17 #0/1/2               | TIM1_CC1 #2                   |                                          |                                   |  |  |  |  |

| F2    | PB2                    |                                           | EBI_A18 #0/1/2               | TIM1_CC2 #2                   |                                          |                                   |  |  |  |  |

| F3    | PB3                    |                                           | EBI_A19 #0/1/2               | PCNT1_S0IN #1                 | US2_TX #1                                |                                   |  |  |  |  |

| F4    | PB4                    |                                           | EBI_A20 #0/1/2               | PCNT1_S1IN #1                 | US2_RX #1                                |                                   |  |  |  |  |

| F8    | VDD_DREG               | Power supply for on-chip                  | o voltage regulator.         | ·                             |                                          |                                   |  |  |  |  |

| F9    | VSS_DREG               | Ground for on-chip volta                  | ge regulator.                |                               |                                          |                                   |  |  |  |  |

| F10   | PE2                    | BU_VOUT                                   | EBI_A09 #0                   | TIM3_CC2 #1                   | U1_TX #3                                 | ACMP0_O #1                        |  |  |  |  |

| F11   | DECOUPLE               | Decouple output for on-o                  | chip voltage regulator. An e | xternal capacitance of size   | e C <sub>DECOUPLE</sub> is required at t | his pin.                          |  |  |  |  |

| G1    | PB5                    |                                           | EBI_A21 #0/1/2               |                               | US2_CLK #1                               |                                   |  |  |  |  |

| G2    | PB6                    |                                           | EBI_A22 #0/1/2               |                               | US2_CS #1                                |                                   |  |  |  |  |

| G3    | VSS                    | Ground                                    |                              |                               |                                          |                                   |  |  |  |  |

| G4    | IOVDD_0                | Digital IO power supply 0.                |                              |                               |                                          |                                   |  |  |  |  |

| G8    | IOVDD_4                | Digital IO power supply                   | 4.                           |                               |                                          |                                   |  |  |  |  |

| G9    | VSS                    | Ground                                    |                              |                               |                                          |                                   |  |  |  |  |

| G10   | PC6                    | ACMP0_CH6                                 | EBI_A05 #0/1/2               |                               | LEU1_TX #0<br>I2C0_SDA #2                | LES_CH6 #0<br>ETM_TCLK #2         |  |  |  |  |

# **EFM°32**

#### ...the world's most energy friendly microcontrollers

| Functionality         0         1         2         3         4         5         6         Description           EBI_ADD1         PE9         PE90         PE10         PE10         PE10         PE10         PE10         PE10         PE11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Alternate     |      |      | L    | OCATIO | N |   |   |                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|------|------|--------|---|---|---|------------------------------------------------------------|

| Expl. Jubit         Press                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Functionality | 0    | 1    | 2    | 3      | 4 | 5 | 6 | Description                                                |

| Edit Adduz         Petric         Petri         Petr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EBI_AD01      | PE9  | PE9  | PE9  |        |   |   |   |                                                            |

| Each DAOA         Print                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EBI_AD02      | PE10 | PE10 | PE10 |        |   |   |   |                                                            |

| EBL, ADDI         PF12         PF12         PF12         PF12         PF12         PF12         PF12         PF13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EBI_AD03      | PE11 | PE11 | PE11 |        |   |   |   |                                                            |

| Ebel Audos         Petas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EBI_AD04      | PE12 | PE12 | PE12 |        |   |   |   |                                                            |

| Ead AddsPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeriaPeria<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EBI_AD05      | PE13 | PE13 | PE13 |        |   |   |   |                                                            |

| Ed., Cubor         Perior         Per                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EBI_AD06      | PE14 | PE14 | PE14 |        |   |   |   |                                                            |

| Edl_ALUSPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1SPA1S <t< td=""><td>EBI_AD07</td><td>PE15</td><td>PE15</td><td>PE15</td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EBI_AD07      | PE15 | PE15 | PE15 |        |   |   |   |                                                            |

| Ebd. ADUS         PAO         PAO         PAO         PAO         Pin O         Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EBI_AD08      | PA15 | PA15 | PA15 |        |   |   |   |                                                            |

| EBL_AD10PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EBI_AD09      | PA0  | PA0  | PA0  |        |   |   |   |                                                            |

| EBL_AD11PA2PA2PA2PA2PA2Pin 1EBL_AD12PA3PA3PA3PA3PA3PA3PA3PA3PA3PA3EBL_AD13PA4PA4PA4PA4PA4PA4PA4PA4PA4PA4EBL_AD13PA4PA4PA4PA4PA4PA4PA4PA4PA4PA4EBL_AD13PA5PA5PA5PA5PA5PA5PA5PA5PA5PA5EBL_AD14PA5PA6PA5PA5PA5PA5PA5PA5PA5PA5EBL_AD15PA6PA6PA6PA6PA6PA6PA6PA6PA6PA6EBL_AD14PA5PA5PA5PA5PA5PA5PA5PA5PA5PA5EBL_AD15PA6PA6PA6PA6PA6PA6PA6PA6PA6PA6EBL_AD17PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7PA7P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EBI_AD10      | PA1  | PA1  | PA1  |        |   |   |   |                                                            |

| EHL_AD12PA3PA3PA3PA3PA3PA3PA3PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EBI_AD11      | PA2  | PA2  | PA2  |        |   |   |   |                                                            |

| EBL_AD13PA4PA4PA4PA4PA4PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1PA1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EBI_AD12      | PA3  | PA3  | PA3  |        |   |   |   |                                                            |

| EBL_AD14PASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPASPAS<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EBI_AD13      | PA4  | PA4  | PA4  |        |   |   |   |                                                            |

| EBI_ADISPAGPAGPAGPAGPAGPAGPAGPAGPINEBI_ALEPF3PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11PC11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EBI_AD14      | PA5  | PA5  | PA5  |        |   |   |   |                                                            |

| EBI_ARDYPF2PF2PF2PF2PF2PF2PF2PF2PF2PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3PF3<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EBI_AD15      | PA6  | PA6  | PA6  |        |   |   |   |                                                            |

| EBI_BLOPF6PF6PF6IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII <t< td=""><td>EBI_ALE</td><td>PF3</td><td>PC11</td><td>PC11</td><td></td><td></td><td></td><td></td><td>External Bus Interface (EBI) Address Latch Enable output.</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | EBI_ALE       | PF3  | PC11 | PC11 |        |   |   |   | External Bus Interface (EBI) Address Latch Enable output.  |