Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 4KB (2K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 20-VQFN (3x3)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny4313-mmh |

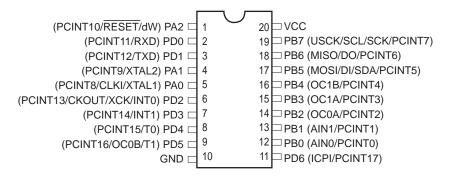

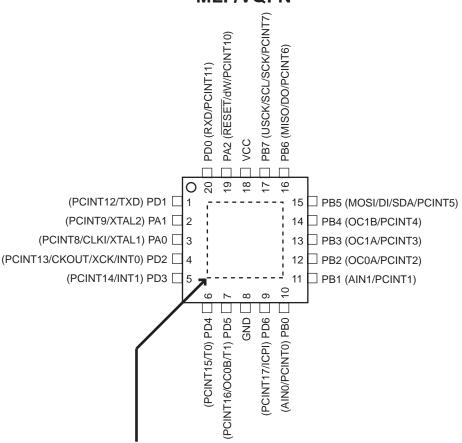

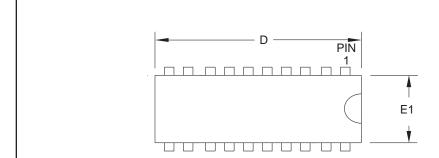

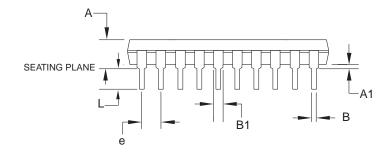

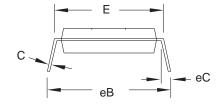

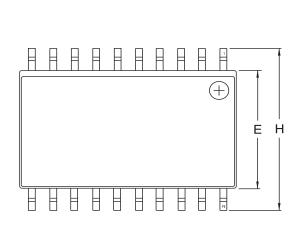

# 1. Pin Configurations

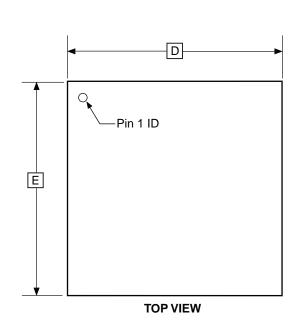

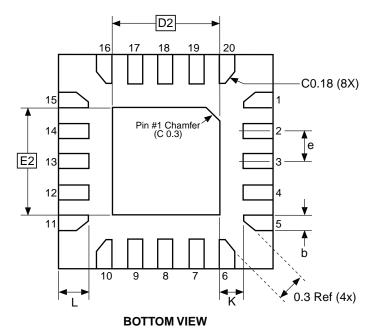

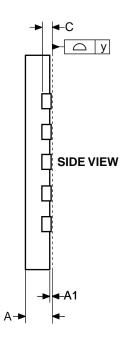

Figure 1-1. Pinout ATtiny2313A/4313

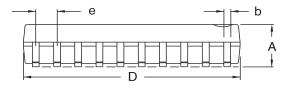

## PDIP/SOIC

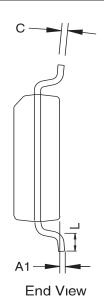

# MLF/VQFN

NOTE: Bottom pad should be soldered to ground.

# 1.1 Pin Descriptions

#### 1.1.1 VCC

Digital supply voltage.

#### 1.1.2 GND

Ground.

#### 1.1.3 Port A (PA2..PA0)

Port A is a 3-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability, except PA2 which has the RESET capability. To use pin PA2 as I/O pin, instead of RESET pin, program ("0") RSTDISBL fuse. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port A also serves the functions of various special features of the ATtiny2313A/4313 as listed on page 61.

#### 1.1.4 Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATtiny2313A/4313 as listed on page 62.

#### 1.1.5 Port D (PD6..PD0)

Port D is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATtiny2313A/4313 as listed on page 66.

#### 1.1.6 **RESET**

Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running and provided that the reset pin has not been disabled. The minimum pulse length is given in Table 22-3 on page 201. Shorter pulses are not guaranteed to generate a reset. The Reset Input is an alternate function for PA2 and dW.

The reset pin can also be used as a (weak) I/O pin.

#### 1.1.7 XTAL1

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit. XTAL1 is an alternate function for PA0.

## 1.1.8 XTAL2

Output from the inverting Oscillator amplifier. XTAL2 is an alternate function for PA1.

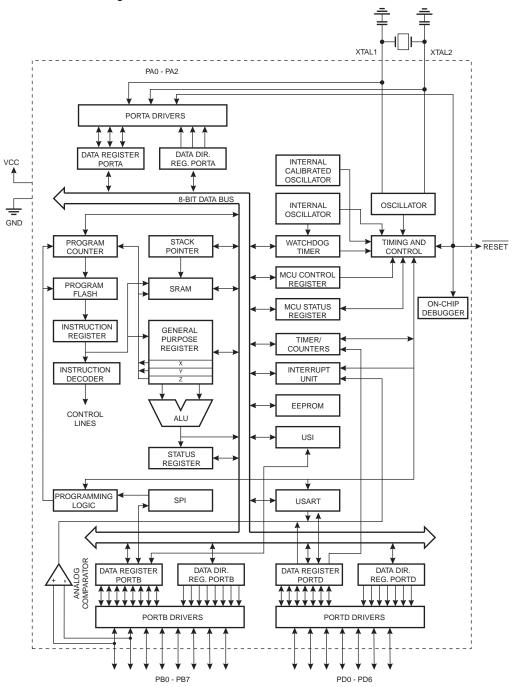

# 2. Overview

The ATtiny2313A/4313 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATtiny2313A/4313 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

# 2.1 Block Diagram

Figure 2-1. Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATtiny2313A/4313 provides the following features: 2/4K bytes of In-System Programmable Flash, 128/256 bytes EEPROM, 128/256 bytes SRAM, 18 general purpose I/O lines, 32 general purpose working registers, a single-wire Interface for On-chip Debugging, two flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, Universal Serial Interface with Start Condition Detector, a programmable Watchdog Timer with internal Oscillator, and three software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or hardware reset. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption.

The device is manufactured using Atmel's high density non-volatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, or by a conventional non-volatile memory programmer. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATtiny2313A/4313 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATtiny2313A/4313 AVR is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, In-Circuit Emulators, and Evaluation kits.

# 2.2 Comparison Between ATtiny2313A and ATtiny4313

The ATtiny2313A and ATtiny4313 differ only in memory sizes. Table 2-1 summarizes the different memory sizes for the two devices.

Table 2-1.Memory Size Summary

| Device      | Flash    | EEPROM    | RAM       |

|-------------|----------|-----------|-----------|

| ATtiny2313A | 2K Bytes | 128 Bytes | 128 Bytes |

| ATtiny4313  | 4K Bytes | 256 Bytes | 256 Bytes |

# 3. About

#### 3.1 Resources

A comprehensive set of drivers, application notes, data sheets and descriptions on development tools are available for download at http://www.atmel.com/avr.

# 3.2 Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

For I/O Registers located in the extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically, this means "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR". Note that not all AVR devices include an extended I/O map.

### 3.3 Data Retention

Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.

# ATtiny2313A/4313

Notes:

- 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. I/O Registers within the address range 0x00 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the status flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses.

# 5. Instruction Set Summary

| Mnemonics          | Operands          | Description                            | Operation                                                     | Flags      | #Clocks |

|--------------------|-------------------|----------------------------------------|---------------------------------------------------------------|------------|---------|

| ARITHMETIC AND L   | OGIC INSTRUCTIONS | 8                                      |                                                               |            |         |

| ADD                | Rd, Rr            | Add two Registers                      | $Rd \leftarrow Rd + Rr$                                       | Z,C,N,V,H  | 1       |

| ADC                | Rd, Rr            | Add with Carry two Registers           | $Rd \leftarrow Rd + Rr + C$                                   | Z,C,N,V,H  | 1       |

| ADIW               | Rdl,K             | Add Immediate to Word                  | Rdh:Rdl ← Rdh:Rdl + K                                         | Z,C,N,V,S  | 2       |

| SUB                | Rd, Rr            | Subtract two Registers                 | $Rd \leftarrow Rd - Rr$                                       | Z,C,N,V,H  | 1       |

| SUBI               | Rd, K             | Subtract Constant from Register        | $Rd \leftarrow Rd - K$                                        | Z,C,N,V,H  | 1       |

| SBC                | Rd, Rr            | Subtract with Carry two Registers      | $Rd \leftarrow Rd - Rr - C$                                   | Z,C,N,V,H  | 1       |

| SBCI               | Rd, K             | Subtract with Carry Constant from Reg. | $Rd \leftarrow Rd - K - C$                                    | Z,C,N,V,H  | 1       |

| SBIW               | Rdl,K             | Subtract Immediate from Word           | Rdh:Rdl ← Rdh:Rdl - K                                         | Z,C,N,V,S  | 2       |

| AND                | Rd, Rr            | Logical AND Registers                  | $Rd \leftarrow Rd \bullet Rr$                                 | Z,N,V      | 1       |

| ANDI               | Rd, K             | Logical AND Register and Constant      | $Rd \leftarrow Rd \bullet K$                                  | Z,N,V      | 1       |

| OR                 | Rd, Rr            | Logical OR Registers                   | $Rd \leftarrow Rd v Rr$                                       | Z,N,V      | 1       |

| ORI                | Rd, K             | Logical OR Register and Constant       | $Rd \leftarrow Rd \vee K$                                     | Z,N,V      | 1       |

| EOR                | Rd, Rr            | Exclusive OR Registers                 | $Rd \leftarrow Rd \oplus Rr$                                  | Z,N,V      | 1       |

| COM                | Rd                | One's Complement                       | $Rd \leftarrow 0xFF - Rd$                                     | Z,C,N,V    | 1       |

| NEG                | Rd                | Two's Complement                       | $Rd \leftarrow 0x00 - Rd$                                     | Z,C,N,V,H  | 1       |

| SBR                | Rd,K              | Set Bit(s) in Register                 | $Rd \leftarrow Rd \vee K$                                     | Z,N,V      | 1       |

| CBR                | Rd,K              | Clear Bit(s) in Register               | $Rd \leftarrow Rd \bullet (0xFF - K)$                         | Z,N,V      | 1       |

| INC                | Rd                | Increment                              | Rd ← Rd + 1                                                   | Z,N,V      | 1       |

| DEC                | Rd                | Decrement                              | Rd ← Rd – 1                                                   | Z,N,V      | 1       |

| TST                | Rd                | Test for Zero or Minus                 | $Rd \leftarrow Rd \bullet Rd$                                 | Z,N,V      | 1       |

| CLR                | Rd                | Clear Register                         | $Rd \leftarrow Rd \oplus Rd$                                  | Z,N,V      | 1       |

| SER                | Rd                | Set Register                           | $Rd \leftarrow 0xFF$                                          | None       | 1       |

| BRANCH INSTRUCT    | TIONS             |                                        |                                                               |            |         |

| RJMP               | k                 | Relative Jump                          | PC ← PC + k + 1                                               | None       | 2       |

| IJMP               |                   | Indirect Jump to (Z)                   | PC ← Z                                                        | None       | 2       |

| RCALL              | k                 | Relative Subroutine Call               | PC ← PC + k + 1                                               | None       | 3       |

| ICALL              |                   | Indirect Call to (Z)                   | PC ← Z                                                        | None       | 3       |

| RET                |                   | Subroutine Return                      | PC ← STACK                                                    | None       | 4       |

| RETI               |                   | Interrupt Return                       | PC ← STACK                                                    | 1          | 4       |

| CPSE               | Rd,Rr             | Compare, Skip if Equal                 | if (Rd = Rr) PC ← PC + 2 or 3                                 | None       | 1/2/3   |

| CP                 | Rd,Rr             | Compare                                | Rd – Rr                                                       | Z, N,V,C,H | 1       |

| CPC                | Rd,Rr             | Compare with Carry                     | Rd – Rr – C                                                   | Z, N,V,C,H | 1       |

| CPI                | Rd,K              | Compare Register with Immediate        | Rd – K                                                        | Z, N,V,C,H | 1       |

| SBRC               | Rr, b             | Skip if Bit in Register Cleared        | if (Rr(b)=0) PC ← PC + 2 or 3                                 | None       | 1/2/3   |

| SBRS               | Rr, b             | Skip if Bit in Register is Set         | if (Rr(b)=1) PC ← PC + 2 or 3                                 | None       | 1/2/3   |

| SBIC               | P, b              | Skip if Bit in I/O Register Cleared    | if (P(b)=0) PC ← PC + 2 or 3                                  | None       | 1/2/3   |

| SBIS               | P, b              | Skip if Bit in I/O Register is Set     | if (P(b)=1) PC ← PC + 2 or 3                                  | None       | 1/2/3   |

| BRBS               | s, k              | Branch if Status Flag Set              | if $(SREG(s) = 1)$ then $PC \leftarrow PC + k + 1$            | None       | 1/2     |

| BRBC               | s, k              | Branch if Status Flag Cleared          | if $(SREG(s) = 0)$ then $PC \leftarrow PC + k + 1$            | None       | 1/2     |

| BREQ               | k                 | Branch if Equal                        | if $(Z = 1)$ then PC $\leftarrow$ PC + k + 1                  | None       | 1/2     |

| BRNE               | k                 | Branch if Not Equal                    | if $(Z = 0)$ then PC $\leftarrow$ PC + k + 1                  | None       | 1/2     |

| BRCS               | k                 | Branch if Carry Set                    | if (C = 1) then PC $\leftarrow$ PC + k + 1                    | None       | 1/2     |

| BRCC               | k                 | Branch if Carry Cleared                | if (C = 0) then PC $\leftarrow$ PC + k + 1                    | None       | 1/2     |

| BRSH               | k                 | Branch if Same or Higher               | if (C = 0) then PC $\leftarrow$ PC + k + 1                    | None       | 1/2     |

| BRLO               | k                 | Branch if Lower                        | if (C = 1) then PC $\leftarrow$ PC + k + 1                    | None       | 1/2     |

| BRMI               | k                 | Branch if Minus                        | if $(N = 1)$ then $PC \leftarrow PC + k + 1$                  | None       | 1/2     |

| BRPL               | k                 | Branch if Plus                         | if $(N = 0)$ then $PC \leftarrow PC + k + 1$                  | None       | 1/2     |

| BRGE               | k                 | Branch if Greater or Equal, Signed     | if (N ⊕ V= 0) then PC ← PC + k + 1                            | None       | 1/2     |

| BRLT               | k                 | Branch if Less Than Zero, Signed       | if (N ⊕ V= 1) then PC ← PC + k + 1                            | None       | 1/2     |

| BRHS               | k                 | Branch if Half Carry Flag Set          | if (H = 1) then PC $\leftarrow$ PC + k + 1                    | None       | 1/2     |

| BRHC               | k                 | Branch if Half Carry Flag Cleared      | if (H = 0) then PC $\leftarrow$ PC + k + 1                    | None       | 1/2     |

| BRTS               | k                 | Branch if T Flag Set                   | if (T = 1) then PC ← PC + k + 1                               | None       | 1/2     |

| BRTC               | k                 | Branch if T Flag Cleared               | if (T = 0) then PC ← PC + k + 1                               | None       | 1/2     |

| BRVS               | k                 | Branch if Overflow Flag is Set         | if (V = 1) then PC ← PC + k + 1                               | None       | 1/2     |

| BRVC               | k                 | Branch if Overflow Flag is Cleared     | if (V = 0) then PC ← PC + k + 1                               | None       | 1/2     |

| BRIE               | k                 | Branch if Interrupt Enabled            | if ( I = 1) then PC ← PC + k + 1                              | None       | 1/2     |

| BRID               | k                 | Branch if Interrupt Disabled           | if ( I = 0) then PC ← PC + k + 1                              | None       | 1/2     |

| BIT AND BIT-TEST I |                   |                                        | T                                                             | T          | ı       |

| SBI                | P,b               | Set Bit in I/O Register                | I/O(P,b) ← 1                                                  | None       | 2       |

| CBI                | P,b               | Clear Bit in I/O Register              | I/O(P,b) ← 0                                                  | None       | 2       |

| LSL                | Rd                | Logical Shift Left                     | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                | Z,C,N,V    | 1       |

| LSR                | Rd                | Logical Shift Right                    | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                | Z,C,N,V    | 1       |

| ROL                | Rd                | Rotate Left Through Carry              | $Rd(0)\leftarrow C,Rd(n+1)\leftarrow Rd(n),C\leftarrow Rd(7)$ | Z,C,N,V    | 1       |

| ASR R SWAP R BSET S BCLR S BST R BLD R SEC CLC SEN CLN SEZ CLZ SEI CLZ SEI CLZ SEI CLY SES CLS SEV CLV SET CLT SEH CLT CLT SEH CLT SEH CLT CLT SEH CLT SEH CLT SEH CLT CLT SEH CLT SEH CLT SEL CLT SEH CLT SEL CLT SEH CLT SEL CLT SEH CLT SET CLT SEH                                     | s<br>Rr, b<br>Rd, b                      | Rotate Right Through Carry Arithmetic Shift Right Swap Nibbles Flag Set Flag Clear Bit Store from Register to T Bit load from T to Register Set Carry Clear Carry Clear Carry Set Negative Flag Clear Negative Flag Clear Plag Clear Zero Flag Clear Zero Flag Cloal Interrupt Disable Set Signed Test Flag Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Set Half Carry Flag in SREG | $ \begin{array}{c} Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0) \\ Rd(n) \leftarrow Rd(n+1), n=0.6 \\ Rd(30) \leftarrow Rd(74), Rd(74) \leftarrow Rd(30) \\ SREG(s) \leftarrow 1 \\ SREG(s) \leftarrow 0 \\ T \leftarrow Rr(b) \\ Rd(b) \leftarrow T \\ C \leftarrow 1 \\ C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ T \leftarrow 1 \end{array} $ | Z,C,N,V Z,C,N,V None SREG(s) SREG(s) T None C C N N I S S S S S S S S S S S S S S V V                                                       | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| ASR R SWAP R BSET S BCLR S BCLR S BST R BLD R SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLS SEV CLV SET CLT SEH CLH DATA TRANSFER INST MOV R MOVW R MOVW R LDI R LD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Rd Rd S S Rr, b Rd, b  STRUCTIONS Rd, Rr | Swap Nibbles Flag Set Flag Clear Bit Store from Register to T Bit load from T to Register Set Carry Clear Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                            | $ \begin{array}{c} Rd(n) \leftarrow Rd(n+1),  n=06 \\ Rd(30) \leftarrow Rd(74), Rd(74) \leftarrow Rd(30) \\ SREG(s) \leftarrow 1 \\ SREG(s) \leftarrow 0 \\ T \leftarrow Rr(b) \\ Rd(b) \leftarrow T \\ C \leftarrow 1 \\ C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ \end{array} $                                                                                    | Z,C,N,V None SREG(s) SREG(s) T None C C N N I I I I I S S V                                                                                 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| SWAP         R           BSET         s           BCLR         s           BST         R           BLD         R           SEC         C           CLC         SEN           CLN         SEZ           CLZ         SE           CLI         SES           CLI         SES           CLS         SEV           CLV         SET           CLT         SEH           CLH         DATA TRANSFER INST           MOV         R           MOVW         R           LD         R <t< td=""><td>Rd s s Rr, b Rd, b</td><td>Swap Nibbles Flag Set Flag Clear Bit Store from Register to T Bit load from T to Register Set Carry Clear Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG</td><td><math display="block"> \begin{array}{c} Rd(30) \leftarrow Rd(74), Rd(74) \leftarrow Rd(30) \\ SREG(s) \leftarrow 1 \\ SREG(s) \leftarrow 0 \\ T \leftarrow Rr(b) \\ Rd(b) \leftarrow T \\ C \leftarrow 1 \\ C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ \end{array} </math></td><td>  None   SREG(s)   SREG(s)   T   None   C   C   N   N   Z   Z   I   I   S   S   V   SREG(s)   T   SREG(s)   T   T   T   T   T   T   T   T   T  </td><td>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1</td></t<>                                                                                                                                                                | Rd s s Rr, b Rd, b                       | Swap Nibbles Flag Set Flag Clear Bit Store from Register to T Bit load from T to Register Set Carry Clear Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                            | $ \begin{array}{c} Rd(30) \leftarrow Rd(74), Rd(74) \leftarrow Rd(30) \\ SREG(s) \leftarrow 1 \\ SREG(s) \leftarrow 0 \\ T \leftarrow Rr(b) \\ Rd(b) \leftarrow T \\ C \leftarrow 1 \\ C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ \end{array} $                                                                                                                       | None   SREG(s)   SREG(s)   T   None   C   C   N   N   Z   Z   I   I   S   S   V   SREG(s)   T   SREG(s)   T   T   T   T   T   T   T   T   T | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| BSET         S           BCLR         S           BST         R           BLD         R           SEC         C           CLC         SEN           CLN         SEZ           CLZ         SEI           CLI         SES           CLI         SES           CLV         SET           CLT         SEH           CLT         SEH           CLH         DATA TRANSFER INST           MOVW         R           MOVW         R           LD         R <t< td=""><td>s s Rr, b Rd, b  STRUCTIONS Rd, Rr</td><td>Flag Set Flag Clear Bit Store from Register to T Bit load from T to Register Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG</td><td><math display="block">SREG(s) \leftarrow 1</math> <math display="block">SREG(s) \leftarrow 0</math> <math display="block">T \leftarrow Rr(b)</math> <math display="block">Rd(b) \leftarrow T</math> <math display="block">C \leftarrow 1</math> <math display="block">C \leftarrow 0</math> <math display="block">N \leftarrow 1</math> <math display="block">N \leftarrow 0</math> <math display="block">Z \leftarrow 1</math> <math display="block">Z \leftarrow 0</math> <math display="block">I \leftarrow 1</math> <math display="block">I \leftarrow 0</math> <math display="block">S \leftarrow 1</math> <math display="block">S \leftarrow 0</math> <math display="block">V \leftarrow 1</math> <math display="block">V \leftarrow 0</math></td><td>SREG(s) SREG(s) T None C C N N I I I I I S S S V</td><td>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1</td></t<> | s s Rr, b Rd, b  STRUCTIONS Rd, Rr       | Flag Set Flag Clear Bit Store from Register to T Bit load from T to Register Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                                                                                            | $SREG(s) \leftarrow 1$ $SREG(s) \leftarrow 0$ $T \leftarrow Rr(b)$ $Rd(b) \leftarrow T$ $C \leftarrow 1$ $C \leftarrow 0$ $N \leftarrow 1$ $N \leftarrow 0$ $Z \leftarrow 1$ $Z \leftarrow 0$ $I \leftarrow 1$ $I \leftarrow 0$ $S \leftarrow 1$ $S \leftarrow 0$ $V \leftarrow 1$ $V \leftarrow 0$                                                                                                                                                                                                                              | SREG(s) SREG(s) T None C C N N I I I I I S S S V                                                                                            | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| BCLR S BST R BLD R SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLL SES CLL SES CLL SES CLL SES CLL SET CLT SEH CLH DATA TRANSFER INST MOV R MOVW R LDI R LD R LD R LD R LD R LD R LD R L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | s<br>Rr, b<br>Rd, b                      | Flag Clear Bit Store from Register to T Bit load from T to Register Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Enable Set Signed Test Flag Set Signed Test Flag Set Tin SREG Clear T in SREG Set Half Carry Flag in SREG                                                                                                                                               | $\begin{array}{c} SREG(s) \leftarrow 0 \\ T \leftarrow Rr(b) \\ Rd(b) \leftarrow T \\ C \leftarrow 1 \\ C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ \end{array}$                                                                                                                                                                                                       | SREG(s) T None C C N N I I I I I S S V                                                                                                      | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| BST R BLD R SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLI SES CLS SEV CLV SET CLT SEH CLH DATA TRANSFER INST MOV R MOVW R LDI R LD R LD R LD R LD R LD R LD R L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Rr, b Rd, b  STRUCTIONS Rd, Rr           | Bit Store from Register to T Bit load from T to Register Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Set Half Carry Flag in SREG                                                                                                         | $ \begin{array}{c} T \leftarrow Rr(b) \\ Rd(b) \leftarrow T \\ C \leftarrow 1 \\ C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ \end{array} $                                                                                                                                                                                                                             | T None C C N N S S V                                                                                                                        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| BLD R SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLS SEV CLS SET CLT SEH CLH DATA TRANSFER INST MOV R MOVW R MOVW R LDI R LD R LD R LD R LD R LD R LD R L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Rd, b  TRUCTIONS Rd, Rr                  | Bit load from T to Register  Set Carry  Clear Carry  Set Negative Flag  Clear Negative Flag  Set Zero Flag  Clear Zero Flag  Clear Zero Flag  Global Interrupt Enable  Global Interrupt Disable  Set Signed Test Flag  Clear Signed Test Flag  Set Twos Complement Overflow.  Clear Twos Complement Overflow  Set T in SREG  Clear T in SREG  Set Half Carry Flag in SREG                                                                                      | $\begin{array}{c} Rd(b) \leftarrow T \\ C \leftarrow 1 \\ C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \end{array}$                                                                                                                                                                                                                                                        | None C C N N S Z Z I I S S S V                                                                                                              | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLI SES CLS SEV CLV SET CLT SEH CLH DATA TRANSFER INST MOV R MOVW R LDI R LD R LD R LD R LD R LD R LD R L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TRUCTIONS<br>Rd, Rr                      | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Set Half Carry Flag in SREG                                                                                                                                                                  | $\begin{array}{c} C \leftarrow 1 \\ C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \end{array}$                                                                                                                                                                                                                                                                              | C C N N N Z Z Z I I I S S S V                                                                                                               | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| CLC  SEN  CLN  SEZ  CLZ  SEI  CLI  SES  CLS  SEV  CLV  SET  CLT  SEH  CLH  DATA TRANSFER INST  MOV  R  MOVW  R  LDI  R  LD  R  R  LD  R  R  LD  R  R  R  R  R  R  R  R  R  R  R  R  R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Rd, Rr                                   | Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Set Half Carry Flag in SREG                                                                                                                                                                            | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \end{array}$                                                                                                                                                                                                                                                                                                | C N N Z Z I I S S S V                                                                                                                       | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| SEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Rd, Rr                                   | Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Set Half Carry Flag in SREG                                                                                                                                                                                        | $\begin{array}{c} N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \end{array}$                                                                                                                                                                                                                                                                                                                  | N N Z Z Z I I I S S S V                                                                                                                     | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| CLN  SEZ  CLZ  SEI  CLI  SES  CLS  SEV  CLV  SET  CLT  SEH  CLT  SEH  CLH  DATA TRANSFER INST  MOV  R  LD  LD  R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Rd, Rr                                   | Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                                                                                                                                                                                          | $\begin{array}{c} N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \end{array}$                                                                                                                                                                                                                                                                                                                                    | N Z Z I I I S S S V                                                                                                                         | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1  |

| SEZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Rd, Rr                                   | Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Z Z I I I S S S V                                                                                                                           | 1<br>1<br>1<br>1<br>1<br>1<br>1       |

| CLZ  SEI  CLI  SES  CLS  SEV  CLV  SET  CLT  SEH  CLH  DATA TRANSFER INST  MOV  R  MOVW  R  LDI  LD  R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Rd, Rr                                   | Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                                                                                                                                                                                                                            | $ \begin{array}{c} Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \end{array} $                                                                                                                                                                                                                                                                                                                                                                      | Z I I S V                                                                                                                                   | 1<br>1<br>1<br>1<br>1<br>1            |

| SEI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Rd, Rr                                   | Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                                                                                                                                                                                                                                            | I ← 1<br>I ← 0<br>S ← 1<br>S ← 0<br>V ← 1<br>V ← 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I<br>I<br>S<br>S<br>V                                                                                                                       | 1<br>1<br>1<br>1                      |

| CLI SES CLS SEV CLV SET CLT SEH CLH DATA TRANSFER INST MOV R MOVW R LDI R LD R LD R LD R LD R LD R LD R L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Rd, Rr                                   | Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                                                                                                                                                                                                                                                                    | I ← 0<br>S ← 1<br>S ← 0<br>V ← 1<br>V ← 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S<br>V                                                                                                                                      | 1<br>1<br>1<br>1                      |

| SES  CLS  SEV  CLV  SET  CLT  SEH  CLH  DATA TRANSFER INST  MOV  R  MOVW  R  LDI  LD  R  R  R  LD  R  R  R  R  R  R  R  R  R  R  R  R  R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Rd, Rr                                   | Set Signed Test Flag Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                                                                                                                                                                                                                                                                                             | S ← 1<br>S ← 0<br>V ← 1<br>V ← 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | S<br>V                                                                                                                                      | 1 1 1                                 |

| CLS  SEV  CLV  SET  CLT  SEH  CLH  DATA TRANSFER INST  MOV  R  MOVW  R  LDI  R  LD  R  R  LD  R  R  LD  R  R  LD  R  R  R  R  R  R  R  R  R  R  R  R  R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Rd, Rr                                   | Clear Signed Test Flag Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                                                                                                                                                                                                                                                                                                                  | S ← 0<br>V ← 1<br>V ← 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | S<br>V                                                                                                                                      | 1                                     |

| SEV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Rd, Rr                                   | Set Twos Complement Overflow. Clear Twos Complement Overflow Set T in SREG Clear T in SREG Set Half Carry Flag in SREG                                                                                                                                                                                                                                                                                                                                         | V ← 1<br>V ← 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V                                                                                                                                           | 1                                     |