Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFl

| Product Status          | Active                                                               |

|-------------------------|----------------------------------------------------------------------|

| Туре                    | Floating Point                                                       |

| Interface               | EBI/EMI, DAI, I <sup>2</sup> C, SPI, SPORT, UART/USART               |

| Clock Rate              | 266MHz                                                               |

| Non-Volatile Memory     | External                                                             |

| On-Chip RAM             | 3Mbit                                                                |

| Voltage - I/O           | 3.30V                                                                |

| Voltage - Core          | 1.10V                                                                |

| Operating Temperature   | -40°C ~ 125°C (TJ)                                                   |

| Mounting Type           | Surface Mount                                                        |

| Package / Case          | 176-LQFP Exposed Pad                                                 |

| Supplier Device Package | 176-LQFP-EP (24x24)                                                  |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/ad21488wbswz1a02 |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **GENERAL DESCRIPTION**

The ADSP-2148x SHARC<sup>®</sup> processors are members of the SIMD SHARC family of DSPs that feature Analog Devices' Super Harvard Architecture. The processors are source code compatible with the ADSP-2126x, ADSP-2136x, ADSP-2137x, ADSP-2146x, ADSP-2147x and ADSP-2116x DSPs, as well as with first generation ADSP-2106x SHARC processors in SISD (single-instruction, single-data) mode. The ADSP-2148x processors are 32-bit/40-bit floating point processors optimized for high performance audio applications with large on-chip SRAM, multiple internal buses to eliminate I/O bottlenecks, and an innovative digital applications interface (DAI).

Table 1 shows performance benchmarks for the ADSP-2148x processors. Table 2 shows the features of the individual product offerings.

#### Table 1. Processor Benchmarks

| Benchmark Algorithm                                | Speed<br>(at 400 MHz) | Speed<br>(at 450 MHz) |

|----------------------------------------------------|-----------------------|-----------------------|

| 1024 Point Complex FFT<br>(Radix 4, with Reversal) | 23 µs                 | 20.44 µs              |

| FIR Filter (per Tap) <sup>1</sup>                  | 1.25 ns               | 1.1 ns                |

| llR Filter (per Biquad) <sup>1</sup>               | 5 ns                  | 4.43 ns               |

| Matrix Multiply (Pipelined)                        |                       |                       |

| $[3 \times 3] \times [3 \times 1]$                 | 11.25 ns              | 10.0 ns               |

| $[4 \times 4] \times [4 \times 1]$                 | 20 ns                 | 17.78 ns              |

| Divide (y/×)                                       | 7.5 ns                | 6.67 ns               |

| Inverse Square Root                                | 11.25 ns              | 10.0 ns               |

<sup>1</sup>Assumes two files in multichannel SIMD mode

| Feature                                                      | ADSP-21483                  | ADSP-21486             | ADSP-21487            | ADSP-21488             | ADSP-21489                  |  |  |

|--------------------------------------------------------------|-----------------------------|------------------------|-----------------------|------------------------|-----------------------------|--|--|

| Maximum Instruction Rate                                     | 400 MHz                     | 400 MHz                | 450 MHz               | 400 MHz                | 450 MHz                     |  |  |

| RAM                                                          | 3 Mbits                     | 5                      | Mbits                 | 2/3 Mbits <sup>1</sup> | 5 Mbits                     |  |  |

| ROM                                                          |                             | 4 Mbits                |                       |                        | No                          |  |  |

| Audio Decoders in ROM <sup>2</sup>                           |                             | Yes                    |                       |                        | No                          |  |  |

| Pulse-Width Modulation                                       |                             | 4 Units (              | 3 Units on 100-Leac   | l Packages)            |                             |  |  |

| DTCP Hardware Accelerator                                    |                             | (                      | Contact Analog Dev    | ices                   |                             |  |  |

| External Port Interface (SDRAM, AMI) <sup>3</sup>            | Yes (16-bit)                | AMI Only               |                       | Yes (16-bit)           |                             |  |  |

| Serial Ports                                                 |                             |                        | 8                     |                        |                             |  |  |

| Direct DMA from SPORTs to External Port<br>(External Memory) |                             |                        | Yes                   |                        |                             |  |  |

| FIR, IIR, FFT Accelerator                                    | Yes                         |                        |                       |                        |                             |  |  |

| Watchdog Timer                                               | Yes (176-Lead Package Only) |                        |                       |                        |                             |  |  |

| MediaLB Interface                                            |                             | A                      | utomotive Models (    | Only                   |                             |  |  |

| IDP/PDAP                                                     |                             |                        | Yes                   |                        |                             |  |  |

| UART                                                         | 1                           |                        |                       |                        |                             |  |  |

| DAI (SRU)/DPI (SRU2)                                         | Yes                         |                        |                       |                        |                             |  |  |

| S/PDIF Transceiver                                           |                             |                        | Yes                   |                        |                             |  |  |

| SPI                                                          |                             |                        | Yes                   |                        |                             |  |  |

| TWI                                                          |                             |                        | 1                     |                        |                             |  |  |

| SRC Performance <sup>4</sup>                                 |                             |                        | –128 dB               |                        |                             |  |  |

| Thermal Diode                                                | Yes                         |                        |                       |                        |                             |  |  |

| VISA Support                                                 |                             |                        | Yes                   |                        |                             |  |  |

| Package <sup>3</sup>                                         |                             | LQFP EPAD<br>LQFP EPAD | 176-Lead LQFP<br>EPAD |                        | d LQFP EPAD<br>I LQFP EPAD⁵ |  |  |

#### Table 2. ADSP-2148x Family Features

<sup>1</sup>See Ordering Guide on Page 66.

<sup>4</sup>Some models have –140 dB performance. For more information, see Ordering Guide on page 66.

<sup>5</sup>Only available up to 400 MHz. See Ordering Guide on Page 66 for details.

<sup>&</sup>lt;sup>2</sup> ROM is factory programmed with latest multichannel audio decoding and post-processing algorithms from Dolby<sup>®</sup> Labs and DTS<sup>®</sup>. Decoder/post-processor algorithm combination support varies depending upon the chip version and the system configurations. Please visit www.analog.com for complete information.

<sup>&</sup>lt;sup>3</sup> The 100-lead packages do not contain an external port. The SDRAM controller pins must be disabled when using this package. For more information, see Pin Function Descriptions on Page 14. The ADSP-21486 processor in the 176-lead package also does not contain a SDRAM controller. For more information, see 176-Lead LQFP\_EP Lead Assignment on page 60.

The diagram on Page 1 shows the two clock domains that make up the ADSP-2148x processors. The core clock domain contains the following features:

- Two processing elements (PEx, PEy), each of which comprises an ALU, multiplier, shifter, and data register file

- Data address generators (DAG1, DAG2)

- Program sequencer with instruction cache

- PM and DM buses capable of supporting 2x64-bit data transfers between memory and the core at every core processor cycle

- One periodic interval timer with pinout

- On-chip SRAM (5 Mbit) and mask-programmable ROM (4 Mbit)

- JTAG test access port for emulation and boundary scan. The JTAG provides software debug through user breakpoints which allows flexible exception handling.

The block diagram of the ADSP-2148x on Page 1 also shows the peripheral clock domain (also known as the I/O processor) which contains the following features:

- IOD0 (peripheral DMA) and IOD1 (external port DMA) buses for 32-bit data transfers

- Peripheral and external port buses for core connection

- External port with an AMI and SDRAM controller

- 4 units for PWM control

- 1 memory-to-memory (MTM) unit for internal-to-internal memory transfers

- Digital applications interface that includes four precision clock generators (PCG), an input data port (IDP/PDAP) for serial and parallel interconnects, an S/PDIF receiver/transmitter, four asynchronous sample rate converters, eight serial ports, and a flexible signal routing unit (DAI SRU).

- Digital peripheral interface that includes two timers, a 2-wire interface (TWI), one UART, two serial peripheral interfaces (SPI), 2 precision clock generators (PCG), pulse width modulation (PWM), and a flexible signal routing unit (DPI SRU2).

As shown in the SHARC core block diagram on Page 5, the processor uses two computational units to deliver a significant performance increase over the previous SHARC processors on a range of DSP algorithms. With its SIMD computational hardware, the processors can perform 2.7 GFLOPS running at 450 MHz.

# FAMILY CORE ARCHITECTURE

The ADSP-2148x is code compatible at the assembly level with the ADSP-2147x, ADSP-2146x, ADSP-2137x, ADSP-2136x, ADSP-2126x, ADSP-21160, and ADSP-21161, and with the first generation ADSP-2106x SHARC processors. The ADSP-2148x shares architectural features with the ADSP-2126x, ADSP-2136x, ADSP-2137x, ADSP-2146x and ADSP-2116x SIMD SHARC processors, as shown in Figure 2 and detailed in the following sections.

### SIMD Computational Engine

The ADSP-2148x contains two computational processing elements that operate as a single-instruction, multiple-data (SIMD) engine. The processing elements are referred to as PEX and PEY and each contains an ALU, multiplier, shifter, and register file. PEx is always active, and PEy may be enabled by setting the PEYEN mode bit in the MODE1 register. SIMD mode allows the processor to execute the same instruction in both processing elements, but each processing element operates on different data. This architecture is efficient at executing math intensive DSP algorithms.

SIMD mode also affects the way data is transferred between memory and the processing elements because twice the data bandwidth is required to sustain computational operation in the processing elements. Therefore, entering SIMD mode also doubles the bandwidth between memory and the processing elements. When using the DAGs to transfer data in SIMD mode, two data values are transferred with each memory or register file access.

### Independent, Parallel Computation Units

Within each processing element is a set of computational units. The computational units consist of an arithmetic/logic unit (ALU), multiplier, and shifter. These units perform all operations in a single cycle and are arranged in parallel, maximizing computational throughput. Single multifunction instructions execute parallel ALU and multiplier operations. In SIMD mode, the parallel ALU and multiplier operations occur in both processing elements. These computation units support IEEE 32-bit single-precision floating-point, 40-bit extended precision floating-point, and 32-bit fixed-point data formats.

### Timer

The processor contains a core timer that can generate periodic software interrupts. The core timer can be configured to use FLAG3 as a timer expired signal.

### Data Register File

Each processing element contains a general-purpose data register file. The register files transfer data between the computation units and the data buses, and store intermediate results. These 10-port, 32-register (16 primary, 16 secondary) register files, combined with the processor's enhanced Harvard architecture, allow unconstrained data flow between computation units and internal memory. The registers in PEX are referred to as R0–R15 and in PEY as S0–S15.

### **Context Switch**

Many of the processor's registers have secondary registers that can be activated during interrupt servicing for a fast context switch. The data registers in the register file, the DAG registers, and the multiplier result registers all have secondary registers. The primary registers are active at reset, while the secondary registers are activated by control bits in a mode control register.

Figure 2. SHARC Core Block Diagram

#### **Universal Registers**

These registers can be used for general-purpose tasks. The USTAT (4) registers allow easy bit manipulations (Set, Clear, Toggle, Test, XOR) for all peripheral registers (control/status).

The data bus exchange register (PX) permits data to be passed between the 64-bit PM data bus and the 64-bit DM data bus, or between the 40-bit register file and the PM/DM data bus. These registers contain hardware to handle the data width difference.

#### Single-Cycle Fetch of Instruction and Four Operands

The ADSP-2148x features an enhanced Harvard architecture in which the data memory (DM) bus transfers data and the program memory (PM) bus transfers both instructions and data. With the its separate program and data memory buses and onchip instruction cache, the processor can simultaneously fetch four operands (two over each data bus) and one instruction (from the cache), all in a single cycle.

#### Instruction Cache

The processor includes an on-chip instruction cache that enables three-bus operation for fetching an instruction and four data values. The cache is selective—only the instructions whose fetches conflict with PM bus data accesses are cached. This cache allows full speed execution of core, looped operations such as digital filter multiply-accumulates, and FFT butterfly processing.

### Data Address Generators With Zero-Overhead Hardware Circular Buffer Support

The two data address generators (DAGs) are used for indirect addressing and implementing circular data buffers in hardware. Circular buffers allow efficient programming of delay lines and other data structures required in digital signal processing, and are commonly used in digital filters and Fourier transforms. The two DAGs contain sufficient registers to allow the creation of up to 32 circular buffers (16 primary register sets, 16 secondary). The DAGs automatically handle address pointer wraparound, reduce overhead, increase performance, and simplify implementation. Circular buffers can start and end at any memory location.

#### Flexible Instruction Set

The 48-bit instruction word accommodates a variety of parallel operations, for concise programming. For example, the processor can conditionally execute a multiply, an add, and a

• Arbitration logic to coordinate core and DMA transfers between internal and external memory over the external port.

Non-SDRAM external memory address space is shown in Table 5.

| Table 5. External Memory for Non-SDRAM Addresses | Table 5. | External Memo | ory for Non-SDRAM Addresses |

|--------------------------------------------------|----------|---------------|-----------------------------|

|--------------------------------------------------|----------|---------------|-----------------------------|

| Bank   | Size in<br>Words | Address Range           |

|--------|------------------|-------------------------|

| Bank 0 | 6M               | 0x0020 0000–0x007F FFFF |

| Bank 1 | 8M               | 0x0400 0000-0x047F FFFF |

| Bank 2 | 8M               | 0x0800 0000-0x087F FFFF |

| Bank 3 | 8M               | 0x0C00 0000-0x0C7F FFFF |

### **External Port**

The external port provides a high performance, glueless interface to a wide variety of industry-standard memory devices. The external port, available on the 176-lead LQFP, may be used to interface to synchronous and/or asynchronous memory devices through the use of its separate internal memory controllers. The first is an SDRAM controller for connection of industry-standard synchronous DRAM devices while the second is an asynchronous memory controller intended to interface to a variety of memory devices. Four memory select pins enable up to four separate devices to coexist, supporting any desired combination of synchronous and asynchronous device types.

#### Asynchronous Memory Controller

The asynchronous memory controller provides a configurable interface for up to four separate banks of memory or I/O devices. Each bank can be independently programmed with different timing parameters, enabling connection to a wide variety of memory devices including SRAM, flash, and EPROM, as well as I/O devices that interface with standard memory control lines. Bank 0 occupies a 6M word window and banks 1, 2, and 3 occupy a 8M word window in the processor's address space but, if not fully populated, these windows are not made contiguous by the memory controller logic.

#### **SDRAM Controller**

The SDRAM controller provides an interface of up to four separate banks of industry-standard SDRAM devices at speeds up to  $f_{SDCLK}$ . Fully compliant with the SDRAM standard, each bank has its own memory select line ( $\overline{MS0}$ – $\overline{MS3}$ ), and can be configured to contain between 4M bytes and 256M bytes of memory. SDRAM external memory address space is shown in Table 6. NOTE: this feature is not available on the ADSP-21486 model.

| Table 6. | External | Memory | for S | DRAM | Addresses |

|----------|----------|--------|-------|------|-----------|

|----------|----------|--------|-------|------|-----------|

| Bank   | Size in<br>Words | Address Range           |

|--------|------------------|-------------------------|

| Bank 0 | 62M              | 0x0020 0000-0x03FF FFFF |

| Bank 1 | 64M              | 0x0400 0000-0x07FF FFFF |

| Bank 2 | 64M              | 0x0800 0000-0x0BFF FFFF |

| Bank 3 | 64M              | 0x0C00 0000-0x0FFF FFFF |

A set of programmable timing parameters is available to configure the SDRAM banks to support slower memory devices. Note that 32-bit wide devices are not supported on the SDRAM and AMI interfaces.

The SDRAM controller address, data, clock, and control pins can drive loads up to distributed 30 pF. For larger memory systems, the SDRAM controller external buffer timing should be selected and external buffering should be provided so that the load on the SDRAM controller pins does not exceed 30 pF.

Note that the external memory bank addresses shown are for normal-word (32-bit) accesses. If 48-bit instructions as well as 32-bit data are both placed in the same external memory bank, care must be taken while mapping them to avoid overlap.

#### SIMD Access to External Memory

The SDRAM controller on the processor supports SIMD access on the 64-bit EPD (external port data bus) which allows access to the complementary registers on the PEy unit in the normal word space (NW). This removes the need to explicitly access the complimentary registers when the data is in external SDRAM memory.

#### VISA and ISA Access to External Memory

The SDRAM controller on the ADSP-2148x processors supports VISA code operation which reduces the memory load since the VISA instructions are compressed. Moreover, bus fetching is reduced because, in the best case, one 48-bit fetch contains three valid instructions. Code execution from the traditional ISA operation is also supported. Note that code execution is only supported from bank 0 regardless of VISA/ISA. Table 7 shows the address ranges for instruction fetch in each mode.

#### Table 7. External Bank 0 Instruction Fetch

| Access Type | Size in<br>Words | Address Range           |

|-------------|------------------|-------------------------|

| ISA (NW)    | 4M               | 0x0020 0000-0x005F FFFF |

| VISA (SW)   | 10M              | 0x0060 0000-0x00FF FFFF |

#### **Pulse-Width Modulation**

The PWM module is a flexible, programmable, PWM waveform generator that can be programmed to generate the required switching patterns for various applications related to motor and engine control or audio power control. The PWM generator can generate either center-aligned or edge-aligned PWM waveforms. In addition, it can generate complementary signals on two outputs in paired mode or independent signals in nonpaired mode (applicable to a single group of four PWM waveforms).

The entire PWM module has four groups of four PWM outputs generating 16 PWM outputs in total. Each PWM group produces two pairs of PWM signals on the four PWM outputs.

### **Middleware Packages**

Analog Devices separately offers middleware add-ins such as real time operating systems, file systems, USB stacks, and TCP/IP stacks. For more information see the following web pages:

- www.analog.com/ucos3

- www.analog.com/ucfs

- www.analog.com/ucusbd

- www.analog.com/lwip

### **Algorithmic Modules**

To speed development, Analog Devices offers add-ins that perform popular audio and video processing algorithms. These are available for use with both CrossCore Embedded Studio and VisualDSP++. For more information visit www.analog.com and search on "Blackfin software modules" or "SHARC software modules".

#### Designing an Emulator-Compatible DSP Board (Target)

For embedded system test and debug, Analog Devices provides a family of emulators. On each JTAG DSP, Analog Devices supplies an IEEE 1149.1 JTAG Test Access Port (TAP). In-circuit emulation is facilitated by use of this JTAG interface. The emulator accesses the processor's internal features via the processor's TAP, allowing the developer to load code, set breakpoints, and view variables, memory, and registers. The processor must be halted to send data and commands, but once an operation is completed by the emulator, the DSP system is set to run at full speed with no impact on system timing. The emulators require the target board to include a header that supports connection of the DSP's JTAG port to the emulator.

For details on target board design issues including mechanical layout, single processor connections, signal buffering, signal termination, and emulator pod logic, see Analog Devices JTAG Emulation Technical Reference (EE-68). This document is updated regularly to keep pace with improvements to emulator support.

## **ADDITIONAL INFORMATION**

This data sheet provides a general overview of the ADSP-2148x architecture and functionality. For detailed information on the ADSP-2148x family core architecture and instruction set, refer to the programming reference manual.

## **RELATED SIGNAL CHAINS**

A signal chain is a series of signal-conditioning electronic components that receive input (data acquired from sampling either real-time phenomena or from stored data) in tandem, with the output of one portion of the chain supplying input to the next. Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on analysis of real-time phenomena. Analog Devices eases signal processing system development by providing signal processing components that are designed to work together well. A tool for viewing relationships between specific applications and related components is available on the www.analog.com website.

The application signal chains page in the Circuits from the Lab<sup>®</sup> site (http://www.analog.com/circuits) provides:

- Graphical circuit block diagram presentation of signal chains for a variety of circuit types and applications

- Drill down links for components in each chain to selection guides and application information

- Reference designs applying best practice design techniques

#### Table 11. Pin Descriptions (Continued)

| Nama                | <b>T</b>                                       | State<br>During/ | Description                                                                                                                                                                                                                                                                                                           |

|---------------------|------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                | Туре                                           | After Reset      | Description                                                                                                                                                                                                                                                                                                           |

| MLBCLK <sup>1</sup> |                                                |                  | <b>Media Local Bus Clock.</b> This clock is generated by the MLB controller that is synchro-<br>nized to the MOST network and provides the timing for the entire MLB interface at<br>49.152 MHz at FS=48 kHz. When the MLB controller is not used, this pin should be<br>grounded.                                    |

| MLBDAT <sup>1</sup> | I/O/T in 3<br>pin mode. I<br>in 5 pin<br>mode. | High-Z           | <b>Media Local Bus Data.</b> The MLBDAT line is driven by the transmitting MLB device and is received by all other MLB devices including the MLB controller. The MLBDAT line carries the actual data. In 5-pin MLB mode, this pin is an input only. When the MLB controller is not used, this pin should be grounded. |

| MLBSIG <sup>1</sup> | I/O/T in 3<br>pin mode. I<br>in 5 pin<br>mode  | High-Z           | <b>Media Local Bus Signal.</b> This is a multiplexed signal which carries the Channel/Address generated by the MLB Controller, as well as the Command and RxStatus bytes from MLB devices. In 5-pin mode, this pin is input only. When the MLB controller is not used, this pin should be grounded.                   |

| MLBDO <sup>1</sup>  | 0/Т                                            | High-Z           | <b>Media Local Bus Data Output (in 5 pin mode).</b> This pin is used only in 5-pin MLB mode.<br>This serves as the output data pin in 5-pin mode. When the MLB controller is not used, this pin should be connected to ground.                                                                                        |

| MLBSO <sup>1</sup>  | 0/Т                                            | High-Z           | <b>Media Local Bus Signal Output (in 5 pin mode).</b> This pin is used only in 5-pin MLB mode. This serves as the output signal pin in 5-pin mode. When the MLB controller is not used, this pin should be connected to ground.                                                                                       |

| TDI                 | l (ipu)                                        |                  | Test Data Input (JTAG). Provides serial data for the boundary scan logic.                                                                                                                                                                                                                                             |

| TDO                 | O/T                                            | High-Z           | Test Data Output (JTAG). Serial scan output of the boundary scan path.                                                                                                                                                                                                                                                |

| TMS                 | l (ipu)                                        |                  | Test Mode Select (JTAG). Used to control the test state machine.                                                                                                                                                                                                                                                      |

| ТСК                 | 1                                              |                  | <b>Test Clock (JTAG).</b> Provides a clock for JTAG boundary scan. TCK must be asserted (pulsed low) after power-up or held low for proper operation of the device.                                                                                                                                                   |

| TRST                | l (ipu)                                        |                  | <b>Test Reset (JTAG).</b> Resets the test state machine. TRST must be asserted (pulsed low) after power-up or held low for proper operation of the processor.                                                                                                                                                         |

| EMU                 | O (O/D, ipu)                                   | High-Z           | <b>Emulation Status.</b> Must be connected to the ADSP-2148x Analog Devices DSP Tools product line of JTAG emulators target board connector only.                                                                                                                                                                     |

The following symbols appear in the Type column of this table:  $\mathbf{A} = asynchronous$ ,  $\mathbf{I} = input$ ,  $\mathbf{O} = output$ ,  $\mathbf{S} = synchronous$ ,  $\mathbf{A}/\mathbf{D} = active drive$ ,  $\mathbf{O}/\mathbf{D} = open drain$ , and  $\mathbf{T} = three-state$ ,  $\mathbf{ipd} = internal pull-down resistor$ ,  $\mathbf{ipu} = internal pull-up resistor$ .

The internal pull-up (ipu) and internal pull-down (ipd) resistors are designed to hold the internal path from the pins at the expected logic levels. To pull-up or pull-down the external pads to the expected logic levels, use external resistors. Internal pull-up/pull-down resistors cannot be enabled/disabled and the value of these resistors cannot be programmed. The range of an ipu resistor can be between  $26 \text{ k}\Omega - 63 \text{ k}\Omega$ . The range of an ipd resistor can be between  $31 \text{ k}\Omega - 85 \text{ k}\Omega$ . The three-state voltage of ipu pads will not reach to the full V<sub>DD\_EXT</sub> level; at typical conditions the voltage is in the range of 2.3 V to 2.7 V.

In this table, all pins are LVTTL compliant with the exception of the thermal diode pins.

## **ELECTRICAL CHARACTERISTICS**

|                                   |                                          |                                                                           |     | 300 MHz / 350 MHz / 400 MH | lz / 450 MHz                 |      |

|-----------------------------------|------------------------------------------|---------------------------------------------------------------------------|-----|----------------------------|------------------------------|------|

| Parameter <sup>1</sup>            | Description                              | Test Conditions                                                           | Min | Тур                        | Max                          | Unit |

| V <sub>OH</sub> <sup>2</sup>      | High Level Output<br>Voltage             | @ $V_{DD\_EXT} = Min$ ,<br>$I_{OH} = -1.0 \text{ mA}^3$                   | 2.4 |                            |                              | V    |

| V <sub>OL</sub> <sup>2</sup>      | Low Level Output<br>Voltage              | @ $V_{DD\_EXT} = Min$ ,<br>$I_{OL} = 1.0 \text{ mA}^3$                    |     |                            | 0.4                          | v    |

| I <sub>IH</sub> <sup>4, 5</sup>   | High Level Input Current                 | @ V <sub>DD_EXT</sub> = Max,<br>V <sub>IN</sub> = V <sub>DD_EXT</sub> Max |     |                            | 10                           | μΑ   |

| I <sub>IL</sub> <sup>4</sup>      | Low Level Input Current                  | $@V_{DD_{EXT}} = Max, V_{IN} = 0 V$                                       |     |                            | 10                           | μA   |

| I <sub>ILPU</sub> <sup>5</sup>    | Low Level Input Current<br>Pull-up       | $@V_{DD_{EXT}} = Max, V_{IN} = 0 V$                                       |     |                            | 200                          | μA   |

| I <sub>OZH</sub> <sup>6, 7</sup>  | Three-State Leakage<br>Current           | @ V <sub>DD_EXT</sub> = Max,<br>V <sub>IN</sub> = V <sub>DD_EXT</sub> Max |     |                            | 10                           | μA   |

| I <sub>OZL</sub> <sup>6</sup>     | Three-State Leakage<br>Current           | $@V_{DD_{EXT}} = Max, V_{IN} = 0 V$                                       |     |                            | 10                           | μA   |

| I <sub>OZLPU</sub> <sup>7</sup>   | Three-State Leakage<br>Current Pull-up   | $@V_{DD_{EXT}} = Max, V_{IN} = 0 V$                                       |     |                            | 200                          | μA   |

| I <sub>OZHPD</sub> <sup>8</sup>   | Three-State Leakage<br>Current Pull-down | @ V <sub>DD_EXT</sub> = Max,<br>V <sub>IN</sub> = V <sub>DD_EXT</sub> Max |     |                            | 200                          | μA   |

| I <sub>DD_INT</sub> 9             | Supply Current (Internal)                | f <sub>CCLK</sub> > 0 MHz                                                 |     |                            | Table 14 + Table 15<br>× ASF | mA   |

| I <sub>DD_INT</sub>               | Supply Current (Internal)                | $V_{DDINT} = 1.1 \text{ V, ASF} = 1,$<br>T <sub>J</sub> = 25°C            |     | 410 / 450 / 500 / 550      |                              | mA   |

| C <sub>IN</sub> <sup>10, 11</sup> | Input Capacitance                        | T <sub>CASE</sub> = 25°C                                                  |     |                            | 5                            | pF   |

<sup>1</sup> Specifications subject to change without notice.

<sup>2</sup> Applies to output and bidirectional pins: ADDR23-0, DATA15-0, <u>AMI\_RD</u>, <u>AMI\_WR</u>, FLAG3-0, DAI\_Px, DPI\_Px, <u>EMU</u>, TDO, <u>RESETOUT</u> MLBSIG, MLBDAT, MLBDO, MLBSO, <u>SDRAS</u>, <u>SDCAS</u>, <u>SDWE</u>, SDCKE, SDA10, SDDQM, <u>MS0-1</u>.

<sup>3</sup>See Output Drive Currents on Page 55 for typical drive current capabilities.

<sup>4</sup>Applies to input pins: BOOT\_CFGx, CLK\_CFGx, TCK, RESET, CLKIN.

<sup>5</sup> Applies to input pins with internal pull-ups: TRST, TMS, TDI.

<sup>6</sup>Applies to three-statable pin: TDO.

<sup>7</sup>Applies to three-statable pins with pull-ups: DAI\_Px, DPI\_Px, EMU.

<sup>8</sup>Applies to three-statable pin with pull-down: SDCLK.

<sup>9</sup>See Engineer-to-Engineer Note Estimating Power for ADSP-214xx SHARC Processors (EE-348) for further information.

<sup>10</sup>Applies to all signal pins.

<sup>11</sup>Guaranteed, but not tested.

#### **Total Power Dissipation**

The information in this section should be augmented with the Engineer-to-Engineer Note Estimating Power for ADSP-214xx SHARC Processors (EE-348).

Total power dissipation has two components:

- 1. Internal power consumption is additionally comprised of two components:

- Static current due to leakage. Table 14 shows the static current consumption ( $I_{DD\_INT\_STATIC}$ ) as a function of junction temperature ( $T_J$ ) and core voltage ( $V_{DD\_INT}$ ).

- Dynamic current ( $I_{DD\_INT\_DYNAMIC}$ ), due to transistor switching characteristics and activity level of the processor. The activity level is reflected by the Activity Scaling Factor (ASF), which represents the activity level of the application code running on the processor core and having various levels of peripheral and external port activity (Table 13).

Dynamic current consumption is calculated by selecting the ASF that corresponds most closely with the user application and then multiplying that with the dynamic current consumption (Table 15).

2. External power consumption is due to the switching activity of the external pins.

| Activity                          | Scaling Factor (ASF) |

|-----------------------------------|----------------------|

| ldle                              | 0.29                 |

| Low                               | 0.53                 |

| Medium Low                        | 0.61                 |

| Medium High                       | 0.77                 |

| Peak Typical (50:50) <sup>2</sup> | 0.85                 |

| Peak Typical (60:40) <sup>2</sup> | 0.93                 |

| Peak Typical (70:30) <sup>2</sup> | 1.00                 |

| High Typical                      | 1.16                 |

| High                              | 1.25                 |

| Peak                              | 1.31                 |

Table 13. Activity Scaling Factors (ASF)<sup>1</sup>

<sup>1</sup>See the Engineer-to-Engineer Note Estimating Power for ADSP-214xx SHARC Processors (EE-348) for more information on the explanation of the power vectors specific to the ASF table.

<sup>2</sup> Ratio of continuous instruction loop (core) to SDRAM control code reads and writes.

| (°C) رT | V <sub>DD_INT</sub> (V) |       |         |        |         |        |         |        |         |  |

|---------|-------------------------|-------|---------|--------|---------|--------|---------|--------|---------|--|

|         | 0.975 V                 | 1.0 V | 1.025 V | 1.05 V | 1.075 V | 1.10 V | 1.125 V | 1.15 V | 1.175 V |  |

| -45     | 68                      | 77    | 86      | 96     | 107     | 118    | 131     | 144    | 159     |  |

| -35     | 74                      | 83    | 92      | 103    | 114     | 126    | 140     | 154    | 170     |  |

| -25     | 82                      | 92    | 101     | 113    | 125     | 138    | 153     | 168    | 185     |  |

| -15     | 94                      | 104   | 115     | 127    | 140     | 155    | 171     | 187    | 205     |  |

| -5      | 109                     | 121   | 133     | 147    | 161     | 177    | 194     | 212    | 233     |  |

| +5      | 129                     | 142   | 156     | 171    | 188     | 206    | 225     | 245    | 268     |  |

| +15     | 152                     | 168   | 183     | 201    | 219     | 240    | 261     | 285    | 309     |  |

| +25     | 182                     | 199   | 216     | 237    | 257     | 280    | 305     | 331    | 360     |  |

| +35     | 217                     | 237   | 256     | 279    | 303     | 329    | 358     | 388    | 420     |  |

| +45     | 259                     | 282   | 305     | 331    | 359     | 389    | 421     | 455    | 492     |  |

| +55     | 309                     | 334   | 361     | 391    | 423     | 458    | 495     | 533    | 576     |  |

| +65     | 369                     | 398   | 429     | 464    | 500     | 539    | 582     | 626    | 675     |  |

| +75     | 437                     | 471   | 506     | 547    | 588     | 633    | 682     | 731    | 789     |  |

| +85     | 519                     | 559   | 599     | 645    | 693     | 746    | 802     | 860    | 926     |  |

| +95     | 615                     | 662   | 707     | 761    | 816     | 877    | 942     | 1007   | 1083    |  |

| +105    | 727                     | 779   | 833     | 897    | 958     | 1026   | 1103    | 1179   | 1266    |  |

| +115    | 853                     | 914   | 975     | 1047   | 1119    | 1198   | 1285    | 1372   | 1473    |  |

| +125    | 997                     | 1067  | 1138    | 1219   | 1305    | 1397   | 1498    | 1601   | 1716    |  |

#### Table 14. Static Current—I<sub>DD\_INT\_STATIC</sub> (mA)<sup>1</sup>

<sup>1</sup>Valid temperature and voltage ranges are model-specific. See Operating Conditions on Page 18.

| f <sub>CCLK</sub><br>(MHz) | V <sub>DD_INT</sub> (V) |       |         |        |         |        |         |        |         |  |

|----------------------------|-------------------------|-------|---------|--------|---------|--------|---------|--------|---------|--|

|                            | 0.975 V                 | 1.0 V | 1.025 V | 1.05 V | 1.075 V | 1.10 V | 1.125 V | 1.15 V | 1.175 V |  |

| 100                        | 76                      | 77    | 81      | 84     | 87      | 88     | 90      | 92     | 95      |  |

| 150                        | 117                     | 119   | 123     | 126    | 130     | 133    | 136     | 139    | 144     |  |

| 200                        | 153                     | 156   | 161     | 165    | 170     | 174    | 179     | 183    | 188     |  |

| 250                        | 190                     | 195   | 201     | 207    | 212     | 217    | 223     | 229    | 235     |  |

| 300                        | 227                     | 233   | 240     | 246    | 253     | 260    | 266     | 273    | 280     |  |

| 350                        | 263                     | 272   | 278     | 286    | 294     | 302    | 309     | 318    | 325     |  |

| 400                        | 300                     | 309   | 317     | 326    | 335     | 344    | 352     | 361    | 370     |  |

| 450                        | 339                     | 349   | 356     | 365    | 374     | 385    | 394     | 405    | 415     |  |

Table 15. Dynamic Current in CCLK Domain $-I_{DD_{INT}_{DYNAMIC}}$  (mA, with ASF = 1.0)<sup>1, 2</sup>

<sup>1</sup>The values are not guaranteed as standalone maximum specifications. They must be combined with static current per the equations of Electrical Characteristics on Page 19. <sup>2</sup>Valid frequency and voltage ranges are model-specific. See Operating Conditions on Page 18.

### **ABSOLUTE MAXIMUM RATINGS**

Stresses at or above those listed in Table 16 may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### Table 16. Absolute Maximum Ratings

| Parameter                                             | Rating                         |

|-------------------------------------------------------|--------------------------------|

| Internal (Core) Supply Voltage (V <sub>DD_INT</sub> ) | –0.3 V to +1.32 V              |

| External (I/O) Supply Voltage (V <sub>DD_EXT</sub> )  | –0.3 V to +3.6 V               |

| Thermal Diode Supply Voltage                          | –0.3 V to +3.6 V               |

| (V <sub>DD_THD</sub> )                                |                                |

| Input Voltage                                         | –0.5 V to +3.6 V               |

| Output Voltage Swing                                  | –0.5 V to $V_{DD\_EXT}$ +0.5 V |

| Storage Temperature Range                             | –65°C to +150°C                |

| Junction Temperature While Biased                     | 125°C                          |

## **ESD SENSITIVITY**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### MAXIMUM POWER DISSIPATION

See Engineer-to-Engineer Note Estimating Power for ADSP-214xx SHARC Processors (EE-348) for detailed thermal and power information regarding maximum power dissipation. For information on package thermal specifications, see Thermal Characteristics on Page 56.

## **PACKAGE INFORMATION**

The information presented in Figure 3 provides details about the package branding for the ADSP-2148x processors. For a complete listing of product availability, see Ordering Guide on Page 66.

| ANALOG<br>DEVICES       |

|-------------------------|

| ADSP-2148x              |

| tppZ-cc                 |

| vvvvv.x n.n             |

| #yyww country_of_origin |

| SHARC                   |

Figure 3. Typical Package Brand

#### Table 17. Package Brand Information<sup>1</sup>

| Brand Key | <b>Field Description</b>          |

|-----------|-----------------------------------|

| t         | Temperature Range                 |

| рр        | Package Type                      |

| Z         | <b>RoHS</b> Compliant Option      |

| сс        | See Ordering Guide                |

| vvvvv.x   | Assembly Lot Code                 |

| n.n       | Silicon Revision                  |

| #         | <b>RoHS</b> Compliant Designation |

| yyww      | Date Code                         |

<sup>1</sup> Non automotive only. For branding information specific to automotive products, contact Analog Devices Inc.

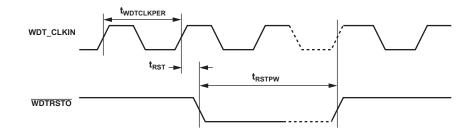

### Watchdog Timer Timing

### Table 27. Watchdog Timer Timing

| Parameter          |                                                               | Min                       | Max  | Unit |

|--------------------|---------------------------------------------------------------|---------------------------|------|------|

| Timing Requ        | uirement                                                      |                           |      |      |

| twdtclkper         |                                                               | 100                       | 1000 | ns   |

| Switching C        | Characteristics                                               |                           |      |      |

| t <sub>RST</sub>   | WDT Clock Rising Edge to Watchdog Timer<br>RESET Falling Edge | 3                         | 6.4  | ns   |

| t <sub>RSTPW</sub> | Reset Pulse Width                                             | $64 \times t_{WDTCLKPER}$ |      | ns   |

Figure 14. Watchdog Timer Timing

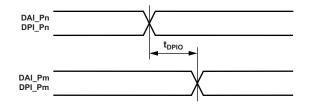

### Pin to Pin Direct Routing (DAI and DPI)

For direct pin connections only (for example DAI\_PB01\_I to DAI\_PB02\_O).

#### Table 28. DAI/DPI Pin to Pin Routing

| Parameter          |                                                       | Min | Max | Unit |

|--------------------|-------------------------------------------------------|-----|-----|------|

| Timing Requirement |                                                       |     |     |      |

| t <sub>DPIO</sub>  | Delay DAI/DPI Pin Input Valid to DAI/DPI Output Valid | 1.5 | 12  | ns   |

Figure 15. DAI Pin to Pin Direct Routing

### AMI Read

Use these specifications for asynchronous interfacing to memories. Note that timing for AMI\_ACK, ADDR, DATA, AMI\_RD, AMI\_WR, and strobe timing parameters only apply to asynchronous access mode.

#### Table 32. AMI Read

| Parameter                           |                                        | Min                         | Мах                   | Unit |

|-------------------------------------|----------------------------------------|-----------------------------|-----------------------|------|

| Timing Requ                         | irements                               |                             |                       |      |

| t <sub>DAD</sub> <sup>1, 2, 3</sup> | Address Selects Delay to Data Valid    |                             | W + $t_{SDCLK}$ – 5.4 | ns   |

| t <sub>DRLD</sub> <sup>1, 3</sup>   | AMI_RD Low to Data Valid               |                             | W – 3.2               | ns   |

| t <sub>SDS</sub>                    | Data Setup to AMI_RD High              | 2.5                         |                       | ns   |

| HDRH <sup>4, 5</sup>                | Data Hold from AMI_RD High             | 0                           |                       | ns   |

| DAAK <sup>2, 6</sup>                | AMI_ACK Delay from Address, Selects    |                             | $t_{SDCLK} - 9.5 + W$ | ns   |

| DSAK <sup>4</sup>                   | AMI_ACK Delay from AMI_RD Low          |                             | W – 7                 | ns   |

| Switching Ch                        | paracteristics                         |                             |                       |      |

| t <sub>DRHA</sub>                   | Address Selects Hold After AMI_RD High | RHC + 0.20                  |                       | ns   |

| DARL <sup>2</sup>                   | Address Selects to AMI_RD Low          | t <sub>SDCLK</sub> – 3.8    |                       | ns   |

| RW                                  | AMI_RD Pulse Width                     | W – 1.4                     |                       | ns   |

| t <sub>RWR</sub>                    | AMI_RD High to AMI_RD Low              | HI + t <sub>SDCLK</sub> – 1 |                       | ns   |

W = (number of wait states specified in AMICTLx register)  $\times$  t<sub>SDCLK</sub>.

$\mathsf{RHC} = (\mathsf{number of Read Hold Cycles specified in AMICTLx register}) \times t_{\mathsf{SDCLK}}$

Where PREDIS = 0

HI = RHC (if IC=0): Read to Read from same bank

$HI = RHC + t_{SDCLK}$  (if IC>0): Read to Read from same bank

HI = RHC + IC: Read to Read from different bank

$HI = RHC + Max (IC, (4 \times t_{SDCLK}))$ : Read to Write from same or different bank

Where PREDIS = 1

$HI = RHC + Max (IC, (4 \times t_{SDCLK}))$ : Read to Write from same or different bank

$HI = RHC + (3 \times t_{SDCLK})$ : Read to Read from same bank

HI = RHC + Max (IC, (3 × t<sub>SDCLK</sub>): Read to Read from different bank

$\mathsf{IC} = (\mathsf{number of idle cycles specified in AMICTLx register}) \times \mathsf{t}_{\mathsf{SDCLK}}$

H = (number of hold cycles specified in AMICTLx register)  $\times$  tSDCLK

<sup>1</sup>Data delay/setup: System must meet t<sub>DAD</sub>, t<sub>DRLD</sub>, or t<sub>SDS</sub>.

<sup>2</sup> The falling edge of  $\overline{\text{MS}}$ x, is referenced.

<sup>3</sup>The maximum limit of timing requirement values for t<sub>DAD</sub> and t<sub>DRLD</sub> parameters are applicable for the case where AMI\_ACK is always high and when the ACK feature is not used.

<sup>4</sup>Note that timing for AMI\_ACK, ADDR, DATA, AMI\_RD, AMI\_WR, and strobe timing parameters only apply to asynchronous access mode.

<sup>5</sup> Data hold: User must meet t<sub>HDRH</sub> in asynchronous access mode. See Test Conditions on Page 55 for the calculation of hold times given capacitive and dc loads.

<sup>6</sup>AMI\_ACK delay/setup: User must meet t<sub>DAAK</sub>, or t<sub>DSAK</sub>, for deassertion of AMI\_ACK (low).

#### Table 36. Serial Ports—External Late Frame Sync

| Parameter<br>Switching Characteristics |                                                                                                           | Min | Max | Unit |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|------|

|                                        |                                                                                                           |     |     |      |

| t <sub>DDTLFSE</sub> 1                 | Data Delay from Late External Transmit Frame Sync or External<br>Receive Frame Sync with MCE = 1, MFD = 0 |     | 8.5 | ns   |

| t <sub>DDTENFS</sub> <sup>1</sup>      | Data Enable for MCE = 1, MFD = $0$                                                                        | 0.5 |     | ns   |

$^{1}$ The t<sub>DDTLFSE</sub> and t<sub>DDTENFS</sub> parameters apply to left-justified, as well as DSP serial mode, and MCE = 1, MFD = 0.

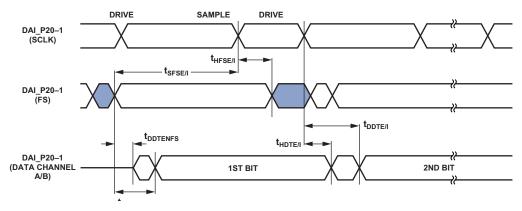

#### DRIVE SAMPLE DRIVE DAI\_P20-1 (SCLK) t<sub>HFSE/I</sub> t<sub>SFSE/I</sub> DAI\_P20-1 (FS) t<sub>DDTE/I</sub> **t**<sub>DDTENFS</sub> t<sub>HDTE/I</sub> DAI\_P20-1 (DATA CHANNEL A/B) 1ST BIT 2ND BIT $\hat{a}$ t<sub>DDTLFSE</sub>

#### EXTERNAL RECEIVE FS WITH MCE = 1, MFD = 0

#### LATE EXTERNAL TRANSMIT FS

Figure 22. External Late Frame Sync<sup>1</sup>

<sup>1</sup>This figure reflects changes made to support left-justified mode.

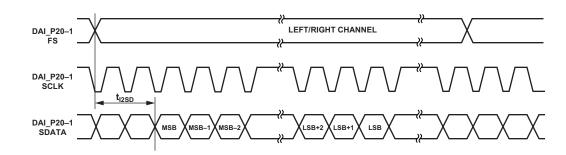

Figure 31 shows the default I<sup>2</sup>S-justified mode. The frame sync is low for the left channel and HI for the right channel. Data is valid on the rising edge of serial clock. The MSB is left-justified to the frame sync transition but with a delay.

### Table 45. S/PDIF Transmitter I<sup>2</sup>S Mode

| Parameter          |                                                  | Nominal | Unit |

|--------------------|--------------------------------------------------|---------|------|

| Timing Requirement |                                                  |         |      |

| t <sub>I2SD</sub>  | Frame Sync to MSB Delay in I <sup>2</sup> S Mode | 1       | SCLK |

Figure 31. I<sup>2</sup>S-Justified Mode

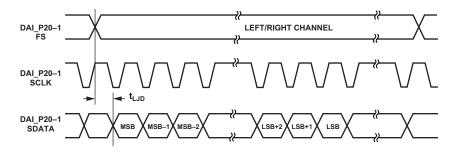

Figure 32 shows the left-justified mode. The frame sync is high for the left channel and low for the right channel. Data is valid on the rising edge of serial clock. The MSB is left-justified to the frame sync transition with no delay.

#### Table 46. S/PDIF Transmitter Left-Justified Mode

| Parameter          |                                                | Nominal | Unit |

|--------------------|------------------------------------------------|---------|------|

| Timing Requirement |                                                |         |      |

| t <sub>LJD</sub>   | Frame Sync to MSB Delay in Left-Justified Mode | 0       | SCLK |

Figure 32. Left-Justified Mode

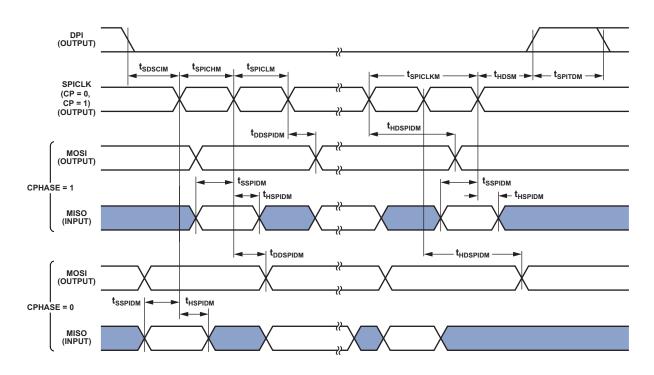

#### SPI Interface—Master

The ADSP-2148x contains two SPI ports. Both primary and secondary are available through DPI only. The timing provided in Table 50 and Table 51 applies to both.

#### Table 50. SPI Interface Protocol-Master Switching and Timing Specifications

| Parameter            |                                                         | Min                       | Max | Unit |

|----------------------|---------------------------------------------------------|---------------------------|-----|------|

| Timing Requirer      | ments                                                   |                           |     |      |

| t <sub>SSPIDM</sub>  | Data Input Valid to SPICLK Edge (Data Input Setup Time) | 8.2                       |     | ns   |

| t <sub>HSPIDM</sub>  | SPICLK Last Sampling Edge to Data Input Not Valid       | 2                         |     | ns   |

| Switching Chard      | acteristics                                             |                           |     |      |

| t <sub>SPICLKM</sub> | Serial Clock Cycle                                      | $8 \times t_{PCLK} - 2$   |     | ns   |

| t <sub>SPICHM</sub>  | Serial Clock High Period                                | $4 \times t_{PCLK} - 2$   |     | ns   |

| t <sub>SPICLM</sub>  | Serial Clock Low Period                                 | $4 \times t_{PCLK} - 2$   |     | ns   |

| t <sub>DDSPIDM</sub> | SPICLK Edge to Data Out Valid (Data Out Delay Time)     |                           | 2.5 | ns   |

| t <sub>HDSPIDM</sub> | SPICLK Edge to Data Out Not Valid (Data Out Hold Time)  | $4 \times t_{PCLK} - 2$   |     | ns   |

| t <sub>SDSCIM</sub>  | DPI Pin (SPI Device Select) Low to First SPICLK Edge    | $4 \times t_{PCLK} - 2$   |     | ns   |

| t <sub>HDSM</sub>    | Last SPICLK Edge to DPI Pin (SPI Device Select) High    | $4 \times t_{PCLK} - 2$   |     | ns   |

| t <sub>SPITDM</sub>  | Sequential Transfer Delay                               | $4 \times t_{PCLK} - 1.2$ |     | ns   |

Figure 35. SPI Master Timing

### JTAG Test Access Port and Emulation

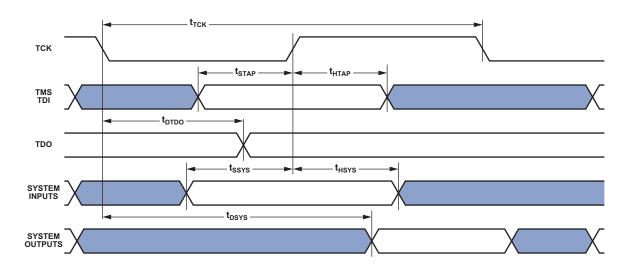

### Table 54. JTAG Test Access Port and Emulation

| Parameter                      |                                     | Min              | Max                      | Unit |

|--------------------------------|-------------------------------------|------------------|--------------------------|------|

| Timing Requ                    | irements                            |                  |                          |      |

| t <sub>TCK</sub>               | TCK Period                          | 20               |                          | ns   |

| t <sub>STAP</sub>              | TDI, TMS Setup Before TCK High      | 5                |                          | ns   |

| t <sub>HTAP</sub>              | TDI, TMS Hold After TCK High        | 6                |                          | ns   |

| t <sub>SSYS</sub> <sup>1</sup> | System Inputs Setup Before TCK High | 7                |                          | ns   |

| t <sub>HSYS</sub> <sup>1</sup> | System Inputs Hold After TCK High   | 18               |                          | ns   |

| t <sub>TRSTW</sub>             | TRST Pulse Width                    | 4t <sub>CK</sub> |                          | ns   |

| Switching C                    | haracteristics                      |                  |                          |      |

| t <sub>DTDO</sub>              | TDO Delay from TCK Low              |                  | 10                       | ns   |

| t <sub>DSYS</sub> <sup>2</sup> | System Outputs Delay After TCK Low  |                  | t <sub>TCK</sub> ÷ 2 + 7 | ns   |

<sup>1</sup> System Inputs = DATA15-0, CLK\_CFG1-0, RESET, BOOT\_CFG2-0, DAI\_Px, DPI\_Px, and FLAG3-0. <sup>2</sup> System Outputs = DAI\_Px, DPI\_Px ADDR23-0, AMI\_RD, AMI\_WR, FLAG3-0, SDCAS, SDCAS, SDCKE, SDA10, SDDQM, SDCLK and EMU.

Figure 40. IEEE 1149.1 JTAG Test Access Port

# **100-LQFP\_EP LEAD ASSIGNMENT**

| Lead Name           | Lead No. |

|---------------------|----------|---------------------|----------|---------------------|----------|---------------------|----------|

| V <sub>DD_INT</sub> | 1        | V <sub>DD_EXT</sub> | 26       | DAI_P10             | 51       | V <sub>DD_INT</sub> | 76       |

| CLK_CFG1            | 2        | DPI_P08             | 27       | V <sub>DD_INT</sub> | 52       | FLAG0               | 77       |

| BOOT_CFG0           | 3        | DPI_P07             | 28       | V <sub>DD_EXT</sub> | 53       | V <sub>DD_INT</sub> | 78       |

| V <sub>DD_EXT</sub> | 4        | V <sub>DD_INT</sub> | 29       | DAI_P20             | 54       | V <sub>DD_INT</sub> | 79       |

| V <sub>DD_INT</sub> | 5        | DPI_P09             | 30       | V <sub>DD_INT</sub> | 55       | FLAG1               | 80       |

| BOOT_CFG1           | 6        | DPI_P10             | 31       | DAI_P08             | 56       | FLAG2               | 81       |

| GND                 | 7        | DPI_P11             | 32       | DAI_P04             | 57       | FLAG3               | 82       |

| NC                  | 8        | DPI_P12             | 33       | DAI_P14             | 58       | MLBCLK              | 83       |

| NC                  | 9        | DPI_P13             | 34       | DAI_P18             | 59       | MLBDAT              | 84       |

| CLK_CFG0            | 10       | DAI_P03             | 35       | DAI_P17             | 60       | MLBDO               | 85       |

| V <sub>DD_INT</sub> | 11       | DPI_P14             | 36       | DAI_P16             | 61       | V <sub>DD_EXT</sub> | 86       |

| CLKIN               | 12       | V <sub>DD_INT</sub> | 37       | DAI_P15             | 62       | MLBSIG              | 87       |

| XTAL                | 13       | V <sub>DD_INT</sub> | 38       | DAI_P12             | 63       | V <sub>DD_INT</sub> | 88       |

| V <sub>DD_EXT</sub> | 14       | V <sub>DD_INT</sub> | 39       | V <sub>DD_INT</sub> | 64       | MLBSO               | 89       |

| V <sub>DD_INT</sub> | 15       | DAI_P13             | 40       | DAI_P11             | 65       | TRST                | 90       |

| V <sub>DD_INT</sub> | 16       | DAI_P07             | 41       | V <sub>DD_INT</sub> | 66       | EMU                 | 91       |

| RESETOUT/RUNRSTIN   | 17       | DAI_P19             | 42       | V <sub>DD_INT</sub> | 67       | TDO                 | 92       |

| V <sub>DD_INT</sub> | 18       | DAI_P01             | 43       | GND                 | 68       | V <sub>DD_EXT</sub> | 93       |

| DPI_P01             | 19       | DAI_P02             | 44       | THD_M               | 69       | V <sub>DD_INT</sub> | 94       |

| DPI_P02             | 20       | V <sub>DD_INT</sub> | 45       | THD_P               | 70       | TDI                 | 95       |

| DPI_P03             | 21       | V <sub>DD_EXT</sub> | 46       | V <sub>DD_THD</sub> | 71       | ТСК                 | 96       |

| V <sub>DD_INT</sub> | 22       | V <sub>DD_INT</sub> | 47       | V <sub>DD_INT</sub> | 72       | V <sub>DD_INT</sub> | 97       |

| DPI_P05             | 23       | DAI_P06             | 48       | V <sub>DD_INT</sub> | 73       | RESET               | 98       |

| DPI_P04             | 24       | DAI_P05             | 49       | V <sub>DD_INT</sub> | 74       | TMS                 | 99       |

| DPI_P06             | 25       | DAI_P09             | 50       | V <sub>DD_INT</sub> | 75       | V <sub>DD_INT</sub> | 100      |

|                     |          |                     |          |                     |          | GND                 | 101*     |

Table 59. 100-Lead LQFP\_EP Lead Assignments (Numerical by Lead Number)

MLB pins (pins 83, 84, 85, 87, and 89) are available for automotive models only. For non-automotive models, these pins should be connected to ground (GND).

\* Pin no. 101 (exposed pad) is the GND supply (see Figure 48 and Figure 49) for the processor; this pad must be **robustly** connected to GND.

# 176-LEAD LQFP\_EP LEAD ASSIGNMENT

| NC         1         Vop_trt         45         DALP10         89         Vop_NT         133           MSO         2         PPLP08         46         Vop_NT         90         FLAG0         134           NC         3         DPLP07         47         Vop_ET         91         FLAG1         135           Vop_INT         4         Vop_NT         48         DALP20         92         FLAG2         136           CLK_CFG1         5         DPLP10         50         DALP08         94         FLAG3         138           BOOT_CFG0         7         DPLP11         51         DALP04         96         GND         140           ADDR1         9         DPLP13         53         DALP17         98         GND         142           ADDR3         11         DALP03         55         DALP17         98         GND         143           ADDR4         12         NC         56         DALP11         103         DATA0         147           ADDR5         13         Vop_DINT         62         BOOT_CFG2         106         DATA1         148           ADDR6         16         NC         63         Vop_IN                                                                                                            | Lead Name           | Lead No. | Lead Name           | Lead No. | Lead Name           | Lead No. | Lead Name                  | Lead No. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|---------------------|----------|---------------------|----------|----------------------------|----------|

| NC         3         DPL P07         47         VDD_DRT         91         FLAG1         135           VDD_JNT         48         DALP20         92         FLAG2         136           CLK_CFG1         5         DPLP09         49         VDD_NT         93         GND         137           ADDR0         6         DPLP10         50         DALP08         94         FLAG3         138           SOOT_CFG0         7         DPLP13         53         DALP14         95         GND         141           ADDR1         9         DPLP13         53         DALP16         94         VD_D_NT         143           ADDR3         11         DALP03         55         DALP12         100         GND         142           ADDR4         12         NC         56         DALP15         101         GND         145           BOOT_CFG1         14         NC         58         VD_D_INT         102         EMT         146           ADDR4         16         NC         60         VD_D_DT         103         DATA1         148           ADDR5         16         NC         61         VD_D_DT         105         DATA                                                                                                           | NC                  | 1        | V <sub>DD_EXT</sub> | 45       | DAI_P10             | 89       | V <sub>DD_INT</sub>        | 133      |

| VDD_INT         4         VDD_INT         48         DAL_P20         92         FLAG2         136           CLK_CFG1         5         DPL_P09         49         VDD_INT         93         GND         137           ADDR0         6         DPL_P10         50         DAL_P08         94         ELAG3         138           BODT_CFG0         7         DPL_P13         53         DAL_P14         95         GND         140           ADDR1         9         DPL_P13         53         DAL_P15         99         YDD_DKT         141           ADDR3         11         DAL_P03         55         DAL_P15         99         YDD_DKT         143           ADDR4         12         NC         56         DAL_P15         101         GND         145           ADDR3         13         YDD_ERT         57         DAL_P15         102         EMU         146           GND         15         NC         59         DAL_P11         103         DATA1         148           ADDR6         16         NC         61         YDD_INT         105         DATA2         150           ADDR4         16         NC         63                                                                                                             | MSO                 | 2        | DPI_P08             | 46       | V <sub>DD_INT</sub> | 90       | FLAG0                      | 134      |

| CLK_CFG1         5         DPLP09         49         VDD_INT         93         GND         137           ADDR0         6         DPLP10         50         DAL_P08         94         PLAG3         138           SODT_CFG0         7         DPLP11         51         DAL_P14         95         GND         139           VDD_EXT         8         DPLP12         52         DAL_P14         96         GND         141           ADDR1         9         DPLP13         53         DAL_P17         98         GND         142           ADDR3         11         DALP03         55         DAL_P15         99         VDD_MT         143           ADDR4         12         NC         56         DALP12         100         TRST         144           ADDR5         13         VD_LEXT         57         DALP11         103         DATA0         147           ADDR6         16         NC         58         VD_LNT         105         DATA2         149           ADDR6         16         NC         60         VDD_LNT         105         DATA3         150           NC         18         VD_LINT         62         BO                                                                                                           | NC                  | 3        | DPI_P07             | 47       | V <sub>DD_EXT</sub> | 91       | FLAG1                      | 135      |

| ADDR0         6         DPLP10         50         DALP08         94         FLAG3         138           BOOT_CFG0         7         DPLP11         51         DALP14         95         GND         139           ADDR1         9         DPLP12         52         DALP18         97         VDD_DRT         141           ADDR3         10         DPLP13         53         DALP16         99         VDD_DRT         142           ADDR3         11         DALP03         55         DALP16         99         VDD_NT         143           ADDR4         12         NC         56         DALP15         101         GND         145           BOOT_CFG1         14         NC         58         VDD_INT         102         EMU         146           ADDR4         12         NC         59         DALP11         103         DATA1         148           ADDR5         13         VDD_INT         62         BOOT_CFG2         106         DATA2         149           NC         18         VDD_INT         62         BOOT_CFG2         106         DATA3         150           NC         18         VDD_INT         62                                                                                                               | V <sub>DD_INT</sub> | 4        | V <sub>DD_INT</sub> | 48       | DAI_P20             | 92       | FLAG2                      | 136      |

| ADDR0         6         DPL P10         50         DAL P08         94         FLAGS         139           BOOT_CFG0         7         DPLP11         51         DALP14         95         GND         139           VDD_DCT         8         DPLP12         52         DALP14         96         GND         140           ADDR1         9         DPLP13         53         DALP16         99         YDD_DKT         141           ADDR3         11         DALP03         55         DALP12         100         GND         142           ADDR4         12         NC         56         DALP12         101         GND         143           ADDR5         13         VD_DETT         57         DALP11         103         DATA1         144           ADDR6         16         NC         59         DALP11         103         DATA1         148           ADDR6         16         NC         60         YD_DENT         105         DATA1         148           ADDR6         17         NC         61         YD_DENT         105         DATA1         150           NC         18         YD_DINT         62         BOOT_CF                                                                                                           | CLK_CFG1            | 5        | DPI_P09             | 49       | V <sub>DD INT</sub> | 93       | GND                        | 137      |

| VDD_ENT         8         DPI_P12         52         DAI_P04         96         GND         140           ADDR1         9         DPI_P13         53         DAI_P18         97         VD_DENT         141           ADDR3         11         DAI_P03         55         DAI_P16         98         GND         142           ADDR4         12         NC         56         DAI_P12         101         GND         143           ADDR4         12         NC         58         DAI_P13         101         GND         145           BOOT_CFG1         14         NC         58         DAI_P11         102         EMU         146           ADDR4         15         NC         60         VD_D_INT         104         DATA1         148           ADDR4         18         VDD_INT         62         BOT_CFG2         106         DATA3         150           NC         18         VDD_INT         63         OD_INT         107         DO_D         151           ADDR4         20         NC         64         AMI_ACK         108         DATA4         152           ADDR4         21         VD_INT         65         G                                                                                                           | ADDR0               | 6        | DPI_P10             | 50       | _                   | 94       | FLAG3                      | 138      |

| ADDR1         9         DPLP13         53         DALP18         97         VDD_EXT         141           ADDR2         10         DPLP14         54         DALP17         98         GND         142           ADDR3         11         DALP03         55         DALP16         99         VDD_INT         143           ADDR4         12         NC         56         DALP15         101         GND         145           BOOT_CFG1         14         NC         58         VDD_INT         102         EMU         146           GND         15         NC         59         DALP11         103         DATA1         148           ADDR6         16         NC         61         VDD_INT         107         DATA1         148           ADDR7         17         NC         61         VD_INT         107         DATA1         150           NC         19         NC         63         ROD_INT         107         DATA1         151           ADDR9         21         VDD_INT         65         GND         109         VDD_ETAT         153           CLK_CFG0         22         NC         61         THD_P                                                                                                                    | BOOT_CFG0           | 7        | DPI_P11             | 51       | DAI_P14             | 95       | GND                        | 139      |