Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Active                                                              |

|-------------------------|---------------------------------------------------------------------|

| Туре                    | Floating Point                                                      |

| Interface               | EBI/EMI, DAI, I²C, SPI, SPORT, UART/USART                           |

| Clock Rate              | 400MHz                                                              |

| Non-Volatile Memory     | External                                                            |

| On-Chip RAM             | 5Mbit                                                               |

| Voltage - I/O           | 3.30V                                                               |

| Voltage - Core          | 1.10V                                                               |

| Operating Temperature   | -40°C ~ 125°C (TJ)                                                  |

| Mounting Type           | Surface Mount                                                       |

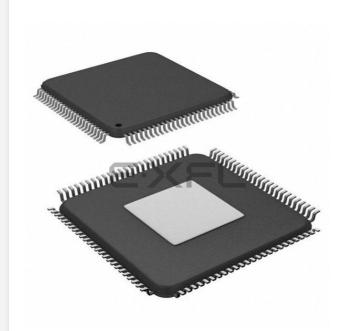

| Package / Case          | 100-LQFP Exposed Pad                                                |

| Supplier Device Package | 100-LQFP-EP (14x14)                                                 |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/ad21489wbswz402 |

|                         |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

subtract in both processing elements while branching and fetching up to four 32-bit values from memory, all in a single instruction.

### Variable Instruction Set Architecture (VISA)

In addition to supporting the standard 48-bit instructions from previous SHARC processors, the ADSP-2148x supports new instructions of 16 and 32 bits. This feature, called Variable Instruction Set Architecture (VISA), drops redundant/unused bits within the 48-bit instruction to create more efficient and compact code. The program sequencer supports fetching these 16-bit and 32-bit instructions from both internal and external SDRAM memory. This support is not extended to the asynchronous memory interface (AMI). Source modules need to be built using the VISA option, in order to allow code generation tools to create these more efficient opcodes.

### **On-Chip Memory**

The ADSP-21483 and the ADSP-21488 processors contain 3 Mbits of internal RAM (Table 3) and the ADSP-21486, ADSP-21487, and ADSP-21489 processors contain 5 Mbits of internal RAM (Table 4). Each memory block supports singlecycle, independent accesses by the core processor and I/O processor.

|                          | IOP Registers 0x0000 0000-0x0003 FFFF                      |                         |                         |  |  |  |

|--------------------------|------------------------------------------------------------|-------------------------|-------------------------|--|--|--|

| Long Word (64 Bits)      | Extended Precision Normal or<br>Instruction Word (48 Bits) | Normal Word (32 Bits)   | Short Word (16 Bits)    |  |  |  |

| Block 0 ROM (Reserved)   | Block 0 ROM (Reserved)                                     | Block 0 ROM (Reserved)  | Block 0 ROM (Reserved)  |  |  |  |

| 0x0004 0000–0x0004 7FFF  | 0x0008 0000–0x0008 AAA9                                    | 0x0008 0000–0x0008 FFFF | 0x0010 0000–0x0011 FFFF |  |  |  |

| Reserved                 | Reserved                                                   | Reserved                | Reserved                |  |  |  |

| 0x0004 8000-0x0004 8FFF  | 0x0008 AAAA-0x0008 BFFF                                    | 0x0009 0000-0x0009 1FFF | 0x0012 0000-0x0012 3FFF |  |  |  |

| Block 0 SRAM             | Block 0 SRAM                                               | Block 0 SRAM            | Block 0 SRAM            |  |  |  |

| 0x0004 9000–0x0004 CFFF  | 0x0008 C000–0x0009 1554                                    | 0x0009 2000–0x0009 9FFF | 0x0012 4000–0x0013 3FFF |  |  |  |

| Reserved                 | Reserved                                                   | Reserved                | Reserved                |  |  |  |

| 0x0004 D000–0x0004 FFFF  | 0x0009 1555–0x0009 FFFF                                    | 0x0009 A000–0x0009 FFFF | 0x0013 4000–0x0013 FFFF |  |  |  |

| Block 1 ROM (Reserved)   | Block 1 ROM (Reserved)                                     | Block 1 ROM (Reserved)  | Block 1 ROM (Reserved)  |  |  |  |

| 0x0005 0000–0x0005 7FFF  | 0x000A 0000-0x000A AAA9                                    | 0x000A 0000–0x000A FFFF | 0x0014 0000–0x0015 FFFF |  |  |  |

| Reserved                 | Reserved                                                   | Reserved                | Reserved                |  |  |  |

| 0x0005 8000-0x0005 8FFF  | 0x000A AAAA–0x000A BFFF                                    | 0x000B 0000-0x000B 1FFF | 0x0016 0000-0x0016 3FFF |  |  |  |

| Block 1 SRAM             | Block 1 SRAM                                               | Block 1 SRAM            | Block 1 SRAM            |  |  |  |

| 0x0005 9000-0x0005 CFFF  | 0x000A C000–0x000B 1554                                    | 0x000B 2000–0x000B 9FFF | 0x0016 4000–0x0017 3FFF |  |  |  |

| Reserved                 | Reserved                                                   | Reserved                | Reserved                |  |  |  |

| 0x0005 D000-0x0005 FFFF  | 0x000B 1555–0x000B FFFF                                    | 0x000B A000–0x000B FFFF | 0x0017 4000-0x0017 FFFF |  |  |  |

| Block 2 SRAM             | Block 2 SRAM                                               | Block 2 SRAM            | Block 2 SRAM            |  |  |  |

| 0x0006 0000-0x0006 1FFF  | 0x000C 0000–0x000C 2AA9                                    | 0x000C 0000–0x000C 3FFF | 0x0018 0000–0x0018 7FFF |  |  |  |

| Reserved                 | Reserved                                                   | Reserved                | Reserved                |  |  |  |

| 0x0006 2000– 0x0006 FFFF | 0x000C 2AAA-0x000D FFFF                                    | 0x000C 4000–0x000D FFFF | 0x0018 8000-0x001B FFFF |  |  |  |

| Block 3 SRAM             | Block 3 SRAM                                               | Block 3 SRAM            | Block 3 SRAM            |  |  |  |

| 0x0007 0000-0x0007 1FFF  | 0x000E 0000–0x000E 2AA9                                    | 0x000E 0000-0x000E 3FFF | 0x001C 0000–0x001C 7FFF |  |  |  |

| Reserved                 | Reserved                                                   | Reserved                | Reserved                |  |  |  |

| 0x0007 2000-0x0007 FFFF  | 0x000E 2AAA-0x000F FFFF                                    | 0x000E 4000–0x000F FFFF | 0x001C 8000–0x001F FFFF |  |  |  |

Table 3. Internal Memory Space (3 MBits-ADSP-21483/ADSP-21488)<sup>1</sup>

<sup>1</sup>Some ADSP-2148x processors include a customer-definable ROM block. ROM addresses on these models are not reserved as shown in this table. Please contact your Analog Devices sales representative for additional details.

The processor's SRAM can be configured as a maximum of 160k words of 32-bit data, 320k words of 16-bit data, 106.7k words of 48-bit instructions (or 40-bit data), or combinations of different word sizes up to 5 megabits. All of the memory can be accessed as 16-bit, 32-bit, 48-bit, or 64-bit words. A 16-bit floating-point storage format is supported that effectively doubles the amount of data that may be stored on-chip. Conversion between the 32-bit floating-point and 16-bit floating-point formats is performed in a single instruction. While each memory block can store combinations of code and data, accesses are

most efficient when one block stores data using the DM bus for transfers, and the other block stores instructions and data using the PM bus for transfers.

Using the DM bus and PM buses, with one bus dedicated to a memory block, assures single-cycle execution with two data transfers. In this case, the instruction must be available in the cache.

The memory maps in Table 3 and Table 4 display the internal memory address space of the processors. The 48-bit space section describes what this address range looks like to an

• Arbitration logic to coordinate core and DMA transfers between internal and external memory over the external port.

Non-SDRAM external memory address space is shown in Table 5.

| Table 5. External Memory for Non-SDRAM Addresses | Table 5. | External Memo | ory for Non-SDRAM Addresses |

|--------------------------------------------------|----------|---------------|-----------------------------|

|--------------------------------------------------|----------|---------------|-----------------------------|

| Bank   | Size in<br>Words | Address Range           |

|--------|------------------|-------------------------|

| Bank 0 | 6M               | 0x0020 0000–0x007F FFFF |

| Bank 1 | 8M               | 0x0400 0000-0x047F FFFF |

| Bank 2 | 8M               | 0x0800 0000-0x087F FFFF |

| Bank 3 | 8M               | 0x0C00 0000-0x0C7F FFFF |

### **External Port**

The external port provides a high performance, glueless interface to a wide variety of industry-standard memory devices. The external port, available on the 176-lead LQFP, may be used to interface to synchronous and/or asynchronous memory devices through the use of its separate internal memory controllers. The first is an SDRAM controller for connection of industry-standard synchronous DRAM devices while the second is an asynchronous memory controller intended to interface to a variety of memory devices. Four memory select pins enable up to four separate devices to coexist, supporting any desired combination of synchronous and asynchronous device types.

#### Asynchronous Memory Controller

The asynchronous memory controller provides a configurable interface for up to four separate banks of memory or I/O devices. Each bank can be independently programmed with different timing parameters, enabling connection to a wide variety of memory devices including SRAM, flash, and EPROM, as well as I/O devices that interface with standard memory control lines. Bank 0 occupies a 6M word window and banks 1, 2, and 3 occupy a 8M word window in the processor's address space but, if not fully populated, these windows are not made contiguous by the memory controller logic.

#### **SDRAM Controller**

The SDRAM controller provides an interface of up to four separate banks of industry-standard SDRAM devices at speeds up to  $f_{SDCLK}$ . Fully compliant with the SDRAM standard, each bank has its own memory select line ( $\overline{MS0}$ – $\overline{MS3}$ ), and can be configured to contain between 4M bytes and 256M bytes of memory. SDRAM external memory address space is shown in Table 6. NOTE: this feature is not available on the ADSP-21486 model.

| Table 6. | External | Memory | for S | DRAM | Addresses |

|----------|----------|--------|-------|------|-----------|

|----------|----------|--------|-------|------|-----------|

| Bank   | Size in<br>Words | Address Range           |

|--------|------------------|-------------------------|

| Bank 0 | 62M              | 0x0020 0000-0x03FF FFFF |

| Bank 1 | 64M              | 0x0400 0000-0x07FF FFFF |

| Bank 2 | 64M              | 0x0800 0000-0x0BFF FFFF |

| Bank 3 | 64M              | 0x0C00 0000-0x0FFF FFFF |

A set of programmable timing parameters is available to configure the SDRAM banks to support slower memory devices. Note that 32-bit wide devices are not supported on the SDRAM and AMI interfaces.

The SDRAM controller address, data, clock, and control pins can drive loads up to distributed 30 pF. For larger memory systems, the SDRAM controller external buffer timing should be selected and external buffering should be provided so that the load on the SDRAM controller pins does not exceed 30 pF.

Note that the external memory bank addresses shown are for normal-word (32-bit) accesses. If 48-bit instructions as well as 32-bit data are both placed in the same external memory bank, care must be taken while mapping them to avoid overlap.

#### SIMD Access to External Memory

The SDRAM controller on the processor supports SIMD access on the 64-bit EPD (external port data bus) which allows access to the complementary registers on the PEy unit in the normal word space (NW). This removes the need to explicitly access the complimentary registers when the data is in external SDRAM memory.

#### VISA and ISA Access to External Memory

The SDRAM controller on the ADSP-2148x processors supports VISA code operation which reduces the memory load since the VISA instructions are compressed. Moreover, bus fetching is reduced because, in the best case, one 48-bit fetch contains three valid instructions. Code execution from the traditional ISA operation is also supported. Note that code execution is only supported from bank 0 regardless of VISA/ISA. Table 7 shows the address ranges for instruction fetch in each mode.

#### Table 7. External Bank 0 Instruction Fetch

| Access Type | Size in<br>Words | Address Range           |

|-------------|------------------|-------------------------|

| ISA (NW)    | 4M               | 0x0020 0000-0x005F FFFF |

| VISA (SW)   | 10M              | 0x0060 0000-0x00FF FFFF |

#### **Pulse-Width Modulation**

The PWM module is a flexible, programmable, PWM waveform generator that can be programmed to generate the required switching patterns for various applications related to motor and engine control or audio power control. The PWM generator can generate either center-aligned or edge-aligned PWM waveforms. In addition, it can generate complementary signals on two outputs in paired mode or independent signals in nonpaired mode (applicable to a single group of four PWM waveforms).

The entire PWM module has four groups of four PWM outputs generating 16 PWM outputs in total. Each PWM group produces two pairs of PWM signals on the four PWM outputs.

The outputs of PCG A and B can be routed through the DAI pins and the outputs of PCG C and D can be driven on to the DAI as well as the DPI pins.

# Digital Peripheral Interface (DPI)

The ADSP-2148x SHARC processors have a digital peripheral interface that provides connections to two serial peripheral interface ports (SPI), one universal asynchronous receiver-transmitter (UART), 12 flags, a 2-wire interface (TWI), three PWM modules (PWM3–1), and two general-purpose timers.

### Serial Peripheral (Compatible) Interface (SPI)

The SPI is an industry-standard synchronous serial link, enabling the SPI-compatible port to communicate with other SPI compatible devices. The SPI consists of two data pins, one device select pin, and one clock pin. It is a full-duplex synchronous serial interface, supporting both master and slave modes. The SPI port can operate in a multimaster environment by interfacing with up to four other SPI-compatible devices, either acting as a master or slave device. The SPI-compatible peripheral implementation also features programmable baud rate and clock phase and polarities. The SPI-compatible port uses open drain drivers to support a multimaster configuration and to avoid data contention.

### **UART Port**

The processors provide a full-duplex Universal Asynchronous Receiver/Transmitter (UART) port, which is fully compatible with PC-standard UARTs. The UART port provides a simplified UART interface to other peripherals or hosts, supporting full-duplex, DMA-supported, asynchronous transfers of serial data. The UART also has multiprocessor communication capability using 9-bit address detection. This allows it to be used in multidrop networks through the RS-485 data interface standard. The UART port also includes support for 5 to 8 data bits, 1 or 2 stop bits, and none, even, or odd parity. The UART port supports two modes of operation:

- PIO (programmed I/O)—The processor sends or receives data by writing or reading I/O-mapped UART registers. The data is double-buffered on both transmit and receive.

- DMA (direct memory access)—The DMA controller transfers both transmit and receive data. This reduces the number and frequency of interrupts required to transfer data to and from memory. The UART has two dedicated DMA channels, one for transmit and one for receive. These DMA channels have lower default priority than most DMA channels because of their relatively low service rates.

#### Timers

The ADSP-2148x has a total of three timers: a core timer that can generate periodic software interrupts and two generalpurpose timers that can generate periodic interrupts and be independently set to operate in one of three modes:

- Pulse waveform generation mode

- Pulse width count/capture mode

- External event watchdog mode

The core timer can be configured to use FLAG3 as a timer expired signal, and the general-purpose timers have one bidirectional pin and four registers that implement its mode of operation: a 6-bit configuration register, a 32-bit count register, a 32-bit period register, and a 32-bit pulse width register. A single control and status register enables or disables the generalpurpose timer.

### 2-Wire Interface Port (TWI)

The TWI is a bidirectional 2-wire, serial bus used to move 8-bit data while maintaining compliance with the I<sup>2</sup>C bus protocol. The TWI master incorporates the following features:

- 7-bit addressing

- Simultaneous master and slave operation on multiple device systems with support for multi master data arbitration

- · Digital filtering and timed event processing

- 100 kbps and 400 kbps data rates

- Low interrupt rate

# **I/O PROCESSOR FEATURES**

The I/O processors provide up to 65 channels of DMA, as well as an extensive set of peripherals.

### DMA Controller

The processor's on-chip DMA controller allows data transfers without processor intervention. The DMA controller operates independently and invisibly to the processor core, allowing DMA operations to occur while the core is simultaneously executing its program instructions. DMA transfers can occur between the ADSP-2148x's internal memory and its serial ports, the SPI-compatible (serial peripheral interface) ports, the IDP (input data port), the PDAP, or the UART. The DMA channel summary is shown in Table 8.

Programs can be downloaded to the ADSP-2148x using DMA transfers. Other DMA features include interrupt generation upon completion of DMA transfers and DMA chaining for automatic linked DMA transfers.

### Table 8. DMA Channels

| Peripheral       | DMA Channels |

|------------------|--------------|

| SPORTs           | 16           |

| IDP/PDAP         | 8            |

| SPI              | 2            |

| UART             | 2            |

| External Port    | 2            |

| Accelerators     | 2            |

| Memory-to-Memory | 2            |

| MLB <sup>1</sup> | 31           |

<sup>1</sup>Automotive models only.

# **PIN FUNCTION DESCRIPTIONS**

Table 11. Pin Descriptions

| Name                 | Tuno                | State<br>During/<br>After Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|---------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR <sub>23-0</sub> | Type<br>I/O/T (ipu) | High-Z/<br>driven low<br>(boot) | <b>External Address.</b> The processor outputs addresses for external memory and peripherals on these pins. The ADDR pins can be multiplexed to support the external memory interface address, and FLAGS15–8 (I/O) and PWM (O). After reset, all ADDR pins are in external memory interface mode and FLAG(0–3) pins are in FLAGS mode (default). When configured in the IDP_PDAP_CTL register, IDP channel 0 scans the ADDR <sub>23-4</sub> pins for parallel input data.                                                                                                                                        |

| DATA <sub>15-0</sub> | I/O/T (ipu)         | High-Z                          | <b>External Data.</b> The data pins can be multiplexed to support the external memory interface data (I/O), and FLAGS <sub>7-0</sub> (I/O).                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AMI_ACK              | l (ipu)             |                                 | <b>Memory Acknowledge.</b> External devices can deassert AMI_ACK (low) to add wait states to an external memory access. AMI_ACK is used by I/O devices, memory controllers, or other peripherals to hold off completion of an external memory access.                                                                                                                                                                                                                                                                                                                                                            |

| MS <sub>0-1</sub>    | O/T (ipu)           | High-Z                          | <b>Memory Select Lines 0–1.</b> These lines are asserted (low) as chip selects for the corresponding banks of external memory. The $\overline{\text{MS}}_{1-0}$ lines are decoded memory address lines that change at the same time as the other address lines. When no external memory access is occurring the $\overline{\text{MS}}_{1-0}$ lines are inactive; they are active however when a conditional memory access instruction is executed, when the condition evaluates as true. The $\overline{\text{MS1}}$ pin can be used in EPORT/FLASH boot mode. For more information, see the hardware reference. |

| AMI_RD               | O/T (ipu)           | High-Z                          | <b>AMI Port Read Enable.</b> AMI_RD is asserted whenever the processor reads a word from external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AMI_WR               | O/T (ipu)           | High-Z                          | <b>AMI Port Write Enable.</b> AMI_WR is asserted when the processor writes a word to external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FLAG0/IRQ0           | I/O (ipu)           | FLAG[0]<br>INPUT                | FLAG0/Interrupt Request0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FLAG1/IRQ1           | I/O (ipu)           | FLAG[1]<br>INPUT                | FLAG1/Interrupt Request1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FLAG2/IRQ2/MS2       | I/O (ipu)           | FLAG[2]<br>INPUT                | FLAG2/Interrupt Request2/Memory Select2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FLAG3/TMREXP/MS3     | I/O (ipu)           | FLAG[3]<br>INPUT                | FLAG3/Timer Expired/Memory Select3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

The following symbols appear in the Type column of this table: **A** = asynchronous, **I** = input, **O** = output, **S** = synchronous, **A/D** = active drive, **O/D** = open drain, and **T** = three-state, **ipd** = internal pull-down resistor, **ipu** = internal pull-up resistor.

The internal pull-up (ipu) and internal pull-down (ipd) resistors are designed to hold the internal path from the pins at the expected logic levels. To pull-up or pull-down the external pads to the expected logic levels, use external resistors. Internal pull-up/pull-down resistors cannot be enabled/disabled and the value of these resistors cannot be programmed. The range of an ipu resistor can be between  $26 \text{ k}\Omega$ - $63 \text{ k}\Omega$ . The range of an ipd resistor can be between  $31 \text{ k}\Omega$ - $85 \text{k}\Omega$ . The three-state voltage of ipu pads will not reach to the full V<sub>DD\_EXT</sub> level; at typical conditions the voltage is in the range of 2.3 V to 2.7 V.

In this table, all pins are LVTTL compliant with the exception of the thermal diode pins.

# **ELECTRICAL CHARACTERISTICS**

|                                   |                                          |                                                                           |     | 300 MHz / 350 MHz / 400 MH | lz / 450 MHz                 |      |

|-----------------------------------|------------------------------------------|---------------------------------------------------------------------------|-----|----------------------------|------------------------------|------|

| Parameter <sup>1</sup>            | Description                              | Test Conditions                                                           | Min | Тур                        | Max                          | Unit |

| V <sub>OH</sub> <sup>2</sup>      | High Level Output<br>Voltage             | @ $V_{DD\_EXT} = Min$ ,<br>$I_{OH} = -1.0 \text{ mA}^3$                   | 2.4 |                            |                              | V    |

| V <sub>OL</sub> <sup>2</sup>      | Low Level Output<br>Voltage              | @ $V_{DD\_EXT} = Min$ ,<br>$I_{OL} = 1.0 \text{ mA}^3$                    |     |                            | 0.4                          | v    |

| I <sub>IH</sub> <sup>4, 5</sup>   | High Level Input Current                 | @ V <sub>DD_EXT</sub> = Max,<br>V <sub>IN</sub> = V <sub>DD_EXT</sub> Max |     |                            | 10                           | μΑ   |

| I <sub>IL</sub> <sup>4</sup>      | Low Level Input Current                  | $@V_{DD_{EXT}} = Max, V_{IN} = 0 V$                                       |     |                            | 10                           | μA   |

| I <sub>ILPU</sub> <sup>5</sup>    | Low Level Input Current<br>Pull-up       | $@V_{DD_{EXT}} = Max, V_{IN} = 0 V$                                       |     |                            | 200                          | μA   |

| I <sub>OZH</sub> <sup>6, 7</sup>  | Three-State Leakage<br>Current           | @ V <sub>DD_EXT</sub> = Max,<br>V <sub>IN</sub> = V <sub>DD_EXT</sub> Max |     |                            | 10                           | μA   |

| I <sub>OZL</sub> <sup>6</sup>     | Three-State Leakage<br>Current           | $@V_{DD_{EXT}} = Max, V_{IN} = 0 V$                                       |     |                            | 10                           | μA   |

| I <sub>OZLPU</sub> <sup>7</sup>   | Three-State Leakage<br>Current Pull-up   | $@V_{DD_{EXT}} = Max, V_{IN} = 0 V$                                       |     |                            | 200                          | μA   |

| I <sub>OZHPD</sub> <sup>8</sup>   | Three-State Leakage<br>Current Pull-down | @ V <sub>DD_EXT</sub> = Max,<br>V <sub>IN</sub> = V <sub>DD_EXT</sub> Max |     |                            | 200                          | μA   |

| I <sub>DD_INT</sub> 9             | Supply Current (Internal)                | f <sub>CCLK</sub> > 0 MHz                                                 |     |                            | Table 14 + Table 15<br>× ASF | mA   |

| I <sub>DD_INT</sub>               | Supply Current (Internal)                | $V_{DDINT} = 1.1 \text{ V, ASF} = 1,$<br>T <sub>J</sub> = 25°C            |     | 410 / 450 / 500 / 550      |                              | mA   |

| C <sub>IN</sub> <sup>10, 11</sup> | Input Capacitance                        | T <sub>CASE</sub> = 25°C                                                  |     |                            | 5                            | pF   |

<sup>1</sup> Specifications subject to change without notice.

<sup>2</sup> Applies to output and bidirectional pins: ADDR23-0, DATA15-0, <u>AMI\_RD</u>, <u>AMI\_WR</u>, FLAG3-0, DAI\_Px, DPI\_Px, <u>EMU</u>, TDO, <u>RESETOUT</u> MLBSIG, MLBDAT, MLBDO, MLBSO, <u>SDRAS</u>, <u>SDCAS</u>, <u>SDWE</u>, SDCKE, SDA10, SDDQM, <u>MS0-1</u>.

<sup>3</sup>See Output Drive Currents on Page 55 for typical drive current capabilities.

<sup>4</sup>Applies to input pins: BOOT\_CFGx, CLK\_CFGx, TCK, RESET, CLKIN.

<sup>5</sup> Applies to input pins with internal pull-ups: TRST, TMS, TDI.

<sup>6</sup>Applies to three-statable pin: TDO.

<sup>7</sup>Applies to three-statable pins with pull-ups: DAI\_Px, DPI\_Px, EMU.

<sup>8</sup>Applies to three-statable pin with pull-down: SDCLK.

<sup>9</sup>See Engineer-to-Engineer Note Estimating Power for ADSP-214xx SHARC Processors (EE-348) for further information.

<sup>10</sup>Applies to all signal pins.

<sup>11</sup>Guaranteed, but not tested.

Note the definitions of the clock periods that are a function of CLKIN and the appropriate ratio control shown in Table 18. All of the timing specifications for the ADSP-2148x peripherals are defined in relation to  $t_{PCLK}$ . See the peripheral specific section for each peripheral's timing information.

### Table 18. Clock Periods

| Timing             |                                                |

|--------------------|------------------------------------------------|

| Requirements       | Description                                    |

| t <sub>CK</sub>    | CLKIN Clock Period                             |

| t <sub>CCLK</sub>  | Processor Core Clock Period                    |

| t <sub>PCLK</sub>  | Peripheral Clock Period = $2 \times t_{CCLK}$  |

| t <sub>SDCLK</sub> | SDRAM Clock Period = $(t_{CCLK}) \times SDCKR$ |

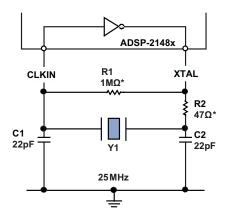

Figure 4 shows core to CLKIN relationships with external oscillator or crystal. The shaded divider/multiplier blocks denote where clock ratios can be set through hardware or software using the power management control register (PMCTL). For more information, see the hardware reference.

Table 19. Power Up Sequencing Timing Requirements (Processor Startup)

### **Power-Up Sequencing**

The timing requirements for processor startup are given in Table 19. While no specific power-up sequencing is required between  $V_{DD\_EXT}$  and  $V_{DD\_INT}$ , there are some considerations that system designs should take into account.

- No power supply should be powered up for an extended period of time (> 200 ms) before another supply starts to ramp up.

- If the  $V_{DD\_INT}$  power supply comes up after  $V_{DD\_EXT}$ , any pin, such as RESETOUT and RESET, may actually drive momentarily until the  $V_{DD\_INT}$  rail has powered up. Systems sharing these signals on the board must determine if there are any issues that need to be addressed based on this behavior.

Note that during power-up, when the  $V_{DD\_INT}$  power supply comes up after  $V_{DD\_EXT}$ , a leakage current of the order of threestate leakage current pull-up, pull-down may be observed on any pin, even if that is an input only (for example the RESET pin) until the  $V_{DD\_INT}$  rail has powered up.

| Parameter                        |                                                                | Min                                     | Max  | Unit |

|----------------------------------|----------------------------------------------------------------|-----------------------------------------|------|------|

| Timing Requirem                  | ents                                                           |                                         |      |      |

| t <sub>RSTVDD</sub>              | RESET Low Before V <sub>DD_EXT</sub> or V <sub>DD_INT</sub> On | 0                                       |      | ms   |

| t <sub>IVDDEVDD</sub>            | V <sub>DD_INT</sub> On Before V <sub>DD_EXT</sub>              | -200                                    | +200 | ms   |

| t <sub>CLKVDD</sub> <sup>1</sup> | CLKIN Valid After $V_{DD_{INT}}$ and $V_{DD_{EXT}}$ Valid      | 0                                       | 200  | ms   |

| t <sub>CLKRST</sub>              | CLKIN Valid Before RESET Deasserted                            | 10 <sup>2</sup>                         |      | μs   |

| t <sub>PLLRST</sub>              | PLL Control Setup Before RESET Deasserted                      | 20 <sup>3</sup>                         |      | μs   |

| Switching Charac                 | cteristic                                                      |                                         |      |      |

| t <sub>CORERST</sub> 4, 5        | Core Reset Deasserted After RESET Deasserted                   | $4096 \times t_{CK} + 2 \times t_{CCL}$ | .K   |      |

<sup>1</sup>Valid V<sub>DD\_INT</sub> and V<sub>DD\_EXT</sub> assumes that the supplies are fully ramped to their nominal values (it does not matter which supply comes up first). Voltage ramp rates can vary from microseconds to hundreds of milliseconds depending on the design of the power supply subsystem.

<sup>2</sup> Assumes a stable CLKIN signal, after meeting worst-case startup timing of crystal oscillators. Refer to your crystal oscillator manufacturer's data sheet for startup time. Assume a 25 ms maximum oscillator startup time if using the XTAL pin and internal oscillator circuit in conjunction with an external crystal.

<sup>3</sup>Based on CLKIN cycles.

<sup>4</sup> Applies after the power-up sequence is complete. Subsequent resets require a minimum of four CLKIN cycles for RESET to be held low in order to properly initialize and propagate default states at all I/O pins.

<sup>5</sup>The 4096 cycle count depends on t<sub>SRST</sub> specification in Table 21. If setup time is not met, one additional CLKIN cycle may be added to the core reset time, resulting in 4097 cycles maximum.

### **Clock Signals**

The ADSP-2148x can use an external clock or a crystal. See the CLKIN pin description in Table 11 on Page 14. Programs can configure the processor to use its internal clock generator by connecting the necessary components to CLKIN and XTAL. Figure 7 shows the component connections used for a crystal

operating in fundamental mode. Note that the clock rate is achieved using a 25 MHz crystal and a PLL multiplier ratio 16:1 (CCLK:CLKIN achieves a clock speed of 400 MHz). To achieve the full core clock rate, programs need to configure the multiplier bits in the PMCTL register.

CHOOSE C1 AND C2 BASED ON THE CRYSTAL Y1. R2 SHOULD BE CHOSEN TO LIMIT CRYSTAL DRIVE

POWER. REFER TO CRYSTAL MANUFACTURER'S

**\*TYPICAL VALUES**

Figure 7. Recommended Circuit for Fundamental Mode Crystal Operation

SPECIFICATIONS.

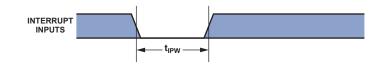

### Interrupts

The following timing specification applies to the FLAG0, FLAG1, and FLAG2 pins when they are configured as  $\overline{IRQ0}$ , IRQ1, and  $\overline{IRQ2}$  interrupts, as well as the DAI\_P20-1 and DPI\_P14-1 pins when they are configured as interrupts.

### Table 23. Interrupts

| Parameter        |                  | Min Max                 | Unit |

|------------------|------------------|-------------------------|------|

| Timing Requir    | rement           |                         |      |

| t <sub>IPW</sub> | IRQx Pulse Width | $2 \times t_{PCLK} + 2$ | ns   |

Figure 10. Interrupts

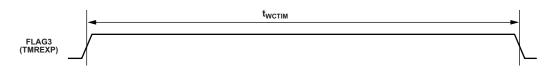

#### **Core Timer**

The following timing specification applies to FLAG3 when it is configured as the core timer (TMREXP).

### Table 24. Core Timer

| Parameter   |                    | Min                     | Мах | Unit |

|-------------|--------------------|-------------------------|-----|------|

| Switching C | haracteristic      |                         |     |      |

| twctim      | TMREXP Pulse Width | $4 \times t_{PCLK} - 1$ |     | ns   |

Figure 11. Core Timer

# Watchdog Timer Timing

### Table 27. Watchdog Timer Timing

| Parameter          |                                                               | Min                       | Мах  | Unit |

|--------------------|---------------------------------------------------------------|---------------------------|------|------|

| Timing Requ        | uirement                                                      |                           |      |      |

| tWDTCLKPER         |                                                               | 100                       | 1000 | ns   |

| Switching C        | Characteristics                                               |                           |      |      |

| t <sub>RST</sub>   | WDT Clock Rising Edge to Watchdog Timer<br>RESET Falling Edge | 3                         | 6.4  | ns   |

| t <sub>RSTPW</sub> | Reset Pulse Width                                             | $64 \times t_{WDTCLKPER}$ |      | ns   |

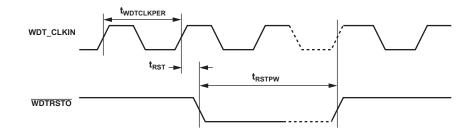

Figure 14. Watchdog Timer Timing

### Pin to Pin Direct Routing (DAI and DPI)

For direct pin connections only (for example DAI\_PB01\_I to DAI\_PB02\_O).

### Table 28. DAI/DPI Pin to Pin Routing

| Parameter                                                               |  | Min | Max | Unit |

|-------------------------------------------------------------------------|--|-----|-----|------|

| Timing Requirement                                                      |  |     |     |      |

| t <sub>DPIO</sub> Delay DAI/DPI Pin Input Valid to DAI/DPI Output Valid |  | 1.5 | 12  | ns   |

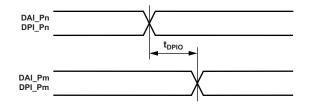

Figure 15. DAI Pin to Pin Direct Routing

### AMI Read

Use these specifications for asynchronous interfacing to memories. Note that timing for AMI\_ACK, ADDR, DATA, AMI\_RD, AMI\_WR, and strobe timing parameters only apply to asynchronous access mode.

### Table 32. AMI Read

| Parameter                           |                                        | Min                         | Мах                   | Unit |

|-------------------------------------|----------------------------------------|-----------------------------|-----------------------|------|

| Timing Requ                         | irements                               |                             |                       |      |

| t <sub>DAD</sub> <sup>1, 2, 3</sup> | Address Selects Delay to Data Valid    |                             | W + $t_{SDCLK}$ – 5.4 | ns   |

| t <sub>DRLD</sub> <sup>1, 3</sup>   | AMI_RD Low to Data Valid               |                             | W – 3.2               | ns   |

| t <sub>SDS</sub>                    | Data Setup to AMI_RD High              | 2.5                         |                       | ns   |

| HDRH <sup>4, 5</sup>                | Data Hold from AMI_RD High             | 0                           |                       | ns   |

| DAAK <sup>2, 6</sup>                | AMI_ACK Delay from Address, Selects    |                             | $t_{SDCLK} - 9.5 + W$ | ns   |

| DSAK <sup>4</sup>                   | AMI_ACK Delay from AMI_RD Low          |                             | W – 7                 | ns   |

| Switching Ch                        | paracteristics                         |                             |                       |      |

| t <sub>DRHA</sub>                   | Address Selects Hold After AMI_RD High | RHC + 0.20                  |                       | ns   |

| DARL <sup>2</sup>                   | Address Selects to AMI_RD Low          | t <sub>SDCLK</sub> – 3.8    |                       | ns   |

| RW                                  | AMI_RD Pulse Width                     | W – 1.4                     |                       | ns   |

| t <sub>RWR</sub>                    | AMI_RD High to AMI_RD Low              | HI + t <sub>SDCLK</sub> – 1 |                       | ns   |

W = (number of wait states specified in AMICTLx register)  $\times$  t<sub>SDCLK</sub>.

$\mathsf{RHC} = (\mathsf{number of Read Hold Cycles specified in AMICTLx register}) \times t_{\mathsf{SDCLK}}$

Where PREDIS = 0

HI = RHC (if IC=0): Read to Read from same bank

$HI = RHC + t_{SDCLK}$  (if IC>0): Read to Read from same bank

HI = RHC + IC: Read to Read from different bank

$HI = RHC + Max (IC, (4 \times t_{SDCLK}))$ : Read to Write from same or different bank

Where PREDIS = 1

$HI = RHC + Max (IC, (4 \times t_{SDCLK}))$ : Read to Write from same or different bank

$HI = RHC + (3 \times t_{SDCLK})$ : Read to Read from same bank

HI = RHC + Max (IC, (3 × t<sub>SDCLK</sub>): Read to Read from different bank

$\mathsf{IC} = (\mathsf{number of idle cycles specified in AMICTLx register}) \times \mathsf{t}_{\mathsf{SDCLK}}$

H = (number of hold cycles specified in AMICTLx register)  $\times$  tSDCLK

<sup>1</sup>Data delay/setup: System must meet t<sub>DAD</sub>, t<sub>DRLD</sub>, or t<sub>SDS</sub>.

<sup>2</sup> The falling edge of  $\overline{\text{MS}}$ x, is referenced.

<sup>3</sup>The maximum limit of timing requirement values for t<sub>DAD</sub> and t<sub>DRLD</sub> parameters are applicable for the case where AMI\_ACK is always high and when the ACK feature is not used.

<sup>4</sup>Note that timing for AMI\_ACK, ADDR, DATA, AMI\_RD, AMI\_WR, and strobe timing parameters only apply to asynchronous access mode.

<sup>5</sup> Data hold: User must meet t<sub>HDRH</sub> in asynchronous access mode. See Test Conditions on Page 55 for the calculation of hold times given capacitive and dc loads.

<sup>6</sup>AMI\_ACK delay/setup: User must meet t<sub>DAAK</sub>, or t<sub>DSAK</sub>, for deassertion of AMI\_ACK (low).

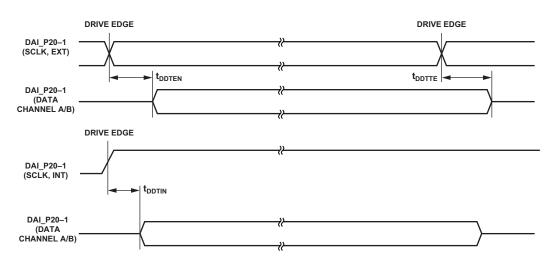

### Serial Ports

In slave transmitter mode and master receiver mode, the maximum serial port frequency is  $f_{PCLK}/8$ . In master transmitter mode and slave receiver mode, the maximum serial port clock frequency is  $f_{PCLK}/4$ . To determine whether communication is possible between two devices at clock speed n, the following

specifications must be confirmed: 1) frame sync delay and frame sync setup and hold; 2) data delay and data setup and hold; and 3) SCLK width.

Serial port signals (SCLK, frame sync, Data Channel A, Data Channel B) are routed to the DAI\_P20-1 pins using the SRU. Therefore, the timing specifications provided below are valid at the DAI\_P20-1 pins.

| Parameter                      |                                                                                                         | Min                                | Max   | Unit |

|--------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------|-------|------|

| Timing Requ                    | uirements                                                                                               |                                    |       |      |

| t <sub>SFSE</sub> 1            | Frame Sync Setup Before SCLK<br>(Externally Generated Frame Sync in either Transmit or Receive<br>Mode) | 2.5                                |       | ns   |

| t <sub>HFSE</sub> 1            | Frame Sync Hold After SCLK<br>(Externally Generated Frame Sync in either Transmit or Receive<br>Mode)   | 2.5                                |       | ns   |

| t <sub>SDRE</sub> <sup>1</sup> | Receive Data Setup Before Receive SCLK                                                                  | 1.9                                |       | ns   |

| t <sub>HDRE</sub> 1            | Receive Data Hold After SCLK                                                                            | 2.5                                |       | ns   |

| t <sub>SCLKW</sub>             | SCLK Width                                                                                              | $(t_{PCLK} \times 4) \div 2 - 1.5$ |       | ns   |

| t <sub>SCLK</sub>              | SCLK Period                                                                                             | $t_{PCLK} \times 4$                |       | ns   |

| Switching C                    | haracteristics                                                                                          |                                    |       |      |

| t <sub>DFSE</sub> <sup>2</sup> | Frame Sync Delay After SCLK<br>(Internally Generated Frame Sync in either Transmit or Receive Mode)     |                                    | 10.25 | ns   |

| t <sub>HOFSE</sub> 2           | Frame Sync Hold After SCLK                                                                              | 2                                  |       |      |

|                                | (Internally Generated Frame Sync in either Transmit or Receive Mode)                                    |                                    |       | ns   |

| t <sub>DDTE</sub> <sup>2</sup> | Transmit Data Delay After Transmit SCLK                                                                 |                                    | 9     | ns   |

| t <sub>HDTE</sub> <sup>2</sup> | Transmit Data Hold After Transmit SCLK                                                                  | 2                                  |       | ns   |

### Table 34. Serial Ports—External Clock

<sup>1</sup>Referenced to sample edge.

<sup>2</sup>Referenced to drive edge.

### Table 35. Serial Ports—Internal Clock

| Paramet                          | er                                                                             | Min                       | Max                       | Unit |

|----------------------------------|--------------------------------------------------------------------------------|---------------------------|---------------------------|------|

| Timing R                         | equirements                                                                    |                           |                           |      |

| t <sub>SFSI</sub> <sup>1</sup>   | Frame Sync Setup Before SCLK                                                   | 7                         |                           |      |

|                                  | (Externally Generated Frame Sync in either Transmit or Receive Mode)           |                           |                           | ns   |

| t <sub>HFSI</sub> 1              | Frame Sync Hold After SCLK                                                     | 2.5                       |                           |      |

|                                  | (Externally Generated Frame Sync in either Transmit or Receive Mode)           |                           |                           | ns   |

| t <sub>SDRI</sub> 1              | Receive Data Setup Before SCLK                                                 | 7                         |                           | ns   |

| t <sub>HDRI</sub> 1              | Receive Data Hold After SCLK                                                   | 2.5                       |                           | ns   |

| Switching                        | g Characteristics                                                              |                           |                           |      |

| t <sub>DFSI</sub> <sup>2</sup>   | Frame Sync Delay After SCLK (Internally Generated Frame Sync in Transmit Mode) |                           | 4                         | ns   |

| t <sub>HOFSI</sub> <sup>2</sup>  | Frame Sync Hold After SCLK (Internally Generated Frame Sync in Transmit Mode)  | -1                        |                           | ns   |

| t <sub>DFSIR</sub> <sup>2</sup>  | Frame Sync Delay After SCLK (Internally Generated Frame Sync in Receive Mode)  |                           | 9.75                      | ns   |

| t <sub>HOFSIR</sub> <sup>2</sup> | Frame Sync Hold After SCLK (Internally Generated Frame Sync in Receive Mode)   | -1                        |                           | ns   |

| t <sub>DDTI</sub> <sup>2</sup>   | Transmit Data Delay After SCLK                                                 |                           | 3.25                      | ns   |

| t <sub>HDTI</sub> <sup>2</sup>   | Transmit Data Hold After SCLK                                                  | -2                        |                           | ns   |

| t <sub>SCKLIW</sub>              | Transmit or Receive SCLK Width                                                 | $2 \times t_{PCLK} - 1.5$ | $2 \times t_{PCLK} + 1.5$ | ns   |

<sup>1</sup>Referenced to the sample edge.

<sup>2</sup>Referenced to drive edge.

#### Table 37. Serial Ports—Enable and Three-State

| Parameter                       |                                          | Min  | Max  | Unit |

|---------------------------------|------------------------------------------|------|------|------|

| Switching Ch                    | paracteristics                           |      |      |      |

| t <sub>DDTEN</sub> 1            | Data Enable from External Transmit SCLK  | 2    |      | ns   |

| t <sub>DDTTE</sub> <sup>1</sup> | Data Disable from External Transmit SCLK |      | 11.5 | ns   |

| t <sub>DDTIN</sub> <sup>1</sup> | Data Enable from Internal Transmit SCLK  | -1.5 |      | ns   |

<sup>1</sup>Referenced to drive edge.

Figure 23. Serial Ports—Enable and Three-State

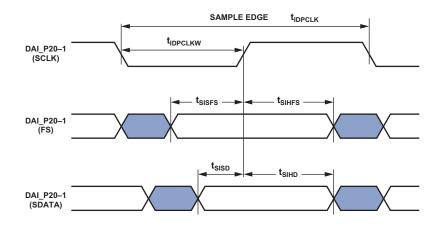

### Input Data Port (IDP)

The timing requirements for the IDP are given in Table 39. IDP signals are routed to the DAI\_P20-1 pins using the SRU. Therefore, the timing specifications provided below are valid at the DAI\_P20-1 pins.

### Table 39. Input Data Port (IDP)

| Parameter            |                                                  | Min                                                    | Max | Unit |

|----------------------|--------------------------------------------------|--------------------------------------------------------|-----|------|

| Timing Requ          | uirements                                        |                                                        |     |      |

| t <sub>SISFS</sub> 1 | Frame Sync Setup Before Serial Clock Rising Edge | 3.8                                                    |     | ns   |

| t <sub>SIHFS</sub> 1 | Frame Sync Hold After Serial Clock Rising Edge   | 2.5                                                    |     | ns   |

| t <sub>SISD</sub> 1  | Data Setup Before Serial Clock Rising Edge       | 2.5                                                    |     | ns   |

| t <sub>SIHD</sub> 1  | Data Hold After Serial Clock Rising Edge         | 2.5                                                    |     | ns   |

| t <sub>IDPCLKW</sub> | Clock Width                                      | $(t_{PCLK} \times 4) \div 2 -$                         | · 1 | ns   |

| t <sub>IDPCLK</sub>  | Clock Period                                     | (t <sub>PCLK</sub> × 4) ÷ 2 –<br>t <sub>PCLK</sub> × 4 |     | ns   |

<sup>1</sup> The serial clock, data, and frame sync signals can come from any of the DAI pins. The serial clock and frame sync signals can also come via PCG or SPORTs. PCG's input can be either CLKIN or any of the DAI pins.

Figure 25. IDP Master Timing

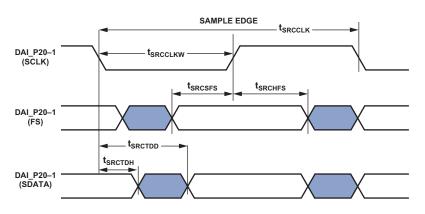

# Sample Rate Converter—Serial Output Port

For the serial output port, the frame sync is an input, and it should meet setup and hold times with regard to SCLK on the output port. The serial data output has a hold time and delay

#### Table 42. ASRC, Serial Output Port

specification with regard to serial clock. Note that serial clock rising edge is the sampling edge, and the falling edge is the drive edge.

| Parameter                        |                                                     | Min                              | Max | Unit |

|----------------------------------|-----------------------------------------------------|----------------------------------|-----|------|

| Timing Requi                     | irements                                            |                                  |     |      |

| t <sub>SRCSFS</sub> <sup>1</sup> | Frame Sync Setup Before Serial Clock Rising Edge    | 4                                |     | ns   |

| t <sub>SRCHFS</sub> <sup>1</sup> | Frame Sync Hold After Serial Clock Rising Edge      | 5.5                              |     | ns   |

| t <sub>SRCCLKW</sub>             | Clock Width                                         | $(t_{PCLK} \times 4) \div 2 - 1$ |     | ns   |

| t <sub>SRCCLK</sub>              | Clock Period                                        | $t_{PCLK} \times 4$              |     | ns   |

| Switching Ch                     | aracteristics                                       |                                  |     |      |

| t <sub>SRCTDD</sub> <sup>1</sup> | Transmit Data Delay After Serial Clock Falling Edge | 9                                | 9.9 | ns   |

| t <sub>SRCTDH</sub> 1            | Transmit Data Hold After Serial Clock Falling Edge  | 1                                |     | ns   |

<sup>1</sup>The serial clock, data, and frame sync signals can come from any of the DAI pins. The serial clock and frame sync signals can also come via PCG or SPORTs. PCG's input can be either CLKIN or any of the DAI pins.

Figure 28. ASRC Serial Output Port Timing

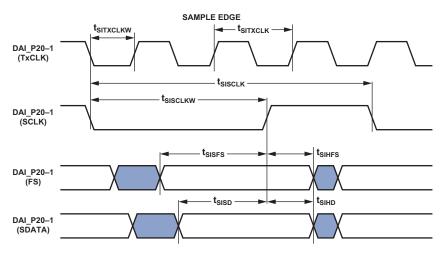

### S/PDIF Transmitter Input Data Timing

The timing requirements for the S/PDIF transmitter are given in Table 47. Input signals are routed to the DAI\_P20-1 pins using the SRU. Therefore, the timing specifications provided below are valid at the DAI\_P20-1 pins.

#### Table 47. S/PDIF Transmitter Input Data Timing

| Parameter                       |                                                  | Min | Мах | Unit |

|---------------------------------|--------------------------------------------------|-----|-----|------|

| Timing Requi                    | irements                                         |     |     |      |

| t <sub>SISFS</sub> <sup>1</sup> | Frame Sync Setup Before Serial Clock Rising Edge | 3   |     | ns   |

| t <sub>SIHFS</sub> 1            | Frame Sync Hold After Serial Clock Rising Edge   | 3   |     | ns   |

| t <sub>SISD</sub> 1             | Data Setup Before Serial Clock Rising Edge       | 3   |     | ns   |

| t <sub>SIHD</sub> 1             | Data Hold After Serial Clock Rising Edge         | 3   |     | ns   |

| t <sub>sitxclkw</sub>           | Transmit Clock Width                             | 9   |     | ns   |

| t <sub>SITXCLK</sub>            | Transmit Clock Period                            | 20  |     | ns   |

| t <sub>SISCLKW</sub>            | Clock Width                                      | 36  |     | ns   |

| t <sub>SISCLK</sub>             | Clock Period                                     | 80  |     | ns   |

<sup>1</sup>The serial clock, data, and frame sync signals can come from any of the DAI pins. The serial clock and frame sync signals can also come via PCG or SPORTs. PCG's input can be either CLKIN or any of the DAI pins.

Figure 33. S/PDIF Transmitter Input Timing

#### **Oversampling Clock (TxCLK) Switching Characteristics**

The S/PDIF transmitter requires an oversampling clock input. This high frequency clock (TxCLK) input is divided down to generate the internal biphase clock.

| Table 48. | <b>Oversampling Clock (TxCLK) Switching Characteristics</b> |

|-----------|-------------------------------------------------------------|

|-----------|-------------------------------------------------------------|

| Parameter                                     | Мах                                                       | Unit |

|-----------------------------------------------|-----------------------------------------------------------|------|

| Frequency for TxCLK = $384 \times$ Frame Sync | Oversampling Ratio × Frame Sync <= 1/t <sub>SITXCLK</sub> | MHz  |

| Frequency for TxCLK = $256 \times$ Frame Sync | 49.2                                                      | MHz  |

| Frame Rate (FS)                               | 192.0                                                     | kHz  |

### **Media Local Bus**

All the numbers given are applicable for all speed modes (1024 FS, 512 FS and 256 FS for 3-pin; 512 FS and 256 FS for 5-pin), unless otherwise specified. Please refer to the MediaLB specification document revision 3.0 for more details.

#### Table 52. MLB Interface, 3-Pin Specifications

| Paramete                       | r                                                                                  | Min      | Тур      | Max        | Unit         |

|--------------------------------|------------------------------------------------------------------------------------|----------|----------|------------|--------------|

| 3-Pin Chard                    | acteristics                                                                        |          |          |            |              |

| t <sub>MLBCLK</sub>            | MLB Clock Period<br>1024 FS                                                        |          | 20.3     |            | ns           |

|                                | 512 FS<br>256 FS                                                                   |          | 40<br>81 |            | ns<br>ns     |

| t <sub>MCKL</sub>              | MLBCLK Low Time<br>1024 FS                                                         | 6.1      |          |            | ns           |

|                                | 512 FS<br>256 FS                                                                   | 14<br>30 |          |            | ns<br>ns     |

| t <sub>MCKH</sub>              | MLBCLK High Time<br>1024 FS                                                        | 9.3      |          |            | ns           |

|                                | 512 FS<br>256 FS                                                                   | 14<br>30 |          |            | ns<br>ns     |

| t <sub>MCKR</sub>              | MLBCLK Rise Time (V <sub>IL</sub> to V <sub>IH</sub> )<br>1024 FS<br>512 FS/256 FS |          |          | 1<br>3     | ns<br>ns     |

| t <sub>MCKF</sub>              | MLBCLK Fall Time (V <sub>IH</sub> to V <sub>IL</sub> )<br>1024 FS<br>512 FS/256 FS |          |          | 1<br>3     | ns<br>ns     |

| t <sub>MPWV</sub> 1            | MLBCLK Pulse Width Variation<br>1024 FS<br>512 FS/256                              |          |          | 0.7<br>2.0 | nspp<br>nspp |

| t <sub>DSMCF</sub>             | DAT/SIG Input Setup Time                                                           | 1        |          |            | ns           |

| t <sub>DHMCF</sub>             | DAT/SIG Input Hold Time                                                            | 2        |          |            | ns           |

| t <sub>MCFDZ</sub>             | DAT/SIG Output Time to Three-state                                                 | 0        |          | 15         | ns           |

| t <sub>MCDRV</sub>             | DAT/SIG Output Data Delay From MLBCLK Rising Edge                                  |          |          | 8          | ns           |

| t <sub>MDZH</sub> <sup>2</sup> | Bus Hold Time<br>1024 FS                                                           | 2        |          |            | ns           |

|                                | 512 FS/256                                                                         | 4        |          |            | ns           |

| C <sub>MLB</sub>               | DAT/SIG Pin Load<br>1024 FS<br>512 FS/256                                          |          |          | 40<br>60   | pf<br>pf     |

<sup>1</sup>Pulse width variation is measured at 1.25 V by triggering on one edge of MLBCLK and measuring the spread on the other edge, measured in ns peak-to-peak (pp).

<sup>2</sup>The board must be designed to ensure that the high-impedance bus does not leave the logic state of the final driven bit for this time period. Therefore, coupling must be minimized while meeting the maximum capacitive load listed.

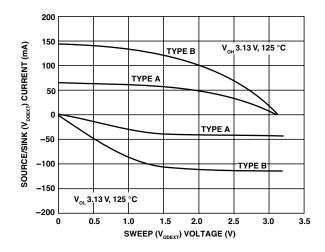

# **OUTPUT DRIVE CURRENTS**

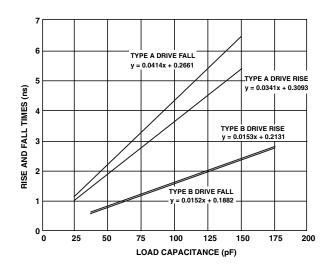

Figure 41 shows typical I-V characteristics for the output drivers of the ADSP-2148x, and Table 55 shows the pins associated with each driver. The curves represent the current drive capability of the output drivers as a function of output voltage.

#### Table 55. Driver Types

| Driver Type | Associated Pins                             |

|-------------|---------------------------------------------|

| А           | FLAG[0–3], AMI_ADDR[0–23], DATA[0–15],      |

|             | AMI_RD, AMI_WR, AMI_ACK, MS[1-0], SDRAS,    |

|             | SDCAS, SDWE, SDDQM, SDCKE, SDA10, EMU, TDO, |

|             | RESETOUT, DPI[1–14], DAI[1–20], WDTRSTO,    |

|             | MLBDAT, MLBSIG, MLBSO, MLBDO, MLBCLK        |

| В           | SDCLK                                       |

Figure 41. Typical Drive at Junction Temperature

# **TEST CONDITIONS**

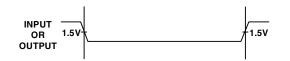

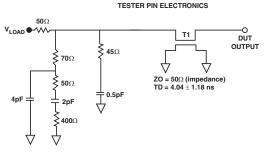

The ac signal specifications (timing parameters) appear in Table 21 on Page 26 through Table 54 on Page 54. These include output disable time, output enable time, and capacitive loading. The timing specifications for the SHARC apply for the voltage reference levels in Figure 42.

Timing is measured on signals when they cross the 1.5 V level as described in Figure 43. All delays (in nanoseconds) are measured between the point that the first signal reaches 1.5  $\rm V$  and the point that the second signal reaches 1.5 V.

Figure 43. Voltage Reference Levels for AC Measurements

NOTES

THE WORST CASE TRANSMISSION LINE DELAY IS SHOWN AND CAN BE USED FOR THE OUTPUT TIMING ANALYSIS TO REFLECT THE TRANSMISSION LINE EFFECT AND MUST BE CONSIDERED. THE TRANSMISSION LINE (TD) IS FOR LOAD ONLY AND DOES NOT AFFECT THE DATA SHEET TIMING SPECIFICATIONS.

ANALOG DEVICES RECOMMENDS USING THE IBIS MODEL TIMING FOR A GIVEN SYSTEM REQUIREMENT. IF NECESSARY, A SYSTEM MAY INCORPORATE EXTERNAL DRIVERS TO COMPENSATE FOR ANY TIMING DIFFERENCES.

Figure 42. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

# **CAPACITIVE LOADING**

Output delays and holds are based on standard capacitive loads: 30 pF on all pins (see Figure 42). Figure 46 and Figure 47 show graphically how output delays and holds vary with load capacitance. The graphs of Figure 44 through Figure 47 may not be linear outside the ranges shown for Typical Output Delay vs. Load Capacitance and Typical Output Rise Time (20% to 80%, V = Min) vs. Load Capacitance.

Figure 44. Typical Output Rise/Fall Time  $(20\% to 80\%, V_{DD EXT} = Max)$

Table 62. Automotive Models ADSP-21488, and ADSP-21489 176-Lead LQFP\_EP Lead Assignment (Numerical by Lead Number)

| Lead Name                     | Lead No. | Lead Name                 | Lead No. | Lead Name           | Lead No. | Lead Name           | Lead No |

|-------------------------------|----------|---------------------------|----------|---------------------|----------|---------------------|---------|

| SDDQM                         | 1        | V <sub>DD_EXT</sub>       | 45       | DAI_P10             | 89       | V <sub>DD_INT</sub> | 133     |

| MSO                           | 2        | DPI_P08                   | 46       | V <sub>DD_INT</sub> | 90       | FLAG0               | 134     |

| SDCKE                         | 3        | DPI_P07                   | 47       | V <sub>DD_EXT</sub> | 91       | FLAG1               | 135     |

| / <sub>DD_INT</sub>           | 4        | V <sub>DD INT</sub>       | 48       | DAI_P20             | 92       | FLAG2               | 136     |

| CLK_CFG1                      | 5        | DPI_P09                   | 49       | V <sub>DD_INT</sub> | 93       | MLBCLK              | 137     |

| ADDRO                         | 6        | DPI_P10                   | 50       | DAI_P08             | 94       | FLAG3               | 138     |

| BOOT_CFG0                     | 7        | DPI_P11                   | 51       | DAI_P14             | 95       | MLBDAT              | 139     |

| V <sub>DD_EXT</sub>           | 8        | DPI_P12                   | 52       | DAI_P04             | 96       | MLBDO               | 140     |

| ADDR1                         | 9        | DPI_P13                   | 53       | DAI_P18             | 97       | V <sub>DD_EXT</sub> | 141     |

| ADDR2                         | 10       | DPI_P14                   | 54       | DAI_P17             | 98       | MLBSIG              | 142     |

| ADDR3                         | 11       | DAI_P03                   | 55       | DAI_P16             | 99       | V <sub>DD_INT</sub> | 143     |

| ADDR4                         | 12       | NC                        | 56       | DAI_P12             | 100      |                     | 144     |

|                               |          |                           |          |                     |          |                     |         |

| ADDR5                         | 13       | V <sub>DD_EXT</sub>       | 57       | DAI_P15             | 101      | MLBSO               | 145     |

| BOOT_CFG1                     | 14       | NC                        | 58       | V <sub>DD_INT</sub> | 102      | EMU                 | 146     |

| GND                           | 15       | NC                        | 59       | DAI_P11             | 103      | DATA0               | 147     |

| ADDR6                         | 16       | NC                        | 60       | V <sub>DD_EXT</sub> | 104      | DATA1               | 148     |

| ADDR7                         | 17       | NC                        | 61       | V <sub>DD_INT</sub> | 105      | DATA2               | 149     |

| NC                            | 18       | V <sub>DD_INT</sub>       | 62       | BOOT_CFG2           | 106      | DATA3               | 150     |

| NC                            | 19       | NC                        | 63       | V <sub>DD_INT</sub> | 107      | TDO                 | 151     |

| ADDR8                         | 20       | NC                        | 64       | AMI_ACK             | 108      | DATA4               | 152     |

| ADDR9                         | 21       | V <sub>DD_INT</sub>       | 65       | GND                 | 109      | V <sub>DD_EXT</sub> | 153     |

| CLK_CFG0                      | 22       | NC                        | 66       | THD_M               | 110      | DATA5               | 154     |

| V <sub>DD_INT</sub>           | 23       | NC                        | 67       | THD_P               | 111      | DATA6               | 155     |

| CLKIN                         | 24       | V <sub>DD_INT</sub>       | 68       | V <sub>DD_THD</sub> | 112      | V <sub>DD_INT</sub> | 156     |

| XTAL                          | 25       | NC                        | 69       | V <sub>DD_INT</sub> | 113      | DATA7               | 157     |

| ADDR10                        | 26       | WDTRSTO                   | 70       | V <sub>DD_INT</sub> | 114      | TDI                 | 158     |

| SDA10                         | 27       | NC                        | 71       | MS1                 | 115      | SDCLK               | 159     |

| V <sub>DD_EXT</sub>           | 28       | V <sub>DD_EXT</sub>       | 72       | V <sub>DD INT</sub> | 116      | V <sub>DD_EXT</sub> | 160     |

| V <sub>DD_INT</sub>           | 29       | DAI_P07                   | 73       | WDT_CLKO            | 117      | DATA8               | 161     |

| ADDR11                        | 30       | DAI_P13                   | 74       | WDT_CLKIN           | 118      | DATA9               | 162     |

| ADDR12                        | 31       | DAI_P19                   | 75       | V <sub>DD_EXT</sub> | 119      | DATA10              | 163     |

| ADDR17                        | 32       | DAI_P01                   | 76       | ADDR23              | 120      | TCK                 | 164     |

| ADDR13                        | 33       | DAI_P02                   | 77       | ADDR22              | 121      | DATA11              | 165     |

|                               | 34       |                           | 78       | ADDR22<br>ADDR21    | 121      | DATA12              | 165     |

| V <sub>DD_INT</sub><br>ADDR18 | 34<br>35 | V <sub>DD_INT</sub><br>NC | 78<br>79 |                     | 122      | DATA12              | 167     |

|                               |          |                           |          |                     |          | DATA14<br>DATA13    |         |

| RESETOUT/RUNRSTIN             | 36       | NC                        | 80       | ADDR20              | 124      |                     | 168     |

|                               | 37       | NC                        | 81       | ADDR19              | 125      |                     | 169     |

| DPI_P01                       | 38       | NC                        | 82       | V <sub>DD_EXT</sub> | 126      | DATA15              | 170     |

| DPI_P02                       | 39       | NC                        | 83       | ADDR16              | 127      | SDWE                | 171     |

| DPI_P03                       | 40       | V <sub>DD_EXT</sub>       | 84       | ADDR15              | 128      | SDRAS               | 172     |

| V <sub>DD_INT</sub>           | 41       | V <sub>DD_INT</sub>       | 85       | V <sub>DD_INT</sub> | 129      | RESET               | 173     |

| DPI_P05                       | 42       | DAI_P06                   | 86       | ADDR14              | 130      | TMS                 | 174     |

| DPI_P04                       | 43       | DAI_P05                   | 87       | AMI_WR              | 131      | SDCAS               | 175     |

| DPI_P06                       | 44       | DAI_P09                   | 88       | AMI_RD              | 132      | V <sub>DD_INT</sub> | 176     |

|                               |          |                           |          |                     |          | GND                 | 177*    |

# **AUTOMOTIVE PRODUCTS**

The following models are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that these automotive models may have specifications that differ from the commercial models and designers should review the product Specifications on Page 18 section of this data sheet carefully. Only the automotive grade products shown in Table 63 are available for use in automotive applications. Contact your local ADI account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

# Table 63. Automotive Products

|                             | Notes |                    |        | Processor<br>Instruction |                     |                |

|-----------------------------|-------|--------------------|--------|--------------------------|---------------------|----------------|

| Model <sup>1, 2, 3, 4</sup> |       | Temperature Range⁵ | RAM    | Rate (Max)               | Package Description | Package Option |

| AD21486WBSWZ4Axx            | 6     | -40°C to +85°C     | 5 Mbit | 400 MHz                  | 100-Lead LQFP_EP    | SW-100-2       |

| AD21487WBSWZ4Axx            | 6     | -40°C to +85°C     | 5 Mbit | 400 MHz                  | 100-Lead LQFP_EP    | SW-100-2       |

| AD21487WBSWZ4Bxx            | 6     | –40°C to +85°C     | 5 Mbit | 400 MHz                  | 176-Lead LQFP_EP    | SW-176-2       |

| AD21488WBSWZ1Axx            |       | -40°C to +85°C     | 3 Mbit | 266 MHz                  | 100-Lead LQFP_EP    | SW-100-2       |

| AD21488WBSWZ2Axx            |       | –40°C to +85°C     | 3 Mbit | 300 MHz                  | 100-Lead LQFP_EP    | SW-100-2       |

| AD21488WBSWZ1Bxx            |       | –40°C to +85°C     | 2 Mbit | 266 MHz                  | 176-Lead LQFP_EP    | SW-176-2       |

| AD21488WBSWZ2Bxx            |       | –40°C to +85°C     | 3 Mbit | 266 MHz                  | 176-Lead LQFP_EP    | SW-176-2       |

| AD21488WBSWZ4Bxx            |       | –40°C to +85°C     | 3 Mbit | 400 MHz                  | 176-Lead LQFP_EP    | SW-176-2       |

| AD21489WBSWZ4xx             |       | -40°C to +85°C     | 5 Mbit | 400 MHz                  | 100-Lead LQFP_EP    | SW-100-2       |

| AD21489WBSWZ4xxRL           |       | –40°C to +85°C     | 5 Mbit | 400 MHz                  | 100-Lead LQFP_EP    | SW-100-2       |

| AD21489WBSWZ4Bxx            |       | –40°C to +85°C     | 5 Mbit | 400 MHz                  | 176-Lead LQFP_EP    | SW-176-2       |

<sup>1</sup>Z =RoHS Compliant Part.

$^{2}W$  = automotive applications.

<sup>3</sup>xx denotes the current die revision.

${}^{4}$ RL = Tape and Reel.

<sup>5</sup>Referenced temperature is ambient temperature. The ambient temperature is not a specification. Please see Operating Conditions on Page 18 for junction temperature (T<sub>j</sub>) specification which is the only temperature specification.

<sup>6</sup>This product contains IP from Dolby, DTS and DTLA. Proper software licenses required. Contact Analog Devices, Inc. for information.