# E. Kenesas Electronics America Inc - <u>R7FS128782A01CLM#AC1 Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM® Cortex®-M0+Core Size32-Bit Single-CoreSpeed32MHzConnectivityCANbus, DALI, PC, SCI, SPI, UART/USART, USBPeripheralsDMA, LVD, POR, PWM, WDTNumber of I/O28Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGA (4x4)Purchase URLInters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Inters/Int                                                                                                                                                                                                       |                            |                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed32MHzConnectivityCANbus, DALI, IPC, SCI, SPI, UART/USART, USBPeripheralsDMA, LVD, POR, PWM, WDTNumber of I/O28Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGA (4x4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Product Status             | Active                                                                                |

| Speed32MHzConnectivityCANbus, DALI, I²C, SCI, SPI, UART/USART, USBPeripheralsDMA, LVD, POR, PWM, WDTNumber of I/O28Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGA (4x4)bttps://www.ox/fl.com/unduct datail/rappers electropics amories/7fc1287820.01cm ac1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Core Processor             | ARM® Cortex®-M0+                                                                      |

| ConnectivityCANbus, DALI, I²C, SCI, SPI, UART/USART, USBPeripheralsDMA, LVD, POR, PWM, WDTNumber of I/O28Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGA (4x4)bttps://www.exfl.com/product.detail/concers.e.glectropics.americe/c7fc129292aD1clm.pc1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Core Size                  | 32-Bit Single-Core                                                                    |

| PeripheralsDMA, LVD, POR, PWM, WDTNumber of I/O28Program Memory Size256KB (256K × 8)Program Memory TypeFLASHEEPROM Size4K × 8RAM Size24K × 8Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGA (4x4)bttps://www.o.xfl.com/product detail/repaces electropics america/r2fc12878200.lclm ac1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Speed                      | 32MHz                                                                                 |

| Number of I/O28Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGA (4x4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Connectivity               | CANbus, DALI, I <sup>2</sup> C, SCI, SPI, UART/USART, USB                             |

| Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGA (4x4)bttps://www.ox.wfl.com/oreglust.detail/concers_clostopics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_interpics_inte | Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Program Memory TypeFLASHEEPROM Size4K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGASupplier Device Package36-WFLGA (4x4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Number of I/O              | 28                                                                                    |

| EEPROM Size4K x 8RAM Size24K x 8RAM Size24K x 8Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGASupplier Device Package36-WFLGA (4x4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Program Memory Size        | 256KB (256K x 8)                                                                      |

| RAM Size24K x 8Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGASupplier Device Package36-WFLGA (4x4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Program Memory Type        | FLASH                                                                                 |

| Voltage - Supply (Vcc/Vdd)1.6V ~ 5.5VData ConvertersA/D 13x14b; D/A 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case36-WFLGASupplier Device Package36-WFLGA (4x4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EEPROM Size                | 4K x 8                                                                                |

| Data Converters       A/D 13x14b; D/A 3x8b         Oscillator Type       Internal         Operating Temperature       -40°C ~ 85°C (TA)         Mounting Type       Surface Mount         Package / Case       36-WFLGA         Supplier Device Package       36-WFLGA (4x4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RAM Size                   | 24K x 8                                                                               |

| Oscillator Type     Internal       Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount       Package / Case     36-WFLGA       Supplier Device Package     36-WFLGA (4x4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                           |

| Operating Temperature       -40°C ~ 85°C (TA)         Mounting Type       Surface Mount         Package / Case       36-WFLGA         Supplier Device Package       36-WFLGA (4x4)         https://www.o.xfl.com/product.detail/represes.electronics.america/r7fc128782a01clm.ac1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Data Converters            | A/D 13x14b; D/A 3x8b                                                                  |

| Mounting Type     Surface Mount       Package / Case     36-WFLGA       Supplier Device Package     36-WFLGA (4x4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Oscillator Type            | Internal                                                                              |

| Package / Case     36-WFLGA       Supplier Device Package     36-WFLGA (4x4)       https://www.exfl.com/product.detail/reposes electropics america/r7fs128782a01clm.ac1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Supplier Device Package 36-WFLGA (4x4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Mounting Type              | Surface Mount                                                                         |

| https://www.a.vfl.com/product.dotail/rappesse.alectropics.america/r7fc129792a01clm.ac1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Package / Case             | 36-WFLGA                                                                              |

| Purchase URL https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs128782a01clm-ac1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Supplier Device Package    | 36-WFLGA (4x4)                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs128782a01clm-ac1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **General Precautions**

1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

3. Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

#### 4. Handling of unused pins

Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

5. Clock signals

After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

6. Voltage application waveform at input pin

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

#### 7. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

8. Differences between products

Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

# RENESAS

#### S128 MCU (Ultra Low-Power MCU)

#### 32-bit ARM® Cortex®-M0+ Microcontroller

Ultra low power 32-MHz ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ microcontroller, up to 256-KB code flash memory, 24-KB SRAM, Digital Addressable Lighting Interface, Capacitive Touch Sensing Unit, 14-bit A/D Converter, 8-bit D/A Converter, security and safety features.

# Features

#### ■ ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ Core

- ARM<sup>®</sup>v6-M architecture

- Maximum operating frequency: 32 MHz

- ARM<sup>®</sup> Memory Protection Unit (MPU) with 8 regions

- Debug and Trace: DWT, BPU, CoreSight<sup>™</sup> MTB-M0+

- CoreSight Debug Port: SW-DP

#### Memory

- Up to 256-KB code flash memory

- 4-KB data flash memory (up to 100,000 erase/write cycles)

- Up to 24-KB SRAM

- Memory protection units

- 128-bit unique ID

#### Connectivity

- USB 2.0 Full-Speed Module (USBFS)

On-chip transceiver with voltage regulator

- Compliant with USB Battery Charging Specification 1.2

Serial Communications Interface (SCI) × 3

- UART - Simple IIC

- Simple SPI

- Serial Peripheral Interface (SPI)  $\times 2$

- I<sup>2</sup>C bus interface (IIC)  $\times$  2

- CAN module (CAN)

- Digital Addressable Lighting Interface (DALI)

#### Analog

- 14-Bit A/D Converter (ADC14)

- 8-Bit D/A Converter (DAC8)  $\times$  3

- High-Speed Analog Comparator (ACMPHS) × 3

- Low-Power Analog Comparator (ACMPLP) × 2

- Operational Amplifier ( $\overline{OPAMP}$ ) × 4

- Temperature Sensor (TSN)

#### Timers

- General PWM Timer 32-Bit (GPT32)

- General PWM Timer 16-Bit High Resolution (GPT16H) × 3

- General PWM Timer 16-Bit (GPT16) × 3

- Asynchronous General-Purpose Timer (AGT) × 2

- Watchdog Timer (WDT)

#### Safety

- ECC in SRAM

- SRAM Parity Error Check

- Flash Area Protection

- ADC self-diagnosis function

- Clock Frequency Accuracy Measurement Circuit (CAC)

- Cyclic Redundancy Check (CRC) Calculator

- Data Operation Circuit (DOC)

- Port Output Enable for GPT (POEG)

- Independent Watchdog Timer (IWDT)

- GPIO Readback Level Detection

- Register Write Protection

- Main Oscillator Stop Detection

- Illegal memory access

#### System and Power Management

- Low-power modes

- RealTime Clock (RTC)

- Event Link Controller (ELC)

Data Transfer Controller (DT)

- Data Transfer Controller (DTC)Key Interrupt Function (KINT)

- Rey Interrupt Function

Power-on reset

- Low Voltage Detection with voltage settings

#### Security and Encryption

- AES128/256

- True Random Number Generator (TRNG)

- Human Machine Interface (HMI)

- Capacitive Touch Sensing Unit (CTSU)

## Multiple Clock Sources

- Main clock oscillator (MOSC)

- (1 to 20 MHz when VCC = 2.4 to 5.5 V) (1 to 8 MHz when VCC = 1.8 to 5.5 V)

- (1 to 4 MHz when VCC = 1.6 to 5.5 V)

- Sub-clock oscillator (SOSC) (32.768 kHz)

- High-speed on-chip oscillator (HOCO) (24, 32, 48, 64 MHz when VCC = 2.4 to 5.5 V) (24, 32, 48 MHz when VCC = 1.8 to 5.5 V) (24, 32 MHz when VCC = 1.6 to 5.5 V)

- Middle-speed on-chip oscillator (MOCO) (8 MHz)

- Low-speed on-chip oscillator (LOCO) (32.768 kHz)

- Independent watchdog timer OCO (15 kHz)

- Clock trim function for HOCO/MOCO/LOCO

# Clock out support

- General Purpose I/O Ports

- Up to 53 input/output pins

- Up to 3 CMOS input

- Up to 50 CMOS input/output

- Up to 5 5-V tolerant input/output (when VCC = 3.6 V)

Up to 2 pins high current (20 mA)

- Op to 2 pins night et

## Operating Voltage

- VCC: 1.6 to 5.5 V

- Operating Temperature and Packages

- Ta =  $-40^{\circ}$ C to  $+85^{\circ}$ C

- 36-pin LGA (4 mm × 4 mm, 0.5 mm pitch)

- Ta =  $-40^{\circ}$ C to  $+105^{\circ}$ C

- 64-pin LQFP (10 mm  $\times$  10 mm, 0.5 mm pitch)

- 48-pin LQFP (7 mm  $\times$  7 mm, 0.5 mm pitch)

- 32-pin LQFP (7 mm × 7 mm, 0.8 mm pitch)

48-pin QFN (7 mm × 7 mm, 0.5 mm pitch)

- 32-pin QFN (5 mm  $\times$  5 mm, 0.5 mm pitch)

# Table 2.5 $I/O V_{IH}, V_{IL}$ (2)

| Parameter                                       |                                                                                        | Symbol          | Min              | Тур | Мах           | Unit | Test<br>Conditions |

|-------------------------------------------------|----------------------------------------------------------------------------------------|-----------------|------------------|-----|---------------|------|--------------------|

| Schmitt trigger                                 | RES, NMI                                                                               | V <sub>IH</sub> | VCC × 0.8        | -   | -3            | V    | -                  |

| nput voltage                                    | Peripheral input pins                                                                  | V <sub>IL</sub> | -                | -   | VCC × 0.2     |      |                    |

|                                                 |                                                                                        | $\Delta V_T$    | VCC × 0.01       | -   | -             |      |                    |

| Input voltage<br>(except for<br>Schmitt trigger | 5V-tolerant ports*1                                                                    | V <sub>IH</sub> | VCC × 0.8        | -   | 5.8           |      |                    |

|                                                 |                                                                                        | V <sub>IL</sub> | -                | -   | VCC × 0.2     |      |                    |

| input pin)                                      | P000 to P004<br>P010 to P015<br>P500 to P502                                           | V <sub>IH</sub> | AVCC0 × 0.8      | -   | -             |      |                    |

|                                                 |                                                                                        | V <sub>IL</sub> | -                | -   | AVCC0 × 0.2   |      |                    |

|                                                 | P914, P915                                                                             | V <sub>IH</sub> | VCC_USB ×<br>0.8 | -   | VCC_USB + 0.3 |      |                    |

|                                                 |                                                                                        | V <sub>IL</sub> | -                | -   | VCC_USB × 0.2 | 1    |                    |

|                                                 | EXTAL                                                                                  | V <sub>IH</sub> | VCC × 0.8        | -   | -             | 1    |                    |

|                                                 | Input ports pins except for<br>P000 to P004, P010 to P015,<br>P500 to P502, P914, P915 | V <sub>IL</sub> | -                | -   | VCC × 0.2     |      |                    |

| Conditions: V | CC = AVCC0 = VCC_USB = VCC_USB_LDO = 1.6 to 2.7 V |

|---------------|---------------------------------------------------|

Note 1. P205, P206, P400, P401, P407 (total 5pins)

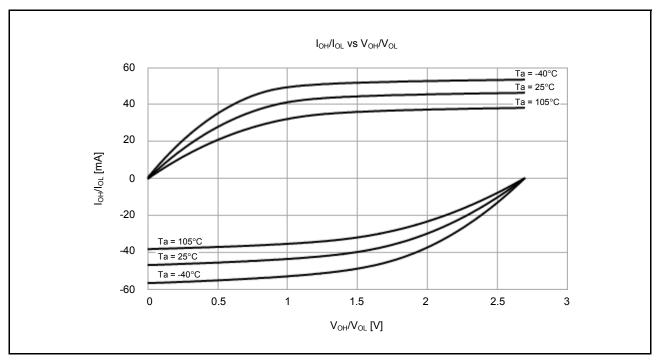

Figure 2.13 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> temperature characteristics at VCC = 2.7 V when middle drive output is selected (reference data)

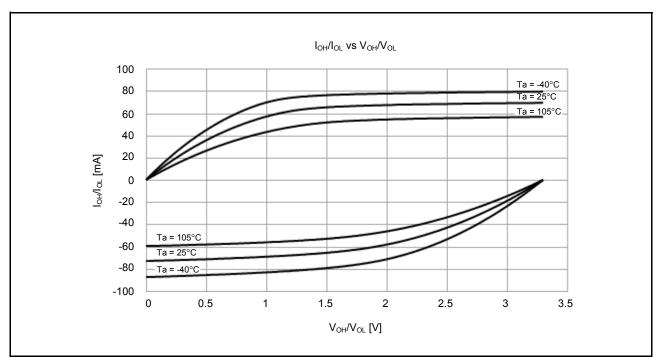

Figure 2.14 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> temperature characteristics at VCC = 3.3 V when middle drive output is selected (reference data)

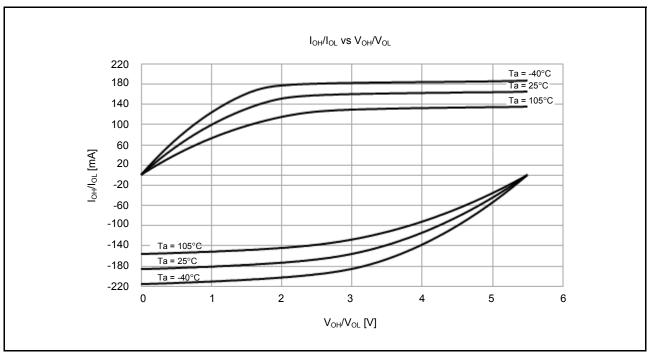

Figure 2.15 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> temperature characteristics at VCC = 5.5 V when middle drive output is selected (reference data)

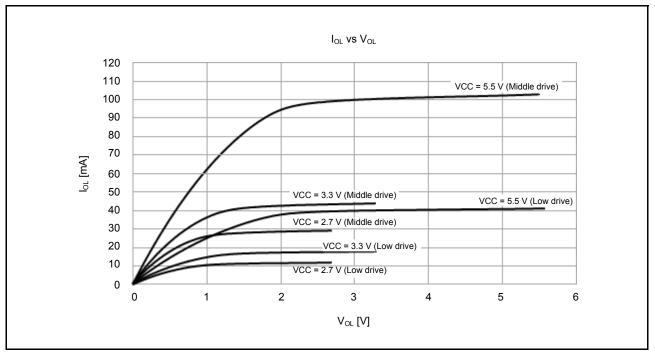

2.2.8 Output Characteristics for IIC I/O Pins

Figure 2.16  $V_{OH}/V_{OL}$  and  $I_{OH}/I_{OL}$  voltage characteristics at Ta = 25°C

# Table 2.11Operating and standby current (1) (2 of 2)Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| Parameter        |                                        |             |                                                                                        |                   | Symbol          | Typ* <sup>9</sup>              | Max   | Unit | Test<br>Conditions |

|------------------|----------------------------------------|-------------|----------------------------------------------------------------------------------------|-------------------|-----------------|--------------------------------|-------|------|--------------------|

| Supply current*1 | Low-voltage mode*3                     | Normal mode | All peripheral clock<br>disabled, while (1) code<br>executing from flash* <sup>5</sup> | ICLK = 4 MHz      | I <sub>CC</sub> | 1.5                            | -     | mA   | *7                 |

|                  |                                        |             | All peripheral clock<br>disabled, CoreMark code<br>executing from flash*5              | ICLK = 4 MHz      |                 | 1.4                            | -     |      |                    |

|                  |                                        |             | All peripheral clock<br>enabled, while (1) code<br>executing from flash* <sup>5</sup>  | ICLK = 4 MHz      |                 | 2.3                            | -     |      | *8                 |

|                  |                                        |             | All peripheral clock<br>enabled, code executing<br>from flash* <sup>5</sup>            | ICLK = 4 MHz      |                 | -                              | 4.0   |      |                    |

|                  |                                        | Sleep mode  | All peripheral clock disabled*5                                                        | ICLK = 4 MHz      |                 | 0.9                            | -     |      | *7                 |

|                  |                                        |             | All peripheral clock enabled*5                                                         | ICLK = 4 MHz      |                 | 1.7                            | -     |      | *8                 |

|                  | Subosc-<br>speed<br>mode <sup>*4</sup> | Normal mode | All peripheral clock<br>disabled, while (1) code<br>executing from flash* <sup>5</sup> | ICLK = 32.768 kHz | I <sub>CC</sub> | 5.9                            | -     | μA   | *7                 |

|                  |                                        |             | All peripheral clock<br>enabled, while (1) code<br>executing from flash* <sup>5</sup>  | ICLK = 32.768 kHz |                 | 13.0                           | -     |      | *8                 |

|                  |                                        |             | All peripheral clock<br>enabled, code executing<br>from flash* <sup>5</sup>            | ICLK = 32.768 kHz |                 | 128.3<br>(17.8)* <sup>10</sup> | 163.7 |      |                    |

|                  |                                        | Sleep mode  | All peripheral clock disabled*5                                                        | ICLK = 32.768 kHz |                 | 3.2                            | -     |      | *7                 |

|                  |                                        |             | All peripheral clock enabled*5                                                         | ICLK = 32.768 kHz | 1               | 10.0                           | -     | 1    | *8                 |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. The clock source is HOCO.

Note 3. The clock source is MOCO.

Note 4. The clock source is the sub-clock oscillator.

Note 5. This does not include BGO operation.

Note 6. This is the increase for programming or erasure of the ROM or flash memory for data storage during program execution.

Note 7. PCLKB and PCLKD are set to divided by 64.

Note 8. PCLKB and PCLKD are the same frequency as that of ICLK.

Note 9. VCC = 3.3 V.

Note 10. MOCO and DAC is stopped.

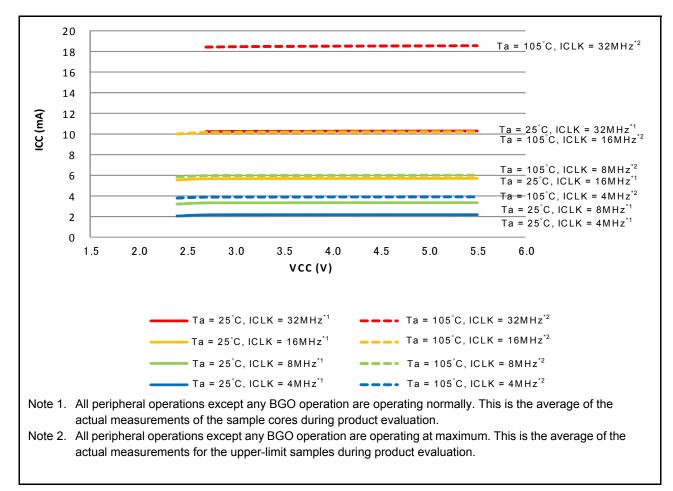

Figure 2.17 Voltage dependency in high-speed mode (reference data)

#### Table 2.18 Operation frequency in low-speed mode

Conditions: VCC = AVCC0 = 1.8 to 5.5 V

| Parameter |                                       |              | Symbol | Min      | Тур | Max* <sup>5</sup> | Unit |

|-----------|---------------------------------------|--------------|--------|----------|-----|-------------------|------|

| Operation | System clock (ICLK)*1, *2, *4         | 1.8 to 5.5 V | f      | 0.032768 | -   | 1                 | MHz  |

| frequency | Peripheral module clock (PCLKB)*4     | 1.8 to 5.5 V |        | -        | -   | 1                 |      |

|           | Peripheral module clock (PCLKD)*3, *4 | 1.8 to 5.5 V |        | -        | -   | 1                 |      |

Note 1. The lower-limit frequency of ICLK is 1 MHz while programming or erasing the flash memory.

Note 3. The lower-limit frequency of PCLKD is 1 MHz when the A/D converter is in use.

- Note 4. See section 8, Clock Generation Circuit in User's Manual for the relationship of frequencies between ICLK, PCLKB, and PCLKD.

- Note 5. The maximum value of operation frequency does not include internal oscillator errors. For details on the range of guaranteed operation, see Table 2.21, Clock timing.

#### Table 2.19 Operation frequency in low-voltage mode

Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| Parameter |                                       |              | Symbol | Min      | Тур | Max* <sup>5</sup> | Unit |

|-----------|---------------------------------------|--------------|--------|----------|-----|-------------------|------|

| Operation | System clock (ICLK)*1, *2, *4         | 1.6 to 5.5 V | f      | 0.032768 | -   | 4                 | MHz  |

| frequency | Peripheral module clock (PCLKB)*4     | 1.6 to 5.5 V |        | -        | -   | 4                 |      |

|           | Peripheral module clock (PCLKD)*3, *4 | 1.6 to 5.5 V |        | -        | -   | 4                 |      |

Note 1. The lower-limit frequency of ICLK is 1 MHz while programming or erasing the flash memory. When using ICLK for programming or erasing the flash memory at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

- Note 2. The frequency accuracy of ICLK must be ±3.5% during programming or erasing the flash memory. Confirm the frequency accuracy of the clock source.

- Note 3. The lower-limit frequency of PCLKD is 4 MHz at 2.4 V or above and 1 MHz at below 2.4 V when the 14-bit A/D converter is in use.

- Note 4. See section 8, Clock Generation Circuit in User's Manual for the relationship of frequencies between ICLK, PCLKB, and PCLKD.

- Note 5. The maximum value of operation frequency does not include internal oscillator errors. For details on the range of guaranteed operation, see Table 2.21, Clock timing.

#### Table 2.20 Operation frequency in Subosc-speed mode

Conditions: VCC = AVCC0 = 1.8 to 5.5 V

| Parameter | Parameter                             |              |   |         | Тур    | Max     | Unit |

|-----------|---------------------------------------|--------------|---|---------|--------|---------|------|

| Operation | System clock (ICLK)*1, *3             | 1.8 to 5.5 V | f | 27.8528 | 32.768 | 37.6832 | kHz  |

| frequency | Peripheral module clock (PCLKB)*3     | 1.8 to 5.5 V |   | -       | -      | 37.6832 |      |

|           | Peripheral module clock (PCLKD)*2, *3 | 1.8 to 5.5 V |   | -       | -      | 37.6832 |      |

Note 1. Programming and erasing the flash memory is not possible.

Note 2. The 14-bit A/D converter cannot be used.

Note 3. See section 8, Clock Generation Circuit in User's Manual for the relationship between ICLK, PCLKB, and PCLKD frequencies.

Note 2. The frequency accuracy of ICLK must be ±3.5% during programming or erasing the flash memory. Confirm the frequency accuracy of the clock source.

### Table 2.21Clock timing (2 of 2)

| Parameter                                  | Symbol              | Min | Тур | Max | Unit | Test conditions |

|--------------------------------------------|---------------------|-----|-----|-----|------|-----------------|

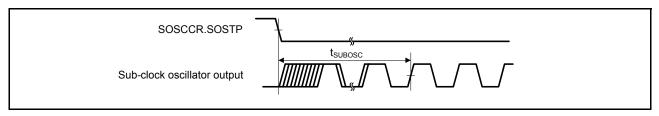

| Sub-clock oscillation stabilization time*2 | t <sub>SUBOSC</sub> | -   | 0.5 | -   | s    | Figure 2.28     |

Note 1. Time until the clock can be used after the main clock oscillator stop bit (MOSCCR.MOSTP) is set to 0 (operating) when the external clock is stable.

Note 2. After changing the setting of the SOSCCR.SOSTP bit to start sub-clock oscillator operation, only start using the sub-clock oscillator after the sub-clock oscillation stabilization wait time elapsed. Use the oscillator wait time value recommended by the oscillator manufacturer.

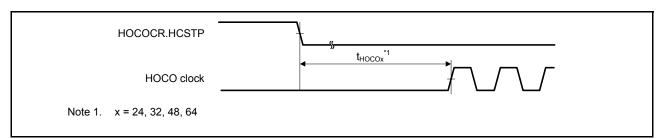

Note 3. The 48-MHz HOCO can be used within a VCC range of 1.8 V to 5.5 V.

Note 4. The 64-MHz HOCO can be used within a VCC range of 2.4 V to 5.5 V.

Note 5. This is a characteristic when the HOCOCR.HCSTP bit is cleared to 0 (oscillation) in the MOCO stop state. When the HOCOCR.HCSTP bit is cleared to 0 (oscillation) during MOCO oscillation, this specification is shortened by 1 µs.

Note 6. Check OSCSF.HOCOSF to confirm whether stabilization time has elapsed.

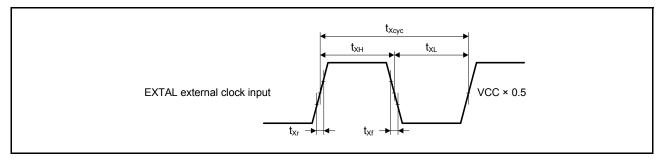

### Figure 2.25 EXTAL external clock input timing

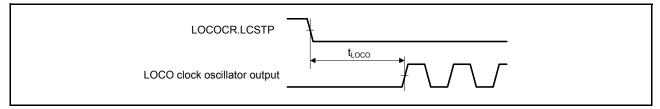

Figure 2.26 LOCO clock oscillation start timing

| Table 2.25 | Timing of recovery from low power modes (3) |

|------------|---------------------------------------------|

|------------|---------------------------------------------|

| Parameter                                        |                   |                                                                  |                                                                          |                    | Min | Тур | Max | Unit | Test<br>conditions |

|--------------------------------------------------|-------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|-----|-----|-----|------|--------------------|

| Recovery time<br>from Software<br>Standby mode*1 | Low-speed<br>mode | Crystal<br>resonator<br>connected to<br>main clock<br>oscillator | System clock source is<br>main clock oscillator<br>(1 MHz)* <sup>2</sup> | t <sub>SBYMC</sub> | -   | 2   | 3   | ms   | Figure 2.31        |

|                                                  |                   | External clock<br>input to main<br>clock oscillator              | System clock source is<br>main clock oscillator<br>(1 MHz)* <sup>3</sup> | t <sub>SBYEX</sub> | -   | 28  | 50  | μs   |                    |

|                                                  |                   | System clock sou                                                 | urce is MOCO (1 MHz)                                                     | t <sub>SBYMO</sub> | -   | 25  | 35  | μs   |                    |

Note 1. The division ratio of ICK and PCKx is the minimum division ratio within the allowable frequency range. The recovery time is determined by the system clock source.

Note 2. The Main Clock Oscillator Wait Control Register (MOSCWTCR) is set to 05h.

Note 3. The Main Clock Oscillator Wait Control Register (MOSCWTCR) is set to 00h.

| Table 2.26 | Timing of recovery from low power modes (4) |

|------------|---------------------------------------------|

|            |                                             |

| Parameter                                        |                     |                                                                  |                                                                          |                    | Min | Тур | Max | Unit | Test<br>conditions |

|--------------------------------------------------|---------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|-----|-----|-----|------|--------------------|

| Recovery time<br>from Software<br>Standby mode*1 | Low-voltage<br>mode | Crystal<br>resonator<br>connected to<br>main clock<br>oscillator | System clock source is<br>main clock oscillator<br>(4 MHz)* <sup>2</sup> | t <sub>SBYMC</sub> | -   | 2   | 3   | ms   | Figure 2.31        |

|                                                  |                     | External clock<br>input to main<br>clock oscillator              | System clock source is<br>main clock oscillator<br>(4 MHz)* <sup>3</sup> | t <sub>SBYEX</sub> | -   | 108 | 130 | μs   |                    |

|                                                  |                     | System clock so                                                  | urce is HOCO (4 MHz)                                                     | t <sub>SBYHO</sub> | -   | 108 | 130 | μs   |                    |

Note 1. The division ratio of ICK and PCKx is the minimum division ratio within the allowable frequency range. The recovery time is determined by the system clock source.

Note 2. The Main Clock Oscillator Wait Control Register (MOSCWTCR) is set to 05h.

Note 3. The Main Clock Oscillator Wait Control Register (MOSCWTCR) is set to 00h.

### Table 2.27 Timing of recovery from low power modes (5)

| Parameter                      |                   |                                                          | Symbol             | Min | Тур  | Max | Unit | Test<br>conditions |

|--------------------------------|-------------------|----------------------------------------------------------|--------------------|-----|------|-----|------|--------------------|

| Recovery time<br>from Software | SubOSC-speed mode | System clock source is sub-clock oscillator (32.768 kHz) | t <sub>SBYSC</sub> | -   | 0.85 | 1   | ms   | Figure 2.31        |

| Standby mode* <sup>1</sup>     |                   | System clock source is LOCO<br>(32.768 kHz)              | t <sub>SBYLO</sub> | -   | 0.85 | 1.2 | ms   |                    |

Note 1. The sub-clock oscillator or LOCO itself continues oscillating in Software Standby mode during Subosc-speed mode.

Note 1. The differences among lines in 1-LSB resolution are normalized by this value.

Note 2. The drive capability of the PWM delay generation circuit output port is middle drive.

#### CAC Timing 2.3.8

#### Table 2.32 CAC timing

| Paramete | er                       |                                | Symbol              | Min                                      | Тур | Max | Unit | Test<br>conditions |

|----------|--------------------------|--------------------------------|---------------------|------------------------------------------|-----|-----|------|--------------------|

| CAC      | CACREF input pulse width | $t_{Pcyc} *^1 \le t_{cac} *^2$ | t <sub>CACREF</sub> | $4.5 \times t_{cac} + 3 \times t_{Pcyc}$ | -   | -   | ns   | -                  |

|          |                          | $t_{Pcyc}^{*1} > t_{cac}^{*2}$ |                     | $5 \times t_{cac} + 6.5 \times t_{Pcyc}$ | -   | -   | ns   |                    |

Note 1.  $t_{Pcyc}$ : PCLKB cycle.

Note 2. t<sub>cac</sub>: CAC count clock source cycle.

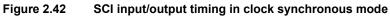

#### 2.3.9 SCI Timing

# Table 2.33SCI timing (1)Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| Param | neter                           |                 |               | Symbol            | Min | Мах | Unit <sup>*1</sup> | Test conditions |

|-------|---------------------------------|-----------------|---------------|-------------------|-----|-----|--------------------|-----------------|

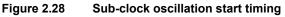

| SCI   | Input clock cycle               | Asynchro        | nous          | t <sub>Scyc</sub> | 4   | -   | t <sub>Pcyc</sub>  | Figure 2.41     |

|       |                                 | Clock syn       | chronous      |                   | 6   | -   |                    |                 |

|       | Input clock pulse wid           | th              |               | t <sub>scкw</sub> | 0.4 | 0.6 | t <sub>Scyc</sub>  |                 |

|       | Input clock rise time           |                 |               | t <sub>SCKr</sub> | -   | 20  | ns                 | -               |

|       | Input clock fall time           |                 |               | t <sub>SCKf</sub> | -   | 20  | ns                 | -               |

|       | Output clock cycle              | Asynchro        | nous          | t <sub>Scyc</sub> | 6   | -   | t <sub>Pcyc</sub>  | -               |

|       |                                 | Clock syn       | chronous      |                   | 4   | -   |                    |                 |

|       | Output clock pulse w            | idth            |               | t <sub>SCKW</sub> | 0.4 | 0.6 | t <sub>Scyc</sub>  | -               |

|       | Output clock rise time          | е               | 1.8V or above | t <sub>SCKr</sub> | -   | 20  | ns                 | -               |

|       |                                 |                 | 1.6V or above |                   | -   | 30  |                    |                 |

|       | Output clock fall time          | :               | 1.8V or above | t <sub>SCKf</sub> | -   | 20  | ns                 | -               |

|       |                                 |                 | 1.6V or above |                   | -   | 30  |                    |                 |

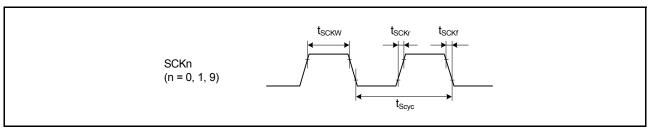

|       | Transmit data delay             | Clock           | 1.8V or above | t <sub>TXD</sub>  | -   | 40  | ns                 | Figure 2.42     |

|       | (master)                        | synchro<br>nous | 1.6V or above |                   | -   | 45  |                    |                 |

|       | Transmit data delay             | Clock           | 2.7V or above |                   | -   | 55  | ns                 | -               |

|       | (slave)                         | synchro<br>nous | 2.4V or above |                   | -   | 60  |                    |                 |

|       |                                 | nous            | 1.8V or above |                   | -   | 100 |                    |                 |

|       |                                 |                 | 1.6V or above |                   | -   | 125 |                    |                 |

|       | Receive data setup              | Clock           | 2.7V or above | t <sub>RXS</sub>  | 45  | -   | ns                 | -               |

|       | time (master)                   | synchro<br>nous | 2.4V or above |                   | 55  | -   |                    |                 |

|       |                                 | nouo            | 1.8V or above |                   | 90  | -   |                    |                 |

|       |                                 |                 | 1.6V or above |                   | 110 | -   |                    |                 |

|       | Receive data setup              | Clock           | 2.7V or above |                   | 40  | -   | ns                 | -               |

|       | time (slave)                    | synchro<br>nous | 1.6V or above |                   | 45  | -   |                    |                 |

|       | Receive data hold time (master) | Clock syn       | chronous      | t <sub>RXH</sub>  | 5   | -   | ns                 |                 |

|       | Receive data hold time (slave)  | Clock syn       | chronous      | t <sub>RXH</sub>  | 40  | -   | ns                 | 1               |

Note 1. t<sub>Pcyc</sub>: PCLKB cycle.

-

Figure 2.41 SCK clock input timing

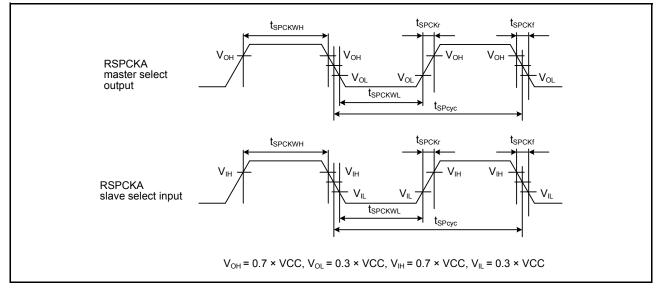

Table 2.36SPI timing (2 of 2)Conditions: Middle drive output is selected in the Port Drive Capability bit in the PmnPFS register.

| neter             |                       |                  |                 | Symbol                               | Min                                             | Max                                               | Unit <sup>*1</sup> | Test condition                       |  |

|-------------------|-----------------------|------------------|-----------------|--------------------------------------|-------------------------------------------------|---------------------------------------------------|--------------------|--------------------------------------|--|

|                   | out setup             | Master           |                 | t <sub>SU</sub>                      | 10                                              | -                                                 | ns                 | Figure 2.50 to                       |  |

| time              |                       | Slave            | 2.4V or above   |                                      | 10                                              | -                                                 |                    | Figure 2.55<br>C = 30 <sub>P</sub> F |  |

|                   |                       |                  | 1.8V or above   |                                      | 15                                              | -                                                 |                    | С – Збрі                             |  |

|                   |                       |                  | 1.6V or above   |                                      | 20                                              | -                                                 |                    |                                      |  |

| Data inp          | out hold time         | Master<br>(RSPCK | is PCLKB/2)     | t <sub>HF</sub>                      | 0                                               | -                                                 | ns                 |                                      |  |

|                   |                       | Master<br>(RSPCK | is not PCLKB/2) | t <sub>H</sub>                       | t <sub>Pcyc</sub>                               | -                                                 | _                  |                                      |  |

|                   |                       | Slave            |                 | t <sub>H</sub>                       | 20                                              | -                                                 |                    |                                      |  |

| SSL set           | up time               | Master<br>Slave  |                 | t <sub>LEAD</sub>                    | – 30 + N x<br>t <sub>Spcyc</sub> * <sup>2</sup> | -                                                 | ns                 |                                      |  |

|                   |                       |                  |                 |                                      | 6 x t <sub>Pcyc</sub>                           | -                                                 | ns                 | 1                                    |  |

| SSL hold time     |                       | Master           |                 | t <sub>LAG</sub>                     | – 30 + N x<br>t <sub>Spcyc</sub> * <sup>3</sup> | -                                                 | ns                 | -                                    |  |

|                   |                       | Slave            |                 |                                      | 6 x t <sub>Pcyc</sub>                           | -                                                 | ns                 | -                                    |  |

| Data out          | Data output delay Mas |                  | 2.7V or above   | t <sub>OD</sub>                      | -                                               | 14                                                | ns                 | Figure 2.50 to                       |  |

| Data odipar dolay |                       |                  | 2.4V or above   |                                      | -                                               | 20                                                | -                  | Figure 2.55                          |  |

|                   |                       |                  | 1.8V or above   |                                      | -                                               | 25                                                | -                  | C = 30 <sub>P</sub> F                |  |

|                   |                       |                  | 1.6V or above   |                                      | -                                               | 30                                                | -                  |                                      |  |

|                   |                       | Slave            | 2.7V or above   | -                                    | -                                               | 50                                                | -                  |                                      |  |

|                   |                       | 01010            | 2.4V or above   | _                                    | -                                               | 60                                                | -                  |                                      |  |