Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 147456                                                                     |

| Number of I/O                  | 97                                                                         |

| Number of Gates                | 1000000                                                                    |

| Voltage - Supply               | 1.14V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 144-LBGA                                                                   |

| Supplier Device Package        | 144-FPBGA (13x13)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p1000l-1fg144i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Flash\*Freeze Technology and Low Power Modes

## Flash\*Freeze Mode

IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 FPGAs offer an ultra-low static power mode to reduce power consumption while preserving the state of the registers, SRAM contents, and I/O states (IGLOO nano and IGLOO PLUS only) without switching off any power supplies, inputs, or input clocks.

Flash\*Freeze technology enables the user to switch to Flash\*Freeze mode within 1 µs, thus simplifying low power design implementation. The Flash\*Freeze (FF) pin (active Low) is a dedicated pin used to enter or exit Flash\*Freeze mode directly; or the pin can be routed internally to the FPGA core and state management IP to allow the user's application to decide if and when it is safe to transition to this mode. If the FF pin is not used, it can be used as a regular I/O.

The FF pin has a built-in glitch filter and optional Schmitt trigger (not available for all devices) to prevent entering or exiting Flash\*Freeze mode accidentally.

There are two ways to use Flash\*Freeze mode. In Flash\*Freeze type 1, entering and exiting the mode is exclusively controlled by the assertion and deassertion of the FF pin. This enables an external processor or human interface device to directly control Flash\*Freeze mode; however, valid data must be preserved using standard procedures (refer to the "Flash\*Freeze Mode Device Behavior" section on page 30). In Flash\*Freeze mode type 2, entering and exiting the mode is controlled by both the FF pin AND user-defined logic. Flash\*Freeze management IP may be used in type 2 mode for clock and data management while entering and exiting Flash\*Freeze mode.

### Flash\*Freeze Type 1: Control by Dedicated Flash\*Freeze Pin

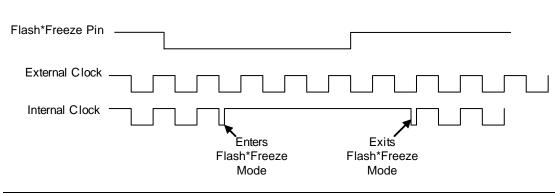

Flash\*Freeze type 1 is intended for systems where either the device will be reset upon exiting Flash\*Freeze mode, or data and clock are managed externally. The device enters Flash\*Freeze mode 1 µs after the dedicated FF pin is asserted (active Low), and returns to normal operation when the FF pin is deasserted (High) (Figure 2-1 on page 25). In this mode, FF pin assertion or deassertion is the only condition that determines entering or exiting Flash\*Freeze mode.

In Libero<sup>®</sup> System-on-Chip (SoC) software v8.2 and before, this mode is implemented by enabling Flash\*Freeze mode (default setting) in the Compile options of the Microsemi Designer software. To simplify usage of Flash\*Freeze mode, beginning with Libero software v8.3, an INBUF\_FF I/O macro was introduced. An INBUF\_FF I/O buffer must be used to identify the Flash\*Freeze input. Microsemi recommends switching to the new implementation.

In Libero software v8.3 and later, the user must manually instantiate the INBUF\_FF macro in the top level of the design to implement Flash\*Freeze Type 1, as shown in Figure 2-1 on page 25.

Flash\*Freeze Technology and Low Power Modes

### Flash\*Freeze Mode Device Behavior

### Entering Flash\*Freeze Mode

- IGLOO, IGLOO nano, IGLOO PLUS, ProASCI3L, and RT ProASIC3 devices are designed and optimized to enter Flash\*Freeze mode only when power supplies are stable. If the device is being powered up while the FF pin is asserted (Flash\*Freeze mode type 1), or while both FF pin and LSICC signal are asserted (Flash\*Freeze mode type 2), the device is expected to enter Flash\*Freeze mode within 5 µs after the I/Os and FPGA core have reached their activation levels.

- If the device is already powered up when the FF pin is asserted, the device will enter Flash\*Freeze mode within 1 µs (type 1). In Flash\*Freeze mode type 2 operation, entering Flash\*Freeze mode is completed within 1 µs after both FF pin and LSICC signal are asserted. Exiting Flash\*Freeze mode is completed within 1 µs after deasserting the FF pin only.

#### PLLs

- If an embedded PLL is used, entering Flash\*Freeze mode will automatically power down the PLL.

- The PLL output clocks will stop toggling within 1 µs after the assertion of the FF pin in type 1, or after both FF pin and LSICC signal are asserted in type 2. At the same time, I/Os will transition into the state specified in Table 2-6 on page 29. The user design must ensure it is safe to enter Flash\*Freeze mode.

#### I/Os and Globals

• While entering Flash\*Freeze mode, inputs, globals, and PLLs will enter their Flash\*Freeze state asynchronously to each other. As a result, clock and data glitches and narrow pulses may be generated while entering Flash\*Freeze mode, as shown in Figure 2-5.

Figure 2-5 • Narrow Clock Pulses During Flash\*Freeze Entrance and Exit

- I/O banks are not all deactivated simultaneously when entering Flash\*Freeze mode. This can cause clocks and inputs to become disabled at different times, resulting in unexpected data being captured.

- Upon entering Flash\*Freeze mode, all inputs and globals become tied High internally (except when an input hold state is used on IGLOO nano or IGLOO PLUS devices). If any of these signals are driven Low or tied Low externally, they will experience a Low to High transition internally when entering Flash\*Freeze mode.

- Upon entering type 2 Flash\*Freeze mode, ensure the LSICC signal (active High) does not deassert. This can prevent the device from entering Flash\*Freeze mode.

- Asynchronous input to output paths may experience output glitches. For example, on a direct into-out path, if the current state is '0' and the input bank turns off first, the input and then the output will transition to '1' before the output enters its Flash\*Freeze state. This can be prevented by using latches in asynchronous in-to-out paths.

- The above situations can cause glitches or invalid data to be clocked into and preserved in the device. Refer to the "Flash\*Freeze Design Guide" section on page 34 for solutions.

ProASIC3L FPGA Fabric User's Guide

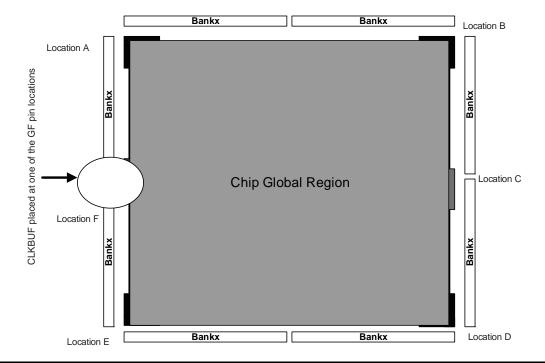

Figure 3-12 • Chip Global Region

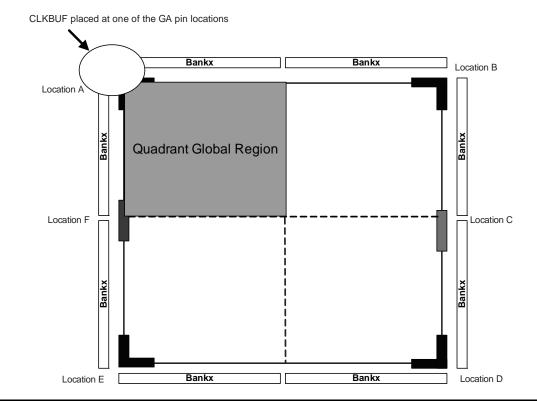

Figure 3-13 • Quadrant Global Region

# List of Changes

| Date                    | Changes                                                                                                                                                                                                                                                                                                                      | Page   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                    | N/A    |

|                         | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                                                                                                                                                                    |        |

|                         | The "Global Architecture" section and "VersaNet Global Network Distribution" section were revised for clarity (SARs 20646, 24779).                                                                                                                                                                                           | 47, 49 |

|                         | The "I/O Banks and Global I/Os" section was moved earlier in the document, renamed to "Chip and Quadrant Global I/Os", and revised for clarity. Figure 3-4 • Global Connections Details, Figure 3-6 • Global Inputs, Table 3-2 • Chip Global Pin Name, and Table 3-3 • Quadrant Global Pin Name are new (SARs 20646, 24779). | 51     |

|                         | The "Clock Aggregation Architecture" section was revised (SARs 20646, 24779).                                                                                                                                                                                                                                                | 57     |

|                         | Figure 3-7 • Chip Global Aggregation was revised (SARs 20646, 24779).                                                                                                                                                                                                                                                        | 59     |

|                         | The "Global Macro and Placement Selections" section is new (SARs 20646, 24779).                                                                                                                                                                                                                                              | 64     |

| v1.4<br>(December 2008) | The "Global Architecture" section was updated to include 10 k devices, and to include information about VersaNet global support for IGLOO nano devices.                                                                                                                                                                      | 47     |

|                         | The Table 3-1 • Flash-Based FPGAs was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                                               | 48     |

|                         | The "VersaNet Global Network Distribution" section was updated to include 10 k devices and to note an exception in global lines for nano devices.                                                                                                                                                                            | 49     |

|                         | Figure 3-2 • Simplified VersaNet Global Network (30 k gates and below) is new.                                                                                                                                                                                                                                               | 50     |

|                         | The "Spine Architecture" section was updated to clarify support for 10 k and nano devices.                                                                                                                                                                                                                                   | 57     |

|                         | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                  | 57     |

|                         | The figure in the CLKBUF_LVDS/LVPECL row of Table 3-8 • Clock Macros was updated to change CLKBIBUF to CLKBUF.                                                                                                                                                                                                               | 62     |

| v1.3<br>(October 2008)  | A third bullet was added to the beginning of the "Global Architecture" section: In Fusion devices, the west CCC also contains a PLL core. In the two larger devices (AFS600 and AFS1500), the west and east CCCs each contain a PLL.                                                                                         | 47     |

|                         | The "Global Resource Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                      | 48     |

|                         | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated to include A3PE600/L in the device column.                                                                                                                                                                                                        | 57     |

|                         | Table note 1 was revised in Table 3-9 • I/O Standards within CLKBUF to include AFS600 and AFS1500.                                                                                                                                                                                                                           | 63     |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 3-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> </ul>                                                                                                                                                            | 48     |

|                         | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                                                                                                               |        |

The following table lists critical changes that were made in each revision of the chapter.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## **Global Buffers with No Programmable Delays**

Access to the global / quadrant global networks can be configured directly from the global I/O buffer, bypassing the CCC functional block (as indicated by the dotted lines in Figure 4-1 on page 77). Internal signals driven by the FPGA core can use the global / quadrant global networks by connecting via the routed clock input of the multiplexer tree.

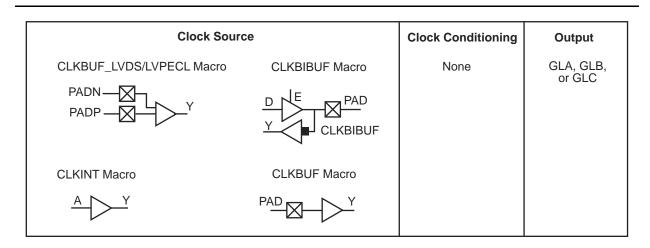

There are many specific CLKBUF macros supporting the wide variety of single-ended I/O inputs (CLKBUF) and differential I/O standards (CLKBUF\_LVDS/LVPECL) in the low power flash families. They are used when connecting global I/Os directly to the global/quadrant networks.

Note: IGLOO nano and ProASIC nano devices do not support differential inputs.

When an internal signal needs to be connected to the global/quadrant network, the CLKINT macro is used to connect the signal to the routed clock input of the network's MUX tree.

To utilize direct connection from global I/Os or from internal signals to the global/quadrant networks, CLKBUF, CLKBUF\_LVPECL/LVDS, and CLKINT macros are used (Figure 4-2).

- The CLKBUF and CLKBUF\_LVPECL/LVDS<sup>1</sup> macros are composite macros that include an I/O macro driving a global buffer, which uses a hardwired connection.

- The CLKBUF, CLKBUF\_LVPECL/LVDS<sup>1</sup> and CLKINT macros are pass-through clock sources and do not use the PLL or provide any programmable delay functionality.

- The CLKINT macro provides a global buffer function driven internally by the FPGA core.

The available CLKBUF macros are described in the *IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide.*

Note: IGLOO nano and ProASIC nano devices do not support differential inputs.

Figure 4-2 • CCC Options: Global Buffers with No Programmable Delay

### **Global Buffer with Programmable Delay**

Clocks requiring clock adjustments can utilize the programmable delay cores before connecting to the global / quadrant global networks. A maximum of 18 CCC global buffers can be instantiated in a device—three per CCC and up to six CCCs per device.

Each CCC functional block contains a programmable delay element for each of the global networks (up to three), and users can utilize these features by using the corresponding macro (Figure 4-3 on page 81).

<sup>1.</sup> B-LVDS and M-LVDS are supported with the LVDS macro.

• Use quadrant global region assignments by finding the clock net associated with the CCC macro under the Nets tab and creating a quadrant global region for the net, as shown in Figure 4-33.

#### Figure 4-33 • Quadrant Clock Assignment for a Global Net

#### External I/O–Driven CCCs

The above-mentioned recommendation for proper layout techniques will ensure the correct assignment. It is possible that, especially with External I/O–Driven CCC macros, placement of the CCC macro in a desired location may not be achieved. For example, assigning an input port of an External I/O–Driven CCC near a particular CCC location does not guarantee global assignments to the desired location. This is because the clock inputs of External I/O–Driven CCCs can be assigned to any I/O location; therefore, it is possible that the CCC connected to the clock input will be routed to a location other than the one closest to the I/O location, depending on resource availability and placement constraints.

#### **Clock Placer**

The clock placer is a placement engine for low power flash devices that places global signals on the chip global and quadrant global networks. Based on the clock assignment constraints for the chip global and quadrant global clocks, it will try to satisfy all constraints, as well as creating quadrant clock regions when necessary. If the clock placer fails to create the quadrant clock regions for the global signals, it will report an error and stop Layout.

The user must ensure that the constraints set to promote clock signals to quadrant global networks are valid.

### **Cascading CCCs**

The CCCs in low power flash devices can be cascaded. Cascading CCCs can help achieve more accurate PLL output frequency results than those achievable with a single CCC. In addition, this technique is useful when the user application requires the output clock of the PLL to be a multiple of the reference clock by an integer greater than the maximum feedback divider value of the PLL (divide by 128) to achieve the desired frequency.

For example, the user application may require a 280 MHz output clock using a 2 MHz input reference clock, as shown in Figure 4-34 on page 126.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

Notes:

2. Flash\*Freeze is supported in all IGLOO devices and the ProASIC3L devices.

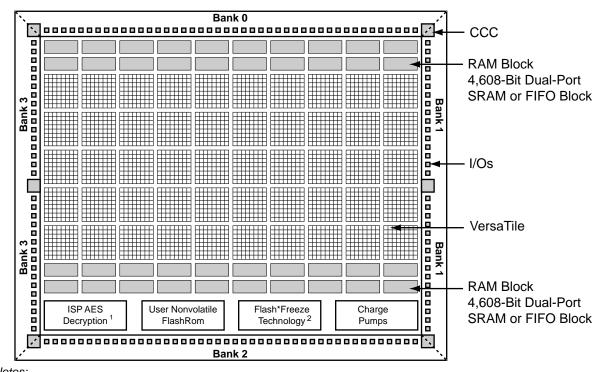

Figure 6-1 • IGLOO and ProASIC3 Device Architecture Overview

<sup>1.</sup> AES decryption not supported in 30 k gate devices and smaller.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

Notes:

- Automotive ProASIC3 devices restrict RAM4K9 to a single port or to dual ports with the same clock 180° out of phase (inverted) between clock pins. In single-port mode, inputs to port B should be tied to ground to prevent errors during compile. This warning applies only to automotive ProASIC3 parts of certain revisions and earlier. Contact Technical Support at soc\_tech@microsemi.com for information on the revision number for a particular lot and date code.

- 2. For FIFO4K18, the same clock 180° out of phase (inverted) between clock pins should be used.

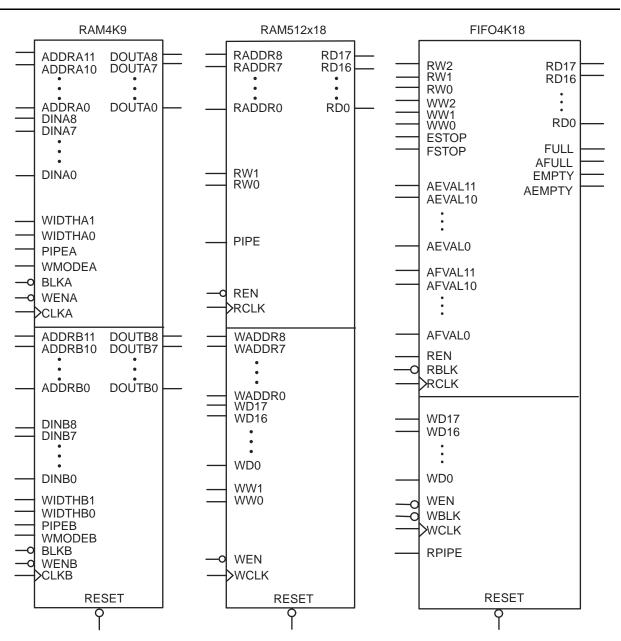

Figure 6-3 • Supported Basic RAM Macros

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, ADDRB should be tied to ground.

|       | ADDRx   |        |  |

|-------|---------|--------|--|

| D×W   | Unused  | Used   |  |

| 4k×1  | None    | [11:0] |  |

| 2k×2  | [11]    | [10:0] |  |

| 1k×4  | [11:10] | [9:0]  |  |

| 512×9 | [11:9]  | [8:0]  |  |

| Table 6-3 • Address Pins Unu | sed/Used for Various S | Supported Bus Widths |

|------------------------------|------------------------|----------------------|

|                              |                        | apportoa Buo matrio  |

Note: The "x" in ADDRx implies A or B.

#### **DINA and DINB**

These are the input data signals, and they are nine bits wide. Not all nine bits are valid in all configurations. When a data width less than nine is specified, unused high-order signals must be grounded (Table 6-4).

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, DINB should be tied to ground.

#### DOUTA and DOUTB

These are the nine-bit output data signals. Not all nine bits are valid in all configurations. As with DINA and DINB, high-order bits may not be used (Table 6-4). The output data on unused pins is undefined.

|       | DINx/DOUTx |       |  |

|-------|------------|-------|--|

| D×W   | Unused     | Used  |  |

| 4k×1  | [8:1]      | [0]   |  |

| 2k×2  | [8:2]      | [1:0] |  |

| 1kx4  | [8:4]      | [3:0] |  |

| 512×9 | None       | [8:0] |  |

Note: The "x" in DINx or DOUTx implies A or B.

#### RAM512X18 Macro

RAM512X18 is the two-port configuration of the same RAM block (Figure 6-5 on page 156). Like the RAM4K9 nomenclature, the RAM512X18 nomenclature refers to both the deepest possible configuration and the widest possible configuration the two-port RAM block can assume. In two-port mode, the RAM block can be configured to either the 512x9 aspect ratio or the 256x18 aspect ratio. RAM512X18 is also fully synchronous and has the following features:

- Dedicated read and write ports

- Active-low read and write enables

- Selectable pipelined or nonpipelined read

- Active-low asynchronous reset

- Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

I/O Structures in IGLOO and ProASIC3 Devices

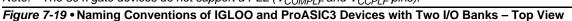

### I/O Banks

Advanced I/Os are divided into multiple technology banks. Each device has two to four banks, and the number of banks is device-dependent as described above. The bank types have different characteristics, such as drive strength, the I/O standards supported, and timing and power differences.

There are three types of banks: Advanced I/O banks, Standard Plus I/O banks, and Standard I/O banks.

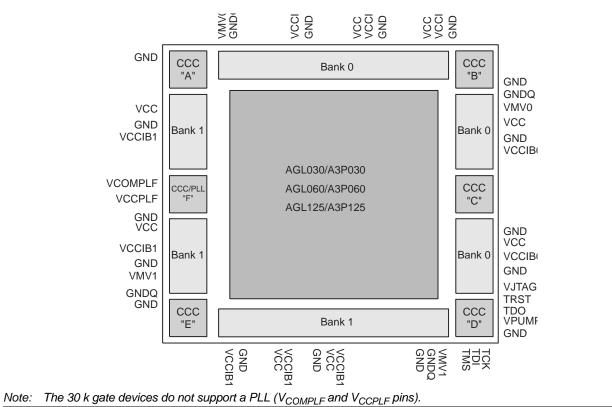

Advanced I/O banks offer single-ended and differential capabilities. These banks are available on the east and west sides of 250K, 400K, 600K, and 1M gate devices.

Standard Plus I/O banks offer LVTTL/LVCMOS and PCI single-ended I/O standards. These banks are available on the north and south sides of 250K, 400K, 600K, and 1M gate devices as well as all sides of 125K and 60K devices.

Standard I/O banks offer LVTTL/LVCMOS single-ended I/O standards. These banks are available on all sides of 30K gate devices.

Table 7-4 shows the I/O bank types, devices and bank locations supported, drive strength, slew rate control, and supported standards.

All inputs and disabled outputs are voltage-tolerant up to 3.3 V.

For more information about I/O and global assignments to I/O banks in a device, refer to the specific pin table for the device in the packaging section of the datasheet and the "User I/O Naming Convention" section on page 206.

|               |                                                           |                                 | I/O Standards Supported |                  |                                       |

|---------------|-----------------------------------------------------------|---------------------------------|-------------------------|------------------|---------------------------------------|

| I/O Bank Type | Device and Bank<br>Location                               | Drive Strength                  | LVTTL/<br>LVCMOS        | PCI/PCI-X        | LVPECL,<br>LVDS,<br>B-LVDS,<br>M-LVDS |

| Standard      | 30 k gate devices (all banks)                             | Refer to Table 7-14 on page 203 | 1                       | Not<br>Supported | Not Supported                         |

| Standard Plus | 60 k and 125 k gate<br>devices (all banks)                | Refer to Table 7-15 on page 203 | 1                       | 1                | Not Supported                         |

|               | North and south banks<br>of 250 k and 1 M gate<br>devices |                                 | ~                       | 1                | Not Supported                         |

| Advanced      | East and west banks of<br>250 k and 1 M gate<br>devices   |                                 | ~                       | ~                | 1                                     |

| Table 7-4 • IGLOO and ProASIC3 Bank Type Definitions and Difference | es |

|---------------------------------------------------------------------|----|

|---------------------------------------------------------------------|----|

ProASIC3L FPGA Fabric User's Guide

Figure 7-20 • Naming Conventions of IGLOO and ProASIC3 Devices with Four I/O Banks – Top View

**Revision 4**

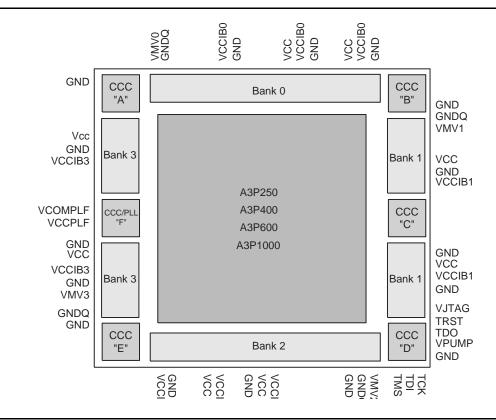

I/O Structures in IGLOOe and ProASIC3E Devices

Figure 8-20 • User I/O Naming Conventions of IGLOOe and ProASIC3E Devices – Top View

### **Board-Level Considerations**

Low power flash devices have robust I/O features that can help in reducing board-level components. The devices offer single-chip solutions, which makes the board layout simpler and more immune to signal integrity issues. Although, in many cases, these devices resolve board-level issues, special attention should always be given to overall signal integrity. This section covers important board-level considerations to facilitate optimum device performance.

### Termination

Proper termination of all signals is essential for good signal quality. Nonterminated signals, especially clock signals, can cause malfunctioning of the device.

For general termination guidelines, refer to the *Board-Level Considerations* application note for Microsemi FPGAs. Also refer to the "Pin Descriptions" chapter of the appropriate datasheet for termination requirements for specific pins.

Low power flash I/Os are equipped with on-chip pull-up/-down resistors. The user can enable these resistors by instantiating them either in the top level of the design (refer to the *IGLOO, Fusion, and ProASIC3 Macro Library Guide* for the available I/O macros with pull-up/-down) or in the I/O Attribute Editor in Designer if generic input or output buffers are instantiated in the top level. Unused I/O pins are configured as inputs with pull-up resistors.

As mentioned earlier, low power flash devices have multiple programmable drive strengths, and the user can eliminate unwanted overshoot and undershoot by adjusting the drive strengths.

I/O Software Control in Low Power Flash Devices

### Instantiating in HDL code

All the supported I/O macros can be instantiated in the top-level HDL code (refer to the *IGLOO*, *ProASIC3*, *SmartFusion*, *and Fusion Macro Library Guide* for a detailed list of all I/O macros). The following is an example:

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3e;

entity TOP is

port(IN2, IN1 : in std_logic; OUT1 : out std_logic);

end TOP;

architecture DEF_ARCH of TOP is

component INBUF_LVCMOS5U

port(PAD : in std_logic := 'U'; Y : out std_logic);

end component;

component INBUF_LVCMOS5

port(PAD : in std_logic := 'U'; Y : out std_logic);

end component;

component OUTBUF_SSTL3_II

port(D : in std_logic := 'U'; PAD : out std_logic);

end component;

Other component ....

signal x, y, z.....other signals : std_logic;

begin

I1 : INBUF_LVCMOS5U

port map(PAD => IN1, Y =>x);

12 : INBUF_LVCMOS5

port map(PAD => IN2, Y => y);

I3 : OUTBUF_SSTL3_II

port map(D => z, PAD => OUT1);

```

other port mapping ...

end DEF\_ARCH;

### Synthesizing the Design

Libero SoC integrates with the Synplify<sup>®</sup> synthesis tool. Other synthesis tools can also be used with Libero SoC. Refer to the *Libero SoC User's Guide* or Libero online help for details on how to set up the Libero tool profile with synthesis tools from other vendors.

During synthesis, the following rules apply:

- Generic macros:

- Users can instantiate generic INBUF, OUTBUF, TRIBUF, and BIBUF macros.

- Synthesis will automatically infer generic I/O macros.

- The default I/O technology for these macros is LVTTL.

- Users will need to use the I/O Attribute Editor in Designer to change the default I/O standard if needed (see Figure 9-6 on page 259).

- Technology-specific I/O macros:

- Technology-specific I/O macros, such as INBUF\_LVCMO25 and OUTBUF\_GTL25, can be instantiated in the design. Synthesis will infer these I/O macros in the netlist.

## **Boundary Scan Support in Low Power Devices**

The information in this document applies to all Fusion, IGLOO, and ProASIC3 devices. For IGLOO, IGLOO PLUS, and ProASIC3L devices, the Flash\*Freeze pin must be deasserted for successful boundary scan operations. Devices cannot enter JTAG mode directly from Flash\*Freeze mode.

## **Boundary Scan Opcodes**

Low power flash devices support all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD, and BYPASS) and the optional IDCODE instruction (Table 16-2).

#### Table 16-2 • Boundary Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| HIGHZ          | 07         |

| USERCODE       | 0E         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | 0F         |

| CLAMP          | 05         |

| BYPASS         | FF         |

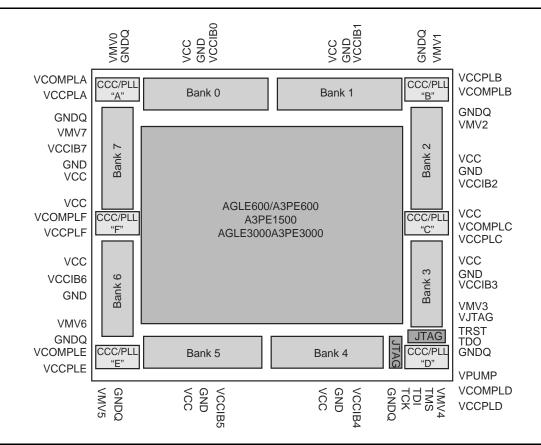

### **Boundary Scan Chain**

The serial pins are used to serially connect all the boundary scan register cells in a device into a boundary scan register chain (Figure 16-2 on page 360), which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic I/O tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Each test section is accessed through the TAP, which has five associated pins: TCK (test clock input), TDI, TDO (test data input and output), TMS (test mode selector), and TRST (test reset input). TMS, TDI, and TRST are equipped with pull-up resistors to ensure proper operation when no input data is supplied to them. These pins are dedicated for boundary scan test usage. Refer to the "JTAG Pins" section in the "Pin Descriptions and Packaging" chapter of the appropriate device datasheet for pull-up/-down recommendations for TCK and TRST pins. Pull-down recommendations are also given in Table 16-3 on page 360

UJTAG Applications in Microsemi's Low Power Flash Devices

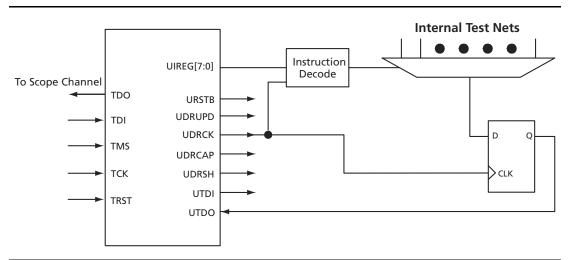

### Silicon Testing and Debugging

In many applications, the design needs to be tested, debugged, and verified on real silicon or in the final embedded application. To debug and test the functionality of designs, users may need to monitor some internal logic (or nets) during device operation. The approach of adding design test pins to monitor the critical internal signals has many disadvantages, such as limiting the number of user I/Os. Furthermore, adding external I/Os for test purposes may require additional or dedicated board area for testing and debugging.

The UJTAG tiles of low power flash devices offer a flexible and cost-effective solution for silicon test and debug applications. In this solution, the signals under test are shifted out to the TDO pin of the TAP Controller. The main advantage is that all the test signals are monitored from the TDO pin; no pins or additional board-level resources are required. Figure 17-6 illustrates this technique. Multiple test nets are brought into an internal MUX architecture. The selection of the MUX is done using the contents of the TAP Controller instruction register, where individual instructions (values from 16 to 127) correspond to different signals under test. The selected test signal can be synchronized with the rising or falling edge of TCK (optional) and sent out to UTDO to drive the TDO output of JTAG.

For flash devices, TDO (the output) is configured as low slew and the highest drive strength available in the technology and/or device. Here are some examples:

- 1. If the device is A3P1000 and VCCI is 3.3 V, TDO will be configured as LVTTL 3.3 V output, 24 mA, low slew.

- If the device is AGLN020 and VCCI is 1.8 V, TDO will be configured as LVCMOS 1.8 V output, 4 mA, low slew.

- 3. If the device is AGLE300 and VCCI is 2.5 V, TDO will be configured as LVCMOS 2.5 V output, 24 mA, low slew.

The test and debug procedure is not limited to the example in Figure 17-5 on page 369. Users can customize the debug and test interface to make it appropriate for their applications. For example, multiple test signals can be registered and then sent out through UTDO, each at a different edge of TCK. In other words, *n* signals are sampled with an  $F_{TCK} / n$  sampling rate. The bandwidth of the information sent out to TDO is always proportional to the frequency of TCK.

Figure 17-6 • UJTAG Usage Example in Test and Debug Applications

UJTAG Applications in Microsemi's Low Power Flash Devices

## Conclusion

Microsemi low power flash FPGAs offer many unique advantages, such as security, nonvolatility, reprogrammability, and low power—all in a single chip. In addition, Fusion, IGLOO, and ProASIC3 devices provide access to the JTAG port from core VersaTiles while the device is in normal operating mode. A wide range of available user-defined JTAG opcodes allows users to implement various types of applications, exploiting this feature of these devices. The connection between the JTAG port and core tiles is implemented through an embedded and hardwired UJTAG tile. A UJTAG tile can be instantiated in designs using the UJTAG library cell. This document presents multiple examples of UJTAG applications, such as dynamic reconfiguration, silicon test and debug, fine-tuning of the design, and RAM initialization. Each of these applications offers many useful advantages.

## **Related Documents**

### **Application Notes**

RAM Initialization and ROM Emulation in ProASIC<sup>PLUS</sup> Devices http://www.microsemi.com/soc/documents/APA\_RAM\_Initd\_AN.pdf

## **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                   | Page |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|

| December 2011           | Information on the drive strength and slew rate of TDO pins was added to the "Silicon Testing and Debugging" section (SAR 31749).         | 370  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides. | N/A  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 17-1 • Flash-Based FPGAs.                                                        | 364  |

| v1.3<br>(October 2008)  | The "UJTAG Support in Flash-Based Devices" section was revised to include new families and make the information more concise.             | 364  |

|                         | The title of Table 17-3 • Configuration Bits of Fusion, IGLOO, and ProASIC3 CCC Blocks was revised to include Fusion.                     | 368  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 17-1 • Flash-<br>Based FPGAs:                                         | 364  |

|                         | <ul><li>ProASIC3L was updated to include 1.5 V.</li><li>The number of PLLs for ProASIC3E was changed from five to six.</li></ul>          |      |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                     | N/A  |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                               | 364  |

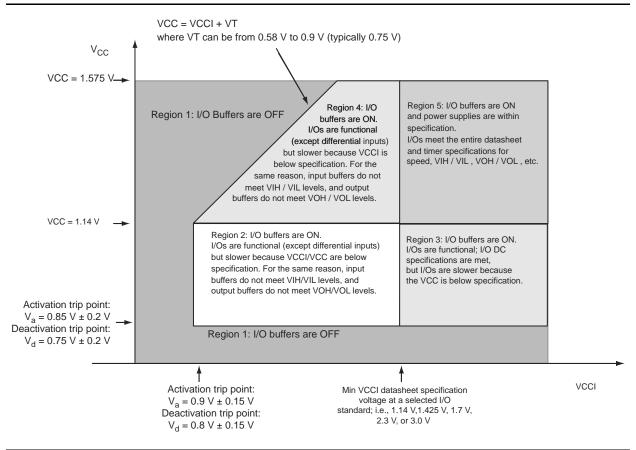

Power-Up/-Down Behavior of Low Power Flash Devices

Figure 18-5 • I/O State as a Function of VCCI and VCC Voltage Levels for IGLOO V2, IGLOO nano V2, IGLOO PLUS V2, and ProASIC3L Devices Running at VCC = 1.2 V ± 0.06 V