Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

∃•XF

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 147456                                                                      |

| Number of I/O                  | 97                                                                          |

| Number of Gates                | 100000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 144-LBGA                                                                    |

| Supplier Device Package        | 144-FPBGA (13x13)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p1000l-1fgg144i |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Flash\*Freeze Technology and Low Power Modes

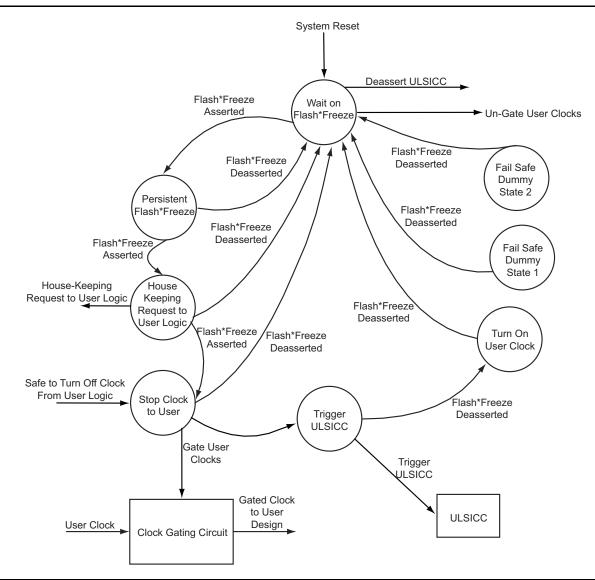

Figure 2-11 • FSM State Diagram

Flash\*Freeze Technology and Low Power Modes

- The INBUF\_FF must be driven by a top-level input port of the design.

- The INBUF\_FF AND the ULSICC macro must be used to enable type 2 Flash\*Freeze mode.

- · For type 2 Flash\*Freeze mode, the INBUF\_FF MUST drive some logic in the design.

- For type 1 Flash\*Freeze mode, the INBUF\_FF may drive some logic in the design, but it may also be left floating.

- Only one INBUF\_FF may be instantiated in a device.

- The FF pin threshold voltages are defined by VCCI and the supported single-ended I/O standard in the corresponding I/O bank.

- The FF pin Schmitt trigger option may be configured in the I/O attribute editor in Microsemi's Designer software. The Schmitt trigger option is only available for IGLOOe, IGLOO nano, IGLOO PLUS, ProASIC3EL, and RT ProASIC3 devices.

- A 2 ns glitch filter resides in the Flash\*Freeze Technology block to filter unwanted glitches on the FF pin.

### ULSICC

The User Low Static ICC (ULSICC) macro allows the FPGA core to access the Flash\*Freeze Technology block so that entering and exiting Flash\*Freeze mode can be controlled by the user's design. The ULSICC macro enables a hard block with an available LSICC input port, as shown in Figure 2-3 on page 27 and Figure 2-10 on page 37. Design rules for the ULSICC macro are as follows:

- The ULSICC macro by itself cannot enable Flash\*Freeze mode. The INBUF\_FF AND the ULSICC macro must both be used to enable type 2 Flash\*Freeze mode.

- The ULSICC controls entering the Flash\*Freeze mode by asserting the LSICC input (logic '1') of the ULSICC macro. The FF pin must also be asserted (logic '0') to enter Flash\*Freeze mode.

- When the LSICC signal is '0', the device cannot enter Flash\*Freeze mode; and if already in Flash\*Freeze mode, it will exit.

- When the ULSICC macro is not instantiated in the user's design, the LSICC port will be tied High.

### Flash\*Freeze Management IP

The Flash\*Freeze management IP can be configured with the Libero (or SmartGen) core generator in a simple, intuitive interface. With the core configuration tool, users can select the number of clocks to be gated, and select whether or not to implement housekeeping. All port names on the Flash\*Freeze management IP block can be renamed by the user.

- The clock gating (filter) blocks include CLKINT buffers for each gated clock output (version 8.3).

- When housekeeping is NOT used, the WAIT\_HOUSEKEEPING signal will be automatically fed back into DONE\_HOUSEKEEPING inside the core, and the ports will not be available at the IP core interface.

- The INBUF\_FF macro is automatically instantiated within the IP core.

- The INBUF\_FF port (default name is "Flash\_Freeze\_N") must be connected to a top-level input port of the design.

- The ULSICC macro is automatically instantiated within the IP core, and the LSICC signal is driven by the FSM.

- Timing analysis can be performed on the clock domain of the source clock (i.e., input to the clock gating filters). For example, if CLKin becomes CLKin\_gated, the timing can be performed on the CLKin domain in SmartTime.

- The gated clocks can be added to the clock list if the user wishes to analyze these clocks specifically. The user can locate the gated clocks by looking for instance names such as those below:

```

Top/ff1/ff_1_wrapper_inst/user_ff_1_wrapper/Primary_Filter_Instance/

Latch_For_Clock_Gating:Q

Top/ff1/ff_1_wrapper_inst/user_ff_1_wrapper/genblk1.genblk2.secondary_filter[0].

seconday_filter_instance/Latch_For_Clock_Gating:Q

Top/ff1/ff_1_wrapper_inst/user_ff_1_wrapper/genblk1.genblk2.secondary_filter[1].

seconday_filter_instance/Latch_For_Clock_Gating:Q

```

ProASIC3L FPGA Fabric User's Guide

| Date                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                          | Page     |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| v2.1<br>(October 2008) | The title changed from "Flash*Freeze Technology and Low Power Modes in IGLOO, IGLOO PLUS, and ProASIC3L Devices" to Actel's Flash*Freeze Technology and Low Power Modes."                                                                                                                                                                                                                                        | N/A      |

|                        | The "Flash Families Support the Flash*Freeze Feature" section was updated.                                                                                                                                                                                                                                                                                                                                       | 22       |

|                        | Significant changes were made to this document to support Libero IDE v8.4 and later functionality. RT ProASIC3 device support information is new. In addition to the other major changes, the following tables and figures were updated or are new:<br>Figure 2-3 • Flash*Freeze Mode Type 2 – Controlled by Flash*Freeze Pin and                                                                                |          |

|                        | Internal Logic (LSICC signal) – updated<br>Figure 2-5 • Narrow Clock Pulses During Flash*Freeze Entrance and Exit – new                                                                                                                                                                                                                                                                                          | 27       |

|                        | Figure 2-10 • Flash*Freeze Management IP Block Diagram – new                                                                                                                                                                                                                                                                                                                                                     | 30       |

|                        | Figure 2-11 • FSM State Diagram – new                                                                                                                                                                                                                                                                                                                                                                            | 37       |

|                        | Table 2-6 • IGLOO nano and IGLOO PLUS Flash*Freeze Mode (type 1 and type 2)—I/O Pad State – updated                                                                                                                                                                                                                                                                                                              | 38<br>29 |

|                        | Please review the entire document carefully.                                                                                                                                                                                                                                                                                                                                                                     | 20       |

| v1.3<br>(June 2008)    | The family description for ProASIC3L in Table 2-1 • Flash-Based FPGAs was updated to include 1.5 V.                                                                                                                                                                                                                                                                                                              | 22       |

| v1.2<br>(March 2008)   | The part number for this document was changed from 51700094-003-1 to 51700094-004-2.                                                                                                                                                                                                                                                                                                                             | N/A      |

|                        | The title of the document was changed to "Flash*Freeze Technology and Low Power Modes in IGLOO, IGLOO PLUS, and ProASIC3L Devices."                                                                                                                                                                                                                                                                              | N/A      |

|                        | The "Flash*Freeze Technology and Low Power Modes" section was updated to remove the parenthetical phrase, "from 25 $\mu$ W," in the second paragraph. The following sentence was added to the third paragraph: "IGLOO PLUS has an additional feature when operating in Flash*Freeze mode, allowing it to retain I/O states as well as SRAM and register states."                                                 | 21       |

|                        | The "Power Conservation Techniques" section was updated to add $V_{JTAG}$ to the parenthetical list of power supplies that should be tied to the ground plane if unused. Additional information was added regarding how the software configures unused I/Os.                                                                                                                                                     | 2-1      |

|                        | Table 2-1 • Flash-Based FPGAs and the accompanying text was updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                                                                                | 22       |

|                        | The "Flash*Freeze Mode" section was revised to include that I/O states are preserved in Flash*Freeze mode for IGLOO PLUS devices. The last sentence in the second paragraph was changed to, "If the FF pin is not used, it can be used as a regular I/O." The following sentence was added for Flash*Freeze mode type 2: "Exiting the mode is controlled by either the FF pin OR the user-defined LSICC signal." | 24       |

|                        | The "Flash*Freeze Type 1: Control by Dedicated Flash*Freeze Pin" section was revised to change instructions for implementing this mode, including instructions for implementation with Libero IDE v8.3.                                                                                                                                                                                                          | 24       |

|                        | Figure 2-1 • Flash*Freeze Mode Type 1 – Controlled by the Flash*Freeze Pin was updated.                                                                                                                                                                                                                                                                                                                          | 25       |

|                        | The "Flash*Freeze Type 2: Control by Dedicated Flash*Freeze Pin and Internal Logic" section was renamed from "Type 2 Software Implementation."                                                                                                                                                                                                                                                                   | 26       |

|                        | The "Type 2 Software Implementation for Libero IDE v8.3" section is new.                                                                                                                                                                                                                                                                                                                                         | 2-6      |

Global Resources in Low Power Flash Devices

# **Global Macro and Placement Selections**

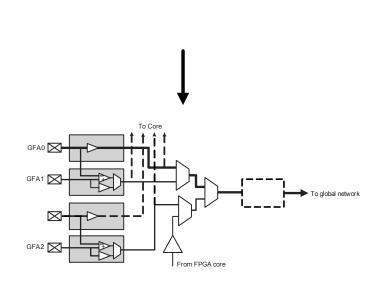

Low power flash devices provide the flexibility of choosing one of the three global input pad locations available to connect to a global / quadrant global network. For 60K gate devices and above, if the single-ended I/O standard is chosen, there is flexibility to choose one of the global input pads (the first, second, and fourth input). Once chosen, the other I/O locations are used as regular I/Os. If the differential I/O standard is chosen, the first and second inputs are considered as paired, and the third input is paired with a regular I/O. The user then has the choice of selecting one of the two sets to be used as the global input source. There is also the option to allow an internal clock signal to feed the global network. A multiplexer tree selects the appropriate global input for routing to the desired location. Note that the global I/O pads do not need to feed the global network; they can also be used as regular I/O pads.

### Hardwired I/O Clock Source

Hardwired I/O refers to global input pins that are hardwired to the multiplexer tree, which directly accesses the global network. These global input pins have designated pin locations and are indicated with the I/O naming convention Gmn (m refers to any one of the positions where the global buffers is available, and n refers to any one of the three global input MUXes and the pin number of the associated global location, m). Choosing this option provides the benefit of directly connecting to the global buffers, which provides less delay. See Figure 3-11 for an example illustration of the connections, shown in red. If a CLKBUF macro is initiated, the clock input can be placed at one of nine dedicated global input pin locations: GmA0, GmA1, GmA2, GmB0, GmB1, GmB2, GmC0, GmC1, or GmC2. Note that the placement of the global will determine whether you are using chip global or quadrant global. For example, if the CLKBIF is placed in one of the GF pin locations, it will use the chip global network; if the CLKBIF is placed in one of the GA pin locations, it will use the chip global network. This is shown in Figure 3-12 on page 65 and Figure 3-13 on page 65.

Figure 3-11 • CLKBUF Macro

# Simple Design Example

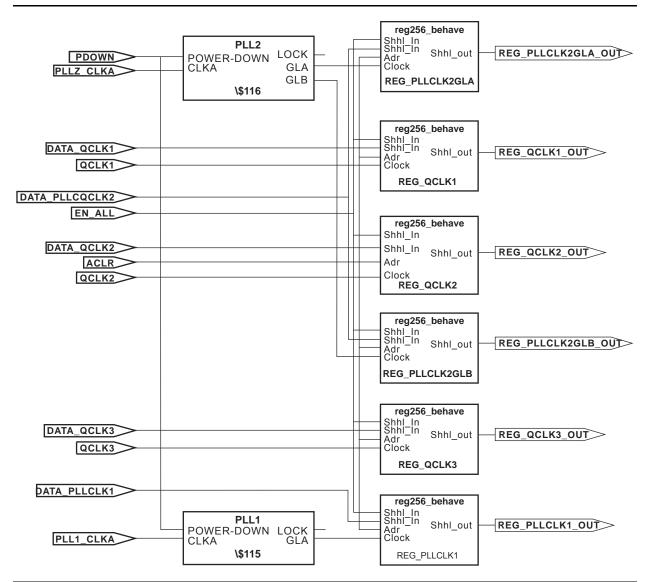

Consider a design consisting of six building blocks (shift registers) and targeted for an A3PE600-PQ208 (Figure 3-16 on page 68). The example design consists of two PLLs (PLL1 has GLA only; PLL2 has both GLA and GLB), a global reset (ACLR), an enable (EN\_ALL), and three external clock domains (QCLK1, QCLK2, and QCLK3) driving the different blocks of the design. Note that the PQ208 package only has two PLLs (which access the chip global network). Because of fanout, the global reset and enable signals need to be assigned to the chip global resources. There is only one free chip global for the remaining global (QCLK1, QCLK2, QCLK3). Place two of these signals on the quadrant global resource. The design example demonstrates manually assignment of QCLK1 and QCLK2 to the quadrant global using the PDC command.

Figure 3-19 • Block Diagram of the Global Management Example Design

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# IGLOOe and ProASIC3E CCC Locations

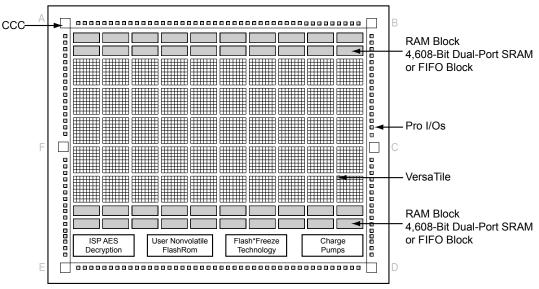

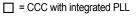

IGLOOe and ProASIC3E devices have six CCCs—one in each of the four corners and one each in the middle of the east and west sides of the device (Figure 4-15).

All six CCCs are integrated with PLLs, except in PQFP-208 package devices. PQFP-208 package devices also have six CCCs, of which two include PLLs and four are simplified CCCs. The CCCs with PLLs are implemented in the middle of the east and west sides of the device (middle right and middle left). The simplified CCCs without PLLs are located in the four corners of the device (Figure 4-16).

Figure 4-16 • CCC Locations in ProASIC3E Family Devices (PQFP-208 package)

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

#### Table 6-2 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

| WIDTHA[1:0] | WIDTHB[1:0] | D×W   |

|-------------|-------------|-------|

| 00          | 00          | 4k×1  |

| 01          | 01          | 2k×2  |

| 10          | 10          | 1k×4  |

| 11          | 11          | 512×9 |

Note: The aspect ratio settings are constant and cannot be changed on the fly.

### BLKA and BLKB

These signals are active-low and will enable the respective ports when asserted. When a BLKx signal is deasserted, that port's outputs hold the previous value.

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, BLKB should be tied to ground.

### WENA and WENB

These signals switch the RAM between read and write modes for the respective ports. A LOW on these signals indicates a write operation, and a HIGH indicates a read.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WENB should be tied to ground.

### **CLKA and CLKB**

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

Note: For Automotive ProASIC3 devices, dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). For use of this macro as a single-port SRAM, the inputs and clock of one port should be tied off (grounded) to prevent errors during design compile.

### PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A LOW on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the corresponding output in the next clock cycle.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, PIPEB should be tied to ground. For use in dual-port mode, the same clock with an inversion between the two clock pins of the macro should be used in the design to prevent errors during compile.

#### WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A LOW on these signals makes the output retain data from the previous read. A HIGH indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WMODEB should be tied to ground.

### RESET

This active-low signal resets the control logic, forces the output hold state registers to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory array.

While the RESET signal is active, read and write operations are disabled. As with any asynchronous reset signal, care must be taken not to assert it too close to the edges of active read and write clocks.

### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 6-3 on page 155).

256×18 FIFO is full, even though a 128×18 FIFO was requested. For this example, the Almost-Full flag can be used instead of the Full flag to signal when the 128th data word is reached.

To accommodate different aspect ratios, the almost-full and almost-empty values are expressed in terms of data bits instead of data words. SmartGen translates the user's input, expressed in data words, into data bits internally. SmartGen allows the user to select the thresholds for the Almost-Empty and Almost-Full flags in terms of either the read data words or the write data words, and makes the appropriate conversions for each flag.

After the empty or full states are reached, the FIFO can be configured so the FIFO counters either stop or continue counting. For timing numbers, refer to the appropriate family datasheet.

### Signal Descriptions for FIFO4K18

The following signals are used to configure the FIFO4K18 memory element:

#### WW and RW

These signals enable the FIFO to be configured in one of the five allowable aspect ratios (Table 6-6).

| WW[2:0]       | RW[2:0]       | D×W      |

|---------------|---------------|----------|

| 000           | 000           | 4k×1     |

| 001           | 001           | 2k×2     |

| 010           | 010           | 1k×4     |

| 011           | 011           | 512×9    |

| 100           | 100           | 256×18   |

| 101, 110, 111 | 101, 110, 111 | Reserved |

#### Table 6-6 • Aspect Ratio Settings for WW[2:0]

### WBLK and RBLK

These signals are active-low and will enable the respective ports when LOW. When the RBLK signal is HIGH, that port's outputs hold the previous value.

### WEN and REN

Read and write enables. WEN is active-low and REN is active-high by default. These signals can be configured as active-high or -low.

#### WCLK and RCLK

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

# Note: For the Automotive ProASIC3 FIFO4K18, for the same clock, 180° out of phase (inverted) between clock pins should be used.

#### RPIPE

This signal is used to specify pipelined read on the output. A LOW on RPIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the output in the next clock cycle.

#### RESET

This active-low signal resets the control logic and forces the output hold state registers to zero when asserted. It does not reset the contents of the memory array (Table 6-7 on page 160).

While the RESET signal is active, read and write operations are disabled. As with any asynchronous RESET signal, care must be taken not to assert it too close to the edges of active read and write clocks.

### WD

This is the input data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. When a data width less than 18 is specified, unused higher-order signals must be grounded (Table 6-7 on page 160).

## **Pipeline Register**

module D\_pipeline (Data, Clock, Q);

input [3:0] Data; input Clock; output [3:0] Q;

reg [3:0] Q;

always @ (posedge Clock) Q <= Data;

endmodule

# 4x4 RAM Block (created by SmartGen Core Generator)

module mem\_block(DI,DO,WADDR,RADDR,WRB,RDB,WCLOCK,RCLOCK);

input [3:0] DI; output [3:0] DO; input [1:0] WADDR, RADDR; input WRB, RDB, WCLOCK, RCLOCK;

wire WEBP, WEAP, VCC, GND;

```

VCC VCC_1_net(.Y(VCC));

GND GND_1_net(.Y(GND));

INV WEBUBBLEB(.A(WRB), .Y(WEBP));

RAM4K9 RAMBLOCK0(.ADDRA11(GND), .ADDRA10(GND), .ADDRA9(GND), .ADDRA8(GND),

.ADDRA7(GND), .ADDRA6(GND), .ADDRA5(GND), .ADDRA4(GND), .ADDRA3(GND), .ADDRA2(GND),

.ADDRA1(RADDR[1]), .ADDRA0(RADDR[0]), .ADDRB11(GND), .ADDRB10(GND), .ADDRB9(GND),

.ADDRB8(GND), .ADDRB7(GND), .ADDRB6(GND), .ADDRB5(GND), .ADDRB4(GND), .ADDRB3(GND),

.ADDRB2(GND), .ADDRB1(WADDR[1]), .ADDRB0(WADDR[0]), .DINA8(GND), .DINA7(GND),

.DINA6(GND), .DINA5(GND), .DINA4(GND), .DINA3(GND), .DINA2(GND), .DINA1(GND),

.DINA0(GND), .DINB8(GND), .DINB7(GND), .DINB6(GND), .DINB5(GND), .DINB4(GND),

.DINB3(DI[3]), .DINB2(DI[2]), .DINB1(DI[1]), .DINB0(DI[0]), .WIDTHA0(GND),

.WIDTHA1(VCC), .WIDTHB0(GND), .WIDTHB1(VCC), .PIPEA(GND), .PIPEB(GND),

.WMODEA(GND), .WMODEB(GND), .BLKA(WEAP), .BLKB(WEBP), .WENA(VCC), .WENB(GND),

.CLKA(RCLOCK), .CLKB(WCLOCK), .RESET(VCC), .DOUTA8(), .DOUTA7(), .DOUTA6(),

.DOUTA5(), .DOUTA4(), .DOUTA3(DO[3]), .DOUTA2(DO[2]), .DOUTA1(DO[1]),

.DOUTA0(DO[0]), .DOUTB8(), .DOUTB7(), .DOUTB6(), .DOUTB5(), .DOUTB4(), .DOUTB3(),

.DOUTB2(), .DOUTB1(), .DOUTB0());

INV WEBUBBLEA(.A(RDB), .Y(WEAP));

```

endmodule

# Conclusion

Fusion, IGLOO, and ProASIC3 devices provide users with extremely flexible SRAM blocks for most design needs, with the ability to choose between an easy-to-use dual-port memory or a wide-word two-port memory. Used with the built-in FIFO controllers, these memory blocks also serve as highly efficient FIFOs that do not consume user gates when implemented. The SmartGen core generator provides a fast and easy way to configure these memory elements for use in designs.

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                                                                                 |     |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| August 2012             | The note connected with Figure 6-3 • Supported Basic RAM Macros, regarding RAM4K9, was revised to explain that it applies only to part numbers of certain revisions and earlier (SAR 29574).                                                                                                            | 152 |  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                               | N/A |  |

| v1.5<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 6-1 • Flash-Based FPGAs.                                                                                                                                                                                                                       | 150 |  |

|                         | IGLOO nano and ProASIC3 nano devices were added to Figure 6-8 • Interfacing TAP Ports and SRAM Blocks.                                                                                                                                                                                                  | 164 |  |

| v1.4<br>(October 2008)  | The "SRAM/FIFO Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                       | 150 |  |

|                         | The "SRAM and FIFO Architecture" section was modified to remove "IGLOO and ProASIC3E" from the description of what the memory block includes, as this statement applies to all memory blocks.                                                                                                           | 151 |  |

|                         | Wording in the "Clocking" section was revised to change "IGLOO and ProASIC3 devices support inversion" to "Low power flash devices support inversion." The reference to IGLOO and ProASIC3 development tools in the last paragraph of the section was changed to refer to development tools in general. | 157 |  |

|                         | The "ESTOP and FSTOP Usage" section was updated to refer to FIFO counters in devices in general rather than only IGLOO and ProASIC3E devices.                                                                                                                                                           | 160 |  |

| v1.3<br>(August 2008)   | The note was removed from Figure 6-7 • RAM Block with Embedded FIFO Controller and placed in the WCLK and RCLK description.                                                                                                                                                                             | 158 |  |

|                         | The "WCLK and RCLK" description was revised.                                                                                                                                                                                                                                                            | 159 |  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 6-1 • Flash-<br>Based FPGAs:                                                                                                                                                                                                        | 150 |  |

|                         | ProASIC3L was updated to include 1.5 V.                                                                                                                                                                                                                                                                 |     |  |

|                         | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                                                                                          |     |  |

| v1.1<br>(March 2008)    | The "Introduction" section was updated to include the IGLOO PLUS family.                                                                                                                                                                                                                                | 147 |  |

|                         | The "Device Architecture" section was updated to state that 15 k gate devices do not support SRAM and FIFO.                                                                                                                                                                                             | 147 |  |

|                         | The first note in Figure 6-1 • IGLOO and ProASIC3 Device Architecture Overview was updated to include mention of 15 k gate devices, and IGLOO PLUS was added to the second note.                                                                                                                        | 149 |  |

I/O Structures in IGLOOe and ProASIC3E Devices

# Low Power Flash Device I/O Support

The low power flash FPGAs listed in Table 8-1 support I/Os and the functions described in this document.

### Table 8-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                              |

|----------|----------------------|--------------------------------------------------------------------------|

| IGLOO    | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |

| ProASIC3 | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                    |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                              |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

# Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E

Table 8-2 shows the voltages and compatible I/O standards for Pro I/Os. I/Os provide programmable slew rates, drive strengths, and weak pull-up and pull-down circuits. All I/O standards, except 3.3 V PCI and 3.3 V PCI-X, are capable of hot-insertion. 3.3 V PCI and 3.3 V PCI-X can be configured to be 5 V– tolerant. See the "5 V Input Tolerance" section on page 232 for possible implementations of 5 V tolerance. Single-ended input buffers support both the Schmitt trigger and programmable delay options on a per–I/O basis.

All I/Os are in a known state during power-up, and any power-up sequence is allowed without current impact. Refer to the "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" section in the datasheet for more information. During power-up, before reaching activation levels, the I/O input and output buffers are disabled while the weak pull-up is enabled. Activation levels are described in the datasheet.

### Table 8-2 • Supported I/O Standards

|                                                                                                              | A3PE600 | AGLE600 | A3PE1500     | A3PE3000/<br>A3PE3000L | AGLE3000 |

|--------------------------------------------------------------------------------------------------------------|---------|---------|--------------|------------------------|----------|

| Single-Ended                                                                                                 |         |         |              |                        |          |

| LVTTL/LVCMOS 3.3 V,<br>LVCMOS 2.5 V / 1.8 V / 1.5 V,<br>LVCMOS 2.5/5.0 V, 3.3 V PCI/PCI-X                    | 1       | 1       | 1            | 1                      | 1        |

| LVCMOS 1.2 V                                                                                                 | _       | 1       | _            | -                      | 1        |

| Differential                                                                                                 |         |         |              |                        |          |

| LVPECL, LVDS, B-LVDS, M-LVDS                                                                                 | 1       | 1       | $\checkmark$ | 1                      | 1        |

| Voltage-Referenced                                                                                           |         |         |              |                        |          |

| GTL+ 2.5 V / 3.3 V, GTL 2.5 V / 3.3 V,<br>HSTL Class I and II, SSTL2 Class I and II,<br>SSTL3 Class I and II | 1       | 1       | <i>✓</i>     | 1                      | 1        |

I/O Structures in IGLOOe and ProASIC3E Devices

#### Notes:

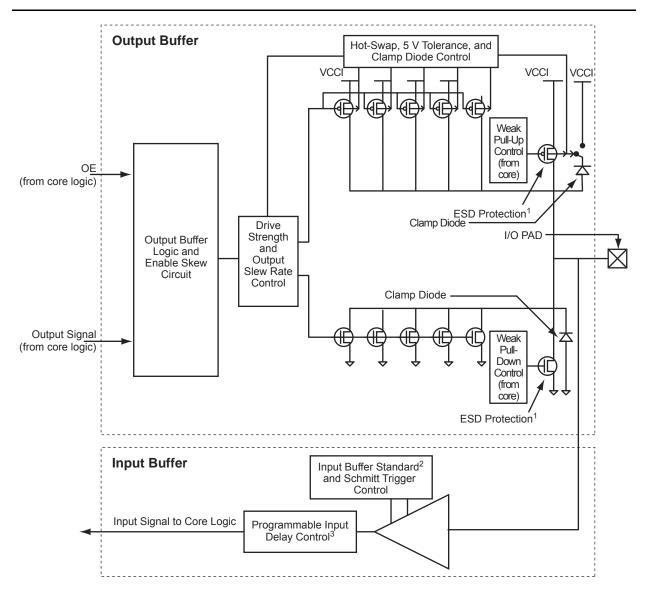

- 1. All NMOS transistors connected to the I/O pad serve as ESD protection.

- 2. See Table 8-2 on page 215 for available I/O standards.

- 3. Programmable input delay is applicable only to ProASIC3E, IGLOOe, ProASIC3EL, and RT ProASIC3 devices.

Figure 8-5 • Simplified I/O Buffer Circuitry

### I/O Registers

Each I/O module contains several input, output, and enable registers. Refer to Figure 8-5 for a simplified representation of the I/O block. The number of input registers is selected by a set of switches (not shown in Figure 8-3 on page 220) between registers to implement single-ended or differential data transmission to and from the FPGA core. The Designer software sets these switches for the user. A common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. Input Register 2 does not have a CLR/PRE pin, as this register is used for DDR implementation. The I/O register combining must satisfy certain rules.

I/O Structures in IGLOOe and ProASIC3E Devices

### Table 8-9 • Hot-Swap Level 1

| Description                              | Cold-swap                                                                                                                                                                                                                                      |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | No                                                                                                                                                                                                                                             |

| Bus State                                | -                                                                                                                                                                                                                                              |

| Card Ground Connection                   | -                                                                                                                                                                                                                                              |

| Device Circuitry Connected to Bus Pins   | -                                                                                                                                                                                                                                              |

| Example Application                      | System and card with Microsemi FPGA chip are<br>powered down, and the card is plugged into the<br>system. Then the power supplies are turned on for<br>the system but not for the FPGA on the card.                                            |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices: Compliant<br>Other IGLOO/ProASIC3 devices: Compliant if bus<br>switch used to isolate FPGA I/Os from rest of<br>system<br>IGLOOe/ProASIC3E devices: Compliant I/Os can,<br>but do not have to be set to hot-insertion mode. |

Table 8-10 • Hot-Swap Level 2

| Description                              | Hot-swap while reset                                                                                                                                                  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | Yes                                                                                                                                                                   |

| Bus State                                | Held in reset state                                                                                                                                                   |

| Card Ground Connection                   | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                                        |

| Device Circuitry Connected to Bus Pins   | -                                                                                                                                                                     |

| Example Application                      | In the PCI hot-plug specification, reset control circuitry isolates the card busses until the card supplies are at their nominal operating levels and stable.         |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices, all IGLOOe/ProASIC3E<br>devices: Compliant I/Os can but do not have to be<br>set to hot-insertion mode.<br>Other IGLOO/ProASIC3 devices: Compliant |

# **Types of Programming for Flash Devices**

The number of devices to be programmed will influence the optimal programming methodology. Those available are listed below:

- In-system programming

- Using a programmer

- Using a microprocessor or microcontroller

- Device programmers

- Single-site programmers

- Multi-site programmers, batch programmers, or gang programmers

- Automated production (robotic) programmers

- Volume programming services

- Microsemi in-house programming

- Programming centers

### In-System Programming

### Device Type Supported: Flash

٠

ISP refers to programming the FPGA after it has been mounted on the system printed circuit board. The FPGA may be preprogrammed and later reprogrammed using ISP.

The advantage of using ISP is the ability to update the FPGA design many times without any changes to the board. This eliminates the requirement of using a socket for the FPGA, saving cost and improving reliability. It also reduces programming hardware expenses, as the ISP methodology is die-/package-independent.

There are two methods of in-system programming: external and internal.

Programmer ISP—Refer to the "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" section on page 327 for more information.

Using an external programmer and a cable, the device can be programmed through a header on the system board. In Microsemi SoC Products Group documentation, this is referred to as external ISP. Microsemi provides FlashPro4, FlashPro3, FlashPro Lite, or Silicon Sculptor 3 to perform external ISP. Note that Silicon Sculptor II and Silicon Sculptor 3 can only provide ISP for ProASIC and ProASIC<sup>PLUS®</sup> families, not for SmartFusion, Fusion, IGLOO, or ProASIC3. Silicon Sculptor II and Silicon Sculptor 3 can be used for programming ProASIC and ProASIC<sup>PLUS®</sup> devices by using an adapter module (part number SMPA-ISP-ACTEL-3).

- Advantages: Allows local control of programming and data files for maximum security. The programming algorithms and hardware are available from Microsemi. The only hardware required on the board is a programming header.

- Limitations: A negligible board space requirement for the programming header and JTAG signal routing

- Microprocessor ISP—Refer to the "Microprocessor Programming of Microsemi's Low Power Flash Devices" chapter of an appropriate FPGA fabric user's guide for more information.

Using a microprocessor and an external or internal memory, you can store the program in memory and use the microprocessor to perform the programming. In Microsemi documentation, this is referred to as internal ISP. Both the code for the programming algorithm and the FPGA programming file must be stored in memory on the board. Programming voltages must also be generated on the board.

- Advantages: The programming code is stored in the system memory. An external programmer is not required during programming.

- Limitations: This is the approach that requires the most design work, since some way of getting and/or storing the data is needed; a system interface to the device must be designed; and the low-level API to the programming firmware must be written and linked into the code provided by Microsemi. While there are benefits to this methodology, serious thought and planning should go into the decision.

2. Choose the appropriate security level setting and enter a FlashLock Pass Key. The default is the **Medium** security level (Figure 12-12). Click **Next**.

If you want to select different options for the FPGA and/or FlashROM, this can be set by clicking **Custom Level**. Refer to the "Advanced Options" section on page 322 for different custom security level options and descriptions of each.

Figure 12-12 • Medium Security Level Selected for Low Power Flash Devices

# **Related Documents**

# **User's Guides**

FlashPro User's Guide

http://www.microsemi.com/soc/documents/flashpro\_ug.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                    | Page |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                  | N/A  |

| v1.5<br>(August 2009)   | The "CoreMP7 Device Security" section was removed from "Security in ARM-<br>Enabled Low Power Flash Devices", since M7-enabled devices are no longer<br>supported.                                                                         | 304  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 12-1 • Flash-Based FPGAs.                                                                                                                                                         | 302  |

| v1.3<br>(October 2008)  | The "Security Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                           | 302  |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 12-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul> | 302  |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                                                                                                                      | N/A  |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                | 302  |

# List of Changes

| Date        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| August 2012 | This chapter will now be published standalone as an application note in addition to being part of the IGLOO/ProASIC3/Fusion FPGA fabric user's guides (SAR 38769).                                                                                                                                                                                                                                                                          | N/A      |

|             | The "ISP Programming Header Information" section was revised to update the description of FP3-10PIN-ADAPTER-KIT in Table 13-3 • Programming Header Ordering Codes, clarifying that it is the adapter kit used for ProASIC <sup>PLUS</sup> based boards, and also for ProASIC3 based boards where a compact programming header is being used (SAR 36779).                                                                                    | 335      |

| June 2011   | The VPUMP programming mode voltage was corrected in Table 13-2 • Power Supplies. The correct value is 3.15 V to 3.45 V (SAR 30668).                                                                                                                                                                                                                                                                                                         | 329      |

|             | The notes associated with Figure 13-5 • Programming Header (top view) and Figure 13-6 • Board Layout and Programming Header Top View were revised to make clear the fact that IGLOO nano V2 devices can be programmed at 1.2 V (SAR 30787).                                                                                                                                                                                                 | 335, 337 |

|             | Figure 13-6 • Board Layout and Programming Header Top View was revised to include resistors tying TCK and TRST to GND. Microsemi recommends tying off TCK and TRST to GND if JTAG is not used (SAR 22921). RT ProASIC3 was added to the list of device families.                                                                                                                                                                            | 337      |

|             | In the "ISP Programming Header Information" section, the kit for adapting ProASIC <sup>PLUS</sup> devices was changed from FP3-10PIN-ADAPTER-KIT to FP3-26PIN-ADAPTER-KIT (SAR 20878).                                                                                                                                                                                                                                                      | 335      |

| July 2010   | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                                                                                                                                   | N/A      |

|             | References to FlashPro4 and FlashPro3X were added to this chapter, giving distinctions between them. References to SmartGen were deleted and replaced with Libero IDE Catalog.                                                                                                                                                                                                                                                              | N/A      |

|             | The "ISP Architecture" section was revised to indicate that V2 devices can be programmed at 1.2 V VCC with FlashPro4.                                                                                                                                                                                                                                                                                                                       | 327      |

|             | SmartFusion was added to Table 13-1 • Flash-Based FPGAs Supporting ISP.                                                                                                                                                                                                                                                                                                                                                                     | 328      |

|             | The "Programming Voltage (VPUMP) and VJTAG" section was revised and 1.2 V was added to Table 13-2 • Power Supplies.                                                                                                                                                                                                                                                                                                                         | 329      |

|             | The "Nonvolatile Memory (NVM) Programming Voltage" section is new.                                                                                                                                                                                                                                                                                                                                                                          | 329      |

|             | Cortex-M3 was added to the "Cortex-M1 and Cortex-M3 Device Security" section.                                                                                                                                                                                                                                                                                                                                                               | 331      |

|             | In the "ISP Programming Header Information" section, the additional header adapter ordering number was changed from FP3-26PIN-ADAPTER to FP3-10PIN-ADAPTER-KIT, which contains 26-pin migration capability.                                                                                                                                                                                                                                 | 335      |

|             | The description of NC was updated in Figure 13-5 • Programming Header (top view), Table 13-4 • Programming Header Pin Numbers and Description and Figure 13-6 • Board Layout and Programming Header Top View.                                                                                                                                                                                                                               | 335, 336 |

|             | The "Symptoms of a Signal Integrity Problem" section was revised to add that customers are expected to troubleshoot board-level signal integrity issues by measuring voltages and taking scope plots. "FlashPro4/3/3X allows TCK to be lowered from 6 MHz down to 1 MHz to allow you to address some signal integrity problems" formerly read, "from 24 MHz down to 1 MHz." "The Scan Chain command expects to see 0x2" was changed to 0x1. | 337      |

The following table lists critical changes that were made in each revision of the chapter.

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

# Microsemi's Flash Families Support Voltage Switching Circuit

The flash FPGAs listed in Table 14-1 support the voltage switching circuit feature and the functions described in this document.

Table 14-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit

| Series   | Family <sup>*</sup>  | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

# IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 14-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 14-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

# Index

# A

AES encryption 305 architecture 147 four I/O banks 13 global 47 IGLOO 12 IGLOO nano 11 IGLOO PLUS 13 IGLOOE 14 ProASIC3 nano 11 ProASIC3E 14 routing 18 spine 57 SRAM and FIFO 151 architecture overview 11 array coordinates 16

# В

boundary scan 357 board-level recommendations 360 chain 359 opcodes 359 brownout voltage 381

# С

CCC 98 board-level considerations 128 cascading 125 **Fusion locations 99** global resources 78 hardwired I/O clock input 124 **IGLOO** locations 97 **IGLOOe** locations 98 locations 96 overview 77 ProASIC3 locations 97 ProASIC3E locations 98 programming 78 software configuration 112 with integrated PLLs 95 without integrated PLLs 95 chip global aggregation 59 CLKDLY macro 81 clock aggregation 60 clock macros 62 clock sources core logic 92 PLL and CLKDLY macros 89 clocks delay adjustment 102 detailed usage information 120 multipliers and dividers 101 phase adjustment 103 physical constraints for quadrant clocks 124 SmartGen settings 121 static timing analysis 123 cold-sparing 382 compiling 261 report 261 contacting Microsemi SoC Products Group customer service 387 email 387 web-based technical support 387 context save and restore 34 customer service 387

# D

DDR architecture 271 design example 282 I/O options 273 input/output support 275 instantiating registers 276 design example 71 design recommendations 62 device architecture 147 DirectC 346 DirectC code 351

## Ε

efficient long-line resources 19 encryption 355

# F

FIFO features 157 initializing 164 memory block consumption 163 software support 170 usage 160 flash switch for programming 9 Flash\*Freeze design flow 39 design guide 34 device behavior 30 I/O state 28 management IP 36 pin locations 31 type 1 24 type 2 26 **ULSICC 40** Flash\*Freeze mode 24