Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells |                                                                            |

| Total RAM Bits                 | 147456                                                                     |

| Number of I/O                  | 97                                                                         |

| Number of Gates                | 1000000                                                                    |

| Voltage - Supply               | 1.14V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 144-LBGA                                                                   |

| Supplier Device Package        | 144-FPBGA (13x13)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p1000l-fgg144i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Flash\*Freeze Technology and Low Power Modes

## Flash\*Freeze Mode Device Behavior

### Entering Flash\*Freeze Mode

- IGLOO, IGLOO nano, IGLOO PLUS, ProASCI3L, and RT ProASIC3 devices are designed and optimized to enter Flash\*Freeze mode only when power supplies are stable. If the device is being powered up while the FF pin is asserted (Flash\*Freeze mode type 1), or while both FF pin and LSICC signal are asserted (Flash\*Freeze mode type 2), the device is expected to enter Flash\*Freeze mode within 5 µs after the I/Os and FPGA core have reached their activation levels.

- If the device is already powered up when the FF pin is asserted, the device will enter Flash\*Freeze mode within 1 µs (type 1). In Flash\*Freeze mode type 2 operation, entering Flash\*Freeze mode is completed within 1 µs after both FF pin and LSICC signal are asserted. Exiting Flash\*Freeze mode is completed within 1 µs after deasserting the FF pin only.

### PLLs

- If an embedded PLL is used, entering Flash\*Freeze mode will automatically power down the PLL.

- The PLL output clocks will stop toggling within 1 µs after the assertion of the FF pin in type 1, or after both FF pin and LSICC signal are asserted in type 2. At the same time, I/Os will transition into the state specified in Table 2-6 on page 29. The user design must ensure it is safe to enter Flash\*Freeze mode.

### I/Os and Globals

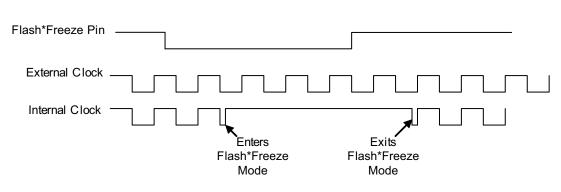

• While entering Flash\*Freeze mode, inputs, globals, and PLLs will enter their Flash\*Freeze state asynchronously to each other. As a result, clock and data glitches and narrow pulses may be generated while entering Flash\*Freeze mode, as shown in Figure 2-5.

Figure 2-5 • Narrow Clock Pulses During Flash\*Freeze Entrance and Exit

- I/O banks are not all deactivated simultaneously when entering Flash\*Freeze mode. This can cause clocks and inputs to become disabled at different times, resulting in unexpected data being captured.

- Upon entering Flash\*Freeze mode, all inputs and globals become tied High internally (except when an input hold state is used on IGLOO nano or IGLOO PLUS devices). If any of these signals are driven Low or tied Low externally, they will experience a Low to High transition internally when entering Flash\*Freeze mode.

- Upon entering type 2 Flash\*Freeze mode, ensure the LSICC signal (active High) does not deassert. This can prevent the device from entering Flash\*Freeze mode.

- Asynchronous input to output paths may experience output glitches. For example, on a direct into-out path, if the current state is '0' and the input bank turns off first, the input and then the output will transition to '1' before the output enters its Flash\*Freeze state. This can be prevented by using latches in asynchronous in-to-out paths.

- The above situations can cause glitches or invalid data to be clocked into and preserved in the device. Refer to the "Flash\*Freeze Design Guide" section on page 34 for solutions.

## Microsemi

Flash\*Freeze Technology and Low Power Modes

| Date                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page          |  |  |  |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|--|--|--|--|

| v1.2<br>(continued)     | Figure 2-3 • Flash*Freeze Mode Type 2 – Controlled by Flash*Freeze Pin and<br>Internal Logic (LSICC signal) was updated.<br>Figure 2-4 • Flash*Freeze Mode Type 2 – Timing Diagram was revised to show                                                                                                                                                                                                                                                                                                                          |               |  |  |  |  |  |  |  |

|                         | Figure 2-4 • Flash*Freeze Mode Type 2 – Timing Diagram was revised to show deasserting LSICC after the device has exited Flash*Freeze mode.                                                                                                                                                                                                                                                                                                                                                                                     |               |  |  |  |  |  |  |  |

|                         | The "IGLOO nano and IGLOO PLUS I/O State in Flash*Freeze Mode" section was added to include information for IGLOO PLUS devices. Table 2-6 • IGLOO nano and IGLOO PLUS Flash*Freeze Mode (type 1 and type 2)—I/O Pad State is new.                                                                                                                                                                                                                                                                                               | 28, 29        |  |  |  |  |  |  |  |

|                         | The "During Flash*Freeze Mode" section was revised to include a new bullet pertaining to output behavior for IGLOO PLUS. The bullet on JTAG operation was revised to provide more detail.                                                                                                                                                                                                                                                                                                                                       | 31            |  |  |  |  |  |  |  |

|                         | Figure 2-6 • Controlling Power-On/-Off State Using Microprocessor and Power FET and Figure 2-7 • Controlling Power-On/-Off State Using Microprocessor and Voltage Regulator were updated to include IGLOO PLUS.                                                                                                                                                                                                                                                                                                                 | 33, 33        |  |  |  |  |  |  |  |

|                         | The first sentence of the "Shutdown Mode" section was updated to list the devices for which it is supported.                                                                                                                                                                                                                                                                                                                                                                                                                    |               |  |  |  |  |  |  |  |

|                         | The first paragraph of the "Power-Up/-Down Behavior" section was revised. The second sentence was changed to, "The I/Os remain tristated until the last voltage supply ( $V_{CC}$ or $V_{CCI}$ ) is powered to its activation level." The word "activation" replaced the word "functional." The sentence, "During power-down, device I/Os become tristated once the first power supply ( $V_{CC}$ or $V_{CCI}$ ) drops below its deactivation voltage level" was revised. The word "deactivation" replaced the word "brownout." |               |  |  |  |  |  |  |  |

|                         | The "Prototyping for IGLOO and ProASIC3L Devices Using ProASIC3" section was revised to state that prototyping in ProASIC3 does not apply for the IGLOO PLUS family.                                                                                                                                                                                                                                                                                                                                                            | 2-21          |  |  |  |  |  |  |  |

|                         | Table 2-8 • Prototyping/Migration Solutions, Table 2-9 • Device Migration—IGLOO Supported Packages in ProASIC3 Devices, and Table 2-10 • Device Migration—<br>ProASIC3L Supported Packages in ProASIC3 Devices were updated with a table note stating that device migration is not supported for IGLOO PLUS devices.                                                                                                                                                                                                            | 2-21,<br>2-23 |  |  |  |  |  |  |  |

|                         | The text following Table 2-10 • Device Migration—ProASIC3L Supported Packages in ProASIC3 Devices was moved to a new section: the "Flash*Freeze Design Guide" section.                                                                                                                                                                                                                                                                                                                                                          | 34            |  |  |  |  |  |  |  |

| v1.1<br>(February 2008) | Table 2-1 • Flash-Based FPGAs was updated to remove the ProASIC3, ProASIC3E, and Automotive ProASIC3 families, which were incorrectly included.                                                                                                                                                                                                                                                                                                                                                                                 | 22            |  |  |  |  |  |  |  |

| v1.0<br>(January 2008)  | Detailed descriptions of low power modes are described in the advanced datasheets. This application note was updated to describe how to use the features in an IGLOO/e application.                                                                                                                                                                                                                                                                                                                                             |               |  |  |  |  |  |  |  |

|                         | Figure 2-1 • Flash*Freeze Mode Type 1 – Controlled by the Flash*Freeze Pin was updated.                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25            |  |  |  |  |  |  |  |

|                         | Figure 2-2 • Flash*Freeze Mode Type 1 – Timing Diagram is new.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25            |  |  |  |  |  |  |  |

|                         | Steps 4 and 5 are new in the "Flash*Freeze Type 2: Control by Dedicated Flash*Freeze Pin and Internal Logic" section.                                                                                                                                                                                                                                                                                                                                                                                                           | 26            |  |  |  |  |  |  |  |

During Layout, Designer will assign two of the signals to quadrant global locations.

### Step 3 (optional)

You can also assign the QCLK1\_c and QCLK2\_c nets to quadrant regions using the following PDC commands:

assign\_local\_clock -net QCLK1\_c -type quadrant UL assign\_local\_clock -net QCLK2\_c -type quadrant LL

### Step 4

Import this PDC with the netlist and run Compile again. You will see the following in the Compile report:

| The fol<br>Fanout | -              | ve been assigned to a global resource:<br>Name                                            |

|-------------------|----------------|-------------------------------------------------------------------------------------------|

| 1536              | INT_NET        | Net : EN_ALL_c<br>Driver: EN_ALL_pad_CLKINT                                               |

| 1536              | SET/RESET_NET  | Source: AUTO PROMOTED<br>Net : ACLR_c<br>Driver: ACLR_pad_CLKINT<br>Source: AUTO PROMOTED |

| 256               | CLK_NET        | Net : QCLK3_c<br>Driver: QCLK3_pad_CLKINT<br>Source: AUTO PROMOTED                        |

| 256               | CLK_NET        | Net : \$1N14<br>Driver: \$1I5/Core                                                        |

| 256               | CLK_NET        | Source: ESSENTIAL<br>Net : \$1N12<br>Driver: \$116/Core<br>Source: ESSENTIAL              |

| 256               | CLK_NET        | Net : \$1N10<br>Driver: \$116/Core<br>Source: ESSENTIAL                                   |

| The fol           | lowing nets ha | ve been assigned to a quadrant clock resource using PDC:                                  |

| Fanout            | 11             |                                                                                           |

|                   | CLK_NET        | Net : QCLK1_c<br>Driver: QCLK1_pad_CLKINT<br>Region: guadrant_UL                          |

| 256               | CLK_NET        | Net : QCLK2_c<br>Driver: QCLK2_pad_CLKINT<br>Region: quadrant_LL                          |

### Step 5

Run Layout.

### **Global Management in PLL Design**

This section describes the legal global network connections to PLLs in the low power flash devices. For detailed information on using PLLs, refer to "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" section on page 77. Microsemi recommends that you use the dedicated global pins to directly drive the reference clock input of the associated PLL for reduced propagation delays and clock distortion. However, low power flash devices offer the flexibility to connect other signals to reference clock inputs. Each PLL is associated with three global networks (Figure 3-5 on page 52). There are some limitations, such as when trying to use the global and PLL at the same time:

- If you use a PLL with only primary output, you can still use the remaining two free global networks.

- If you use three globals associated with a PLL location, you cannot use the PLL on that location.

- If the YB or YC output is used standalone, it will occupy one global, even though this signal does not go to the global network.

## **CCC Support in Microsemi's Flash Devices**

The flash FPGAs listed in Table 4-1 support the CCC feature and the functions described in this document.

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                                    |  |  |  |  |  |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |  |  |  |  |  |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |  |  |  |  |  |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |  |  |  |  |  |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |  |  |  |  |  |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |  |  |  |  |  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |  |  |  |  |  |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |  |  |  |  |  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |  |  |  |  |  |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |  |  |  |  |  |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |  |  |  |  |  |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |  |  |  |  |  |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |  |  |  |  |  |

### Table 4-1 • Flash-Based FPGAs

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

## Microsemi

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## **CCC** Locations

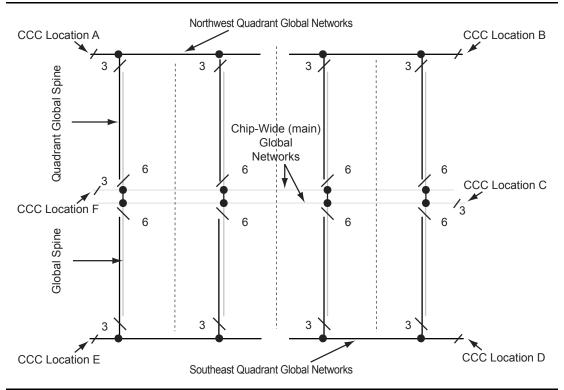

CCCs located in the middle of the east and west sides of the device access the three VersaNet global networks on each side (six total networks), while the four CCCs located in the four corners access three quadrant global networks (twelve total networks). See Figure 4-13.

Figure 4-13 • Global Network Architecture for 60 k Gate Devices and Above

The following explains the locations of the CCCs in IGLOO and ProASIC3 devices:

In Figure 4-15 on page 98 through Figure 4-16 on page 98, CCCs with integrated PLLs are indicated in red, and simplified CCCs are indicated in yellow. There is a letter associated with each location of the CCC, in clockwise order. The upper left corner CCC is named "A," the upper right is named "B," and so on. These names finish up at the middle left with letter "F."

| OADIVHALF /<br>OBDIVHALF /<br>OCDIVHALF | OADIV<4:0> /<br>OBDIV<4:0> /<br>OCDIV<4:0><br>(in decimal) | Divider Factor | Input Clock<br>Frequency | Output Clock<br>Frequency (MHz)   |

|-----------------------------------------|------------------------------------------------------------|----------------|--------------------------|-----------------------------------|

| 1                                       | 2                                                          | 1.5            | 100 MHz RC               | 66.7                              |

|                                         | 4                                                          | 2.5            | Oscillator               | 40.0                              |

|                                         | 6                                                          | 3.5            |                          | 28.6                              |

|                                         | 8                                                          | 4.5            |                          | 22.2                              |

|                                         | 10                                                         | 5.5            |                          | 18.2                              |

|                                         | 12                                                         | 6.5            |                          | 15.4                              |

|                                         | 14                                                         | 7.5            |                          | 13.3                              |

|                                         | 16                                                         | 8.5            |                          | 11.8                              |

|                                         | 18                                                         | 9.5            |                          | 10.5                              |

|                                         | 20                                                         | 10.5           |                          | 9.5                               |

|                                         | 22                                                         | 11.5           |                          | 8.7                               |

|                                         | 24                                                         | 12.5           |                          | 8.0                               |

|                                         | 26                                                         | 13.5           |                          | 7.4                               |

|                                         | 28                                                         | 14.5           | 1                        | 6.9                               |

| 0                                       | 0–31                                                       | 1–32           | Other Clock Sources      | Depends on other divider settings |

### Table 4-18 • Fusion Dynamic CCC Division by Half Configuration

### Table 4-19 • Configuration Bit <76:75> / VCOSEL<2:1> Selection for All Families

|                     |               | VCOSEL[2:1]   |               |               |               |               |               |               |  |  |  |  |  |  |  |

|---------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|--|--|--|--|--|--|--|

|                     | (             | 0             | 0             | )1            | 1             | 0             | 1             | 1             |  |  |  |  |  |  |  |

| Voltage             | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) |  |  |  |  |  |  |  |

| IGLOO and IGLOO     | PLUS          |               |               |               | •             |               |               |               |  |  |  |  |  |  |  |

| 1.2 V ± 5%          | 24            | 35            | 30            | 70            | 60            | 140           | 135           | 160           |  |  |  |  |  |  |  |

| 1.5 V ± 5%          | 24            | 43.75         | 30            | 87.5          | 60            | 175           | 135           | 250           |  |  |  |  |  |  |  |

| ProASIC3L, RT Pro   | ASIC3, and    | Military Pro  | ASIC3/L       | •             | •             |               |               |               |  |  |  |  |  |  |  |

| 1.2 V ± 5%          | 24            | 35            | 30            | 70            | 60            | 140           | 135           | 250           |  |  |  |  |  |  |  |

| 1.5 V ± 5%          | 24            | 43.75         | 30            | 70            | 60            | 175           | 135           | 350           |  |  |  |  |  |  |  |

| ProASIC3 and Fusion |               |               |               |               |               |               |               |               |  |  |  |  |  |  |  |

| 1.5 V ± 5%          | 24            | 43.75         | 33.75         | 87.5          | 67.5          | 175           | 135           | 350           |  |  |  |  |  |  |  |

### Table 4-20 • Configuration Bit <74> / VCOSEL<0> Selection for All Families

| VCOSEL[0] | Description                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0         | Fast PLL lock acquisition time with high tracking jitter. Refer to the corresponding datasheet for specific value and definition. |

| 1         | Slow PLL lock acquisition time with low tracking jitter. Refer to the corresponding datasheet for specific value and definition.  |

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

```

wire VCC, GND;

VCC VCC_1_net(.Y(VCC));

GND GND_1_net(.Y(GND));

CLKDLY Inst1(.CLK(CLK), .GL(GL), .DLYGL0(VCC), .DLYGL1(GND), .DLYGL2(VCC),

.DLYGL3(GND), .DLYGL4(GND));

endmodule

```

## **Detailed Usage Information**

### **Clock Frequency Synthesis**

Deriving clocks of various frequencies from a single reference clock is known as frequency synthesis. The PLL has an input frequency range from 1.5 to 350 MHz. This frequency is automatically divided down to a range between 1.5 MHz and 5.5 MHz by input dividers (not shown in Figure 4-19 on page 100) between PLL macro inputs and PLL phase detector inputs. The VCO output is capable of an output range from 24 to 350 MHz. With dividers before the input to the PLL core and following the VCO outputs, the VCO output frequency can be divided to provide the final frequency range from 0.75 to 350 MHz. Using SmartGen, the dividers are automatically set to achieve the closest possible matches to the specified output frequencies.

Users should be cautious when selecting the desired PLL input and output frequencies and the I/O buffer standard used to connect to the PLL input and output clocks. Depending on the I/O standards used for the PLL input and output clocks, the I/O frequencies have different maximum limits. Refer to the family datasheets for specifications of maximum I/O frequencies for supported I/O standards. Desired PLL input or output frequencies will not be achieved if the selected frequencies are higher than the maximum I/O frequencies allowed by the selected I/O standards. Users should be careful when selecting the I/O standards used for PLL input and output clocks. Performing post-layout simulation can help detect this type of error, which will be identified with pulse width violation errors. Users are strongly encouraged to perform post-layout simulation to ensure the I/O standard used can provide the desired PLL input or output frequencies. Users can also choose to cascade PLLs together to achieve the high frequencies needed for their applications. Details of cascading PLLs are discussed in the "Cascading CCCs" section on page 125.

In SmartGen, the actual generated frequency (under typical operating conditions) will be displayed beside the requested output frequency value. This provides the ability to determine the exact frequency that can be generated by SmartGen, in real time. The log file generated by SmartGen is a useful tool in determining how closely the requested clock frequencies match the user specifications. For example, assume a user specifies 101 MHz as one of the secondary output frequencies. If the best output frequency that could be achieved were 100 MHz, the log file generated by SmartGen would indicate the actual generated frequency.

### **Simulation Verification**

The integration of the generated PLL and CLKDLY modules is similar to any VHDL component or Verilog module instantiation in a larger design; i.e., there is no special requirement that users need to take into account to successfully synthesize their designs.

For simulation purposes, users need to refer to the VITAL or Verilog library that includes the functional description and associated timing parameters. Refer to the Software Tools section of the Microsemi SoC Products Group website to obtain the family simulation libraries. If Designer is installed, these libraries are stored in the following locations:

<Designer\_Installation\_Directory>\lib\vtl\95\proasic3.vhd

<Designer\_Installation\_Directory>Vib\vtl\95\proasic3e.vhd

- <Designer\_Installation\_Directory>\lib\vlog\proasic3.v

- <Designer\_Installation\_Directory>Vib\vlog\proasic3e.v

For Libero users, there is no need to compile the simulation libraries, as they are conveniently precompiled in the Model  $Sim^{\mbox{$^{\circ}$}}$  Microsemi simulation tool.

Use quadrant global region assignments by finding the clock net associated with the CCC macro under the Nets tab and creating a quadrant global region for the net, as shown in Figure 4-33.

### Figure 4-33 • Quadrant Clock Assignment for a Global Net

### External I/O–Driven CCCs

The above-mentioned recommendation for proper layout techniques will ensure the correct assignment. It is possible that, especially with External I/O–Driven CCC macros, placement of the CCC macro in a desired location may not be achieved. For example, assigning an input port of an External I/O–Driven CCC near a particular CCC location does not guarantee global assignments to the desired location. This is because the clock inputs of External I/O–Driven CCCs can be assigned to any I/O location; therefore, it is possible that the CCC connected to the clock input will be routed to a location other than the one closest to the I/O location, depending on resource availability and placement constraints.

### **Clock Placer**

The clock placer is a placement engine for low power flash devices that places global signals on the chip global and quadrant global networks. Based on the clock assignment constraints for the chip global and quadrant global clocks, it will try to satisfy all constraints, as well as creating quadrant clock regions when necessary. If the clock placer fails to create the quadrant clock regions for the global signals, it will report an error and stop Layout.

The user must ensure that the constraints set to promote clock signals to quadrant global networks are valid.

## **Cascading CCCs**

The CCCs in low power flash devices can be cascaded. Cascading CCCs can help achieve more accurate PLL output frequency results than those achievable with a single CCC. In addition, this technique is useful when the user application requires the output clock of the PLL to be a multiple of the reference clock by an integer greater than the maximum feedback divider value of the PLL (divide by 128) to achieve the desired frequency.

For example, the user application may require a 280 MHz output clock using a 2 MHz input reference clock, as shown in Figure 4-34 on page 126.

# 5 – FlashROM in Microsemi's Low Power Flash Devices

## Introduction

The Fusion, IGLOO, and ProASIC3 families of low power flash-based devices have a dedicated nonvolatile FlashROM memory of 1,024 bits, which provides a unique feature in the FPGA market. The FlashROM can be read, modified, and written using the JTAG (or UJTAG) interface. It can be read but not modified from the FPGA core. Only low power flash devices contain on-chip user nonvolatile memory (NVM).

## Architecture of User Nonvolatile FlashROM

Low power flash devices have 1 kbit of user-accessible nonvolatile flash memory on-chip that can be read from the FPGA core fabric. The FlashROM is arranged in eight banks of 128 bits (16 bytes) during programming. The 128 bits in each bank are addressable as 16 bytes during the read-back of the FlashROM from the FPGA core. Figure 5-1 shows the FlashROM logical structure.

The FlashROM can only be programmed via the IEEE 1532 JTAG port. It cannot be programmed directly from the FPGA core. When programming, each of the eight 128-bit banks can be selectively reprogrammed. The FlashROM can only be reprogrammed on a bank boundary. Programming involves an automatic, on-chip bank erase prior to reprogramming the bank. The FlashROM supports synchronous read. The address is latched on the rising edge of the clock, and the new output data is stable after the falling edge of the same clock cycle. For more information, refer to the timing diagrams in the DC and Switching Characteristics chapter of the appropriate datasheet. The FlashROM can be read on byte boundaries. The upper three bits of the FlashROM address from the FPGA core define the bank being accessed. The lower four bits of the FlashROM address from the FPGA core define which of the 16 bytes in the bank is being accessed.

|                                 |   | Byte Number in Bank |    |    |    |    |    |   | 4 LSB of ADDR (READ) |   |   |   |   |   |   |   |   |

|---------------------------------|---|---------------------|----|----|----|----|----|---|----------------------|---|---|---|---|---|---|---|---|

|                                 |   | 15                  | 14 | 13 | 12 | 11 | 10 | 9 | 8                    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| of                              | 7 |                     |    |    |    |    |    |   |                      |   |   |   |   |   |   |   |   |

| 3 MSB of<br>EAD)                | 6 |                     |    |    |    |    |    |   |                      |   |   |   |   |   |   |   |   |

| ΑD                              | 5 |                     |    |    |    |    |    |   |                      |   |   |   |   |   |   |   |   |

| RE C                            | 4 |                     |    |    |    |    |    |   |                      |   |   |   |   |   |   |   |   |

| dr (                            | 3 |                     |    |    |    |    |    |   |                      |   |   |   |   |   |   |   |   |

| NU                              | 2 |                     |    |    |    |    |    |   |                      |   |   |   |   |   |   |   |   |

| Bank Number 3 MS<br>ADDR (READ) | 1 |                     |    |    |    |    |    |   |                      |   |   |   |   |   |   |   |   |

| ä                               | 0 |                     |    |    |    |    |    |   |                      |   |   |   |   |   |   |   |   |

Figure 5-1 • FlashROM Architecture

## Microsemi

FlashROM in Microsemi's Low Power Flash Devices

## **FlashROM Applications**

The SmartGen core generator is used to configure FlashROM content. You can configure each page independently. SmartGen enables you to create and modify regions within a page; these regions can be 1 to 16 bytes long (Figure 5-4).

|          |   |    | Byte Number in Page |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----------|---|----|---------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|          |   | 15 | 14                  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|          | 7 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| <u> </u> | 6 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| he       | 5 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Numb     | 4 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| ۵<br>ا   | 3 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Pag      | 2 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| а.       | 1 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|          | 0 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

### Figure 5-4 • FlashROM Configuration

The FlashROM content can be changed independently of the FPGA core content. It can be easily accessed and programmed via JTAG, depending on the security settings of the device. The SmartGen core generator enables each region to be independently updated (described in the "Programming and Accessing FlashROM" section on page 138). This enables you to change the FlashROM content on a per-part basis while keeping some regions "constant" for all parts. These features allow the FlashROM to be used in diverse system applications. Consider the following possible uses of FlashROM:

- Internet protocol (IP) addressing (wireless or fixed)

- System calibration settings

- Restoring configuration after unpredictable system power-down

- · Device serialization and/or inventory control

- Subscription-based business models (e.g., set-top boxes)

- Secure key storage

- Asset management tracking

- Date stamping

- Version management

FlashROM in Microsemi's Low Power Flash Devices

Figure 5-12 shows the programming file generator, which enables different STAPL file generation methods. When you select **Program FlashROM** and choose the UFC file, the FlashROM Settings window appears, as shown in Figure 5-13. In this window, you can select the FlashROM page you want to program and the data value for the configured regions. This enables you to use a different page for different programming files.

*Figure 5-12* • Programming File Generator

### Figure 5-13 • Setting FlashROM during Programming File Generation

The programming hardware and software can load the FlashROM with the appropriate STAPL file. Programming software handles the single STAPL file that contains multiple FlashROM contents for multiple devices, and programs the FlashROM in sequential order (e.g., for device serialization). This feature is supported in the programming software. After programming with the STAPL file, you can run DEVICE\_INFO to check the FlashROM content.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, ADDRB should be tied to ground.

|       | ADDRx   |        |  |  |  |  |  |  |

|-------|---------|--------|--|--|--|--|--|--|

| D×W   | Unused  | Used   |  |  |  |  |  |  |

| 4k×1  | None    | [11:0] |  |  |  |  |  |  |

| 2k×2  | [11]    | [10:0] |  |  |  |  |  |  |

| 1k×4  | [11:10] | [9:0]  |  |  |  |  |  |  |

| 512×9 | [11:9]  | [8:0]  |  |  |  |  |  |  |

Note: The "x" in ADDRx implies A or B.

#### DINA and DINB

These are the input data signals, and they are nine bits wide. Not all nine bits are valid in all configurations. When a data width less than nine is specified, unused high-order signals must be grounded (Table 6-4).

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, DINB should be tied to ground.

#### DOUTA and DOUTB

These are the nine-bit output data signals. Not all nine bits are valid in all configurations. As with DINA and DINB, high-order bits may not be used (Table 6-4). The output data on unused pins is undefined.

|       | DINx/DOUTx |       |  |

|-------|------------|-------|--|

| D×W   | Unused     | Used  |  |

| 4k×1  | [8:1]      | [0]   |  |

| 2k×2  | [8:2]      | [1:0] |  |

| 1k×4  | [8:4]      | [3:0] |  |

| 512×9 | None       | [8:0] |  |

Note: The "x" in DINx or DOUTx implies A or B.

### RAM512X18 Macro

RAM512X18 is the two-port configuration of the same RAM block (Figure 6-5 on page 156). Like the RAM4K9 nomenclature, the RAM512X18 nomenclature refers to both the deepest possible configuration and the widest possible configuration the two-port RAM block can assume. In two-port mode, the RAM block can be configured to either the 512×9 aspect ratio or the 256×18 aspect ratio. RAM512X18 is also fully synchronous and has the following features:

- Dedicated read and write ports

- · Active-low read and write enables

- · Selectable pipelined or nonpipelined read

- Active-low asynchronous reset

- Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

### SRAM Usage

The following descriptions refer to the usage of both RAM4K9 and RAM512X18.

### Clocking

The dual-port SRAM blocks are only clocked on the rising edge. SmartGen allows falling-edge-triggered clocks by adding inverters to the netlist, hence achieving dual-port SRAM blocks that are clocked on either edge (rising or falling). For dual-port SRAM, each port can be clocked on either edge and by separate clocks by port. Note that for Automotive ProASIC3, the same clock, with an inversion between the two clock pins of the macro, should be used in design to prevent errors during compile.

Low power flash devices support inversion (bubble-pushing) throughout the FPGA architecture, including the clock input to the SRAM modules. Inversions added to the SRAM clock pin on the design schematic or in the HDL code will be automatically accounted for during design compile without incurring additional delay in the clock path.

The two-port SRAM can be clocked on the rising or falling edge of WCLK and RCLK.

If negative-edge RAM and FIFO clocking is selected for memory macros, clock edge inversion management (bubble-pushing) is automatically used within the development tools, without performance penalty.

### Modes of Operation

There are two read modes and one write mode:

- Read Nonpipelined (synchronous—1 clock edge): In the standard read mode, new data is driven onto the RD bus in the same clock cycle following RA and REN valid. The read address is registered on the read port clock active edge, and data appears at RD after the RAM access time. Setting PIPE to OFF enables this mode.

- Read Pipelined (synchronous—2 clock edges): The pipelined mode incurs an additional clock delay from address to data but enables operation at a much higher frequency. The read address is registered on the read port active clock edge, and the read data is registered and appears at RD after the second read clock edge. Setting PIPE to ON enables this mode.

- Write (synchronous—1 clock edge): On the write clock active edge, the write data is written into the SRAM at the write address when WEN is HIGH. The setup times of the write address, write enables, and write data are minimal with respect to the write clock.

### **RAM** Initialization

Each SRAM block can be individually initialized on power-up by means of the JTAG port using the UJTAG mechanism. The shift register for a target block can be selected and loaded with the proper bit configuration to enable serial loading. The 4,608 bits of data can be loaded in a single operation.

### **FIFO Features**

The FIFO4KX18 macro is created by merging the RAM block with dedicated FIFO logic (Figure 6-6 on page 158). Since the FIFO logic can only be used in conjunction with the memory block, there is no separate FIFO controller macro. As with the RAM blocks, the FIFO4KX18 nomenclature does not refer to a possible aspect ratio, but rather to the deepest possible data depth and the widest possible data width. FIFO4KX18 can be configured into the following aspect ratios: 4,096×1, 2,048×2, 1,024×4, 512×9, and 256×18. In addition to being fully synchronous, the FIFO4KX18 also has the following features:

- Four FIFO flags: Empty, Full, Almost-Empty, and Almost-Full

- Empty flag is synchronized to the read clock

- Full flag is synchronized to the write clock

- Both Almost-Empty and Almost-Full flags have programmable thresholds

- · Active-low asynchronous reset

- Active-low block enable

- Active-low write enable

- Active-high read enable

- Ability to configure the FIFO to either stop counting after the empty or full states are reached or to allow the FIFO counters to continue

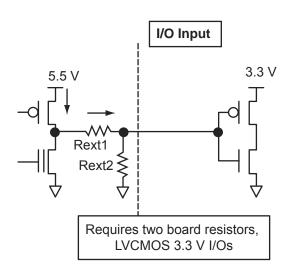

### Solution 1

### Figure 8-10 • Solution 1

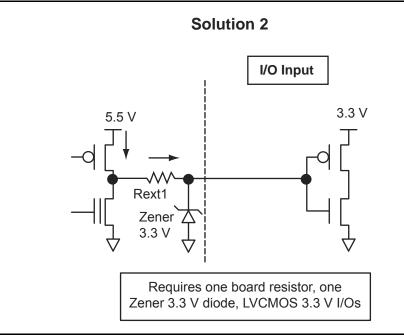

### Solution 2

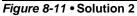

The board-level design must ensure that the reflected waveform at the pad does not exceed the voltage overshoot/undershoot limits provided in the datasheet. This is a requirement to ensure long-term reliability.

This scheme will also work for a 3.3 V PCI/PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the external resistors and Zener, as shown in Figure 8-11. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

### Solution 4

The board-level design must ensure that the reflected waveform at the pad does not exceed the voltage overshoot/undershoot limits provided in the datasheet. This is a requirement to ensure long-term reliability.

### Figure 8-13 • Solution 4

| Solution | Board Components                                                                                                                                                                 | Speed                    | Current Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Two resistors                                                                                                                                                                    | Low to High <sup>1</sup> | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2        | Resistor and Zener 3.3 V                                                                                                                                                         | Medium                   | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3        | Bus switch                                                                                                                                                                       | High                     | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4        | Minimum resistor value <sup>2,3,4,5</sup><br>R = 47 $\Omega$ at T <sub>J</sub> = 70°C<br>R = 150 $\Omega$ at T <sub>J</sub> = 85°C<br>R = 420 $\Omega$ at T <sub>J</sub> = 100°C | Medium                   | Maximum diode current at 100% duty cycle, signal<br>constantly at 1<br>52.7 mA at $T_J = 70^{\circ}$ C / 10-year lifetime<br>16.5 mA at $T_J = 85^{\circ}$ C / 10-year lifetime<br>5.9 mA at $T_J = 100^{\circ}$ C / 10-year lifetime<br>For duty cycles other than 100%, the currents can be<br>increased by a factor of 1 / (duty cycle).<br>Example: 20% duty cycle at 70°C<br>Maximum current = (1 / 0.2) × 52.7 mA = 5 × 52.7 mA =<br>263.5 mA |

Notes:

- 1. Speed and current consumption increase as the board resistance values decrease.

- 2. Resistor values ensure I/O diode long-term reliability.

- 3. At 70°C, customers could still use 420  $\Omega$  on every I/O.

- 4. At 85°C, a 5 V solution on every other I/O is permitted, since the resistance is lower (150  $\Omega$ ) and the current is higher. Also, the designer can still use 420  $\Omega$  and use the solution on every I/O.

- 5. At 100°C, the 5 V solution on every I/O is permitted, since 420  $\Omega$  are used to limit the current to 5.9 mA.

I/O Software Control in Low Power Flash Devices

those banks, the user does not need to assign the same VCCI voltage to another bank. The user needs to assign the other three VCCI voltages to three more banks.

## Assigning Technologies and VREF to I/O Banks

Low power flash devices offer a wide variety of I/O standards, including voltage-referenced standards. Before proceeding to Layout, each bank must have the required VCCI voltage assigned for the corresponding I/O technologies used for that bank. The voltage-referenced standards require the use of a reference voltage (VREF). This assignment can be done manually or automatically. The following sections describe this in detail.

## Manually Assigning Technologies to I/O Banks

The user can import the PDC at this point and resolve this requirement. The PDC command is

set\_iobank [bank name] -vcci [vcci value]

Another method is to use the I/O Bank Settings dialog box (**MVN** > **Edit** > **I/O Bank Settings**) to set up the  $V_{CCI}$  voltage for the bank (Figure 9-12).

Figure 9-12 • Setting VCCI for a Bank

If the assignment is not successful, an error message appears in the Output window.

To undo the I/O bank assignments, choose **Undo** from the **Edit** menu. Undo removes the I/O technologies assigned by the IOBA. It does not remove the I/O technologies previously assigned.

To redo the changes undone by the Undo command, choose Redo from the Edit menu.

To clear I/O bank assignments made before using the Undo command, manually unassign or reassign I/O technologies to banks. To do so, choose **I/O Bank Settings** from the **Edit** menu to display the I/O Bank Settings dialog box.

## Conclusion

Fusion, IGLOO, and ProASIC3 support for multiple I/O standards minimizes board-level components and makes possible a wide variety of applications. The Microsemi Designer software, integrated with Libero SoC, presents a clear visual display of I/O assignments, allowing users to verify I/O and board-level design requirements before programming the device. The device I/O features and functionalities ensure board designers can produce low-cost and low power FPGA applications fulfilling the complexities of contemporary design needs.

## **Related Documents**

### **User's Guides**

Libero SoC User's Guide http://www.microsemi.com/soc/documents/libero\_ug.pdf IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide http://www.microsemi.com/soc/documents/pa3\_libguide\_ug.pdf SmartGen Core Reference Guide http://www.microsemi.com/soc/documents/genguide ug.pdf

Programming Flash Devices

# List of Changes

| Date      | Changes                                                                                                                                                                                                                                                                                                         | Page |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010 | FlashPro4 is a replacement for FlashPro3 and has been added to this chapter.<br>FlashPro is no longer available.                                                                                                                                                                                                | N/A  |

|           | The chapter was updated to include SmartFusion devices.                                                                                                                                                                                                                                                         | N/A  |

|           | The following were deleted:                                                                                                                                                                                                                                                                                     | N/A  |

|           | "Live at Power-Up (LAPU) or Boot PROM" section                                                                                                                                                                                                                                                                  |      |

|           | "Design Security" section                                                                                                                                                                                                                                                                                       |      |

|           | Table 14-2 • Programming Features for Actel Devices and much of the text in the "Programming Features for Microsemi Devices" section                                                                                                                                                                            |      |

|           | "Programming Flash FPGAs" section                                                                                                                                                                                                                                                                               |      |

|           | "Return Material Authorization (RMA) Policies" section                                                                                                                                                                                                                                                          |      |

|           | The "Device Programmers" section was revised.                                                                                                                                                                                                                                                                   | 291  |

|           | The Independent Programming Centers information was removed from the "Volume Programming Services" section.                                                                                                                                                                                                     | 292  |

|           | Table 11-3 • Programming Solutions was revised to add FlashPro4 and note that FlashPro is discontinued. A note was added for FlashPro Lite regarding power supply requirements.                                                                                                                                 | 293  |

|           | Most items were removed from Table 11-4 • Programming Ordering Codes, including FlashPro3 and FlashPro.                                                                                                                                                                                                         | 294  |

|           | The "Programmer Device Support" section was deleted and replaced with a reference to the Microsemi SoC Products Group website for the latest information.                                                                                                                                                       | 294  |

|           | The "Certified Programming Solutions" section was revised to add FlashPro4 and remove Silicon Sculptor I and Silicon Sculptor 6X. Reference to <i>Programming and Functional Failure Guidelines</i> was added.                                                                                                  | 294  |

|           | The file type *.pdb was added to the "Use the Latest Version of the Designer Software to Generate Your Programming File (recommended)" section.                                                                                                                                                                 | 295  |

|           | Instructions on cleaning and careful insertion were added to the "Perform Routine<br>Hardware Self-Diagnostic Test" section. Information was added regarding testing<br>Silicon Sculptor programmers with an adapter module installed before every<br>programming session verifying their calibration annually. | 295  |

|           | The "Signal Integrity While Using ISP" section is new.                                                                                                                                                                                                                                                          | 296  |

|           | The "Programming Failure Allowances" section was revised.                                                                                                                                                                                                                                                       | 296  |

The following table lists critical changes that were made in each revision of the chapter.

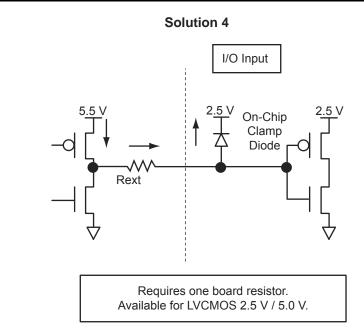

## STAPL vs. DirectC

Programming the low power flash devices is performed using DirectC or the STAPL player. Both tools use the STAPL file as an input. DirectC is a compiled language, whereas STAPL is an interpreted language. Microprocessors will be able to load the FPGA using DirectC much more quickly than STAPL. This speed advantage becomes more apparent when lower clock speeds of 8- or 16-bit microprocessors are used. DirectC also requires less memory than STAPL, since the programming algorithm is directly implemented. STAPL does have one advantage over DirectC—the ability to upgrade. When a new programming algorithm is required, the STAPL user simply needs to regenerate a STAPL file using the latest version of the Designer software and download it to the system. The DirectC user must download the latest version of DirectC from Microsemi, compile everything, and download the result into the system (Figure 15-4).

Figure 15-4 • STAPL vs. DirectC

Microsemi

UJTAG Applications in Microsemi's Low Power Flash Devices

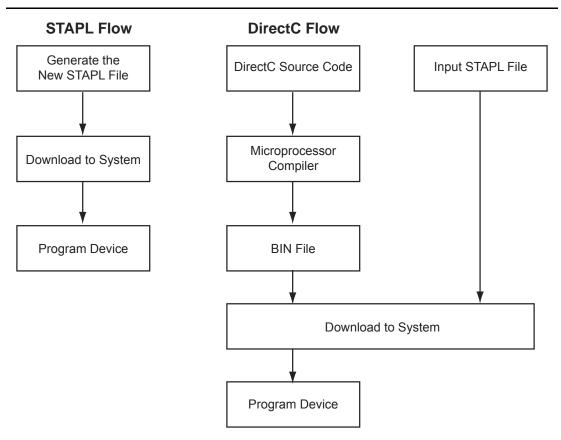

Figure 17-3 • Connectivity Method of UJTAG Macro

## **UJTAG Operation**

There are a few basic functions of the UJTAG macro that users must understand before designing with it. The most important fundamental concept of the UJTAG design is its connection with the TAP Controller state machine.

## **TAP Controller State Machine**

The 16 states of the TAP Controller state machine are shown in Figure 17-4 on page 367. The 1s and 0s, shown adjacent to the state transitions, represent the TMS values that must be present at the time of a rising TCK edge for a state transition to occur. In the states that include the letters "IR," the instruction register operates; in the states that contain the letters "DR," the test data register operates. The TAP Controller receives two control inputs, TMS and TCK, and generates control and clock signals for the rest of the test logic.

On power-up (or the assertion of TRST), the TAP Controller enters the Test-Logic-Reset state. To reset the controller from any other state, TMS must be held HIGH for at least five TCK cycles. After reset, the TAP state changes at the rising edge of TCK, based on the value of TMS.