Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Active                                                                   |

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 110592                                                                   |

| Number of I/O                  | 97                                                                       |

| Number of Gates                | 600000                                                                   |

| Voltage - Supply               | 1.14V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 144-LBGA                                                                 |

| Supplier Device Package        | 144-FPBGA (13x13)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p600l-1fg144 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Flash\*Freeze Technology and Low Power Modes

# Flash\*Freeze Mode

IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 FPGAs offer an ultra-low static power mode to reduce power consumption while preserving the state of the registers, SRAM contents, and I/O states (IGLOO nano and IGLOO PLUS only) without switching off any power supplies, inputs, or input clocks.

Flash\*Freeze technology enables the user to switch to Flash\*Freeze mode within 1 µs, thus simplifying low power design implementation. The Flash\*Freeze (FF) pin (active Low) is a dedicated pin used to enter or exit Flash\*Freeze mode directly; or the pin can be routed internally to the FPGA core and state management IP to allow the user's application to decide if and when it is safe to transition to this mode. If the FF pin is not used, it can be used as a regular I/O.

The FF pin has a built-in glitch filter and optional Schmitt trigger (not available for all devices) to prevent entering or exiting Flash\*Freeze mode accidentally.

There are two ways to use Flash\*Freeze mode. In Flash\*Freeze type 1, entering and exiting the mode is exclusively controlled by the assertion and deassertion of the FF pin. This enables an external processor or human interface device to directly control Flash\*Freeze mode; however, valid data must be preserved using standard procedures (refer to the "Flash\*Freeze Mode Device Behavior" section on page 30). In Flash\*Freeze mode type 2, entering and exiting the mode is controlled by both the FF pin AND user-defined logic. Flash\*Freeze management IP may be used in type 2 mode for clock and data management while entering and exiting Flash\*Freeze mode.

### Flash\*Freeze Type 1: Control by Dedicated Flash\*Freeze Pin

Flash\*Freeze type 1 is intended for systems where either the device will be reset upon exiting Flash\*Freeze mode, or data and clock are managed externally. The device enters Flash\*Freeze mode 1 µs after the dedicated FF pin is asserted (active Low), and returns to normal operation when the FF pin is deasserted (High) (Figure 2-1 on page 25). In this mode, FF pin assertion or deassertion is the only condition that determines entering or exiting Flash\*Freeze mode.

In Libero<sup>®</sup> System-on-Chip (SoC) software v8.2 and before, this mode is implemented by enabling Flash\*Freeze mode (default setting) in the Compile options of the Microsemi Designer software. To simplify usage of Flash\*Freeze mode, beginning with Libero software v8.3, an INBUF\_FF I/O macro was introduced. An INBUF\_FF I/O buffer must be used to identify the Flash\*Freeze input. Microsemi recommends switching to the new implementation.

In Libero software v8.3 and later, the user must manually instantiate the INBUF\_FF macro in the top level of the design to implement Flash\*Freeze Type 1, as shown in Figure 2-1 on page 25.

Flash\*Freeze Technology and Low Power Modes

Table 2-4 summarizes the Flash\*Freeze mode implementations.

| Flash*Freeze<br>Mode Type | Description                                   | Flash*Freeze<br>Pin State | Instantiate<br>ULSICC Macro | LSICC<br>Signal | Operating Mode    |

|---------------------------|-----------------------------------------------|---------------------------|-----------------------------|-----------------|-------------------|

|                           | Flash*Freeze mode is                          |                           | No                          | N/A             | Normal operation  |

|                           | controlled only by the<br>FF pin.             | Asserted                  | No                          | N/A             | Flash*Freeze mode |

| 2                         | Flash*Freeze mode is                          |                           | Yes                         | Deasserted      | Normal operation  |

|                           | controlled by the FF<br>pin and LSICC signal. | Deasserted                | Yes                         | "Don't care"    | Normal operation  |

|                           |                                               |                           | Yes                         | Asserted        | Flash*Freeze mode |

| Table 2-4 • | Flash*Freeze | Mode Usage |

|-------------|--------------|------------|

|-------------|--------------|------------|

Note: Refer to Table 2-3 on page 26 for Flash\*Freeze pin and LSICC signal assertion and deassertion values.

# IGLOO, ProASIC3L, and RT ProASIC3 I/O State in Flash\*Freeze Mode

In IGLOO and ProASIC3L devices, when the device enters Flash\*Freeze mode, I/Os become tristated. If the weak pull-up or pull-down feature is used, the I/Os will maintain the configured weak pull-up or pull-down status. This feature enables the design to set the I/O state to a certain level that is determined by the pull-up/-down configuration.

Table 2-5 shows the I/O pad state based on the configuration and buffer type.

Note that configuring weak pull-up or pull-down for the FF pin is not allowed. The FF pin can be configured as a Schmitt trigger input in IGLOOe, IGLOO nano, IGLOO PLUS, and ProASIC3EL devices.

#### Table 2-5 • IGLOO, ProASIC3L, and RT ProASIC3 Flash\*Freeze Mode (type 1 and type 2)—I/O Pad State

| Buffer Type              |                           | I/O Pad Weak<br>Pull-Up/-Down | I/O Pad State in Flash*Freeze Mode |  |

|--------------------------|---------------------------|-------------------------------|------------------------------------|--|

| Input/Global             |                           | Enabled                       | Weak pull-up/pull-down*            |  |

|                          |                           | Disabled                      | Tristate*                          |  |

| Output                   |                           | Enabled                       | Weak pull-up/pull-down             |  |

|                          |                           | Disabled                      | Tristate                           |  |

| Bidirectional / Tristate | E = 0<br>(input/tristate) | Enabled                       | Weak pull-up/pull-down*            |  |

| Buffer                   |                           | Disabled                      | Tristate*                          |  |

|                          | E = 1 (output)            | Enabled                       | Weak pull-up/pull-down             |  |

|                          |                           | Disabled                      | Tristate                           |  |

\* Internal core logic driven by this input/global buffer will be tied High as long as the device is in Flash\*Freeze mode.

### IGLOO nano and IGLOO PLUS I/O State in Flash\*Freeze Mode

In IGLOO nano and IGLOO PLUS devices, users have multiple options in how to configure I/Os during Flash\*Freeze mode:

- 1. Hold the previous state

- 2. Set I/O pad to weak pull-up or pull-down

- 3. Tristate I/O pads

The I/O configuration must be configured by the user in the I/O Attribute Editor or in a PDC constraint file, and can be done on a pin-by-pin basis. The output hold feature will hold the output in the last registered state, using the I/O pad weak pull-up or pull-down resistor when the FF pin is asserted. When inputs are configured with the hold feature enabled, the FPGA core side of the input will hold the last valid state of the input pad before the device entered Flash\*Freeze mode. The input pad can be driven to any value, configured as tristate, or configured with the weak pull-up or pull-down I/O pad feature during Flash\*Freeze mode without affecting the hold state. If the weak pull-up or pull-down feature is used without the output hold feature, the input and output pads will maintain the configured weak pull-up or pull-down is defined on an output buffer or as bidirectional in output mode, and a hold state is also defined for the same pin, the pin will be configured with the predefined weak pull-up or pull-down. Any I/Os that do not use the hold state or I/O pad weak pull-up or pull-down features will be tristated during Flash\*Freeze mode and the FPGA core will be driven High by inputs. Inputs that are tristated during Flash\*Freeze mode may be left floating without any reliability concern or impact to power consumption.

Table 2-6 shows the I/O pad state based on the configuration and buffer type.

Note that configuring weak pull-up or pull-down for the FF pin is not allowed.

| Buffer Type                        |                                                           | Hold State | I/O Pad Weak<br>Pull-Up/-Down | I/O Pad State in<br>Flash*Freeze Mode |

|------------------------------------|-----------------------------------------------------------|------------|-------------------------------|---------------------------------------|

| Input                              |                                                           | Enabled    | Enabled                       | Weak pull-up/pull-down <sup>1</sup>   |

|                                    |                                                           | Disabled   | Enabled                       | Weak pull-up/pull-down <sup>2</sup>   |

|                                    |                                                           | Enabled    | Disabled                      | Tristate <sup>1</sup>                 |

|                                    |                                                           | Disabled   | Disabled                      | Tristate <sup>2</sup>                 |

| Output                             | Output                                                    |            | "Don't care"                  | Weak pull to hold state               |

|                                    |                                                           | Disabled   | Enabled                       | Weak pull-up/pull-down                |

|                                    |                                                           | Disabled   | Disabled                      | Tristate                              |

| Bidirectional / Tristate<br>Buffer | Bidirectional / Tristate E = 0<br>Buffer (input/tristate) |            | Enabled                       | Weak pull-up/pull-down <sup>1</sup>   |

|                                    |                                                           | Disabled   | Enabled                       | Weak pull-up/pull-down <sup>2</sup>   |

|                                    |                                                           | Enabled    | Disabled                      | Tristate <sup>1</sup>                 |

|                                    |                                                           | Disabled   | Disabled                      | Tristate <sup>2</sup>                 |

|                                    | E = 1 (output)                                            | Enabled    | "Don't care"                  | Weak pull to hold state <sup>3</sup>  |

|                                    |                                                           | Disabled   | Enabled                       | Weak pull-up/pull-down                |

|                                    |                                                           | Disabled   | Disabled                      | Tristate                              |

#### Table 2-6 • IGLOO nano and IGLOO PLUS Flash\*Freeze Mode (type 1 and type 2)—I/O Pad State

Notes:

- 1. Internal core logic driven by this input buffer will be set to the value this I/O had when entering Flash\*Freeze mode.

- 2. Internal core logic driven by this input buffer will be tied High as long as the device is in Flash\*Freeze mode.

- 3. For bidirectional buffers: Internal core logic driven by the input portion of the bidirectional buffer will be set to the hold state.

Global Resources in Low Power Flash Devices

# **Global Resource Support in Flash-Based Devices**

The flash FPGAs listed in Table 3-1 support the global resources and the functions described in this document.

#### Table 3-1 • Flash-Based FPGAs

| Series                                                               | Family <sup>*</sup> | Description                                                                                                                                                                             |  |  |

|----------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IGLOO                                                                | IGLOO               | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                       |  |  |

|                                                                      | IGLOOe              | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                   |  |  |

|                                                                      | IGLOO PLUS          | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                              |  |  |

|                                                                      | IGLOO nano          | The industry's lowest-power, smallest-size solution                                                                                                                                     |  |  |

| ProASIC3                                                             | ProASIC3            | Low power, high-performance 1.5 V FPGAs                                                                                                                                                 |  |  |

|                                                                      | ProASIC3E           | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                |  |  |

|                                                                      | ProASIC3 nano       | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                     |  |  |

|                                                                      | ProASIC3L           | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                   |  |  |

|                                                                      | RT ProASIC3         | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                             |  |  |

| Military ProASIC3/EL Military temperature A3PE600L, A3P1000, and A3P |                     | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                   |  |  |

|                                                                      | Automotive ProASIC3 | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                    |  |  |

| Fusion                                                               | Fusion              | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable<br>analog block, support for ARM <sup>®</sup> Cortex™-M1 soft processors, and flash<br>memory into a monolithic device |  |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO products as listed in Table 3-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 3-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

### **CCC** Locations

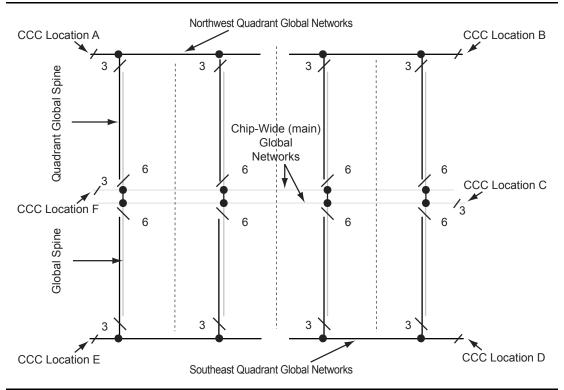

CCCs located in the middle of the east and west sides of the device access the three VersaNet global networks on each side (six total networks), while the four CCCs located in the four corners access three quadrant global networks (twelve total networks). See Figure 4-13.

Figure 4-13 • Global Network Architecture for 60 k Gate Devices and Above

The following explains the locations of the CCCs in IGLOO and ProASIC3 devices:

In Figure 4-15 on page 98 through Figure 4-16 on page 98, CCCs with integrated PLLs are indicated in red, and simplified CCCs are indicated in yellow. There is a letter associated with each location of the CCC, in clockwise order. The upper left corner CCC is named "A," the upper right is named "B," and so on. These names finish up at the middle left with letter "F."

I/O Structures in IGLOO and ProASIC3 Devices

|                    | Maximum Performance |                                                            |                                           |  |

|--------------------|---------------------|------------------------------------------------------------|-------------------------------------------|--|

| Specification      | ProASIC3            | IGLOO V2 or V5<br>Devices, 1.5 V DC Core<br>Supply Voltage | IGLOO V2, 1.2 V DC<br>Core Supply Voltage |  |

| LVTTL/LVCMOS 3.3 V | 200 MHz             | 180 MHz                                                    | TBD                                       |  |

| LVCMOS 2.5 V       | 250 MHz             | 230 MHz                                                    | TBD                                       |  |

| LVCMOS 1.8 V       | 200 MHz             | 180 MHz                                                    | TBD                                       |  |

| LVCMOS 1.5 V       | 130 MHz             | 120 MHz                                                    | TBD                                       |  |

| PCI                | 200 MHz             | 180 MHz                                                    | TBD                                       |  |

| PCI-X              | 200 MHz             | 180 MHz                                                    | TBD                                       |  |

| LVDS               | 350 MHz             | 300 MHz                                                    | TBD                                       |  |

| LVPECL             | 350 MHz             | 300 MHz                                                    | TBD                                       |  |

# Table 7-6 • Maximum I/O Frequency for Single-Ended and Differential I/Os in All Banks in IGLOO and ProASIC Devices (maximum drive strength and high slew selected)

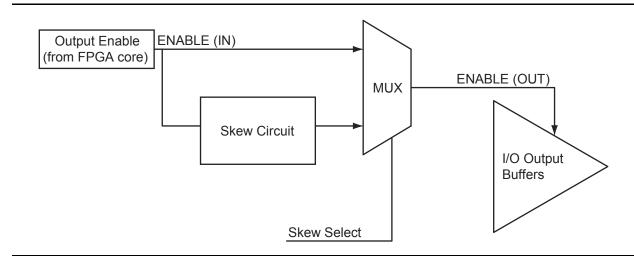

### Selectable Skew between Output Buffer Enable and Disable Times

Low power flash devices have a configurable skew block in the output buffer circuitry that can be enabled to delay output buffer assertion without affecting deassertion time. Since this skew block is only available for the OE signal, the feature can be used in tristate and bidirectional buffers. A typical 1.2 ns delay is added to the OE signal to prevent potential bus contention. Refer to the appropriate family datasheet for detailed timing diagrams and descriptions.

The skew feature is available for all I/O standards.

This feature can be implemented by using a PDC command (Table 7-5 on page 179) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

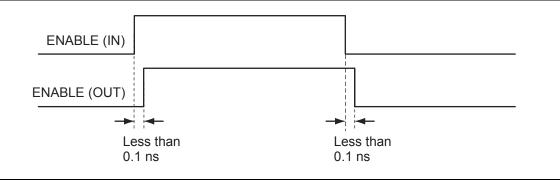

The configurable skew block is used to delay output buffer assertion (enable) without affecting deassertion (disable) time.

Figure 7-13 • Block Diagram of Output Enable Path

Figure 7-14 • Timing Diagram (option 1: bypasses skew circuit)

# **User I/O Naming Convention**

### **IGLOO and ProASIC3**

Due to the comprehensive and flexible nature of IGLOO and ProASIC3 device user I/Os, a naming scheme is used to show the details of each I/O (Figure 7-19 on page 207 and Figure 7-20 on page 207). The name identifies to which I/O bank it belongs, as well as pairing and pin polarity for differential I/Os.

I/O Nomenclature = FF/Gmn/IOuxwBy

Gmn is only used for I/Os that also have CCC access—i.e., global pins.

- FF = Indicates the I/O dedicated for the Flash\*Freeze mode activation pin in IGLOO and ProASIC3L devices only

- G = Global

- m = Global pin location associated with each CCC on the device: A (northwest corner), B (northeast corner), C (east middle), D (southeast corner), E (southwest corner), and F (west middle)

- n = Global input MUX and pin number of the associated Global location m—either A0, A1, A2, B0, B1, B2, C0, C1, or C2. Refer to the "Global Resources in Low Power Flash Devices" section on page 47 for information about the three input pins per clock source MUX at CCC location m.

- u = I/O pair number in the bank, starting at 00 from the northwest I/O bank and proceeding in a clockwise direction

- x = P or U (Positive), N or V (Negative) for differential pairs, or R (Regular—single-ended) for the I/Os that support single-ended and voltage-referenced I/O standards only. U (Positive) or V (Negative)—for LVDS, DDR LVDS, B-LVDS, and M-LVDS only—restricts the I/O differential pair from being selected as an LVPECL pair.

- w = D (Differential Pair), P (Pair), or S (Single-Ended). D (Differential Pair) if both members of the pair are bonded out to adjacent pins or are separated only by one GND or NC pin; P (Pair) if both members of the pair are bonded out but do not meet the adjacency requirement; or S (Single-Ended) if the I/O pair is not bonded out. For Differential Pairs (D), adjacency for ball grid packages means only vertical or horizontal. Diagonal adjacency does not meet the requirements for a true differential pair.

- B = Bank

- y = Bank number (0–3). The Bank number starts at 0 from the northwest I/O bank and proceeds in a clockwise direction.

# 8 – I/O Structures in IGLOOe and ProASIC3E Devices

# Introduction

Low power flash devices feature a flexible I/O structure, supporting a range of mixed voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V) through bank-selectable voltages. IGLOO<sup>®</sup>e, ProASIC<sup>®</sup>3EL, and ProASIC3E families support Pro I/Os.

Users designing I/O solutions are faced with a number of implementation decisions and configuration choices that can directly impact the efficiency and effectiveness of their final design. The flexible I/O structure, supporting a wide variety of voltages and I/O standards, enables users to meet the growing challenges of their many diverse applications. The Libero SoC software provides an easy way to implement I/O that will result in robust I/O design.

This document first describes the two different I/O types in terms of the standards and features they support. It then explains the individual features and how to implement them in Libero SoC.

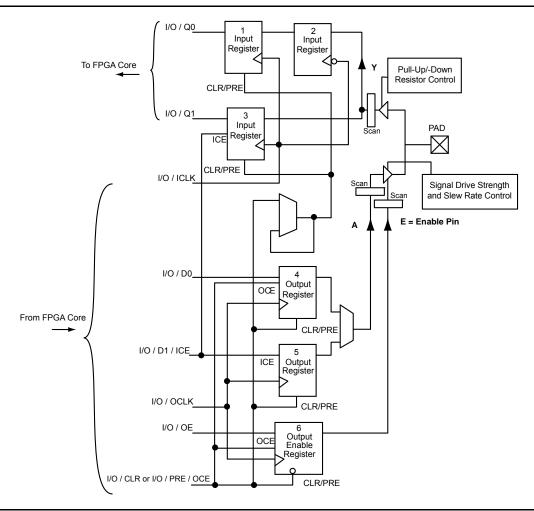

Figure 8-1 • DDR Configured I/O Block Logical Representation

I/O Structures in IGLOOe and ProASIC3E Devices

### IGLOOe and ProASIC3E

For devices requiring Level 3 and/or Level 4 compliance, the board drivers connected to the I/Os must have 10 k $\Omega$  (or lower) output drive resistance at hot insertion, and 1 k $\Omega$  (or lower) output drive resistance at hot removal. This resistance is the transmitter resistance sending a signal toward the I/O, and no additional resistance is needed on the board. If that cannot be assured, three levels of staging can be used to achieve Level 3 and/or Level 4 compliance. Cards with two levels of staging should have the following sequence:

- Grounds

- · Powers, I/Os, and other pins

### **Cold-Sparing Support**

*Cold-sparing* refers to the ability of a device to leave system data undisturbed when the system is powered up, while the component itself is powered down, or when power supplies are floating.

Cold-sparing is supported on ProASIC3E devices only when the user provides resistors from each power supply to ground. The resistor value is calculated based on the decoupling capacitance on a given power supply. The RC constant should be greater than 3  $\mu$ s.

To remove resistor current during operation, it is suggested that the resistor be disconnected (e.g., with an NMOS switch) from the power supply after the supply has reached its final value. Refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 373 for details on cold-sparing.

Cold-sparing means that a subsystem with no power applied (usually a circuit board) is electrically connected to the system that is in operation. This means that all input buffers of the subsystem must present very high input impedance with no power applied so as not to disturb the operating portion of the system.

The 30 k gate devices fully support cold-sparing, since the I/O clamp diode is always off (see Table 8-13 on page 231). If the 30 k gate device is used in applications requiring cold-sparing, a discharge path from the power supply to ground should be provided. This can be done with a discharge resistor or a switched resistor. This is necessary because the 30 k gate devices do not have built-in I/O clamp diodes.

For other IGLOOe and ProASIC3E devices, since the I/O clamp diode is always active, cold-sparing can be accomplished either by employing a bus switch to isolate the device I/Os from the rest of the system or by driving each I/O pin to 0 V. If the resistor is chosen, the resistor value must be calculated based on decoupling capacitance on a given power supply on the board (this decoupling capacitance is in parallel with the resistor). The RC time constant should ensure full discharge of supplies before cold-sparing functionality is required. The resistor is necessary to ensure that the power pins are discharged to ground every time there is an interruption of power to the device.

IGLOOe and ProASIC3E devices support cold-sparing for all I/O configurations. Standards, such as PCI, that require I/O clamp diodes can also achieve cold-sparing compliance, since clamp diodes get disconnected internally when the supplies are at 0 V.

When targeting low power applications, I/O cold-sparing may add additional current if a pin is configured with either a pull-up or pull-down resistor and driven in the opposite direction. A small static current is induced on each I/O pin when the pin is driven to a voltage opposite to the weak pull resistor. The current is equal to the voltage drop across the input pin divided by the pull resistor. Refer to the "Detailed I/O DC Characteristics" section of the appropriate family datasheet for the specific pull resistor value for the corresponding I/O standard.

For example, assuming an LVTTL 3.3 V input pin is configured with a weak pull-up resistor, a current will flow through the pull-up resistor if the input pin is driven LOW. For LVTTL 3.3 V, the pull-up resistor is ~45 k $\Omega$ , and the resulting current is equal to 3.3 V / 45 k $\Omega$  = 73 µA for the I/O pin. This is true also when a weak pull-down is chosen and the input pin is driven High. This current can be avoided by driving the input Low when a weak pull-down resistor is used and driving it High when a weak pull-up resistor is used.

I/O Software Control in Low Power Flash Devices

### **Output Buffers**

There are two variations: Regular and Special.

If the **Regular** variation is selected, only the Width (1 to 128) needs to be entered. The default value for Width is 1.

The Special variation has Width, Technology, Output Drive, and Slew Rate options.

#### **Bidirectional Buffers**

There are two variations: Regular and Special.

The Regular variation has Enable Polarity (Active High, Active Low) in addition to the Width option.

The **Special** variation has Width, Technology, Output Drive, Slew Rate, and Resistor Pull-Up/-Down options.

#### **Tristate Buffers**

Same as Bidirectional Buffers.

#### DDR

There are eight variations: DDR with Regular Input Buffers, Special Input Buffers, Regular Output Buffers, Special Output Buffers, Regular Tristate Buffers, Special Tristate Buffers, Regular Bidirectional Buffers, and Special Bidirectional Buffers.

These variations resemble the options of the previous I/O macro. For example, the Special Input Buffers variation has Width, Technology, Voltage Level, and Resistor Pull-Up/-Down options. DDR is not available on IGLOO PLUS devices.

- 4. Once the desired configuration is selected, click the **Generate** button. The Generate Core window opens (Figure 9-4).

- 5. Enter a name for the macro. Click **OK**. The core will be generated and saved to the appropriate location within the project files (Figure 9-5 on page 257).

Figure 9-4 • Generate Core Window

6. Instantiate the I/O macro in the top-level code.

The user must instantiate the DDR\_REG or DDR\_OUT macro in the design. Use SmartGen to generate both these macros and then instantiate them in your top level. To combine the DDR macros with the I/O, the following rules must be met:

I/O Software Control in Low Power Flash Devices

### Instantiating in HDL code

All the supported I/O macros can be instantiated in the top-level HDL code (refer to the *IGLOO*, *ProASIC3*, *SmartFusion*, *and Fusion Macro Library Guide* for a detailed list of all I/O macros). The following is an example:

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3e;

entity TOP is

port(IN2, IN1 : in std_logic; OUT1 : out std_logic);

end TOP;

architecture DEF_ARCH of TOP is

component INBUF_LVCMOS5U

port(PAD : in std_logic := 'U'; Y : out std_logic);

end component;

component INBUF_LVCMOS5

port(PAD : in std_logic := 'U'; Y : out std_logic);

end component;

component OUTBUF_SSTL3_II

port(D : in std_logic := 'U'; PAD : out std_logic);

end component;

Other component ....

signal x, y, z.....other signals : std_logic;

begin

I1 : INBUF_LVCMOS5U

port map(PAD => IN1, Y =>x);

12 : INBUF LVCMOS5

port map(PAD => IN2, Y => y);

I3 : OUTBUF_SSTL3_II

port map(D => z, PAD => OUT1);

```

other port mapping ...

end DEF\_ARCH;

### Synthesizing the Design

Libero SoC integrates with the Synplify<sup>®</sup> synthesis tool. Other synthesis tools can also be used with Libero SoC. Refer to the *Libero SoC User's Guide* or Libero online help for details on how to set up the Libero tool profile with synthesis tools from other vendors.

During synthesis, the following rules apply:

- Generic macros:

- Users can instantiate generic INBUF, OUTBUF, TRIBUF, and BIBUF macros.

- Synthesis will automatically infer generic I/O macros.

- The default I/O technology for these macros is LVTTL.

- Users will need to use the I/O Attribute Editor in Designer to change the default I/O standard if needed (see Figure 9-6 on page 259).

- Technology-specific I/O macros:

- Technology-specific I/O macros, such as INBUF\_LVCMO25 and OUTBUF\_GTL25, can be instantiated in the design. Synthesis will infer these I/O macros in the netlist.

### I/O Bank Resource Usage

This is an important portion of the report. The user must meet the requirements stated in this table. Figure 9-10 shows the I/O Bank Resource Usage table included in the I/O bank report:

#### Figure 9-10 • I/O Bank Resource Usage Table

The example in Figure 9-10 shows that none of the I/O macros is assigned to the bank because more than one VCCI is detected.

### I/O Voltage Usage

The I/O Voltage Usage table provides the number of VREF (E devices only) and  $V_{CCI}$  assignments required in the design. If the user decides to make I/O assignments manually (PDC or MVN), the issues listed in this table must be resolved before proceeding to Layout. As stated earlier, VREF assignments must be made if there are any voltage-referenced I/Os.

Figure 9-11 shows the I/O Voltage Usage table included in the I/O bank report.

### Figure 9-11 • I/O Voltage Usage Table

The table in Figure 9-11 indicates that there are two voltage-referenced I/Os used in the design. Even though both of the voltage-referenced I/O technologies have the same VCCI voltage, their VREF voltages are different. As a result, two I/O banks are needed to assign the VCCI and VREF voltages.

In addition, there are six single-ended I/Os used that have the same VCCI voltage. Since two banks are already assigned with the same VCCI voltage and there are enough unused bonded I/Os in

### VHDL

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3; use proasic3.all;

entity DDR_BiDir_HSTL_I_LowEnb is

port(DataR, DataF, CLR, CLK, Trien : in std_logic; QR, QF : out std_logic;

PAD : inout std_logic) ;

end DDR_BiDir_HSTL_I_LowEnb;

architecture DEF_ARCH of DDR_BiDir_HSTL_I_LowEnb is

component INV

port(A : in std_logic := 'U'; Y : out std_logic) ;

end component;

component DDR_OUT

port(DR, DF, CLK, CLR : in std_logic := 'U'; Q : out std_logic);

end component;

component DDR_REG

port(D, CLK, CLR : in std_logic := 'U'; QR, QF : out std_logic) ;

end component;

component BIBUF_HSTL_I

port(PAD : inout std_logic := 'U'; D, E : in std_logic := 'U'; Y : out std_logic) ;

end component;

signal TrienAux, D, Q : std_logic ;

begin

```

```

Inv_Tri : INV

port map(A => Trien, Y => TrienAux);

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

DDR_REG_0_inst : DDR_REG

port map(D => D, CLK => CLK, CLR => CLR, QR => QR, QF => QF);

BIBUF_HSTL_I_0_inst : BIBUF_HSTL_I

port map(PAD => PAD, D => Q, E => TrienAux, Y => D);

```

end DEF\_ARCH;

#### Figure 10-11 • DDR Input/Output Cells as Seen by ChipPlanner for IGLOO/e Devices

#### Verilog

module Inbuf\_ddr(PAD,CLR,CLK,QR,QF);

input PAD, CLR, CLK; output QR, QF;

wire Y;

```

DDR_REG_DDR_REG_0_inst(.D(Y), .CLK(CLK), .CLR(CLR), .QR(QR), .QF(QF));

INBUF INBUF_0_inst(.PAD(PAD), .Y(Y));

```

endmodule

module Outbuf\_ddr(DataR,DataF,CLR,CLK,PAD);

input DataR, DataF, CLR, CLK; output PAD;

wire Q, VCC;

```

VCC VCC_1_net(.Y(VCC));

DDR_OUT DDR_OUT_0_inst(.DR(DataR), .DF(DataF), .CLK(CLK), .CLR(CLR), .Q(Q));

OUTBUF OUTBUF_0_inst(.D(Q), .PAD(PAD));

```

endmodule

2. Choose the appropriate security level setting and enter a FlashLock Pass Key. The default is the **Medium** security level (Figure 12-12). Click **Next**.

If you want to select different options for the FPGA and/or FlashROM, this can be set by clicking **Custom Level**. Refer to the "Advanced Options" section on page 322 for different custom security level options and descriptions of each.

Figure 12-12 • Medium Security Level Selected for Low Power Flash Devices

Security in Low Power Flash Devices

3. Choose the desired settings for the FlashROM configurations to be programmed (Figure 12-13). Click **Finish** to generate the STAPL programming file for the design.

Figure 12-13 • FlashROM Configuration Settings for Low Power Flash Devices

### Generation of Security Header Programming File Only— Application 2

As mentioned in the "Application 2: Nontrusted Environment—Unsecured Location" section on page 309, the designer may employ FlashLock Pass Key protection or FlashLock Pass Key with AES encryption on the device before sending it to a nontrusted or unsecured location for device programming. To achieve this, the user needs to generate a programming file containing only the security settings desired (Security Header programming file).

Note: If AES encryption is configured, FlashLock Pass Key protection must also be configured.

The available security options are indicated in Table 12-4 and Table 12-5 on page 317.

| Security Option       | FlashROM Only | FPGA Core Only | Both FlashROM<br>and FPGA |

|-----------------------|---------------|----------------|---------------------------|

| No AES / no FlashLock | -             | -              | -                         |

| FlashLock only        | 1             | 1              | ✓                         |

| AES and FlashLock     | 1             | 1              | ✓                         |

Table 12-4 • FlashLock Security Options for IGLOO and ProASIC3

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

3. VCC switches from 1.5 V to 1.2 V when TRST is LOW.

#### Figure 14-4 • TRST Toggled LOW

In Figure 14-4, the TRST signal and the VCC core voltage signal are labeled. As TRST is pulled to ground, the core voltage is observed to switch from 1.5 V to 1.2 V. The observed fall time is approximately 2 ms.

## **DirectC**

The above analysis is based on FlashPro3, but there are other solutions to ISP, such as DirectC. DirectC is a microprocessor program that can be run in-system to program Microsemi flash devices. For FlashPro3, TRST is the most convenient control signal to use for the recommended circuit. However, for DirectC, users may use any signal to control the FET. For example, the DirectC code can be edited so that a separate non-JTAG signal can be asserted from the microcontroller that signals the board that it is about to start programming the device. After asserting the N-Channel Digital FET control signal, the programming algorithm must allow sufficient time for the supply to rise to 1.5 V before initiating DirectC programming. As seen in Figure 14-3 on page 345, 50 ms is adequate time. Depending on the size of the PCB and the capacitance on the VCC supply, results may vary from system to system. Microsemi recommends using a conservative value for the wait time to make sure that the VCC core voltage is at the right level.

# Conclusion

For applications using IGLOO and ProASIC3L low power FPGAs and taking advantage of the low core voltage power supplies with less than 1.5 V operation, there must be a way for the core voltage to switch from 1.2 V (or other voltage) to 1.5 V, which is required during in-system programming. The circuit explained in this document illustrates one simple, cost-effective way of handling this requirement. A JTAG signal from the FlashPro3 programmer allows the circuit to sense when programming is in progress, enabling it to switch to the correct core voltage.

# 16 – Boundary Scan in Low Power Flash Devices

# **Boundary Scan**

Low power flash devices are compatible with IEEE Standard 1149.1, which defines a hardware architecture and the set of mechanisms for boundary scan testing. JTAG operations are used during boundary scan testing.

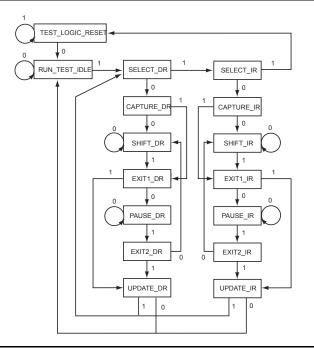

The basic boundary scan logic circuit is composed of the TAP controller, test data registers, and instruction register (Figure 16-2 on page 360).

Low power flash devices support three types of test data registers: bypass, device identification, and boundary scan. The bypass register is selected when no other register needs to be accessed in a device. This speeds up test data transfer to other devices in a test data path. The 32-bit device identification register is a shift register with four fields (LSB, ID number, part number, and version). The boundary scan register observes and controls the state of each I/O pin. Each I/O cell has three boundary scan register cells, each with serial-in, serial-out, parallel-in, and parallel-out pins.

# **TAP Controller State Machine**

The TAP controller is a 4-bit state machine (16 states) that operates as shown in Figure 16-1.

The 1s and 0s represent the values that must be present on TMS at a rising edge of TCK for the given state transition to occur. IR and DR indicate that the instruction register or the data register is operating in that state.

The TAP controller receives two control inputs (TMS and TCK) and generates control and clock signals for the rest of the test logic architecture. On power-up, the TAP controller enters the Test-Logic-Reset state. To guarantee a reset of the controller from any of the possible states, TMS must remain HIGH for five TCK cycles. The TRST pin can also be used to asynchronously place the TAP controller in the Test-Logic-Reset state.

Figure 16-1 • TAP Controller State Machine