Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                      |

|--------------------------------|-----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 516096                                                                      |

| Number of I/O                  | 341                                                                         |

| Number of Gates                | 300000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 484-BGA                                                                     |

| Supplier Device Package        | 484-FPBGA (23x23)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pe3000l-1fgg484 |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

FPGA Array Architecture in Low Power Flash Devices

## **FPGA Array Architecture Support**

The flash FPGAs listed in Table 1-1 support the architecture features described in this document.

#### Table 1-1 • Flash-Based FPGAs

| Series                             | Family <sup>*</sup>  | Description                                                                                                                                                                                    |  |  |  |  |

|------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| IGLOO <sup>®</sup>                 | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |  |  |  |  |

|                                    | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |  |  |  |  |

|                                    | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |  |  |  |  |

|                                    | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |  |  |  |  |

| ProASIC <sup>®</sup> 3 ProASIC3 Lo |                      | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |  |  |  |  |

|                                    | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |  |  |  |  |

|                                    | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |  |  |  |  |

|                                    | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |  |  |  |  |

|                                    | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |  |  |  |  |

|                                    | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |  |  |  |  |

|                                    | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |  |  |  |  |

| analog bl                          |                      | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |  |  |  |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

### IGLOO nano and IGLOO PLUS I/O State in Flash\*Freeze Mode

In IGLOO nano and IGLOO PLUS devices, users have multiple options in how to configure I/Os during Flash\*Freeze mode:

- 1. Hold the previous state

- 2. Set I/O pad to weak pull-up or pull-down

- 3. Tristate I/O pads

The I/O configuration must be configured by the user in the I/O Attribute Editor or in a PDC constraint file, and can be done on a pin-by-pin basis. The output hold feature will hold the output in the last registered state, using the I/O pad weak pull-up or pull-down resistor when the FF pin is asserted. When inputs are configured with the hold feature enabled, the FPGA core side of the input will hold the last valid state of the input pad before the device entered Flash\*Freeze mode. The input pad can be driven to any value, configured as tristate, or configured with the weak pull-up or pull-down I/O pad feature during Flash\*Freeze mode without affecting the hold state. If the weak pull-up or pull-down feature is used without the output hold feature, the input and output pads will maintain the configured weak pull-up or pull-down is defined on an output buffer or as bidirectional in output mode, and a hold state is also defined for the same pin, the pin will be configured with the predefined weak pull-up or pull-down. Any I/Os that do not use the hold state or I/O pad weak pull-up or pull-down features will be tristated during Flash\*Freeze mode and the FPGA core will be driven High by inputs. Inputs that are tristated during Flash\*Freeze mode may be left floating without any reliability concern or impact to power consumption.

Table 2-6 shows the I/O pad state based on the configuration and buffer type.

Note that configuring weak pull-up or pull-down for the FF pin is not allowed.

| Buffer Type                        |                           | Hold State | I/O Pad Weak<br>Pull-Up/-Down | I/O Pad State in<br>Flash*Freeze Mode |  |  |

|------------------------------------|---------------------------|------------|-------------------------------|---------------------------------------|--|--|

| Input                              |                           | Enabled    | Enabled                       | Weak pull-up/pull-down <sup>1</sup>   |  |  |

|                                    |                           | Disabled   | Enabled                       | Weak pull-up/pull-down <sup>2</sup>   |  |  |

|                                    |                           | Enabled    | Disabled                      | Tristate <sup>1</sup>                 |  |  |

|                                    |                           | Disabled   | Disabled                      | Tristate <sup>2</sup>                 |  |  |

| Output                             |                           | Enabled    | Enabled "Don't care" Weak pu  |                                       |  |  |

|                                    |                           | Disabled   | Enabled                       | Weak pull-up/pull-down                |  |  |

|                                    |                           | Disabled   | Disabled                      | Tristate                              |  |  |

| Bidirectional / Tristate<br>Buffer | E = 0<br>(input/tristate) | Enabled    | Enabled                       | Weak pull-up/pull-down <sup>1</sup>   |  |  |

|                                    |                           | Disabled   | Enabled                       | Weak pull-up/pull-down <sup>2</sup>   |  |  |

|                                    |                           | Enabled    | Disabled                      | Tristate <sup>1</sup>                 |  |  |

|                                    |                           |            | Disabled                      | Tristate <sup>2</sup>                 |  |  |

| E = 1 (output)                     |                           | Enabled    | "Don't care"                  | Weak pull to hold state <sup>3</sup>  |  |  |

|                                    |                           | Disabled   | Enabled                       | Weak pull-up/pull-down                |  |  |

|                                    |                           | Disabled   | Disabled                      | Tristate                              |  |  |

#### Table 2-6 • IGLOO nano and IGLOO PLUS Flash\*Freeze Mode (type 1 and type 2)—I/O Pad State

Notes:

- 1. Internal core logic driven by this input buffer will be set to the value this I/O had when entering Flash\*Freeze mode.

- 2. Internal core logic driven by this input buffer will be tied High as long as the device is in Flash\*Freeze mode.

- 3. For bidirectional buffers: Internal core logic driven by the input portion of the bidirectional buffer will be set to the hold state.

Flash\*Freeze Technology and Low Power Modes

- The INBUF\_FF must be driven by a top-level input port of the design.

- The INBUF\_FF AND the ULSICC macro must be used to enable type 2 Flash\*Freeze mode.

- · For type 2 Flash\*Freeze mode, the INBUF\_FF MUST drive some logic in the design.

- For type 1 Flash\*Freeze mode, the INBUF\_FF may drive some logic in the design, but it may also be left floating.

- Only one INBUF\_FF may be instantiated in a device.

- The FF pin threshold voltages are defined by VCCI and the supported single-ended I/O standard in the corresponding I/O bank.

- The FF pin Schmitt trigger option may be configured in the I/O attribute editor in Microsemi's Designer software. The Schmitt trigger option is only available for IGLOOe, IGLOO nano, IGLOO PLUS, ProASIC3EL, and RT ProASIC3 devices.

- A 2 ns glitch filter resides in the Flash\*Freeze Technology block to filter unwanted glitches on the FF pin.

### ULSICC

The User Low Static ICC (ULSICC) macro allows the FPGA core to access the Flash\*Freeze Technology block so that entering and exiting Flash\*Freeze mode can be controlled by the user's design. The ULSICC macro enables a hard block with an available LSICC input port, as shown in Figure 2-3 on page 27 and Figure 2-10 on page 37. Design rules for the ULSICC macro are as follows:

- The ULSICC macro by itself cannot enable Flash\*Freeze mode. The INBUF\_FF AND the ULSICC macro must both be used to enable type 2 Flash\*Freeze mode.

- The ULSICC controls entering the Flash\*Freeze mode by asserting the LSICC input (logic '1') of the ULSICC macro. The FF pin must also be asserted (logic '0') to enter Flash\*Freeze mode.

- When the LSICC signal is '0', the device cannot enter Flash\*Freeze mode; and if already in Flash\*Freeze mode, it will exit.

- When the ULSICC macro is not instantiated in the user's design, the LSICC port will be tied High.

#### Flash\*Freeze Management IP

The Flash\*Freeze management IP can be configured with the Libero (or SmartGen) core generator in a simple, intuitive interface. With the core configuration tool, users can select the number of clocks to be gated, and select whether or not to implement housekeeping. All port names on the Flash\*Freeze management IP block can be renamed by the user.

- The clock gating (filter) blocks include CLKINT buffers for each gated clock output (version 8.3).

- When housekeeping is NOT used, the WAIT\_HOUSEKEEPING signal will be automatically fed back into DONE\_HOUSEKEEPING inside the core, and the ports will not be available at the IP core interface.

- The INBUF\_FF macro is automatically instantiated within the IP core.

- The INBUF\_FF port (default name is "Flash\_Freeze\_N") must be connected to a top-level input port of the design.

- The ULSICC macro is automatically instantiated within the IP core, and the LSICC signal is driven by the FSM.

- Timing analysis can be performed on the clock domain of the source clock (i.e., input to the clock gating filters). For example, if CLKin becomes CLKin\_gated, the timing can be performed on the CLKin domain in SmartTime.

- The gated clocks can be added to the clock list if the user wishes to analyze these clocks specifically. The user can locate the gated clocks by looking for instance names such as those below:

```

Top/ff1/ff_1_wrapper_inst/user_ff_1_wrapper/Primary_Filter_Instance/

Latch_For_Clock_Gating:Q

Top/ff1/ff_1_wrapper_inst/user_ff_1_wrapper/genblk1.genblk2.secondary_filter[0].

seconday_filter_instance/Latch_For_Clock_Gating:Q

Top/ff1/ff_1_wrapper_inst/user_ff_1_wrapper/genblk1.genblk2.secondary_filter[1].

seconday_filter_instance/Latch_For_Clock_Gating:Q

```

## **CCC Support in Microsemi's Flash Devices**

The flash FPGAs listed in Table 4-1 support the CCC feature and the functions described in this document.

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                       |  |  |  |  |  |

|----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                 |  |  |  |  |  |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                             |  |  |  |  |  |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                        |  |  |  |  |  |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                               |  |  |  |  |  |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                           |  |  |  |  |  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                          |  |  |  |  |  |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                               |  |  |  |  |  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                             |  |  |  |  |  |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                       |  |  |  |  |  |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                             |  |  |  |  |  |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                              |  |  |  |  |  |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex™-M1 soft processors, and flash memory into a monolithic device |  |  |  |  |  |

#### Table 4-1 • Flash-Based FPGAs

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

# 5 – FlashROM in Microsemi's Low Power Flash Devices

### Introduction

The Fusion, IGLOO, and ProASIC3 families of low power flash-based devices have a dedicated nonvolatile FlashROM memory of 1,024 bits, which provides a unique feature in the FPGA market. The FlashROM can be read, modified, and written using the JTAG (or UJTAG) interface. It can be read but not modified from the FPGA core. Only low power flash devices contain on-chip user nonvolatile memory (NVM).

### Architecture of User Nonvolatile FlashROM

Low power flash devices have 1 kbit of user-accessible nonvolatile flash memory on-chip that can be read from the FPGA core fabric. The FlashROM is arranged in eight banks of 128 bits (16 bytes) during programming. The 128 bits in each bank are addressable as 16 bytes during the read-back of the FlashROM from the FPGA core. Figure 5-1 shows the FlashROM logical structure.

The FlashROM can only be programmed via the IEEE 1532 JTAG port. It cannot be programmed directly from the FPGA core. When programming, each of the eight 128-bit banks can be selectively reprogrammed. The FlashROM can only be reprogrammed on a bank boundary. Programming involves an automatic, on-chip bank erase prior to reprogramming the bank. The FlashROM supports synchronous read. The address is latched on the rising edge of the clock, and the new output data is stable after the falling edge of the same clock cycle. For more information, refer to the timing diagrams in the DC and Switching Characteristics chapter of the appropriate datasheet. The FlashROM can be read on byte boundaries. The upper three bits of the FlashROM address from the FPGA core define the bank being accessed. The lower four bits of the FlashROM address from the FPGA core define which of the 16 bytes in the bank is being accessed.

|                                 |   | Byte Number in Bank |    |    |    |    |    | 4 LSB of ADDR (READ) |   |   |   |   |   |   |   |   |   |

|---------------------------------|---|---------------------|----|----|----|----|----|----------------------|---|---|---|---|---|---|---|---|---|

|                                 |   | 15                  | 14 | 13 | 12 | 11 | 10 | 9                    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| of                              | 7 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| 3 MSB of<br>EAD)                | 6 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| ΑD                              | 5 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| RE C                            | 4 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| dr (                            | 3 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| NU                              | 2 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| Bank Number 3 MS<br>ADDR (READ) | 1 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| ä                               | 0 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

Figure 5-1 • FlashROM Architecture

FlashROM in Microsemi's Low Power Flash Devices

## **Programming and Accessing FlashROM**

The FlashROM content can only be programmed via JTAG, but it can be read back selectively through the JTAG programming interface, the UJTAG interface, or via direct FPGA core addressing. The pages of the FlashROM can be made secure to prevent read-back via JTAG. In that case, read-back on these secured pages is only possible by the FPGA core fabric or via UJTAG.

A 7-bit address from the FPGA core defines which of the eight pages (three MSBs) is being read, and which of the 16 bytes within the selected page (four LSBs) are being read. The FlashROM content can be read on a random basis; the access time is 10 ns for a device supporting commercial specifications. The FPGA core will be powered down during writing of the FlashROM content. FPGA power-down during FlashROM programming is managed on-chip, and FPGA core functionality is not available during programming of the FlashROM. Table 5-2 summarizes various FlashROM access scenarios.

| Access Mode | FlashROM Read | FlashROM Write |

|-------------|---------------|----------------|

| JTAG        | Yes           | Yes            |

| UJTAG       | Yes           | No             |

| FPGA core   | Yes           | No             |

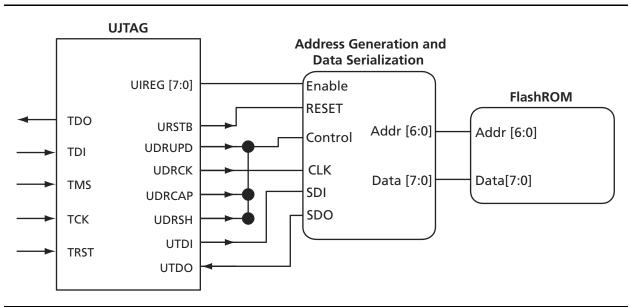

Figure 5-6 shows the accessing of the FlashROM using the UJTAG macro. This is similar to FPGA core access, where the 7-bit address defines which of the eight pages (three MSBs) is being read and which of the 16 bytes within the selected page (four LSBs) are being read. Refer to the "UJTAG Applications in Microsemi's Low Power Flash Devices" section on page 363 for details on using the UJTAG macro to read the FlashROM.

Figure 5-7 on page 139 and Figure 5-8 on page 139 show the FlashROM access from the JTAG port. The FlashROM content can be read on a random basis. The three-bit address defines which page is being read or updated.

Figure 5-6 • Block Diagram of Using UJTAG to Read FlashROM Contents

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

#### Table 6-2 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

| WIDTHA[1:0] | WIDTHB[1:0] | D×W   |

|-------------|-------------|-------|

| 00          | 00          | 4k×1  |

| 01          | 01          | 2k×2  |

| 10          | 10          | 1k×4  |

| 11          | 11          | 512×9 |

Note: The aspect ratio settings are constant and cannot be changed on the fly.

#### BLKA and BLKB

These signals are active-low and will enable the respective ports when asserted. When a BLKx signal is deasserted, that port's outputs hold the previous value.

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, BLKB should be tied to ground.

#### WENA and WENB

These signals switch the RAM between read and write modes for the respective ports. A LOW on these signals indicates a write operation, and a HIGH indicates a read.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WENB should be tied to ground.

#### **CLKA and CLKB**

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

Note: For Automotive ProASIC3 devices, dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). For use of this macro as a single-port SRAM, the inputs and clock of one port should be tied off (grounded) to prevent errors during design compile.

#### PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A LOW on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the corresponding output in the next clock cycle.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, PIPEB should be tied to ground. For use in dual-port mode, the same clock with an inversion between the two clock pins of the macro should be used in the design to prevent errors during compile.

#### WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A LOW on these signals makes the output retain data from the previous read. A HIGH indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WMODEB should be tied to ground.

#### RESET

This active-low signal resets the control logic, forces the output hold state registers to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory array.

While the RESET signal is active, read and write operations are disabled. As with any asynchronous reset signal, care must be taken not to assert it too close to the edges of active read and write clocks.

#### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 6-3 on page 155).

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

Note: For timing diagrams of the RAM signals, refer to the appropriate family datasheet.

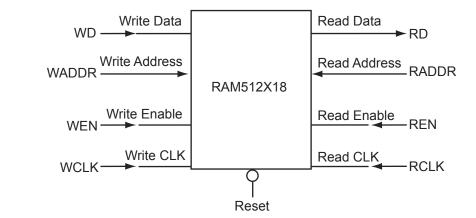

Figure 6-5 • 512X18 Two-Port RAM Block Diagram

### Signal Descriptions for RAM512X18

RAM512X18 has slightly different behavior from RAM4K9, as it has dedicated read and write ports.

#### WW and RW

These signals enable the RAM to be configured in one of the two allowable aspect ratios (Table 6-5).

| WW[1:0] | RW[1:0] | D×W      |

|---------|---------|----------|

| 01      | 01      | 512×9    |

| 10      | 10      | 256×18   |

| 00, 11  | 00, 11  | Reserved |

#### WD and RD

These are the input and output data signals, and they are 18 bits wide. When a 512×9 aspect ratio is used for write, WD[17:9] are unused and must be grounded. If this aspect ratio is used for read, RD[17:9] are undefined.

#### WADDR and RADDR

These are read and write addresses, and they are nine bits wide. When the 256×18 aspect ratio is used for write or read, WADDR[8] and RADDR[8] are unused and must be grounded.

#### WCLK and RCLK

These signals are the write and read clocks, respectively. They can be clocked on the rising or falling edge of WCLK and RCLK.

#### WEN and REN

These signals are the write and read enables, respectively. They are both active-low by default. These signals can be configured as active-high.

#### RESET

This active-low signal resets the control logic, forces the output hold state registers to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory array.

While the RESET signal is active, read and write operations are disabled. As with any asynchronous reset signal, care must be taken not to assert it too close to the edges of active read and write clocks.

#### PIPE

This signal is used to specify pipelined read on the output. A LOW on PIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the output in the next clock cycle.

#### Table 6-10 • RAM and FIFO Memory Block Consumption

|       |    |               |                                 |                                |                                |                                                | Depth                                           |                                                 |                                                    |                                                    |                                                   |                                                    |

|-------|----|---------------|---------------------------------|--------------------------------|--------------------------------|------------------------------------------------|-------------------------------------------------|-------------------------------------------------|----------------------------------------------------|----------------------------------------------------|---------------------------------------------------|----------------------------------------------------|

|       | Ì  |               | 2                               | 56                             | 512                            | 1,024                                          | 2,048                                           | 4,096                                           | 8,192                                              | 16,384                                             | 32,768                                            | 65,536                                             |

|       | 1  |               | Two-Port                        | Dual-Port                      | Dual-Port                      | Dual-Port                                      | Dual-Port                                       | Dual-Port                                       | Dual-Port                                          | Dual-Port                                          | Dual-Port                                         | Dual-Port                                          |

|       | 1  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 1                                               | 1                                               | 2                                                  | 4                                                  | 8                                                 | 16 × 1                                             |

|       |    | Configuration | Any                             | Any                            | Any                            | 1,024 × 4                                      | 2,048 × 2                                       | 4,096 × 1                                       | 2 × (4,096 × 1)<br>Cascade Deep                    | 4 × (4,096 × 1)<br>Cascade Deep                    | 8 × (4,096 × 1)<br>Cascade Deep                   | 16 × (4,096 × 1)<br>Cascade Deep                   |

|       | 2  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 1                                               | 2                                               | 4                                                  | 8                                                  | 16                                                | 32                                                 |

|       |    | Configuration | Any                             | Any                            | Any                            | 1,024×4                                        | 2,048 × 2                                       | 2 × (4,096 × 1)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 2 Wide   | 8 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 2 Wide   | 16 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 2 Wide | 32 × (4,096 × 1)<br>Cascaded 16<br>Deep and 2 Wide |

|       | 4  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 2                                               | 4                                               | 8                                                  | 16                                                 | 32                                                | 64                                                 |

|       |    | Configuration | Any                             | Any                            | Any                            | 1,024 × 4                                      | 2 × (2,048 × 2)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 4 Wide   | 16 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 4 Wide  | 32 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 4 Wide | 64 × (4,096 × 1)<br>Cascaded 16<br>Deep and 4 Wide |

|       | 8  | Number Block  | 1                               | 1                              | 1                              | 2                                              | 4                                               | 8                                               | 16                                                 | 32                                                 | 64                                                |                                                    |

|       |    | Configuration | Any                             | Any                            | Any                            | 2 × (1,024 × 4)<br>Cascaded Wide               | 4 × (2,048 × 2)<br>Cascaded Wide                | 8 × (4,096 × 1)<br>Cascaded Wide                | 16 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 8 Wide  | 32 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 8 Wide  | 64 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 8 Wide |                                                    |

|       | 9  | Number Block  | 1                               | 1                              | 1                              | 2                                              | 4                                               | 8                                               | 16                                                 | 32                                                 |                                                   |                                                    |

|       |    | Configuration | Any                             | Any                            | Any                            | 2 × (512 × 9)<br>Cascaded Deep                 | 4 × (512 × 9)<br>Cascaded Deep                  | 8 × (512 × 9)<br>Cascaded Deep                  | 16 × (512 × 9)<br>Cascaded Deep                    | 32 × (512 × 9)<br>Cascaded Deep                    |                                                   |                                                    |

|       | 16 | Number Block  | 1                               | 1                              | 1                              | 4                                              | 8                                               | 16                                              | 32                                                 | 64                                                 |                                                   |                                                    |

| Width |    | Configuration | 256 × 18                        | 256 × 18                       | 256 × 18                       | 4 × (1,024 × 4)<br>Cascaded Wide               | 8 × (2,048 × 2)<br>Cascaded Wide                | 16 × (4,096 × 1)<br>Cascaded Wide               | 32 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 16 Wide | 32 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 16 Wide |                                                   |                                                    |

|       | 18 | Number Block  | 1                               | 2                              | 2                              | 4                                              | 8                                               | 18                                              | 32                                                 |                                                    |                                                   |                                                    |

|       |    | Configuration | 256 × 8                         | 2 × (512 × 9)<br>Cascaded Wide | 2 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded 2 Deep<br>and 2 Wide | 8 × (512 × 9)<br>Cascaded 4 Deep<br>and 2 Wide  | 16 × (512 × 9)<br>Cascaded 8 Deep<br>and 2 Wide | 16 × (512 × 9)<br>Cascaded 16<br>Deep and 2 Wide   |                                                    |                                                   |                                                    |

|       | 32 | Number Block  | 2                               | 4                              | 4                              | 8                                              | 16                                              | 32                                              | 64                                                 |                                                    |                                                   |                                                    |

|       |    | Configuration | 2 × (256 × 18)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 8 × (1,024 × 4)<br>Cascaded Wide               | 16 × (2,048 × 2)<br>Cascaded Wide               | 32 × (4,096 × 1)<br>Cascaded Wide               | 64 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 32 Wide |                                                    |                                                   |                                                    |

|       | 36 | Number Block  | 2                               | 4                              | 4                              | 8                                              | 16                                              | 32                                              |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 2 × (256 × 18)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded 2 Deep<br>and 4 Wide | 16 × (512 × 9)<br>Cascaded 4 Deep<br>and 4 Wide | 16 × (512 × 9)<br>Cascaded 8 Deep<br>and 4 Wide |                                                    |                                                    |                                                   |                                                    |

|       | 64 | Number Block  | 4                               | 8                              | 8                              | 16                                             | 32                                              | 64                                              |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 4 × (256 × 18)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 16 × (1,024 × 4)<br>Cascaded Wide              | 32 × (2,048 × 2)<br>Cascaded Wide               | 64 × (4,096 × 1)<br>Cascaded Wide               |                                                    |                                                    |                                                   |                                                    |

|       | 72 | Number Block  | 4                               | 8                              | 8                              | 16                                             | 32                                              |                                                 |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 4 × (256 × 18)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 16 × (512 × 9)<br>Cascaded Wide                | 16 × (512 × 9)<br>Cascaded 4 Deep<br>and 8 Wide |                                                 |                                                    |                                                    |                                                   |                                                    |

|       |    | 11            |                                 |                                |                                | -                                              | -                                               |                                                 |                                                    |                                                    |                                                   |                                                    |

Note: Memory configurations represented by grayed cells are not supported.

### Features Supported on Every I/O

Table 7-5 lists all features supported by transmitter/receiver for single-ended and differential I/Os. Table 7-6 on page 180 lists the performance of each I/O technology.

| Feature                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All I/O                                                     | <ul> <li>High performance (Table 7-6 on page 180)</li> <li>Electrostatic discharge (ESD) protection</li> <li>I/O register combining option</li> </ul>                                                                                                                                                                                                                                                           |

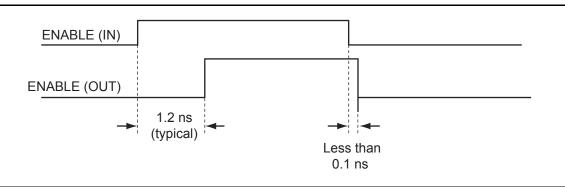

| Single-Ended Transmitter Features                           | <ul> <li>Hot-swap: <ul> <li>30K gate devices: hot-swap in every mode</li> <li>All other IGLOO and ProASIC3 devices: no hot-swap</li> </ul> </li> <li>Output slew rate: 2 slew rates (except 30K gate devices)</li> <li>Weak pull-up and pull-down resistors</li> <li>Output drive: 3 drive strengths</li> <li>Programmable output loading</li> <li>Skew between output buffer enable/disable time: 2</li> </ul> |

|                                                             | <ul> <li>ns delay on rising edge and 0 ns delay on falling edge (see the "Selectable Skew between Output Buffer Enable and Disable Times" section on page 199 for more information)</li> <li>LVTTL/LVCMOS 3.3 V outputs compatible with 5 V TTL inputs</li> </ul>                                                                                                                                               |

| Single-Ended Receiver Features                              | <ul> <li>5 V–input–tolerant receiver (Table 7-12 on page 193)</li> <li>Separate ground plane for GNDQ pin and power plane for VMV pin are used for input buffer to reduce output-induced noise.</li> </ul>                                                                                                                                                                                                      |

| Differential Receiver Features—250K through 1M Gate Devices | <ul> <li>Separate ground plane for GNDQ pin and power<br/>plane for VMV pin are used for input buffer to reduce<br/>output-induced noise.</li> </ul>                                                                                                                                                                                                                                                            |

| CMOS-Style LVDS, B-LVDS, M-LVDS, or<br>LVPECL Transmitter   | <ul> <li>Two I/Os and external resistors are used to provide a CMOS-style LVDS, DDR LVDS, B-LVDS, and M-LVDS/LVPECL transmitter solution.</li> <li>High slew rate</li> <li>Weak pull-up and pull-down resistors</li> <li>Programmable output loading</li> </ul>                                                                                                                                                 |

Table 7-5 • I/O Features

I/O Structures in IGLOO and ProASIC3 Devices

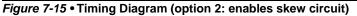

At the system level, the skew circuit can be used in applications where transmission activities on bidirectional data lines need to be coordinated. This circuit, when selected, provides a timing margin that can prevent bus contention and subsequent data loss and/or transmitter over-stress due to transmitter-to-transmitter current shorts. Figure 7-16 presents an example of the skew circuit implementation in a bidirectional communication system. Figure 7-17 on page 201 shows how bus contention is created, and Figure 7-18 on page 201 shows how it can be avoided with the skew circuit.

Figure 7-16 • Example of Implementation of Skew Circuits in Bidirectional Transmission Systems Using IGLOO or ProASIC3 Devices

-

ProASIC3L FPGA Fabric User's Guide

Refer to Table 8-16 on page 242 for SLEW and OUT\_DRIVE settings. Table 8-18 on page 244 lists the voltages for the supported I/O standards.

| I/O Standard         | SLEW (output only) | OUT_DRIVE (output only) | SKEW (tribuf and bibuf only) | RES_PULL | OUT_LOAD (output only) | <b>COMBINE_REGISTER</b> | IN_DELAY (input only) | IN_DELAY_VAL (input only) | SCHMITT_TRIGGER (input only) |

|----------------------|--------------------|-------------------------|------------------------------|----------|------------------------|-------------------------|-----------------------|---------------------------|------------------------------|

| LVTTL/LVCMOS 3.3 V   | See<br>Table 8-15  | See<br>Table 8-15 on    | Off                          | None     | 35 pF                  | -                       | Off                   | 0                         | Off                          |

| LVCMOS 2.5 V         | on page 240        | page 240                | Off                          | None     | 35 pF                  | -                       | Off                   | 0                         | Off                          |

| LVCMOS 2.5/5.0 V     |                    |                         | Off                          | None     | 35 pF                  | -                       | Off                   | 0                         | Off                          |

| LVCMOS 1.8 V         |                    |                         | Off                          | None     | 35 pF                  | -                       | Off                   | 0                         | Off                          |

| LVCMOS 1.5 V         |                    |                         | Off                          | None     | 35 pF                  | -                       | Off                   | 0                         | Off                          |

| PCI (3.3 V)          |                    |                         | Off                          | None     | 10 pF                  | -                       | Off                   | 0                         | Off                          |

| PCI-X (3.3 V)        |                    |                         | Off                          | None     | 10 pF                  | -                       | Off                   | 0                         | Off                          |

| GTL+ (3.3 V)         |                    |                         | Off                          | None     | 10 pF                  | -                       | Off                   | 0                         | Off                          |

| GTL+ (2.5 V)         |                    |                         | Off                          | None     | 10 pF                  | -                       | Off                   | 0                         | Off                          |

| GTL (3.3 V)          |                    |                         | Off                          | None     | 10 pF                  | -                       | Off                   | 0                         | Off                          |

| GTL (2.5 V)          |                    |                         | Off                          | None     | 10 pF                  | _                       | Off                   | 0                         | Off                          |

| HSTL Class I         |                    |                         | Off                          | None     | 20 pF                  | _                       | Off                   | 0                         | Off                          |

| HSTL Class II        |                    |                         | Off                          | None     | 20 pF                  | -                       | Off                   | 0                         | Off                          |

| SSTL2 Class I and II |                    |                         | Off                          | None     | 30 pF                  | _                       | Off                   | 0                         | Off                          |

| SSTL3 Class I and II |                    |                         | Off                          | None     | 30 pF                  | _                       | Off                   | 0                         | Off                          |

| LVDS, B-LVDS, M-LVDS |                    |                         | Off                          | None     | 0 pF                   | -                       | Off                   | 0                         | Off                          |

| LVPECL               |                    |                         | Off                          | None     | 0 pF                   | -                       | Off                   | 0                         | Off                          |

### Table 8-17 • IGLOOe and ProASIC3E I/O Default Attributes

т

Г

DDR for Microsemi's Low Power Flash Devices

## **DDR Support in Flash-Based Devices**

The flash FPGAs listed in Table 10-1 support the DDR feature and the functions described in this document.

#### Table 10-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 10-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 10-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

## **Related Documents**

### **User's Guides**

FlashPro User's Guide

http://www.microsemi.com/soc/documents/flashpro\_ug.pdf

## **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                    | Page |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                  | N/A  |

| v1.5<br>(August 2009)   | The "CoreMP7 Device Security" section was removed from "Security in ARM-<br>Enabled Low Power Flash Devices", since M7-enabled devices are no longer<br>supported.                                                                         | 304  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 12-1 • Flash-Based FPGAs.                                                                                                                                                         | 302  |

| v1.3<br>(October 2008)  | The "Security Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                           | 302  |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 12-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul> | 302  |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                                                                                                                      | N/A  |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                | 302  |

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

## Microsemi's Flash Families Support Voltage Switching Circuit

The flash FPGAs listed in Table 14-1 support the voltage switching circuit feature and the functions described in this document.

Table 14-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit

| Series   | Family <sup>*</sup>  | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 14-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 14-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

2. VCC rises to 1.5 V before programming begins.

#### Figure 14-3 • Programming Algorithm

The oscilloscope plot in Figure 14-3 shows a wider time interval for the programming algorithm and includes the TDI and TMS signals from the FlashPro3. These signals carry the programming information that is programmed into the device and should only start toggling after the  $V_{CC}$  core voltage reaches 1.5 V. Again, TRST from FlashPro3 and the  $V_{CC}$  core voltage of the IGLOO device are labeled. As shown in Figure 14-3, TDI and TMS are floating initially, and the core voltage is 1.2 V. When a programming command on the FlashPro3 is executed, TRST is driven HIGH and TDI is momentarily driven to ground. In response to the HIGH TRST signal, the circuit responds and pulls the core voltage to 1.5 V. After 100 ms, TRST is briefly driven LOW by the FlashPro software. This is expected behavior that ensures the device JTAG state machine is in Reset prior to programming. TRST remains HIGH for the duration of the programming. It can be seen in Figure 14-3 that the VCC core voltage signal remains at 1.5 V for approximately 50 ms before information starts passing through on TDI and TMS. This confirms that the voltage switching circuit drives the VCC core supply voltage to 1.5 V prior to programming.

UJTAG Applications in Microsemi's Low Power Flash Devices

## Conclusion

Microsemi low power flash FPGAs offer many unique advantages, such as security, nonvolatility, reprogrammablity, and low power—all in a single chip. In addition, Fusion, IGLOO, and ProASIC3 devices provide access to the JTAG port from core VersaTiles while the device is in normal operating mode. A wide range of available user-defined JTAG opcodes allows users to implement various types of applications, exploiting this feature of these devices. The connection between the JTAG port and core tiles is implemented through an embedded and hardwired UJTAG tile. A UJTAG tile can be instantiated in designs using the UJTAG library cell. This document presents multiple examples of UJTAG applications, such as dynamic reconfiguration, silicon test and debug, fine-tuning of the design, and RAM initialization. Each of these applications offers many useful advantages.

## **Related Documents**

### **Application Notes**

RAM Initialization and ROM Emulation in ProASIC<sup>PLUS</sup> Devices http://www.microsemi.com/soc/documents/APA RAM Initd AN.pdf

## **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                            | Page |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| December 2011           | Information on the drive strength and slew rate of TDO pins was added to the "Silicon Testing and Debugging" section (SAR 31749).                                  | 370  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                          | N/A  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 17-1 • Flash-Based FPGAs.                                                                                 | 364  |

| v1.3<br>(October 2008)  | The "UJTAG Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                      | 364  |

|                         | The title of Table 17-3 • Configuration Bits of Fusion, IGLOO, and ProASIC3 CCC Blocks was revised to include Fusion.                                              | 368  |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 17-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> </ul> | 364  |

|                         | <ul> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul>                                                                                 |      |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                                              | N/A  |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                        | 364  |

Power-Up/-Down Behavior of Low Power Flash Devices

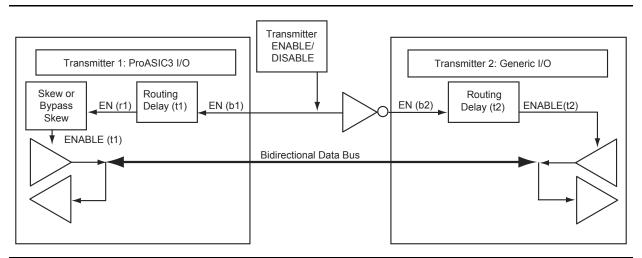

### **Transient Current on VCC**

The characterization of the transient current on VCC is performed on nearly all devices within the IGLOO, ProASIC3L, and ProASIC3 families. A sample size of five units is used from each device family member. All the device I/Os are internally pulled down while the transient current measurements are performed. For ProASIC3 devices, the measurements at typical conditions show that the maximum transient current on VCC, when the power supply is powered at ramp-rates ranging from 15 V/ms to 0.15 V/ms, does not exceed the maximum standby current specified in the device datasheets. Refer to the DC and Switching Characteristics chapters of the *ProASIC3 Flash Family FPGAS* datasheet and *ProASIC3E Flash Family FPGAs* datasheet for more information.

Similarly, IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices exhibit very low transient current on VCC. The transient current does not exceed the typical operating current of the device while in active mode. For example, the characterization of AGL600-FG256 V2 and V5 devices has shown that the transient current on VCC is typically in the range of 1–5 mA.

### **Transient Current on VCCI**

The characterization of the transient current on VCCI is performed on devices within the IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3, ProASIC3 nano, and ProASIC3L groups of devices, similarly to VCC transient current measurements. For ProASIC3 devices, the measurements at typical conditions show that the maximum transient current on VCCI, when the power supply is powered at ramp-rates ranging from 33 V/ms to 0.33 V/ms, does not exceed the maximum standby current specified in the device datasheet. Refer to the DC and Switching Characteristics chapters of the *ProASIC3 Flash Family FPGAS* datasheet and *ProASIC3E Flash Family FPGAs* datasheet for more information.

Similarly, IGLOO, IGLOO PLUS, and ProASIC3L devices exhibit very low transient current on VCCI. The transient current does not exceed the typical operating current of the device while in active mode. For example, the characterization of AGL600-FG256 V2 and V5 devices has shown that the transient current on VCCI is typically in the range of 1–2 mA.

Power-Up/-Down Behavior of Low Power Flash Devices

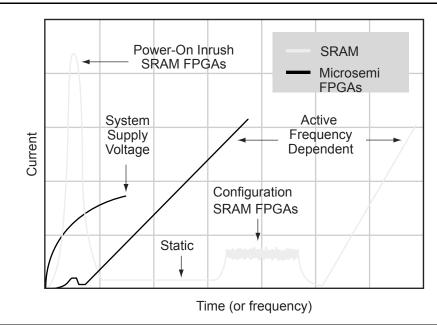

Figure 18-5 • I/O State as a Function of VCCI and VCC Voltage Levels for IGLOO V2, IGLOO nano V2, IGLOO PLUS V2, and ProASIC3L Devices Running at VCC = 1.2 V ± 0.06 V

Power-Up/-Down Behavior of Low Power Flash Devices

## **Related Documents**

### Datasheets

ProASIC3 Flash Family FPGAs http://www.microsemi.com/soc/documents/PA3\_DS.pdf ProASIC3E Flash Family FPGAs http://www.microsemi.com/soc/documents/PA3E\_DS.pdf

## List of Changes

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                                                                  | Page |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| v1.2<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to the document as supported device types.                                                                                                                                                                                               |      |

| v1.1<br>(October 2008)  | The "Introduction" section was updated to add Military ProASIC3EL and RT<br>ProASIC3 devices to the list of devices that can have inputs driven in while the<br>device is not powered.                                                                                                   | 373  |

|                         | The "Flash Devices Support Power-Up Behavior" section was revised to include new families and make the information more concise.                                                                                                                                                         | 374  |

|                         | The "Cold-Sparing" section was revised to add Military ProASIC3/EL and RT ProASIC3 devices to the lists of devices with and without cold-sparing support.                                                                                                                                | 382  |

|                         | The "Hot-Swapping" section was revised to add Military ProASIC3/EL and RT<br>ProASIC3 devices to the lists of devices with and without hot-swap support.<br>AGL400 was added to the list of devices that do not support hot-swapping.                                                    | 383  |

| v1.0<br>(August 2008)   | This document was revised, renamed, and assigned a new part number. It now includes data for the IGLOO and ProASIC3L families.                                                                                                                                                           | N/A  |

| v1.3<br>(March 2008)    | The "List of Changes" section was updated to include the three different I/O Structure handbook chapters.                                                                                                                                                                                | 384  |

| v1.2<br>(February 2008) | The first sentence of the "PLL Behavior at Brownout Condition" section was updated to read, "When PLL power supply voltage and/or V <sub>CC</sub> levels drop below the VCC brownout levels (0.75 V $\pm$ 0.25 V), the PLL output lock signal goes low and/or the output clock is lost." | 381  |

| v1.1<br>(January 2008)  | The "PLL Behavior at Brownout Condition" section was added.                                                                                                                                                                                                                              | 381  |