Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                    |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | ·                                                                         |

| Total RAM Bits                 | 516096                                                                    |

| Number of I/O                  | 620                                                                       |

| Number of Gates                | 300000                                                                    |

| Voltage - Supply               | 1.14V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                           |

| Package / Case                 | 896-BGA                                                                   |

| Supplier Device Package        | 896-FBGA (31x31)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pe3000l-fg896 |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Flash\*Freeze Technology and Low Power Modes

# Flash Families Support the Flash\*Freeze Feature

The low power flash FPGAs listed in Table 2-1 support the Flash\*Freeze feature and the functions described in this document.

#### Table 2-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 2-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 2-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

Flash\*Freeze Technology and Low Power Modes

# **Sleep and Shutdown Modes**

### **Sleep Mode**

IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 FPGAs support Sleep mode when device functionality is not required. In Sleep mode,  $V_{CC}$  (core voltage),  $V_{JTAG}$  (JTAG DC voltage), and VPUMP (programming voltage) are grounded, resulting in the FPGA core being turned off to reduce power consumption. While the device is in Sleep mode, the rest of the system can still be operating and driving the input buffers of the device. The driven inputs do not pull up the internal power planes, and the current draw is limited to minimal leakage current.

Table 2-7 shows the power supply status in Sleep mode.

#### Table 2-7 • Sleep Mode—Power Supply Requirement for IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 Devices

| Power Supplies | Power Supply State |

|----------------|--------------------|

| VCC            | Powered off        |

| VCCI = VMV     | Powered on         |

| VJTAG          | Powered off        |

| VPUMP          | Powered off        |

Refer to the "Power-Up/-Down Behavior" section on page 33 for more information about I/O states during Sleep mode and the timing diagram for entering and exiting Sleep mode.

### Shutdown Mode

Shutdown mode is supported for all IGLOO nano and IGLOO PLUS devices as well the following IGLOO/e devices: AGL015, AGL030, AGLE600, AGLE3000, and A3PE3000L. Shutdown mode can be used by turning off all power supplies when the device function is not needed. Cold-sparing and hot-insertion features enable these devices to be powered down without turning off the entire system. When power returns, the live-at-power-up feature enables operation of the device after reaching the voltage activation point.

- · The device is reset upon exiting Flash\*Freeze mode or internal state saving is not required.

- State saving is required, but data and clock management is performed external to the FPGA. In other words, incoming data is externally guaranteed and held valid prior to entering Flash\*Freeze mode.

Type 2 Flash\*Freeze mode is ideally suited for applications with the following design criteria:

- Entering Flash\*Freeze mode is dependent on an internal or external signal in addition to the external FF pin.

- State saving is required and incoming data is not externally guaranteed valid.

- The designer wants to use his/her own Flash\*Freeze management IP for clock and data management.

- The designer wants to use his/her own Flash\*Freeze management logic for clock and data management.

- Internal housekeeping is required prior to entering Flash\*Freeze mode. Housekeeping activities

may include loading data to SRAM, system shutdown, completion of current task, or ensuring

valid Flash\*Freeze pin assertion.

There is no downside to type 2 mode, and Microsemi's Flash\*Freeze management IP offers a very low tile count clock and data management solution. Microsemi's recommendation for most designs is to use type 2 Flash\*Freeze mode with Flash\*Freeze management IP.

### **Design Solutions**

#### Clocks

- Microsemi recommends using a completely synchronous design in Type 2 mode with Flash\*Freeze management IP cleanly gating all internal and external clocks. This will prevent narrow pulses upon entrance and exit from Flash\*Freeze mode (Figure 2-5 on page 30).

- Upon entering Flash\*Freeze mode, external clocks become tied off High, internal to the clock pin (unless hold state is used on IGLOO nano or IGLOO PLUS), and PLLs are turned off. Any clock that is externally Low will realize a Low to High transition internal to the device while entering Flash\*Freeze. If clocks will float during Flash\*Freeze mode, Microsemi recommends using the weak pull-up feature. If clocks will continue to drive the device during Flash\*Freeze mode, the clock gating (filter) available in Flash\*Freeze management IP can help to filter unwanted narrow clock pulses upon Flash\*Freeze mode entry and exit.

- Clocks may continue to drive FPGA pins while the device is in Flash\*Freeze mode, with virtually

no power consumption. The weak pull-up/-down configuration will result in unnecessary power

consumption if used in this scenario.

- Floating clocks can cause totem pole currents on the input I/O circuitry when the device is in

active mode. If clocks are externally gated prior to entering Flash\*Freeze mode, Microsemi

recommends gating them to a known value (preferably '1', to avoid a possible narrow pulse upon

Flash\*Freeze mode exit), and not leaving them floating. However, during Flash\*Freeze mode, all

inputs and clocks are internally tied off to prevent totem pole currents, so they can be left floating.

- Upon exiting Flash\*Freeze mode, the design must allow maximum acquisition time for the PLL to acquire the lock signal, and for a PLL clock to become active. If a PLL output clock is used as the primary clock for Flash\*Freeze management IP, it is important to note that the clock gating circuit will only release other clocks after the primary PLL output clock becomes available.

# Chip and Quadrant Global I/Os

The following sections give an overview of naming conventions and other related I/O information.

## Naming of Global I/Os

In low power flash devices, the global I/Os have access to certain clock conditioning circuitry and have direct access to the global network. Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities to those of regular I/Os. Due to the comprehensive and flexible nature of the I/Os in low power flash devices, a naming scheme is used to show the details of the I/O. The global I/O uses the generic name Gmn/IOuxwByVz. Note that Gmn refers to a global input pin and IOuxwByVz refers to a regular I/O Pin, as these I/Os can be used as either global or regular I/Os. Refer to the I/O Structures chapter of the user's guide for the device that you are using for more information on this naming convention.

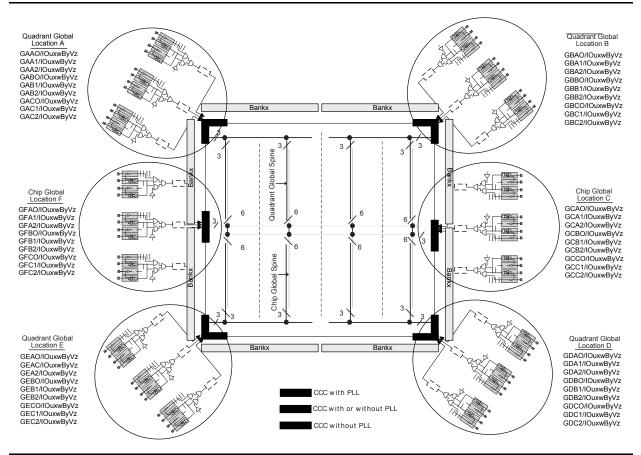

Figure 3-4 represents the global input pins connection. It shows all 54 global pins available to access the 18 global networks in ProASIC3E families.

Figure 3-4 • Global Connections Details

# **CCC Support in Microsemi's Flash Devices**

The flash FPGAs listed in Table 4-1 support the CCC feature and the functions described in this document.

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                       |

|----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                 |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                             |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                        |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                               |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                           |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                          |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                               |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                             |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                       |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                             |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                              |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex™-M1 soft processors, and flash memory into a monolithic device |

#### Table 4-1 • Flash-Based FPGAs

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

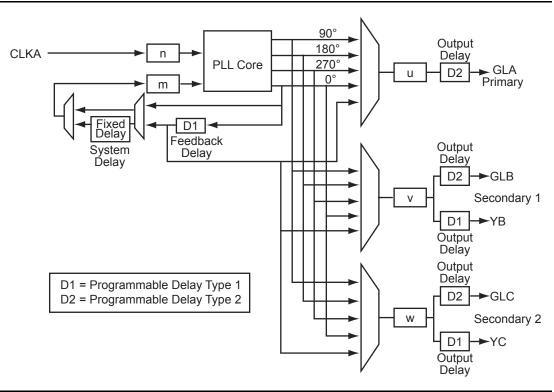

# **Global Buffers with PLL Function**

Clocks requiring frequency synthesis or clock adjustments can utilize the PLL core before connecting to the global / quadrant global networks. A maximum of 18 CCC global buffers can be instantiated in a device—three per CCC and up to six CCCs per device. Each PLL core can generate up to three global/quadrant clocks, while a clock delay element provides one.

The PLL functionality of the clock conditioning block is supported by the PLL macro.

| Clock Source            | Clock Conditioning | Output                                                                                                        |

|-------------------------|--------------------|---------------------------------------------------------------------------------------------------------------|

| Input LVDS/LVPECL Macro | PLL Macro          | GLA<br>or<br>GLA and (GLB or YB)<br>or<br>GLA and (GLC or YC)<br>or<br>GLA and (GLB or YB) and<br>(GLC or YC) |

Notes:

- 1. For Fusion only.

- 2. Refer to the IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide for more information.

- 3. For INBUF\* driving a PLL macro or CLKDLY macro, the I/O will be hard-routed to the CCC; i.e., will be placed by software to a dedicated Global I/O.

- 4. IGLOO nano and ProASIC3 nano devices do not support differential inputs.

#### Figure 4-4 • CCC Options: Global Buffers with PLL

The PLL macro provides five derived clocks (three independent) from a single reference clock. The PLL macro also provides power-down input and lock output signals. The additional inputs shown on the macro are configuration settings, which are configured through the use of SmartGen. For manual setting of these bits refer to the *IGLOO*, *ProASIC3*, *SmartFusion*, *and Fusion Macro Library Guide* for details.

Figure 4-6 on page 87 illustrates the various clock output options and delay elements.

difference will cause the VCO to increase its frequency until the output signal is phase-identical to the input after undergoing division. In other words, lock in both frequency and phase is achieved when the output frequency is M times the input. Thus, clock division in the feedback path results in multiplication at the output.

A similar argument can be made when the delay element is inserted into the feedback path. To achieve steady-state lock, the VCO output signal will be delayed by the input period *less* the feedback delay. For periodic signals, this is equivalent to time-advancing the output clock by the feedback delay.

Another key parameter of a PLL system is the acquisition time. Acquisition time is the amount of time it takes for the PLL to achieve lock (i.e., phase-align the feedback signal with the input reference clock). For example, suppose there is no voltage applied to the VCO, allowing it to operate at its free-running frequency. Should an input reference clock suddenly appear, a lock would be established within the maximum acquisition time.

## **Functional Description**

This section provides detailed descriptions of PLL block functionality: clock dividers and multipliers, clock delay adjustment, phase adjustment, and dynamic PLL configuration.

## **Clock Dividers and Multipliers**

The PLL block contains five programmable dividers. Figure 4-20 shows a simplified PLL block.

Figure 4-20 • PLL Block Diagram

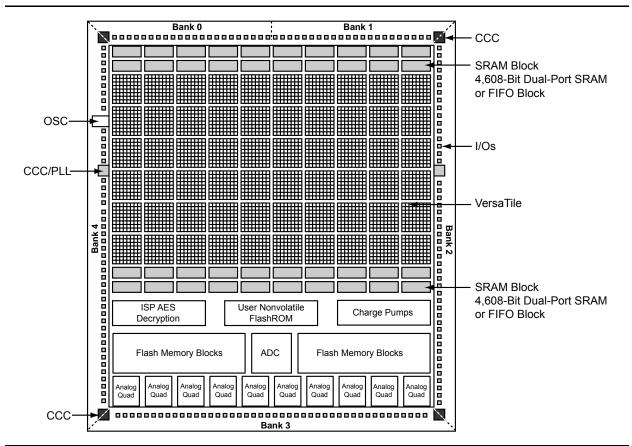

# ProASIC3L FPGA Fabric User's Guide

DYNCCC Core(.CLKA(CLKA), .EXTFB(GND), .POWERDOWN(POWERDOWN), .GLA(GLA), .LOCK(LOCK), .CLKB(CLKB), .GLB(GLB), .YB(), .CLKC(CLKC), .GLC(GLC), .YC(), .SDIN(SDIN), .SCLK(SCLK), .SSHIFT(SSHIFT), .SUPDATE(SUPDATE), .MODE(MODE), .SDOUT(SDOUT), .OADIV0(GND), .OADIV1(GND), .OADIV2(VCC), .OADIV3(GND), .OADIV4(GND), .OAMUX0(GND), .OAMUX1(GND), .OAMUX2(VCC), .DLYGLA0(GND), .DLYGLA1(GND), .DLYGLA2(GND), .DLYGLA3(GND), .DLYGLA4(GND), .OBDIV0(GND), .OBDIV1(GND), .OBDIV2(GND), .OBDIV3(GND), .OBDIV4(GND), .OBMUX0(GND), .OBMUX1(GND), .OBMUX2(GND), .DLYYB0(GND), .DLYYB1(GND), .DLYYB2(GND), .DLYYB3(GND), .DLYYB4(GND), .DLYGLB0(GND), .DLYGLB1(GND), .DLYGLB2(GND), .DLYGLB3(GND), .DLYGLB4(GND), .OCDIV0(GND), .OCDIV1(GND), .OCDIV2(GND), .OCDIV3(GND), .OCDIV4(GND), .OCMUX0(GND), .OCMUX1(GND), .OCMUX2(GND), .DLYYC0(GND), .DLYYC1(GND), .DLYYC2(GND), .DLYYC3(GND), .DLYYC4(GND), .DLYGLC0(GND), .DLYGLC1(GND), .DLYGLC2(GND), .DLYGLC3(GND), .DLYGLC4(GND), .FINDIV0(VCC), .FINDIV1(GND), .FINDIV2(VCC), .FINDIV3(GND), .FINDIV4(GND), .FINDIV5(GND), .FINDIV6(GND), .FBDIV0(GND), .FBDIV1(GND), .FBDIV2(GND), .FBDIV3(GND), .FBDIV4(GND), .FBDIV5(VCC), .FBDIV6(GND), .FBDLY0(GND), .FBDLY1(GND), .FBDLY2(GND), .FBDLY3(GND), .FBDLY4(GND), .FBSEL0(VCC), .FBSEL1(GND), .XDLYSEL(GND), .VCOSEL0(GND), .VCOSEL1(GND), .VCOSEL2(VCC)); defparam Core.VCOFREQUENCY = 165.000;

endmodule

\*\*\*\*\*

### **Delayed Clock Configuration**

The CLKDLY macro can be generated with the desired delay and input clock source (Hardwired I/O, External I/O, or Core Logic), as in Figure 4-28.

#### Figure 4-28 • Delayed Clock Configuration Dialog Box

After setting all the required parameters, users can generate one or more PLL configurations with HDL or EDIF descriptions by clicking the **Generate** button. SmartGen gives the option of saving session results and messages in a log file:

```

Macro Parameters

*****

: delay_macro

Name

Family

: ProASIC3

: Verilog

Output Format

: Delayed Clock

Type

Delay Index

: 2

CLKA Source

: Hardwired I/O

Total Clock Delay = 0.935 ns.

The resultant CLKDLY macro Verilog netlist is as follows:

module delay_macro(GL,CLK);

output GL;

input CLK;

```

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

global assignments are not allocated properly. See the "Physical Constraints for Quadrant Clocks" section for information on assigning global signals to the quadrant clock networks.

Promoted global signals will be instantiated with CLKINT macros to drive these signals onto the global network. This is automatically done by Designer when the Auto-Promotion option is selected. If the user wishes to assign the signals to the quadrant globals instead of the default chip globals, this can done by using ChipPlanner, by declaring a physical design constraint (PDC), or by importing a PDC file.

### **Physical Constraints for Quadrant Clocks**

If it is necessary to promote global clocks (CLKBUF, CLKINT, PLL, CLKDLY) to quadrant clocks, the user can define PDCs to execute the promotion. PDCs can be created using PDC commands (pre-compile) or the MultiView Navigator (MVN) interface (post-compile). The advantage of using the PDC flow over the MVN flow is that the Compile stage is able to automatically promote any regular net to a global net before assigning it to a quadrant. There are three options to place a quadrant clock using PDC commands:

- Place a clock core (not hardwired to an I/O) into a quadrant clock location.

- Place a clock core (hardwired to an I/O) into an I/O location (set\_io) or an I/O module location (set\_location) that drives a quadrant clock location.

- Assign a net driven by a regular net or a clock net to a quadrant clock using the following command:

assign\_local\_clock -net <net name> -type quadrant <quadrant clock region>

where

<net name> is the name of the net assigned to the local user clock region.

<quadrant clock region> defines which quadrant the net should be assigned to. Quadrant clock regions are defined as UL (upper left), UR (upper right), LL (lower left), and LR (lower right).

Note: If the net is a regular net, the software inserts a CLKINT buffer on the net.

#### For example:

assign\_local\_clock -net localReset -type quadrant UR

Keep in mind the following when placing quadrant clocks using MultiView Navigator:

#### Hardwired I/O–Driven CCCs

• Find the associated clock input port under the Ports tab, and place the input port at one of the Gmn\* locations using PinEditor or I/O Attribute Editor, as shown in Figure 4-32.

Figure 4-32 • Port Assignment for a CCC with Hardwired I/O Clock Input

ProASIC3L FPGA Fabric User's Guide

| Date                   | Changes                                                                                                                                                                                                                                                                                  | Page |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| v1.2<br>(June 2008)    | <ul> <li>The following changes were made to the family descriptions in Figure 4-1 • Overview of the CCCs Offered in Fusion, IGLOO, and ProASIC3:</li> <li>• ProASIC3L was updated to include 1.5 V.</li> <li>• The number of PLLs for ProASIC3E was changed from five to six.</li> </ul> | 77   |  |  |

| v1.1<br>(March 2008)   | Table 4-1 • Flash-Based FPGAs and the associated text were updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                         | 79   |  |  |

|                        | The "Global Input Selections" section was updated to include 15 k gate devices as supported I/O types for globals, for CCC only.                                                                                                                                                         |      |  |  |

|                        | Table 4-5 • Number of CCCs by Device Size and Package was revised to include ProASIC3L, IGLOO PLUS, A3P015, AGL015, AGLP030, AGLP060, and AGLP125.                                                                                                                                       |      |  |  |

|                        | The "IGLOO and ProASIC3 CCC Locations" section was revised to include 15 k gate devices in the exception statements, as they do not contain PLLs.                                                                                                                                        | 97   |  |  |

| v1.0<br>(January 2008) | Information about unlocking the PLL was removed from the "Dynamic PLL Configuration" section.                                                                                                                                                                                            |      |  |  |

|                        | In the "Dynamic PLL Configuration" section, information was added about running Layout and determining the exact setting of the ports.                                                                                                                                                   | 116  |  |  |

|                        | In Table 4-8 • Configuration Bit Descriptions for the CCC Blocks, the following bits were updated to delete "transport to the user" and reference the footnote at the bottom of the table: 79 to 71.                                                                                     | 106  |  |  |

FlashROM in Microsemi's Low Power Flash Devices

# **FlashROM Applications**

The SmartGen core generator is used to configure FlashROM content. You can configure each page independently. SmartGen enables you to create and modify regions within a page; these regions can be 1 to 16 bytes long (Figure 5-4).

|          |   |    | Byte Number in Page |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----------|---|----|---------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|          |   | 15 | 14                  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|          | 7 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| <u> </u> | 6 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| he       | 5 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Numb     | 4 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| ۵<br>ا   | 3 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Pag      | 2 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| а.       | 1 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|          | 0 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

#### Figure 5-4 • FlashROM Configuration

The FlashROM content can be changed independently of the FPGA core content. It can be easily accessed and programmed via JTAG, depending on the security settings of the device. The SmartGen core generator enables each region to be independently updated (described in the "Programming and Accessing FlashROM" section on page 138). This enables you to change the FlashROM content on a per-part basis while keeping some regions "constant" for all parts. These features allow the FlashROM to be used in diverse system applications. Consider the following possible uses of FlashROM:

- Internet protocol (IP) addressing (wireless or fixed)

- System calibration settings

- Restoring configuration after unpredictable system power-down

- · Device serialization and/or inventory control

- Subscription-based business models (e.g., set-top boxes)

- Secure key storage

- Asset management tracking

- Date stamping

- Version management

I/O Structures in IGLOO and ProASIC3 Devices

# Low Power Flash Device I/O Support

The low power flash FPGAs listed in Table 7-1 support I/Os and the functions described in this document.

#### Table 7-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                       |

|----------|----------------------|-------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L             |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                       |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

4. Right-click and then choose **Highlight VREF range**. All the pins covered by that VREF pin will be highlighted (Figure 9-14).

#### Figure 9-14 • VREF Range

Using PinEditor or ChipPlanner, VREF pins can also be assigned (Figure 9-15).

#### Figure 9-15 • Assigning VREF from PinEditor

To unassign a VREF pin:

- 1. Select the pin to unassign.

- 2. Right-click and choose **Use Pin for VREF.** The check mark next to the command disappears. The VREF pin is now a regular pin.

Resetting the pin may result in unassigning I/O cores, even if they are locked. In this case, a warning message appears so you can cancel the operation.

After you assign the VREF pins, right-click a VREF pin and choose **Highlight VREF Range** to see how many I/Os are covered by that pin. To unhighlight the range, choose **Unhighlight All** from the **Edit** menu.

## **Related Documents**

Below is a list of related documents, their location on the Microsemi SoC Products Group website, and a brief summary of each document.

## **Application Notes**

Programming Antifuse Devices http://www.microsemi.com/soc/documents/AntifuseProgram\_AN.pdf Implementation of Security in Actel's ProASIC and ProASIC<sup>PLUS</sup> Flash-Based FPGAs http://www.microsemi.com/soc/documents/Flash\_Security\_AN.pdf

## **User's Guides**

### FlashPro Programmers

FlashPro4,<sup>1</sup> FlashPro3, FlashPro Lite, and FlashPro<sup>2</sup> http://www.microsemi.com/soc/products/hardware/program\_debug/flashpro/default.aspx *FlashPro User's Guide* http://www.microsemi.com/soc/documents/FlashPro\_UG.pdf The FlashPro User's Guide includes hardware and software setup, self-test instructions, use instructions, and a troubleshooting / error message guide.

### Silicon Sculptor 3 and Silicon Sculptor II

http://www.microsemi.com/soc/products/hardware/program\_debug/ss/default.aspx

## **Other Documents**

http://www.microsemi.com/soc/products/solutions/security/default.aspx#flashlock The security resource center describes security in Microsemi Flash FPGAs. *Quality and Reliability Guide* http://www.microsemi.com/soc/documents/RelGuide.pdf *Programming and Functional Failure Guidelines* http://www.microsemi.com/soc/documents/FA\_Policies\_Guidelines\_5-06-00002.pdf

<sup>1.</sup> FlashPro4 replaced FlashPro3 in Q1 2010.

<sup>2.</sup> FlashPro is no longer available.

Security in Low Power Flash Devices

# **Security Support in Flash-Based Devices**

The flash FPGAs listed in Table 12-1 support the security feature and the functions described in this document.

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                          |  |  |  |

|----------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                    |  |  |  |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                |  |  |  |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                  |  |  |  |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                           |  |  |  |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                              |  |  |  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                             |  |  |  |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                  |  |  |  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                |  |  |  |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                          |  |  |  |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                |  |  |  |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                 |  |  |  |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM Cortex™-M1 soft processors, and flash memory into a monolithic device |  |  |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 12-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 12-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

Security in Low Power Flash Devices

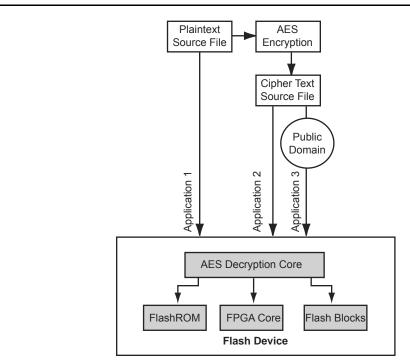

Figure 12-3 • Block Representation of the AES Decryption Core in a Fusion AFS600 FPGA

## **Security Features**

IGLOO and ProASIC3 devices have two entities inside: FlashROM and the FPGA core fabric. Fusion devices contain three entities: FlashROM, FBs, and the FPGA core fabric. The parts can be programmed or updated independently with a STAPL programming file. The programming files can be AES-encrypted or plaintext. This allows maximum flexibility in providing security to the entire device. Refer to the "Programming Flash Devices" section on page 287 for information on the FlashROM structure.

Unlike SRAM-based FPGA devices, which require a separate boot PROM to store programming data, low power flash devices are nonvolatile, and the secured configuration data is stored in on-chip flash cells that are part of the FPGA fabric. Once programmed, this data is an inherent part of the FPGA array and does not need to be loaded at system power-up. SRAM-based FPGAs load the configuration bitstream upon power-up; therefore, the configuration is exposed and can be read easily.

The built-in FPGA core, FBs, and FlashROM support programming files encrypted with the 128-bit AES (FIPS-192) block ciphers. The AES key is stored in dedicated, on-chip flash memory and can be programmed before the device is shipped to other parties (allowing secure remote field updates).

### Security in ARM-Enabled Low Power Flash Devices

There are slight differences between the regular flash devices and the  $\text{ARM}^{\$}$ -enabled flash devices, which have the M1 and M7 prefix.

The AES key is used by Microsemi and preprogrammed into the device to protect the ARM IP. As a result, the design is encrypted along with the ARM IP, according to the details below.

Security in Low Power Flash Devices

# **Security in Action**

This section illustrates some applications of the security advantages of Microsemi's devices (Figure 12-6).

Note: Flash blocks are only used in Fusion devices

Figure 12-6 • Security Options

# **Related Documents**

## **User's Guides**

FlashPro User's Guide

http://www.microsemi.com/soc/documents/flashpro\_ug.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                    | Page |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                  | N/A  |

| v1.5<br>(August 2009)   | The "CoreMP7 Device Security" section was removed from "Security in ARM-<br>Enabled Low Power Flash Devices", since M7-enabled devices are no longer<br>supported.                                                                         |      |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 12-1 • Flash-Based FPGAs.                                                                                                                                                         |      |

| v1.3<br>(October 2008)  | The "Security Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                           |      |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 12-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul> |      |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                                                                                                                      | N/A  |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                | 302  |

UJTAG Applications in Microsemi's Low Power Flash Devices

# **Typical UJTAG Applications**

Bidirectional access to the JTAG port from VersaTiles—without putting the device into test mode creates flexibility to implement many different applications. This section describes a few of these. All are based on importing/exporting data through the UJTAG tiles.

## **Clock Conditioning Circuitry—Dynamic Reconfiguration**

In low power flash devices, CCCs, which include PLLs, can be configured dynamically through either an 81-bit embedded shift register or static flash programming switches. These 81 bits control all the characteristics of the CCC: routing MUX architectures, delay values, divider values, etc. Table 17-3 lists the 81 configuration bits in the CCC.

| Bit Number(s) | Control Function |

|---------------|------------------|

| 80            | RESET ENABLE     |

| 79            | DYNCSEL          |

| 78            | DYNBSEL          |

| 77            | DYNASEL          |

| <76:74>       | VCOSEL [2:0]     |

| 73            | STATCSEL         |

| 72            | STATBSEL         |

| 71            | STATASEL         |

| <70:66>       | DLYC [4:0]       |

| <65:61>       | DLYB {4:0]       |

| <60:56>       | DLYGLC [4:0]     |

| <55:51>       | DLYGLB [4:0]     |

| <50:46>       | DLYGLA [4:0]     |

| 45            | XDLYSEL          |

| <44:40>       | FBDLY [4:0]      |

| <39:38>       | FBSEL            |

| <37:35>       | OCMUX [2:0]      |

| <34:32>       | OBMUX [2:0]      |

| <31:29>       | OAMUX [2:0]      |

| <28:24>       | OCDIV [4:0]      |

| <23:19>       | OBDIV [4:0]      |

| <18:14>       | OADIV [4:0]      |

| <13:7>        | FBDIV [6:0]      |

| <6:0>         | FINDIV [6:0]     |

Table 17-3 • Configuration Bits of Fusion, IGLOO, and ProASIC3 CCC Blocks

The embedded 81-bit shift register (for the dynamic configuration of the CCC) is accessible to the VersaTiles, which, in turn, have access to the UJTAG tiles. Therefore, the CCC configuration shift register can receive and load the new configuration data stream from JTAG.

Dynamic reconfiguration eliminates the need to reprogram the device when reconfiguration of the CCC functional blocks is needed. The CCC configuration can be modified while the device continues to operate. Employing the UJTAG core requires the user to design a module to provide the configuration data and control the CCC configuration shift register. In essence, this is a user-designed TAP Controller requiring chip resources.

Similar reconfiguration capability exists in the ProASIC<sup>PLUS®</sup> family. The only difference is the number of shift register bits controlling the CCC (27 in ProASIC<sup>PLUS</sup> and 81 in IGLOO, ProASIC3, and Fusion).