Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Betans                         |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 516096                                                                      |

| Number of I/O                  | 341                                                                         |

| Number of Gates                | 300000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 484-BGA                                                                     |

| Supplier Device Package        | 484-FPBGA (23x23)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pe3000l-fgg484i |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

FPGA Array Architecture in Low Power Flash Devices

# **FPGA Array Architecture Support**

The flash FPGAs listed in Table 1-1 support the architecture features described in this document.

#### Table 1-1 • Flash-Based FPGAs

| Series                 | Family <sup>*</sup>  | Description                                                                                                                                                                                    |  |

|------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO <sup>®</sup>     | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |  |

|                        | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |  |

|                        | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |  |

|                        | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |  |

| ProASIC <sup>®</sup> 3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |  |

|                        | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |  |

|                        | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |  |

|                        | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |  |

|                        | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |  |

|                        | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |  |

|                        | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |  |

| Fusion                 | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

## **Clock Aggregation Architecture**

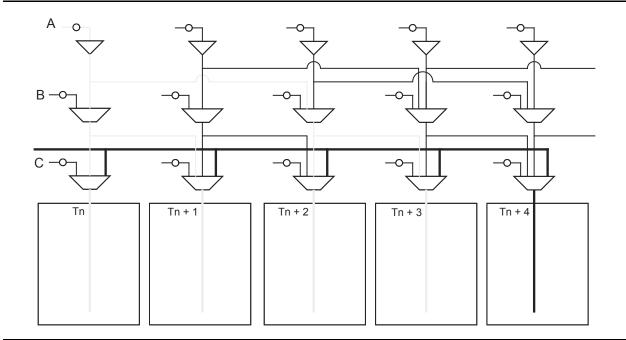

This clock aggregation feature allows a balanced clock tree, which improves clock skew. The physical regions for clock aggregation are defined from left to right and shift by one spine. For chip global networks, there are three types of clock aggregation available, as shown in Figure 3-10:

- Long lines that can drive up to four adjacent spines (A)

- Long lines that can drive up to two adjacent spines (B)

- Long lines that can drive one spine (C)

There are three types of clock aggregation available for the quadrant spines, as shown in Figure 3-10:

- I/Os or local resources that can drive up to four adjacent spines

- I/Os or local resources that can drive up to two adjacent spines

- I/Os or local resources that can drive one spine

As an example, A3PE600 and AFS600 devices have twelve spine locations: T1, T2, T3, T4, T5, T6, B1, B2, B3, B4, B5, and B6. Table 3-7 shows the clock aggregation you can have in A3PE600 and AFS600.

Figure 3-10 • Four Spines Aggregation

| Clock Aggregation | Spine                                                                |  |  |

|-------------------|----------------------------------------------------------------------|--|--|

| 1 spine           | T1, T2, T3, T4, T5, T6, B1, B2, B3, B4, B5, B6                       |  |  |

| 2 spines          | T1:T2, T2:T3, T3:T4, T4:T5, T5:T6, B1:B2, B2:B3, B3:B4, B4:B5, B5:B6 |  |  |

| 4 spines          | B1:B4, B2:B5, B3:B6, T1:T4, T2:T5, T3:T6                             |  |  |

The clock aggregation for the quadrant spines can cross over from the left to right quadrant, but not from top to bottom. The quadrant spine assignment T1:T4 is legal, but the quadrant spine assignment T1:B1 is not legal. Note that this clock aggregation is hardwired. You can always assign signals to spine T1 and B2 by instantiating a buffer, but this may add skew in the signal.

# 4 – Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## Introduction

This document outlines the following device information: Clock Conditioning Circuit (CCC) features, PLL core specifications, functional descriptions, software configuration information, detailed usage information, recommended board-level considerations, and other considerations concerning clock conditioning circuits and global networks in low power flash devices or mixed signal FPGAs.

# **Overview of Clock Conditioning Circuitry**

In Fusion, IGLOO, and ProASIC3 devices, the CCCs are used to implement frequency division, frequency multiplication, phase shifting, and delay operations. The CCCs are available in six chip locations—each of the four chip corners and the middle of the east and west chip sides. For device-specific variations, refer to the "Device-Specific Layout" section on page 94.

The CCC is composed of the following:

- PLL core

- 3 phase selectors

- 6 programmable delays and 1 fixed delay that advances/delays phase

- 5 programmable frequency dividers that provide frequency multiplication/division (not shown in Figure 4-6 on page 87 because they are automatically configured based on the user's required frequencies)

- · 1 dynamic shift register that provides CCC dynamic reconfiguration capability

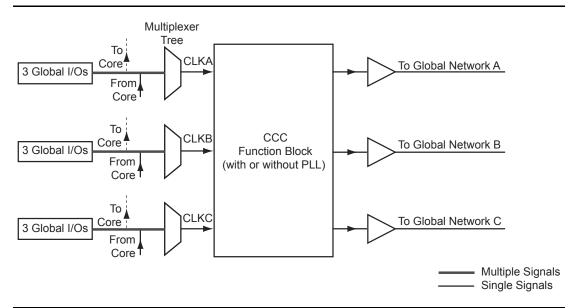

Figure 4-1 provides a simplified block diagram of the physical implementation of the building blocks in each of the CCCs.

Figure 4-1 • Overview of the CCCs Offered in Fusion, IGLOO, and ProASIC3

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## **CCC** Locations

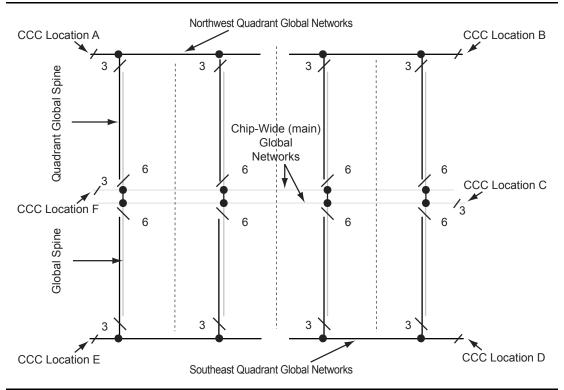

CCCs located in the middle of the east and west sides of the device access the three VersaNet global networks on each side (six total networks), while the four CCCs located in the four corners access three quadrant global networks (twelve total networks). See Figure 4-13.

Figure 4-13 • Global Network Architecture for 60 k Gate Devices and Above

The following explains the locations of the CCCs in IGLOO and ProASIC3 devices:

In Figure 4-15 on page 98 through Figure 4-16 on page 98, CCCs with integrated PLLs are indicated in red, and simplified CCCs are indicated in yellow. There is a letter associated with each location of the CCC, in clockwise order. The upper left corner CCC is named "A," the upper right is named "B," and so on. These names finish up at the middle left with letter "F."

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

Each group of control bits is assigned a specific location in the configuration shift register. For a list of the 81 configuration bits (C[80:0]) in the CCC and a description of each, refer to "PLL Configuration Bits Description" on page 106. The configuration register can be serially loaded with the new configuration data and programmed into the CCC using the following ports:

- SDIN: The configuration bits are serially loaded into a shift register through this port. The LSB of the configuration data bits should be loaded first.

- SDOUT: The shift register contents can be shifted out (LSB first) through this port using the shift operation.

- SCLK: This port should be driven by the shift clock.

- SSHIFT: The active-high shift enable signal should drive this port. The configuration data will be shifted into the shift register if this signal is HIGH. Once SSHIFT goes LOW, the data shifting will be halted.

- SUPDATE: The SUPDATE signal is used to configure the CCC with the new configuration bits when shifting is complete.

To access the configuration ports of the shift register (SDIN, SDOUT, SSHIFT, etc.), the user should instantiate the CCC macro in his design with appropriate ports. Microsemi recommends that users choose SmartGen to generate the CCC macros with the required ports for dynamic reconfiguration.

Users must familiarize themselves with the architecture of the CCC core and its input, output, and configuration ports to implement the desired delay and output frequency in the CCC structure. Figure 4-22 shows a model of the CCC with configurable blocks and switches.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

# **SRAM/FIFO Support in Flash-Based Devices**

The flash FPGAs listed in Table 6-1 support SRAM and FIFO blocks and the functions described in this document.

#### Table 6-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>                                                        | Description                                                                                                                                                                       |  |

|----------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO    | IGLOO                                                                      | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                 |  |

|          | IGLOOe                                                                     | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                             |  |

|          | IGLOO nano                                                                 | The industry's lowest-power, smallest-size solution                                                                                                                               |  |

|          | IGLOO PLUS                                                                 | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                        |  |

| ProASIC3 | ProASIC3                                                                   | Low power, high-performance 1.5 V FPGAs                                                                                                                                           |  |

|          | ProASIC3E                                                                  | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                          |  |

|          | ProASIC3 nano                                                              | Lowest-cost solution with enhanced I/O capabilities                                                                                                                               |  |

|          | ProASIC3L                                                                  | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                             |  |

|          | RT ProASIC3                                                                | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                       |  |

|          | Military ProASIC3/EL Military temperature A3PE600L, A3P1000, and A3PE3000L |                                                                                                                                                                                   |  |

|          | Automotive ProASIC3                                                        | ProASIC3 FPGAs qualified for automotive applications                                                                                                                              |  |

| Fusion   | Fusion                                                                     | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex™-M1 soft processors, and flash memory into a monolithic device |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 6-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 6-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

recommended, since it reduces the complexity of the user interface block and the board-level JTAG driver.

Moreover, using an internal counter for address generation speeds up the initialization procedure, since the user only needs to import the data through the JTAG port.

The designer may use different methods to select among the multiple RAM blocks. Using counters along with demultiplexers is one approach to set the write enable signals. Basically, the number of RAM blocks needing initialization determines the most efficient approach. For example, if all the blocks are initialized with the same data, one enable signal is enough to activate the write procedure for all of them at the same time. Another alternative is to use different opcodes to initialize each memory block. For a small number of RAM blocks, using counters is an optimal choice. For example, a ring counter can be used to select from multiple RAM blocks. The clock driver of this counter needs to be controlled by the address generation process.

Once the addressing of one block is finished, a clock pulse is sent to the (ring) counter to select the next memory block.

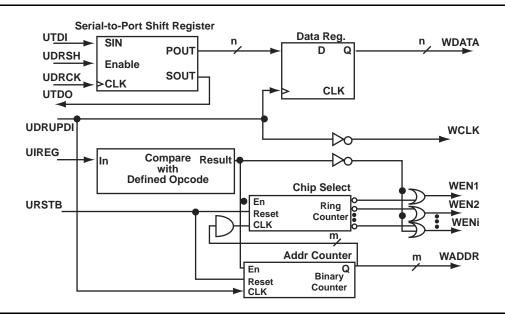

Figure 6-9 illustrates a simple block diagram of an interface block between UJTAG and RAM blocks.

#### Figure 6-9 • Block Diagram of a Sample User Interface

In the circuit shown in Figure 6-9, the shift register is enabled by the UDRSH output of the UJTAG macro. The counters and chip select outputs are controlled by the value of the TAP Instruction Register. The comparison block compares the UIREG value with the "start initialization" opcode value (defined by the user). If the result is true, the counters start to generate addresses and activate the WEN inputs of appropriate RAM blocks.

The UDRUPD output of the UJTAG macro, also shown in Figure 6-9, is used for generating the write clock (WCLK) and synchronizing the data register and address counter with WCLK. UDRUPD is HIGH when the TAP Controller is in the Data Register Update state, which is an indication of completing the loading of one data word. Once the TAP Controller goes into the Data Register Update state, the UDRUPD output of the UJTAG macro goes HIGH. Therefore, the pipeline register and the address counter place the proper data and address on the outputs of the interface block. Meanwhile, WCLK is defined as the inverted UDRUPD. This will provide enough time (equal to the UDRUPD HIGH time) for the data and address to be placed at the proper ports of the RAM block before the rising edge of WCLK. The inverter is not required if the RAM blocks are clocked at the falling edge of the write clock. An example of this is described in the "Example of RAM Initialization" section on page 166.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

```

//

addr_counter counter_1 (.Clock(data_update), .Q(wr_addr), .Aset(rst_n),

.Enable(enable));

addr_counter counter_2 (.Clock(test_clk), .Q(rd_addr), .Aset(rst_n),

.Enable( test_active));

```

endmodule

### Interface Block / UJTAG Wrapper

This example is a sample wrapper, which connects the interface block to the UJTAG and the memory blocks.

```

// WRAPPER

module top_init (TDI, TRSTB, TMS, TCK, TDO, test, test_clk, test_ out);

input TDI, TRSTB, TMS, TCK;

output TDO;

input test, test_clk;

output [3:0] test_out;

wire [7:0] IR;

wire reset, DR_shift, DR_cap, init_clk, DR_update, data_in, data_out;

wire clk out, wen, ren;

wire [3:0] word_in, word_out;

wire [1:0] write_addr, read_addr;

UJTAG UJTAG_U1 (.UIREG0(IR[0]), .UIREG1(IR[1]), .UIREG2(IR[2]), .UIREG3(IR[3]),

.UIREG4(IR[4]), .UIREG5(IR[5]), .UIREG6(IR[6]), .UIREG7(IR[7]), .URSTB(reset),

.UDRSH(DR_shift), .UDRCAP(DR_cap), .UDRCK(init_clk), .UDRUPD(DR_update),

.UT-DI(data_in), .TDI(TDI), .TMS(TMS), .TCK(TCK), .TRSTB(TRSTB), .TDO(TDO),

.UT-DO(data_out));

mem_block RAM_block (.DO(word_out), .RCLOCK(clk_out), .WCLOCK(clk_out), .DI(word_in),

.WRB(wen), .RDB(ren), .WAD-DR(write_addr), .RADDR(read_addr));

interface init_block (.IR(IR), .rst_n(reset), .data_shift(DR_shift), .clk_in(init_clk),

.data_update(DR_update), .din_ser(data_in), .dout_ser(data_out), .test(test),

.test_out(test_out), .test_clk(test_clk), .clk_out(clk_out), .wr_en(wen),

.rd_en(ren), .write_word(word_in), .read_word(word_out), .rd_addr(read_addr),

.wr_addr(write_addr));

```

endmodule

#### Address Counter

module addr\_counter (Clock, Q, Aset, Enable);

```

input Clock;

output [1:0] Q;

input Aset;

input Enable;

reg [1:0] Qaux;

always @(posedge Clock or negedge Aset)

begin

if (!Aset) Qaux <= 2'b11;

else if (Enable) Qaux <= Qaux + 1;

end

assign Q = Qaux;

endmodule

```

# Conclusion

Fusion, IGLOO, and ProASIC3 devices provide users with extremely flexible SRAM blocks for most design needs, with the ability to choose between an easy-to-use dual-port memory or a wide-word two-port memory. Used with the built-in FIFO controllers, these memory blocks also serve as highly efficient FIFOs that do not consume user gates when implemented. The SmartGen core generator provides a fast and easy way to configure these memory elements for use in designs.

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                                                                                                   | Changes                                                                                                                                                                                                                                                                                                 |     |  |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| August 2012                                                                                            | The note connected with Figure 6-3 • Supported Basic RAM Macros, regarding RAM4K9, was revised to explain that it applies only to part numbers of certain revisions and earlier (SAR 29574).                                                                                                            | 152 |  |

| July 2010                                                                                              | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                               | N/A |  |

| v1.5<br>(December 2008)                                                                                | IGLOO nano and ProASIC3 nano devices were added to Table 6-1 • Flash-Based FPGAs.                                                                                                                                                                                                                       | 150 |  |

|                                                                                                        | IGLOO nano and ProASIC3 nano devices were added to Figure 6-8 • Interfacing TAP Ports and SRAM Blocks.                                                                                                                                                                                                  | 164 |  |

| v1.4<br>(October 2008)                                                                                 | The "SRAM/FIFO Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                       | 150 |  |

|                                                                                                        | The "SRAM and FIFO Architecture" section was modified to remove "IGLOO and ProASIC3E" from the description of what the memory block includes, as this statement applies to all memory blocks.                                                                                                           | 151 |  |

|                                                                                                        | Wording in the "Clocking" section was revised to change "IGLOO and ProASIC3 devices support inversion" to "Low power flash devices support inversion." The reference to IGLOO and ProASIC3 development tools in the last paragraph of the section was changed to refer to development tools in general. | 157 |  |

|                                                                                                        | The "ESTOP and FSTOP Usage" section was updated to refer to FIFO counters in devices in general rather than only IGLOO and ProASIC3E devices.                                                                                                                                                           | 160 |  |

| v1.3<br>(August 2008)                                                                                  | The note was removed from Figure 6-7 • RAM Block with Embedded FIFO Controller and placed in the WCLK and RCLK description.                                                                                                                                                                             | 158 |  |

|                                                                                                        | The "WCLK and RCLK" description was revised.                                                                                                                                                                                                                                                            | 159 |  |

| v1.2 The following changes were made to the family descriptions in Table 6<br>(June 2008) Based FPGAs: |                                                                                                                                                                                                                                                                                                         | 150 |  |

|                                                                                                        | ProASIC3L was updated to include 1.5 V.                                                                                                                                                                                                                                                                 |     |  |

|                                                                                                        | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                                                                                          |     |  |

| v1.1<br>(March 2008)                                                                                   | The "Introduction" section was updated to include the IGLOO PLUS family.                                                                                                                                                                                                                                | 147 |  |

|                                                                                                        | The "Device Architecture" section was updated to state that 15 k gate devices do not support SRAM and FIFO.                                                                                                                                                                                             | 147 |  |

|                                                                                                        | The first note in Figure 6-1 • IGLOO and ProASIC3 Device Architecture Overview was updated to include mention of 15 k gate devices, and IGLOO PLUS was added to the second note.                                                                                                                        | 149 |  |

# I/O Architecture

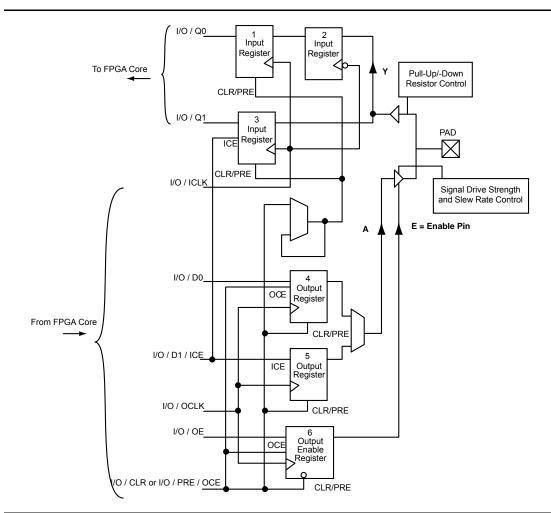

## I/O Tile

The I/O tile provides a flexible, programmable structure for implementing a large number of I/O standards. In addition, the registers available in the I/O tile can be used to support high-performance register inputs and outputs, with register enable if desired (Figure 7-2). The registers can also be used to support the JESD-79C Double Data Rate (DDR) standard within the I/O structure (see the "DDR for Microsemi's Low Power Flash Devices" section on page 271 for more information). In addition, the registers available in the I/O tile can be used to support high-performance register inputs and outputs, with register enable if desired (Figure 7-2).

As depicted in Figure 7-2, all I/O registers share one CLR port. The output register and output enable register share one CLK port.

Figure 7-2 • DDR Configured I/O Block Logical Representation

I/O Structures in IGLOO and ProASIC3 Devices

# Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout

Each I/O voltage bank has a separate ground and power plane for input and output circuits (VMV/GNDQ for input buffers and VCCI/GND for output buffers). This isolation is necessary to minimize simultaneous switching noise from the input and output (SSI and SSO). The switching noise (ground bounce and power bounce) is generated by the output buffers and transferred into input buffer circuits, and vice versa.

Since voltage bounce originates on the package inductance, the VMV and VCCI supplies have separate package pin assignments. For the same reason, GND and GNDQ also have separate pin assignments.

The VMV and VCCI pins must be shorted to each other on the board. Also, the GND and GNDQ pins must be shorted to each other on the board. This will prevent unwanted current draw from the power supply.

SSOs can cause signal integrity problems on adjacent signals that are not part of the SSO bus. Both inductive and capacitive coupling parasitics of bond wires inside packages and of traces on PCBs will transfer noise from SSO busses onto signals adjacent to those busses. Additionally, SSOs can produce ground bounce noise and VCCI dip noise. These two noise types are caused by rapidly changing currents through GND and VCCI package pin inductances during switching activities (EQ 2 and EQ 3).

Ground bounce noise voltage = L(GND) × di/dt

VCCI dip noise voltage = L(VCCI) × di/dt

EQ 3

EQ 2

Any group of four or more input pins switching on the same clock edge is considered an SSO bus. The shielding should be done both on the board and inside the package unless otherwise described.

In-package shielding can be achieved in several ways; the required shielding will vary depending on whether pins next to the SSO bus are LVTTL/LVCMOS inputs, LVTTL/LVCMOS outputs, or GTL/SSTL/HSTL/LVDS/LVPECL inputs and outputs. Board traces in the vicinity of the SSO bus have to be adequately shielded from mutual coupling and inductive noise that can be generated by the SSO bus. Also, noise generated by the SSO bus needs to be reduced inside the package.

PCBs perform an important function in feeding stable supply voltages to the IC and, at the same time, maintaining signal integrity between devices.

Key issues that need to be considered are as follows:

- · Power and ground plane design and decoupling network design

- Transmission line reflections and terminations

For extensive data per package on the SSO and PCB issues, refer to the "ProASIC3/E SSO and Pin Placement and Guidelines" chapter of the *ProASIC3 FPGA Fabric User's Guide*.

## GTL 2.5 V (Gunning Transceiver Logic 2.5 V)

This is a low power standard (JESD 8-3) for electrical signals used in CMOS circuits that allows for low electromagnetic interference at high transfer speeds. It has a voltage swing between 0.4 V and 1.2 V and typically operates at speeds of between 20 and 40 MHz. VCCI must be connected to 2.5 V. The reference voltage (VREF) is 0.8 V.

## GTL 3.3 V (Gunning Transceiver Logic 3.3 V)

This is the same as GTL 2.5 V above, except VCCI must be connected to 3.3 V.

### GTL+ (Gunning Transceiver Logic Plus)

This is an enhanced version of GTL that has defined slew rates and higher voltage levels. It requires a differential amplifier input buffer and an open-drain output buffer. Even though the output is open-drain, VCCI must be connected to either 2.5 V or 3.3 V. The reference voltage (VREF) is 1 V.

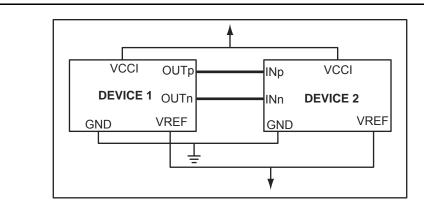

## **Differential Standards**

These standards require two I/Os per signal (called a "signal pair"). Logic values are determined by the potential difference between the lines, not with respect to ground. This is why differential drivers and receivers have much better noise immunity than single-ended standards. The differential interface standards offer higher performance and lower power consumption than their single-ended counterparts. Two I/O pins are used for each data transfer channel. Both differential standards require resistor termination.

Figure 8-8 • Differential Topology

## LVPECL (Low-Voltage Positive Emitter Coupled Logic)

LVPECL requires that one data bit be carried through two signal lines; therefore, two pins are needed per input or output. It also requires external resistor termination. The voltage swing between the two signal lines is approximately 850 mV. When the power supply is +3.3 V, it is commonly referred to as Low-Voltage PECL (LVPECL). Refer to the device datasheet for the full implementation of the LVPECL transmitter and receiver.

## LVDS (Low-Voltage Differential Signal)

LVDS is a moderate-speed differential signaling system, in which the transmitter generates two different voltages that are compared at the receiver. LVDS uses a differential driver connected to a terminated receiver through a constant-impedance transmission line. It requires that one data bit be carried through two signal lines; therefore, the user will need two pins per input or output. It also requires external resistor termination. The voltage swing between the two signal lines is approximately 350 mV.  $V_{CCI}$  is 2.5 V. Low power flash devices contain dedicated circuitry supporting a high-speed LVDS standard that has its own user specification. Refer to the device datasheet for the full implementation of the LVDS transmitter and receiver.

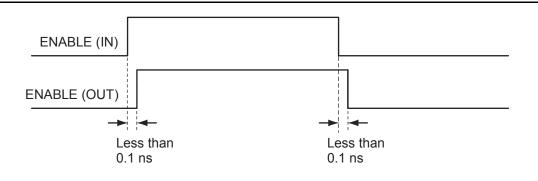

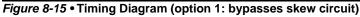

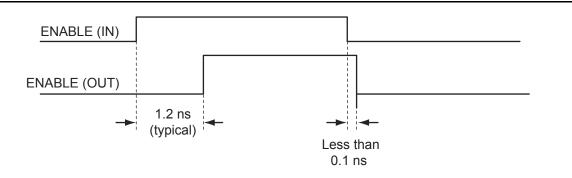

At the system level, the skew circuit can be used in applications where transmission activities on bidirectional data lines need to be coordinated. This circuit, when selected, provides a timing margin that can prevent bus contention and subsequent data loss and/or transmitter over-stress due to transmitter-to-transmitter current shorts. Figure 8-17 presents an example of the skew circuit implementation in a bidirectional communication system. Figure 8-18 on page 238 shows how bus contention is created, and Figure 8-19 on page 238 shows how it can be avoided with the skew circuit.

## **Power-Up Behavior**

Low power flash devices are power-up/-down friendly; i.e., no particular sequencing is required for power-up and power-down. This eliminates extra board components for power-up sequencing, such as a power-up sequencer.

During power-up, all I/Os are tristated, irrespective of I/O macro type (input buffers, output buffers, I/O buffers with weak pull-ups or weak pull-downs, etc.). Once I/Os become activated, they are set to the user-selected I/O macros. Refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 373 for details.

## **Drive Strength**

Low power flash devices have up to seven programmable output drive strengths. The user can select the drive strength of a particular output in the I/O Attribute Editor or can instantiate a specialized I/O macro, such as OUTBUF\_S\_12 (slew = low, out\_drive = 12 mA).

The maximum available drive strength is 24 mA per I/O. Though no I/O should be forced to source or sink more than 24 mA indefinitely, I/Os may handle a higher amount of current (refer to the device IBIS model for maximum source/sink current) during signal transition (AC current). Every device package has its own power dissipation limit; hence, power calculation must be performed accurately to determine how much current can be tolerated per I/O within that limit.

## I/O Interfacing

Low power flash devices are 5 V–input– and 5 V–output–tolerant if certain I/O standards are selected (refer to the "5 V Input and Output Tolerance" section on page 232). Along with other low-voltage I/O macros, this 5 V tolerance makes these devices suitable for many types of board component interfacing.

| Table 8-19 shows some hi | gh-level interfacing | examples using | low power flash devices. |

|--------------------------|----------------------|----------------|--------------------------|

|                          |                      |                |                          |

|                    | (            | Clock I/O       |       |              |              |                 |

|--------------------|--------------|-----------------|-------|--------------|--------------|-----------------|

| Interface          | Туре         | Frequency       | Туре  | Signals In   | Signals Out  | Data I/O        |

| GM                 | Src Sync     | 125 MHz         | LVTTL | 8            | 8            | 125 Mbps        |

| ТВІ                | Src Sync     | 125 MHz         | LVTTL | 10           | 10           | 125 Mbps        |

| XSBI               | Src Sync     | 644 MHz         | LVDS  | 16           | 16           | 644 Mbps        |

| XGMI               | Src Sync DDR | 156 MHz         | HSTL1 | 32           | 32           | 312 Mbps        |

| FlexBus 3          | Sys Sync     | 104 MHz         | LVTTL | ≤ <b>32</b>  | ≤ <b>32</b>  | ≤ 104           |

| Pos-PHY3/SPI-3     | Sys Sync     | 104             | LVTTL | 8,16,32      | 8,16,32      | $\leq$ 104 Mbps |

| FlexBus 4/SPI-4.1  | Src Sync     | 200 MHz         | HSTL1 | 16,64        | 16,64        | 200 Mbps        |

| Pos-PHY4/SPI-4.2   | Src Sync DDR | ≥ 311 MHz       | LVDS  | 16           | 16           | $\geq$ 622 Mbps |

| SFI-4.1            | Src Sync     | 622 MHz         | LVDS  | 16           | 16           | 622 Mbps        |

| CSIX L1            | Sys Sync     | $\leq$ 250 MHz  | HSTL1 | 32,64,96,128 | 32,64,96,128 | $\leq$ 250 Mbps |

| Hyper Transport    | Sys Sync DDR | $\leq$ 800 MHz  | LVDS  | 2,4,8,16     | 2,4,8,16     | $\leq$ 1.6 Gbps |

| Rapid I/O Parallel | Sys Sync DDR | 250 MHz – 1 GHz | LVDS  | 8,16         | 8,16         | ≤ 2 Gbps        |

| Star Fabric        | CDR          |                 | LVDS  | 4            | 4            | 622 Mbps        |

#### Table 8-19 • High-Level Interface Examples

Note: Sys Sync = System Synchronous Clocking, Src Sync = Source Synchronous Clocking, and CDR = Clock and Data Recovery.

I/O Structures in IGLOOe and ProASIC3E Devices

# Conclusion

IGLOOe and ProASIC3E support for multiple I/O standards minimizes board-level components and makes possible a wide variety of applications. The Microsemi Designer software, integrated with Libero SoC, presents a clear visual display of I/O assignments, allowing users to verify I/O and board-level design requirements before programming the device. The IGLOOe and ProASIC3E device I/O features and functionalities ensure board designers can produce low-cost and low power FPGA applications fulfilling the complexities of contemporary design needs.

# **Related Documents**

## **Application Notes**

Board-Level Considerations http://www.microsemi.com/soc/documents/ALL\_AC276\_AN.pdf

## **User's Guides**

ProASIC3 FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/PA3\_UG.pdf ProASIC3E FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/PA3E\_UG.pdf IGLOOe FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/IGLOOe\_UG.pdf Libero SoC User's Guide http://www.microsemi.com/soc/documents/libero\_ug.pdf IGLOO, Fusion, and ProASIC3 Macro Library Guide http://www.microsemi.com/soc/documents/pa3\_libguide\_ug.pdf SmartGen Core Reference Guide http://www.microsemi.com/soc/documents/genguide\_ug.pdf

- The I/O standard of technology-specific I/O macros cannot be changed in the I/O Attribute Editor (see Figure 9-6).

- The user MUST instantiate differential I/O macros (LVDS/LVPECL) in the design. This is the only way to use these standards in the design (IGLOO nano and ProASIC3 nano devices do not support differential inputs).

- To implement the DDR I/O function, the user must instantiate a DDR\_REG or DDR\_OUT macro. This is the only way to use a DDR macro in the design.

Figure 9-6 • Assigning a Different I/O Standard to the Generic I/O Macro

### Performing Place-and-Route on the Design

The netlist created by the synthesis tool should now be imported into Designer and compiled. During Compile, the user can specify the I/O placement and attributes by importing the PDC file. The user can also specify the I/O placement and attributes using ChipPlanner and the I/O Attribute Editor under MVN.

### Defining I/O Assignments in the PDC File

A PDC file is a Tcl script file specifying physical constraints. This file can be imported to and exported from Designer.

Table 9-3 shows I/O assignment constraints supported in the PDC file.

| Command Action    |                                                                                                                            | Example Comment                                                                      |                                                                  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| I/O Banks Setting | I/O Banks Setting Constraints                                                                                              |                                                                                      |                                                                  |  |  |  |  |

| set_iobank        | Sets the I/O supply voltage, $V_{CCI}$ , and the input reference voltage, $V_{REF}$ , for the specified I/O bank.          | [-vcci vcci_voltage]<br>[-vref vref_voltage]                                         | Must use in case of mixed I/O voltage (V <sub>CCI</sub> ) design |  |  |  |  |

| set_vref          | Assigns a V <sub>REF</sub> pin to a bank.                                                                                  | set_vref -bank [bankname]<br>[pinnum]<br>set_vref -bank Bank0<br>685 704 723 742 761 | Must use if voltage-<br>referenced I/Os are used                 |  |  |  |  |

| set_vref_defaults | Sets the default $V_{REF}$ pins for the specified bank. This command is ignored if the bank does not need a $V_{REF}$ pin. | <pre>set_vref_defaults bank2</pre>                                                   |                                                                  |  |  |  |  |

Table 9-3 • PDC I/O Constraints

*Note: Refer to the* Libero SoC User's Guide for detailed rules on PDC naming and syntax conventions.

I/O Software Control in Low Power Flash Devices

### I/O Function

Figure 9-8 shows an example of the I/O Function table included in the I/O bank report:

### Figure 9-8 • I/O Function Table

This table lists the number of input I/Os, output I/Os, bidirectional I/Os, and differential input and output I/O pairs that use I/O and DDR registers.

Note: IGLOO nano and ProASIC3 nano devices do not support differential inputs.

Certain rules must be met to implement registered and DDR I/O functions (refer to the I/O Structures section of the handbook for the device you are using and the "DDR" section on page 256).

### I/O Technology

The I/O Technology table (shown in Figure 9-9) gives the values of VCCI and VREF (reference voltage) for all the I/O standards used in the design. The user should assign these voltages appropriately.

Figure 9-9 • I/O Technology Table

DDR for Microsemi's Low Power Flash Devices

# **DDR Support in Flash-Based Devices**

The flash FPGAs listed in Table 10-1 support the DDR feature and the functions described in this document.

#### Table 10-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                                    |  |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |  |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |  |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |  |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |  |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |  |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |  |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |  |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |  |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 10-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 10-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

## **Related Documents**

Below is a list of related documents, their location on the Microsemi SoC Products Group website, and a brief summary of each document.

## **Application Notes**

Programming Antifuse Devices http://www.microsemi.com/soc/documents/AntifuseProgram\_AN.pdf Implementation of Security in Actel's ProASIC and ProASIC<sup>PLUS</sup> Flash-Based FPGAs http://www.microsemi.com/soc/documents/Flash\_Security\_AN.pdf

## **User's Guides**

### FlashPro Programmers

FlashPro4,<sup>1</sup> FlashPro3, FlashPro Lite, and FlashPro<sup>2</sup> http://www.microsemi.com/soc/products/hardware/program\_debug/flashpro/default.aspx *FlashPro User's Guide* http://www.microsemi.com/soc/documents/FlashPro\_UG.pdf The FlashPro User's Guide includes hardware and software setup, self-test instructions, use instructions, and a troubleshooting / error message guide.

### Silicon Sculptor 3 and Silicon Sculptor II

http://www.microsemi.com/soc/products/hardware/program\_debug/ss/default.aspx

## **Other Documents**

http://www.microsemi.com/soc/products/solutions/security/default.aspx#flashlock The security resource center describes security in Microsemi Flash FPGAs. *Quality and Reliability Guide* http://www.microsemi.com/soc/documents/RelGuide.pdf *Programming and Functional Failure Guidelines* http://www.microsemi.com/soc/documents/FA\_Policies\_Guidelines\_5-06-00002.pdf

<sup>1.</sup> FlashPro4 replaced FlashPro3 in Q1 2010.

<sup>2.</sup> FlashPro is no longer available.

## **Brownout Voltage**

Brownout is a condition in which the voltage supplies are lower than normal, causing the device to malfunction as a result of insufficient power. In general, Microsemi does not guarantee the functionality of the design inside the flash FPGA if voltage supplies are below their minimum recommended operating condition. Microsemi has performed measurements to characterize the brownout levels of FPGA power supplies. Refer to Table 18-3 for device-specific brownout deactivation levels. For the purpose of characterization, a direct path from the device input to output is monitored while voltage supplies are lowered gradually. The brownout point is defined as the voltage level at which the output stops following the input. Characterization tests performed on several IGLOO, ProASIC3L, and ProASIC3 devices in typical operating conditions showed the brownout voltage levels to be within the specification.

During device power-down, the device I/Os become tristated once the first supply in the power-down sequence drops below its brownout deactivation voltage.

#### Table 18-3 • Brownout Deactivation Levels for VCC and VCCI

| Devices                                                                                                   | VCC Brownout<br>Deactivation Level (V) | VCCI Brownout<br>Deactivation Level (V) |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|

| ProASIC3, ProASIC3 nano, IGLOO, IGLOO nano,<br>IGLOO PLUS and ProASIC3L devices running at<br>VCC = 1.5 V | 0.75 V ± 0.25 V                        | 0.8 V ± 0.3 V                           |

| IGLOO, IGLOO nano, IGLOO PLUS, and<br>ProASIC3L devices running at VCC = 1.2 V                            | 0.75 V ± 0.2 V                         | 0.8 V ± 0.15 V                          |

## PLL Behavior at Brownout Condition

When PLL power supply voltage and/or V<sub>CC</sub> levels drop below the V<sub>CC</sub> brownout levels mentioned above for 1.5 V and 1.2 V devices, the PLL output lock signal goes LOW and/or the output clock is lost. The following sections explain PLL behavior during and after the brownout condition.

### VCCPLL and VCC Tied Together

In this condition, both VCC and VCCPLL drop below the 0.75 V ( $\pm$  0.25 V or  $\pm$  0.2 V) brownout level. During the brownout recovery, once VCCPLL and VCC reach the activation point (0.85  $\pm$  0.25 V or  $\pm$  0.2 V) again, the PLL output lock signal may still remain LOW with the PLL output clock signal toggling. If this condition occurs, there are two ways to recover the PLL output lock signal:

- 1. Cycle the power supplies of the PLL (power off and on) by using the PLL POWERDOWN signal.

- 2. Turn off the input reference clock to the PLL and then turn it back on.

#### Only VCCPLL Is at Brownout

In this case, only VCCPLL drops below the 0.75 V ( $\pm$  0.25 V or  $\pm$  0.2 V) brownout level and the VCC supply remains at nominal recommended operating voltage (1.5 V  $\pm$  0.075 V for 1.5 V devices and 1.2 V  $\pm$  0.06 V for 1.2 V devices). In this condition, the PLL behavior after brownout recovery is similar to initial power-up condition, and the PLL will regain lock automatically after VCCPLL is ramped up above the activation level (0.85  $\pm$  0.25 V or  $\pm$  0.2 V). No intervention is necessary in this case.

#### Only VCC Is at Brownout

In this condition, VCC drops below the 0.75 V ( $\pm$  0.25 V or  $\pm$  0.2 V) brownout level and VCCPLL remains at nominal recommended operating voltage (1.5 V  $\pm$  0.075 V for 1.5 V devices and 1.2 V  $\pm$  0.06 V for 1.2 V devices). During the brownout recovery, once VCC reaches the activation point again (0.85  $\pm$  0.25 V or  $\pm$  0.2 V), the PLL output lock signal may still remain LOW with the PLL output clock signal toggling. If this condition occurs, there are two ways to recover the PLL output lock signal:

- 1. Cycle the power supplies of the PLL (power off and on) by using the PLL POWERDOWN signal.

- 2. Turn off the input reference clock to the PLL and then turn it back on.

It is important to note that Microsemi recommends using a monotonic power supply or voltage regulator to ensure proper power-up behavior.