Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | ·                                                                          |

| Total RAM Bits                 | 516096                                                                     |

| Number of I/O                  | 620                                                                        |

| Number of Gates                | 300000                                                                     |

| Voltage - Supply               | 1.14V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                            |

| Package / Case                 | 896-BGA                                                                    |

| Supplier Device Package        | 896-FBGA (31x31)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pe3000l-fgg896 |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| /О Туре      | Beginning of I/O Name | Notes                                                    |

|--------------|-----------------------|----------------------------------------------------------|

| Single-Ended | GAAO/IOuxwByVz        | Only one of the I/Os can be directly connected to        |

|              | GAA1/IOuxwByVz        | quadrant global at a time                                |

|              | GAA2/IOuxwByVz        |                                                          |

|              | GABO/IOuxwByVz        | Only one of the I/Os can be directly connected to        |

|              | GAB1/IOuxwByVz        | quadrant global at a time.                               |

|              | GAB2/IOuxwByVz        |                                                          |

|              | GAC0/IOuxwByVz        | Only one of the I/Os can be directly connected to        |

|              | GAC1/IOuxwByVz        | quadrant global at a time.                               |

|              | GAC2/IOuxwByVz        |                                                          |

|              | GBAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GBA1/IOuxwByVz        | at a time.                                               |

|              | GBA2/IOuxwByVz        |                                                          |

|              | GBBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GBB1/IOuxwByVz        | at a time.                                               |

|              | GBB2/IOuxwByVz        |                                                          |

|              | GBC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GBC1/IOuxwByVz        | at a time.                                               |

|              | GBC2/IOuxwByVz        |                                                          |

|              | GDAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GDA1/IOuxwByVz        | at a time.                                               |

|              | GDA2/IOuxwByVz        |                                                          |

|              | GDBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GDB1/IOuxwByVz        | at a time.                                               |

|              | GDB2/IOuxwByVz        |                                                          |

|              | GDC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GDC1/IOuxwByVz        | at a time.                                               |

|              | GDC2/IOuxwByVz        |                                                          |

|              | GEAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GEA1/IOuxwByVz        | at a time.                                               |

|              | GEA2/IOuxwByVz        |                                                          |

|              | GEBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GEB1/IOuxwByVz        | at a time.                                               |

|              | GEB2/IOuxwByVz        |                                                          |

|              | GEC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GEC1/IOuxwByVz        | at a time.                                               |

|              | GEC2/IOuxwByVz        |                                                          |

#### Table 3-3 • Quadrant Global Pin Name

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

# **Clock Aggregation Architecture**

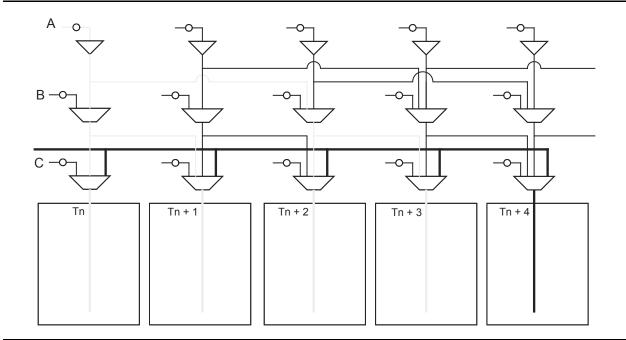

This clock aggregation feature allows a balanced clock tree, which improves clock skew. The physical regions for clock aggregation are defined from left to right and shift by one spine. For chip global networks, there are three types of clock aggregation available, as shown in Figure 3-10:

- Long lines that can drive up to four adjacent spines (A)

- Long lines that can drive up to two adjacent spines (B)

- Long lines that can drive one spine (C)

There are three types of clock aggregation available for the quadrant spines, as shown in Figure 3-10:

- I/Os or local resources that can drive up to four adjacent spines

- I/Os or local resources that can drive up to two adjacent spines

- I/Os or local resources that can drive one spine

As an example, A3PE600 and AFS600 devices have twelve spine locations: T1, T2, T3, T4, T5, T6, B1, B2, B3, B4, B5, and B6. Table 3-7 shows the clock aggregation you can have in A3PE600 and AFS600.

Figure 3-10 • Four Spines Aggregation

| Clock Aggregation | Spine                                                                |

|-------------------|----------------------------------------------------------------------|

| 1 spine           | T1, T2, T3, T4, T5, T6, B1, B2, B3, B4, B5, B6                       |

| 2 spines          | T1:T2, T2:T3, T3:T4, T4:T5, T5:T6, B1:B2, B2:B3, B3:B4, B4:B5, B5:B6 |

| 4 spines          | B1:B4, B2:B5, B3:B6, T1:T4, T2:T5, T3:T6                             |

The clock aggregation for the quadrant spines can cross over from the left to right quadrant, but not from top to bottom. The quadrant spine assignment T1:T4 is legal, but the quadrant spine assignment T1:B1 is not legal. Note that this clock aggregation is hardwired. You can always assign signals to spine T1 and B2 by instantiating a buffer, but this may add skew in the signal.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# IGLOOe and ProASIC3E CCC Locations

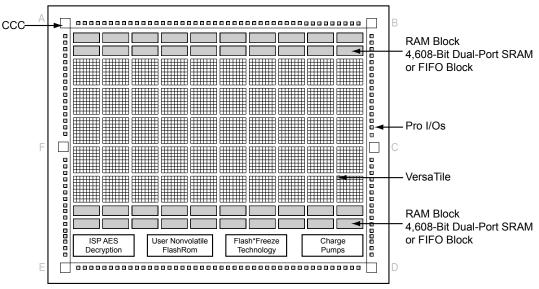

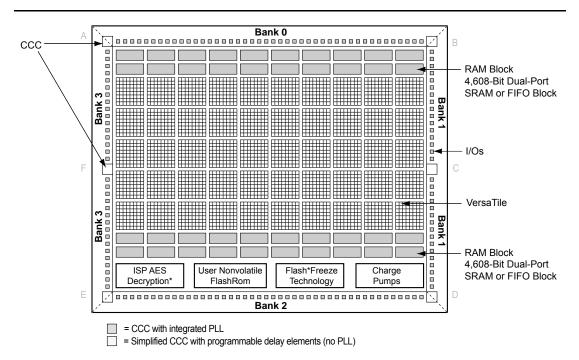

IGLOOe and ProASIC3E devices have six CCCs—one in each of the four corners and one each in the middle of the east and west sides of the device (Figure 4-15).

All six CCCs are integrated with PLLs, except in PQFP-208 package devices. PQFP-208 package devices also have six CCCs, of which two include PLLs and four are simplified CCCs. The CCCs with PLLs are implemented in the middle of the east and west sides of the device (middle right and middle left). The simplified CCCs without PLLs are located in the four corners of the device (Figure 4-16).

Figure 4-16 • CCC Locations in ProASIC3E Family Devices (PQFP-208 package)

```

wire VCC, GND;

VCC VCC_1_net(.Y(VCC));

GND GND_1_net(.Y(GND));

PLL Core(.CLKA(CLKA), .EXTFB(GND), .POWERDOWN(POWERDOWN),

.GLA(GLA), .LOCK(LOCK), .GLB(), .YB(), .GLC(), .YC(),

.OADIV0(GND), .OADIV1(GND), .OADIV2(GND), .OADIV3(GND),

.OADIV4(GND), .OAMUX0(GND), .OAMUX1(GND), .OAMUX2(VCC),

.DLYGLA0(GND), .DLYGLA1(GND), .DLYGLA2(GND), .DLYGLA3(GND)

, .DLYGLA4(GND), .OBDIV0(GND), .OBDIV1(GND), .OBDIV2(GND),

.OBDIV3(GND), .OBDIV4(GND), .OBMUX0(GND), .OBMUX1(GND),

.OBMUX2(GND), .DLYYB0(GND), .DLYYB1(GND), .DLYYB2(GND),

.DLYYB3(GND), .DLYYB4(GND), .DLYGLB0(GND), .DLYGLB1(GND),

.DLYGLB2(GND), .DLYGLB3(GND), .DLYGLB4(GND), .OCDIV0(GND),

.OCDIV1(GND), .OCDIV2(GND), .OCDIV3(GND), .OCDIV4(GND),

.OCMUX0(GND), .OCMUX1(GND), .OCMUX2(GND), .DLYYC0(GND),

.DLYYC1(GND), .DLYYC2(GND), .DLYYC3(GND), .DLYYC4(GND),

.DLYGLC0(GND), .DLYGLC1(GND), .DLYGLC2(GND), .DLYGLC3(GND)

, .DLYGLC4(GND), .FINDIV0(VCC), .FINDIV1(GND), .FINDIV2(

VCC), .FINDIV3(GND), .FINDIV4(GND), .FINDIV5(GND),

.FINDIV6(GND), .FBDIV0(VCC), .FBDIV1(GND), .FBDIV2(VCC),

.FBDIV3(GND), .FBDIV4(GND), .FBDIV5(GND), .FBDIV6(GND),

.FBDLY0(GND), .FBDLY1(GND), .FBDLY2(GND), .FBDLY3(GND),

.FBDLY4(GND), .FBSEL0(VCC), .FBSEL1(GND), .XDLYSEL(GND),

.VCOSEL0(GND), .VCOSEL1(GND), .VCOSEL2(GND));

defparam Core.VCOFREQUENCY = 33.000;

endmodule

```

The "PLL Configuration Bits Description" section on page 106 provides descriptions of the PLL configuration bits for completeness. The configuration bits are shown as busses only for purposes of illustration. They will actually be broken up into individual pins in compilation libraries and all simulation models. For example, the FBSEL[1:0] bus will actually appear as pins FBSEL1 and FBSEL0. The setting of these select lines for the static PLL configuration is performed by the software and is completely transparent to the user.

# Microsemi

FlashROM in Microsemi's Low Power Flash Devices

# **FlashROM Design Flow**

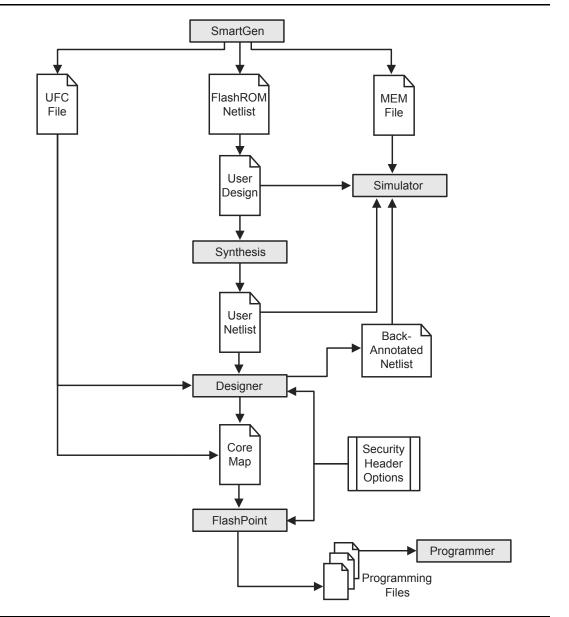

The Microsemi Libero System-on-Chip (SoC) software has extensive FlashROM support, including FlashROM generation, instantiation, simulation, and programming. Figure 5-9 shows the user flow diagram. In the design flow, there are three main steps:

- 1. FlashROM generation and instantiation in the design

- 2. Simulation of FlashROM design

- 3. Programming file generation for FlashROM design

Figure 5-9 • FlashROM Design Flow

FlashROM in Microsemi's Low Power Flash Devices

Figure 5-12 shows the programming file generator, which enables different STAPL file generation methods. When you select **Program FlashROM** and choose the UFC file, the FlashROM Settings window appears, as shown in Figure 5-13. In this window, you can select the FlashROM page you want to program and the data value for the configured regions. This enables you to use a different page for different programming files.

*Figure 5-12* • Programming File Generator

#### Figure 5-13 • Setting FlashROM during Programming File Generation

The programming hardware and software can load the FlashROM with the appropriate STAPL file. Programming software handles the single STAPL file that contains multiple FlashROM contents for multiple devices, and programs the FlashROM in sequential order (e.g., for device serialization). This feature is supported in the programming software. After programming with the STAPL file, you can run DEVICE\_INFO to check the FlashROM content.

# Microsemi

FlashROM in Microsemi's Low Power Flash Devices

# Conclusion

The Fusion, IGLOO, and ProASIC3 families are the only FPGAs that offer on-chip FlashROM support. This document presents information on the FlashROM architecture, possible applications, programming, access through the JTAG and UJTAG interface, and integration into your design. In addition, the Libero tool set enables easy creation and modification of the FlashROM content.

The nonvolatile FlashROM block in the FPGA can be customized, enabling multiple applications.

Additionally, the security offered by the low power flash devices keeps both the contents of FlashROM and the FPGA design safe from system over-builders, system cloners, and IP thieves.

# **Related Documents**

### **User's Guides**

FlashPro User's Guide http://www.microsemi.com/documents/FlashPro\_UG.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                   | Page     |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                 | N/A      |  |  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 5-1 • Flash-Based FPGAs.                                                                                                                                                         |          |  |  |

| v1.3<br>(October 2008)  | ber 2008) The "FlashROM Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                |          |  |  |

|                         | Figure 5-2 • Fusion Device Architecture Overview (AFS600) was replaced.<br>Figure 5-5 • Programming FlashROM Using AES was revised to change "Fusion" to<br>"Flash Device."                                                               | 135, 137 |  |  |

|                         | The <i>FlashPoint User's Guide</i> was removed from the "User's Guides" section, as its content is now part of the <i>FlashPro User's Guide</i> .                                                                                         | 146      |  |  |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 5-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul> | 134      |  |  |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                         | N/A      |  |  |

|                    | Maximum Performance |                                                             |                                            |

|--------------------|---------------------|-------------------------------------------------------------|--------------------------------------------|

| Specification      | ProASIC3E           | IGLOOe V2 or V5<br>Devices, 1.5 V DC Core<br>Supply Voltage | IGLOOe V2, 1.2 V DC<br>Core Supply Voltage |

| LVTTL/LVCMOS 3.3 V | 200 MHz             | 180 MHz                                                     | TBD                                        |

| LVCMOS 2.5 V       | 250 MHz             | 230 MHz                                                     | TBD                                        |

| LVCMOS 1.8 V       | 200 MHz             | 180 MHz                                                     | TBD                                        |

| LVCMOS 1.5 V       | 130 MHz             | 120 MHz                                                     | TBD                                        |

| PCI                | 200 MHz             | 180 MHz                                                     | TBD                                        |

| PCI-X              | 200 MHz             | 180 MHz                                                     | TBD                                        |

| HSTL-I             | 300 MHz             | 275 MHz                                                     | TBD                                        |

| HSTL-II            | 300 MHz             | 275 MHz                                                     | TBD                                        |

| SSTL2-I            | 300 MHz             | 275 MHz                                                     | TBD                                        |

| SSTL2-II           | 300 MHz             | 275 MHz                                                     | TBD                                        |

| SSTL3-I            | 300 MHz             | 275 MHz                                                     | TBD                                        |

| SSTL3-II           | 300 MHz             | 275 MHz                                                     | TBD                                        |

| GTL+ 3.3 V         | 300 MHz             | 275 MHz                                                     | TBD                                        |

| GTL+ 2.5 V         | 300 MHz             | 275 MHz                                                     | TBD                                        |

| GTL 3.3 V          | 300 MHz             | 275 MHz                                                     | TBD                                        |

| GTL 2.5 V          | 300 MHz             | 275 MHz                                                     | TBD                                        |

| LVDS               | 350 MHz             | 300 MHz                                                     | TBD                                        |

| M-LVDS             | 200 MHz             | 180 MHz                                                     | TBD                                        |

| B LVDS             | 200 MHz             | 180 MHz                                                     | TBD                                        |

| LVPECL             | 350 MHz             | 300 MHz                                                     | TBD                                        |

#### Table 8-7 • Maximum I/O Frequency for Single-Ended and Differential I/Os in All Banks in ProASIC3E Devices (maximum drive strength and high slew selected)

# List of Changes

| Date                    | Changes                                                                                                                                                                                                                                                                                                                          | Page     |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| August 2012             | Figure 8-1 • DDR Configured I/O Block Logical Representation and Figure 8-3 • DDR Configured I/O Block Logical Representation were revised to indicate that resets on registers 1, 3, 4, and 5 are active high rather than active low. The title of the figures was revised from "I/O Block Logical Representation" (SAR 40685). | 213, 220 |

|                         | AGLE1500 was removed from Table 8-2 • Supported I/O Standards because it is not a valid offering. LVCMOS 1.2 was added to the single-ended standards. LVCMOS 1.2 was added to Table 8-3 • VCCI Voltages and Compatible IGLOOe and ProASIC3E Standards (SAR 33207).                                                               | 215, 217 |

|                         | Lack of a heading for the "User I/O Naming Convention" section made the information difficult to locate. A heading now introduces the user I/O naming conventions (SAR 38059).                                                                                                                                                   | 245      |

|                         | Figure 8-5 • Simplified I/O Buffer Circuitry and Table 8-8 • Programmable I/O Features (user control via I/O Attribute Editor) were modified to indicate that programmable input delay control is applicable only to ProASIC3E, IGLOOe, ProASIC3EL, and RT ProASIC3 devices (SAR 39666).                                         | 222, 227 |

|                         | The hyperlink for the <i>Board-Level Considerations</i> application note was corrected (SAR 36663).                                                                                                                                                                                                                              | 246, 248 |

| June 2011               | Figure 8-1 • DDR Configured I/O Block Logical Representation and Figure 8-3 • DDR Configured I/O Block Logical Representation were revised so that the I/O_CLR and I/O_OCLK nets are no longer joined in front of Input Register 3 but instead on the branch of the CLR/PRE signal (SAR 26052).                                  | 213, 220 |

|                         | The "Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E" section was revised.<br>Formerly it stated, "3.3 V PCI and 3.3 V PCI-X are 5 V–tolerant." This sentence<br>now reads, "3.3 V PCI and 3.3 V PCI-X can be configured to be 5 V–tolerant" (SAR<br>20983).                                                                          | 215      |

|                         | Table 8-5 • Legal IGLOOe and ProASIC3E I/O Usage Matrix within the Same Bank was revised as follows (SAR 22467):                                                                                                                                                                                                                 | 217      |

|                         | The combination of 3.3 V I/O bank voltage with 1.50 V minibank voltage and LVDS, B-LVDS, M-LVDS, and DDR was made an illegal combination (now gray instead of white).                                                                                                                                                            |          |

|                         | The combination of 2.5 V I/O bank voltage with no minibank voltage and LVDS, B-LVDS, M-LVDS, and DDR was made a valid combination (now white instead of gray).                                                                                                                                                                   |          |

|                         | The following sentence was removed from the "LVCMOS (Low-Voltage CMOS)" section (SAR 22634): "All these versions use a 3.3 V-tolerant CMOS input buffer and a push-pull output buffer."                                                                                                                                          | 223      |

|                         | The "Electrostatic Discharge Protection" section was revised to remove references to tolerances (refer to the <i>Reliability Report</i> for tolerances). The Machine Model (MM) is not supported and was deleted from this section (SAR 24385).                                                                                  | 231      |

|                         | The "I/O Interfacing" section was revised to state that low power flash devices are 5 V–input– and 5 V–output–tolerant if certain I/O standards are selected, removing "without adding any extra circuitry," which was incorrect (SAR 21404).                                                                                    | 247      |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                        | N/A      |

| v1.4<br>(December 2008) | The terminology in the "Low Power Flash Device I/O Support" section was revised.                                                                                                                                                                                                                                                 | 214      |

The following table lists critical changes that were made in each revision of the document.

# Software-Controlled I/O Attributes

Users may modify these programmable I/O attributes using the I/O Attribute Editor. Modifying an I/O attribute may result in a change of state in Designer. Table 9-2 details which steps have to be re-run as a function of modified I/O attribute.

|                           | Designer States <sup>1</sup> |        |      |        |       |

|---------------------------|------------------------------|--------|------|--------|-------|

| I/O Attribute             | Compile                      | Layout | Fuse | Timing | Power |

| Slew Control <sup>2</sup> | No                           | No     | Yes  | Yes    | Yes   |

| Output Drive (mA)         | No                           | No     | Yes  | Yes    | Yes   |

| Skew Control              | No                           | No     | Yes  | Yes    | Yes   |

| Resistor Pull             | No                           | No     | Yes  | Yes    | Yes   |

| Input Delay               | No                           | No     | Yes  | Yes    | Yes   |

| Schmitt Trigger           | No                           | No     | Yes  | Yes    | Yes   |

| OUT_LOAD                  | No                           | No     | No   | Yes    | Yes   |

| COMBINE_REGISTER          | Yes                          | Yes    | N/A  | N/A    | N/A   |

Table 9-2 • Designer State (resulting from I/O attribute modification)

Notes:

1. No = Remains the same, Yes = Re-run the step, N/A = Not applicable

2. Skew control does not apply to IGLOO nano, IGLOO PLUS, and ProASIC3 nano devices.

3. Programmable input delay is applicable only for ProASIC3E, ProASIC3EL, RT ProASIC3, and IGLOOe devices.

# **Compiling the Design**

During Compile, a PDC I/O constraint file can be imported along with the netlist file. If only the netlist file is compiled, certain I/O assignments need to be completed before proceeding to Layout. All constraints that can be entered in PDC can also be entered using ChipPlanner, I/O Attribute Editor, and PinEditor.

There are certain rules that must be followed in implementing I/O register combining and the I/O DDR macro (refer to the I/O Registers section of the handbook for the device that you are using and the "DDR" section on page 256 for details). Provided these rules are met, the user can enable or disable I/O register combining by using the PDC command set\_io portname -register yes |no in the I/O Attribute Editor or selecting a check box in the Compile Options dialog box (see Figure 9-7). The Compile Options dialog box appears when the design is compiled for the first time. It can also be accessed by choosing **Options** > **Compile** during successive runs. I/O register combining is off by default. The PDC command overrides the setting in the Compile Options dialog box.

Figure 9-7 • Setting Register Combining During Compile

### Understanding the Compile Report

The I/O bank report is generated during Compile and displayed in the log window. This report lists the I/O assignments necessary before Layout can proceed.

When Designer is started, the I/O Bank Assigner tool is run automatically if the Layout command is executed. The I/O Bank Assigner takes care of the necessary I/O assignments. However, these assignments can also be made manually with MVN or by importing the PDC file. Refer to the "Assigning Technologies and VREF to I/O Banks" section on page 264 for further description.

The I/O bank report can also be extracted from Designer by choosing **Tools** > **Report** and setting the Report Type to **IOBank**.

This report has the following tables: I/O Function, I/O Technology, I/O Bank Resource Usage, and I/O Voltage Usage. This report is useful if the user wants to do I/O assignments manually.

I/O Software Control in Low Power Flash Devices

those banks, the user does not need to assign the same VCCI voltage to another bank. The user needs to assign the other three VCCI voltages to three more banks.

# Assigning Technologies and VREF to I/O Banks

Low power flash devices offer a wide variety of I/O standards, including voltage-referenced standards. Before proceeding to Layout, each bank must have the required VCCI voltage assigned for the corresponding I/O technologies used for that bank. The voltage-referenced standards require the use of a reference voltage (VREF). This assignment can be done manually or automatically. The following sections describe this in detail.

## Manually Assigning Technologies to I/O Banks

The user can import the PDC at this point and resolve this requirement. The PDC command is

set\_iobank [bank name] -vcci [vcci value]

Another method is to use the I/O Bank Settings dialog box (**MVN** > **Edit** > **I/O Bank Settings**) to set up the  $V_{CCI}$  voltage for the bank (Figure 9-12).

Figure 9-12 • Setting VCCI for a Bank

# Microsemi

DDR for Microsemi's Low Power Flash Devices

# **DDR Support in Flash-Based Devices**

The flash FPGAs listed in Table 10-1 support the DDR feature and the functions described in this document.

#### Table 10-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 10-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 10-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

# 11 – Programming Flash Devices

# Introduction

This document provides an overview of the various programming options available for the Microsemi flash families. The electronic version of this document includes active links to all programming resources, which are available at http://www.microsemi.com/soc/products/hardware/default.aspx. For Microsemi antifuse devices, refer to the *Programming Antifuse Devices* document.

# **Summary of Programming Support**

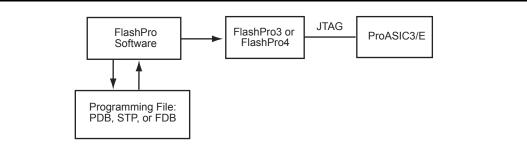

FlashPro4 and FlashPro3 are high-performance in-system programming (ISP) tools targeted at the latest generation of low power flash devices offered by the SmartFusion,<sup>®</sup> Fusion, IGLOO,<sup>®</sup> and ProASIC<sup>®</sup>3 families, including ARM-enabled devices. FlashPro4 and FlashPro3 offer extremely high performance through the use of USB 2.0, are high-speed compliant for full use of the 480 Mbps bandwidth, and can program ProASIC3 devices in under 30 seconds. Powered exclusively via USB, FlashPro4 and FlashPro3 provide a VPUMP voltage of 3.3 V for programming these devices.

FlashPro4 replaced FlashPro3 in 2010. FlashPro4 supports SmartFusion, Fusion, ProASIC3, and IGLOO devices as well as future generation flash devices. FlashPro4 also adds 1.2 V programming for IGLOO nano V2 devices. FlashPro4 is compatible with FlashPro3; however it adds a programming mode (PROG\_MODE) signal to the previously unused pin 4 of the JTAG connector. The PROG\_MODE goes high during programming and can be used to turn on a 1.5 V external supply for those devices that require 1.5 V for programming. If both FlashPro3 and FlashPro4 programmers are used for programming the same boards, pin 4 of the JTAG connector must not be connected to anything on the board because FlashPro4 uses pin 4 for PROG\_MODE.

Figure 11-1 • FlashPro Programming Setup

# **Related Documents**

Below is a list of related documents, their location on the Microsemi SoC Products Group website, and a brief summary of each document.

# **Application Notes**

Programming Antifuse Devices http://www.microsemi.com/soc/documents/AntifuseProgram\_AN.pdf Implementation of Security in Actel's ProASIC and ProASIC<sup>PLUS</sup> Flash-Based FPGAs http://www.microsemi.com/soc/documents/Flash\_Security\_AN.pdf

# **User's Guides**

### FlashPro Programmers

FlashPro4,<sup>1</sup> FlashPro3, FlashPro Lite, and FlashPro<sup>2</sup> http://www.microsemi.com/soc/products/hardware/program\_debug/flashpro/default.aspx *FlashPro User's Guide* http://www.microsemi.com/soc/documents/FlashPro\_UG.pdf The FlashPro User's Guide includes hardware and software setup, self-test instructions, use instructions, and a troubleshooting / error message guide.

#### Silicon Sculptor 3 and Silicon Sculptor II

http://www.microsemi.com/soc/products/hardware/program\_debug/ss/default.aspx

# **Other Documents**

http://www.microsemi.com/soc/products/solutions/security/default.aspx#flashlock The security resource center describes security in Microsemi Flash FPGAs. *Quality and Reliability Guide* http://www.microsemi.com/soc/documents/RelGuide.pdf *Programming and Functional Failure Guidelines* http://www.microsemi.com/soc/documents/FA\_Policies\_Guidelines\_5-06-00002.pdf

<sup>1.</sup> FlashPro4 replaced FlashPro3 in Q1 2010.

<sup>2.</sup> FlashPro is no longer available.

ProASIC3L FPGA Fabric User's Guide

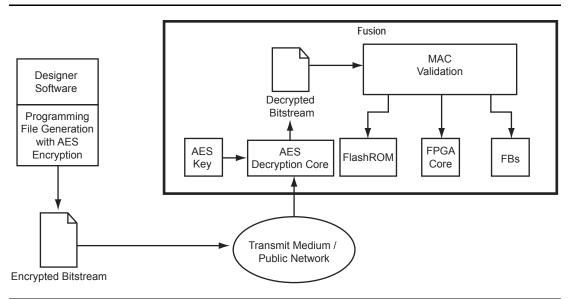

Figure 12-5 • Example Application Scenario Using AES in Fusion Devices

### FlashLock

#### Additional Options for IGLOO and ProASIC3 Devices

The user also has the option of prohibiting Write operations to the FPGA array but allowing Verify operations on the FPGA array and/or Read operations on the FlashROM without the use of the FlashLock Pass Key. This option provides the user the freedom of verifying the FPGA array and/or reading the FlashROM contents after the device is programmed, without having to provide the FlashLock Pass Key. The user can incorporate AES encryption on the programming files to better enhance the level of security used.

## **Permanent Security Setting Options**

In applications where a permanent lock is not desired, yet the security settings should not be modifiable, IGLOO and ProASIC3 devices can accommodate this requirement.

This application is particularly useful in cases where a device is located at a remote location and must be reprogrammed with a design or data update. Refer to the "Application 3: Nontrusted Environment—Field Updates/Upgrades" section on page 310 for further discussion and examples of how this can be achieved.

The user must be careful when considering the Permanent FlashLock or Permanent Security Settings option. Once the design is programmed with the permanent settings, it is not possible to reconfigure the security settings already employed on the device. Therefore, exercise careful consideration before programming permanent settings.

#### Permanent FlashLock

The purpose of the permanent lock feature is to provide the benefits of the highest level of security to IGLOO and ProASIC3 devices. If selected, the permanent FlashLock feature will create a permanent barrier, preventing any access to the contents of the device. This is achieved by permanently disabling Write and Verify access to the array, and Write and Read access to the FlashROM. After permanently locking the device, it has been effectively rendered one-time-programmable. This feature is useful if the intended applications do not require design or system updates to the device.

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

# **Circuit Verification**

The power switching circuit recommended above is implemented on Microsemi's lcicle board (Figure 14-2). On the lcicle board, VJTAGENB is used to control the N-Channel Digital FET; however, this circuit was modified to use TRST instead of VJTAGENB in this application. There are three important aspects of this circuit that were verified:

- 1. The rise on VCC from 1.2 V to 1.5 V when TRST is HIGH

- 2. VCC rises to 1.5 V before programming begins.

- 3. VCC switches from 1.5 V to 1.2 V when TRST is LOW.

### **Verification Steps**

1. The rise on VCC from 1.2 V to 1.5 V when TRST is HIGH.

#### Figure 14-2 • Core Voltage on the IGLOO AGL125-QNG132 Device

In the oscilloscope plots (Figure 14-2), the TRST from FlashPro3 and the VCC core voltage of the IGLOO device are labeled. This plot shows the rise characteristic of the TRST signal from FlashPro3. Once the TRST signal is asserted HIGH, the LTC3025 shown in Figure 14-1 on page 343 senses the increase in voltage and changes the output from 1.2 V to 1.5 V. It takes the circuit approximately 100  $\mu$ s to respond to TRST and change the voltage to 1.5 V on the VCC core.

# **Boundary Scan Support in Low Power Devices**

The information in this document applies to all Fusion, IGLOO, and ProASIC3 devices. For IGLOO, IGLOO PLUS, and ProASIC3L devices, the Flash\*Freeze pin must be deasserted for successful boundary scan operations. Devices cannot enter JTAG mode directly from Flash\*Freeze mode.

# **Boundary Scan Opcodes**

Low power flash devices support all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD, and BYPASS) and the optional IDCODE instruction (Table 16-2).

#### Table 16-2 • Boundary Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| HIGHZ          | 07         |

| USERCODE       | 0E         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | 0F         |

| CLAMP          | 05         |

| BYPASS         | FF         |

# **Boundary Scan Chain**

The serial pins are used to serially connect all the boundary scan register cells in a device into a boundary scan register chain (Figure 16-2 on page 360), which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic I/O tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Each test section is accessed through the TAP, which has five associated pins: TCK (test clock input), TDI, TDO (test data input and output), TMS (test mode selector), and TRST (test reset input). TMS, TDI, and TRST are equipped with pull-up resistors to ensure proper operation when no input data is supplied to them. These pins are dedicated for boundary scan test usage. Refer to the "JTAG Pins" section in the "Pin Descriptions and Packaging" chapter of the appropriate device datasheet for pull-up/-down recommendations for TCK and TRST pins. Pull-down recommendations are also given in Table 16-3 on page 360

# Microsemi

# Index

### A

AES encryption 305 architecture 147 four I/O banks 13 global 47 IGLOO 12 IGLOO nano 11 IGLOO PLUS 13 IGLOOE 14 ProASIC3 nano 11 ProASIC3E 14 routing 18 spine 57 SRAM and FIFO 151 architecture overview 11 array coordinates 16

### В

boundary scan 357 board-level recommendations 360 chain 359 opcodes 359 brownout voltage 381

# С

CCC 98 board-level considerations 128 cascading 125 **Fusion locations 99** global resources 78 hardwired I/O clock input 124 **IGLOO** locations 97 **IGLOOe** locations 98 locations 96 overview 77 ProASIC3 locations 97 ProASIC3E locations 98 programming 78 software configuration 112 with integrated PLLs 95 without integrated PLLs 95 chip global aggregation 59 CLKDLY macro 81 clock aggregation 60 clock macros 62 clock sources core logic 92 PLL and CLKDLY macros 89 clocks delay adjustment 102 detailed usage information 120 multipliers and dividers 101 phase adjustment 103 physical constraints for quadrant clocks 124 SmartGen settings 121 static timing analysis 123 cold-sparing 382 compiling 261 report 261 contacting Microsemi SoC Products Group customer service 387 email 387 web-based technical support 387 context save and restore 34 customer service 387

# D

DDR architecture 271 design example 282 I/O options 273 input/output support 275 instantiating registers 276 design example 71 design recommendations 62 device architecture 147 DirectC 346 DirectC code 351

### Ε

efficient long-line resources 19 encryption 355

### F

FIFO features 157 initializing 164 memory block consumption 163 software support 170 usage 160 flash switch for programming 9 Flash\*Freeze design flow 39 design guide 34 device behavior 30 I/O state 28 management IP 36 pin locations 31 type 1 24 type 2 26 **ULSICC 40** Flash\*Freeze mode 24

sleep 32 static 23 summary 23 product support customer service 387 email 387 My Cases 388 outside the U.S. 388 technical support 387 website 387 programmers 291 device support 294 programming AES encryption 319 basics 289 features 289 file header definition 323 flash and antifuse 291 flash devices 289 glossary 324 guidelines for flash programming 295 header pin numbers 336 microprocessor 349 power supplies 329 security 313 solution 334 solutions 293 voltage 329 volume services 292 programming support 287

## R

RAM memory block consumption 163 remote upgrade via TCP/IP 354 routing structure 18

## S

security 330 architecture 303 encrypted programming 354 examples 308 features 304 FlashLock 307 FlashROM 137 FlashROM use models 311 in programmable logic 301 overview 301 shutdown mode 32 context save and restore 34 signal integrity problem 337 silicon testing 370 sleep mode 32 context save and restore 34 SmartGen 170 spine architecture 57 spine assignment 68 SRAM features 153 initializing 164 software support 170 usage 157 STAPL player 351 STAPL vs. DirectC 353 static mode 23 switching circuit 344 verification 344 synthesizing 258

# Т

TAP controller state machine 357, 366 tech support ITAR 388 My Cases 388 outside the U.S. 388 technical support 387 transient current VCC 376 VCCI 376 transient current, power-up/-down 375

### U

UJTAG CCC dynamic reconfiguration 368 fine tuning 369 macro 365 operation 366 port usage 367 use to read FlashROM contents 363 ULSICC 40 ultra-fast local lines 18

## V

variable aspect ratio and cascading 161 VersaNet global networks 49 VersaTile 15 very-long-line resources 19 ViewDraw 257 VREF pins manually assigning 265

### W

web-based technical support 387