Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            |                                                                             |

| Number of Logic Elements/Cells | - ·                                                                         |

| Total RAM Bits                 | 516096                                                                      |

| Number of I/O                  | 147                                                                         |

| Number of Gates                | 300000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 208-BFQFP                                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pe3000l-pqg208i |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Flash\*Freeze Technology and Low Power Modes

# Flash\*Freeze Mode

IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 FPGAs offer an ultra-low static power mode to reduce power consumption while preserving the state of the registers, SRAM contents, and I/O states (IGLOO nano and IGLOO PLUS only) without switching off any power supplies, inputs, or input clocks.

Flash\*Freeze technology enables the user to switch to Flash\*Freeze mode within 1 µs, thus simplifying low power design implementation. The Flash\*Freeze (FF) pin (active Low) is a dedicated pin used to enter or exit Flash\*Freeze mode directly; or the pin can be routed internally to the FPGA core and state management IP to allow the user's application to decide if and when it is safe to transition to this mode. If the FF pin is not used, it can be used as a regular I/O.

The FF pin has a built-in glitch filter and optional Schmitt trigger (not available for all devices) to prevent entering or exiting Flash\*Freeze mode accidentally.

There are two ways to use Flash\*Freeze mode. In Flash\*Freeze type 1, entering and exiting the mode is exclusively controlled by the assertion and deassertion of the FF pin. This enables an external processor or human interface device to directly control Flash\*Freeze mode; however, valid data must be preserved using standard procedures (refer to the "Flash\*Freeze Mode Device Behavior" section on page 30). In Flash\*Freeze mode type 2, entering and exiting the mode is controlled by both the FF pin AND user-defined logic. Flash\*Freeze management IP may be used in type 2 mode for clock and data management while entering and exiting Flash\*Freeze mode.

### Flash\*Freeze Type 1: Control by Dedicated Flash\*Freeze Pin

Flash\*Freeze type 1 is intended for systems where either the device will be reset upon exiting Flash\*Freeze mode, or data and clock are managed externally. The device enters Flash\*Freeze mode 1 µs after the dedicated FF pin is asserted (active Low), and returns to normal operation when the FF pin is deasserted (High) (Figure 2-1 on page 25). In this mode, FF pin assertion or deassertion is the only condition that determines entering or exiting Flash\*Freeze mode.

In Libero<sup>®</sup> System-on-Chip (SoC) software v8.2 and before, this mode is implemented by enabling Flash\*Freeze mode (default setting) in the Compile options of the Microsemi Designer software. To simplify usage of Flash\*Freeze mode, beginning with Libero software v8.3, an INBUF\_FF I/O macro was introduced. An INBUF\_FF I/O buffer must be used to identify the Flash\*Freeze input. Microsemi recommends switching to the new implementation.

In Libero software v8.3 and later, the user must manually instantiate the INBUF\_FF macro in the top level of the design to implement Flash\*Freeze Type 1, as shown in Figure 2-1 on page 25.

# 3 – Global Resources in Low Power Flash Devices

# Introduction

IGLOO, Fusion, and ProASIC3 FPGA devices offer a powerful, low-delay VersaNet global network scheme and have extensive support for multiple clock domains. In addition to the Clock Conditioning Circuits (CCCs) and phase-locked loops (PLLs), there is a comprehensive global clock distribution network called a VersaNet global network. Each logical element (VersaTile) input and output port has access to these global networks. The VersaNet global networks can be used to distribute low-skew clock signals or high-fanout nets. In addition, these highly segmented VersaNet global networks contain spines (the vertical branches of the global network tree) and ribs that can reach all the VersaTiles inside their region. This allows users the flexibility to create low-skew local clock networks using spines. This document describes VersaNet global networks and discusses how to assign signals to these global networks and spines in a design flow. Details concerning low power flash device PLLs are described in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" section on page 77. This chapter describes the low power flash devices' global architecture and uses of these global networks in designs.

## **Global Architecture**

Low power flash devices offer powerful and flexible control of circuit timing through the use of global circuitry. Each chip has up to six CCCs, some with PLLs.

- In IGLOOe, ProASIC3EL, and ProASIC3E devices, all CCCs have PLLs—hence, 6 PLLs per device (except the PQ208 package, which has only 2 PLLs).

- In IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3, and ProASIC3L devices, the west CCC contains a PLL core (except in 10 k through 30 k devices).

- In Fusion devices, the west CCC also contains a PLL core. In the two larger devices (AFS600 and AFS1500), the west and east CCCs each contain a PLL.

Refer to Table 4-6 on page 100 for details. Each PLL includes delay lines, a phase shifter (0°, 90°, 180°, 270°), and clock multipliers/dividers. Each CCC has all the circuitry needed for the selection and interconnection of inputs to the VersaNet global network. The east and west CCCs each have access to three chip global lines on each side of the chip (six chip global lines total). The CCCs at the four corners each have access to three quadrant global lines in each quadrant of the chip (except in 10 k through 30 k gate devices).

The nano 10 k, 15 k, and 20 k devices support four VersaNet global resources, and 30 k devices support six global resources. The 10 k through 30 k devices have simplified CCCs called CCC-GLs.

The flexible use of the VersaNet global network allows the designer to address several design requirements. User applications that are clock-resource-intensive can easily route external or gated internal clocks using VersaNet global routing networks. Designers can also drastically reduce delay penalties and minimize resource usage by mapping critical, high-fanout nets to the VersaNet global network.

Note: Microsemi recommends that you choose the appropriate global pin and use the appropriate global resource so you can realize these benefits.

The following sections give an overview of the VersaNet global network, the structure of the global network, access point for the global networks, and the clock aggregation feature that enables a design to have very low clock skew using spines.

Global Resources in Low Power Flash Devices

#### Figure 3-18 • Globals Management GUI in Designer

- 3. Occasionally, the synthesis tool assigns a global macro to clock nets, even though the fanout is significantly less than other asynchronous signals. Select **Demote global nets whose fanout is less than** and enter a reasonable value for fanouts. This frees up some global networks from the signals that have very low fanouts. This can also be done using PDC.

- 4. Use a local clock network for the signals that do not need to go to the whole chip but should have low skew. This local clock network assignment can only be done using PDC.

- 5. Assign the I/O buffer using MVN if you have fixed I/O assignment. As shown in Figure 3-10 on page 61, there are three sets of global pins that have a hardwired connection to each global network. Do not try to put multiple CLKBUF macros in these three sets of global pins. For example, do not assign two CLKBUFs to GAA0x and GAA2x pins.

- 6. You must click **Commit** at the end of MVN assignment. This runs the pre-layout checker and checks the validity of global assignment.

- 7. Always run Compile with the **Keep existing physical constraints** option on. This uses the quadrant clock network assignment in the MVN assignment and checks if you have the desired signals on the global networks.

- 8. Run Layout and check the timing.

# List of Changes

| Date                    | Changes                                                                                                                                                                                                                                                                                                                      | Page |  |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|--|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                    | N/A  |  |  |  |  |  |

|                         | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                                                                                                                                                                    |      |  |  |  |  |  |

|                         | The "Global Architecture" section and "VersaNet Global Network Distribution" 4 section were revised for clarity (SARs 20646, 24779).                                                                                                                                                                                         |      |  |  |  |  |  |

|                         | The "I/O Banks and Global I/Os" section was moved earlier in the document, renamed to "Chip and Quadrant Global I/Os", and revised for clarity. Figure 3-4 • Global Connections Details, Figure 3-6 • Global Inputs, Table 3-2 • Chip Global Pin Name, and Table 3-3 • Quadrant Global Pin Name are new (SARs 20646, 24779). | 51   |  |  |  |  |  |

|                         | The "Clock Aggregation Architecture" section was revised (SARs 20646, 24779).                                                                                                                                                                                                                                                | 57   |  |  |  |  |  |

|                         | Figure 3-7 • Chip Global Aggregation was revised (SARs 20646, 24779).                                                                                                                                                                                                                                                        | 59   |  |  |  |  |  |

|                         | The "Global Macro and Placement Selections" section is new (SARs 20646, 24779).                                                                                                                                                                                                                                              | 64   |  |  |  |  |  |

| v1.4<br>(December 2008) | The "Global Architecture" section was updated to include 10 k devices, and to include information about VersaNet global support for IGLOO nano devices.                                                                                                                                                                      | 47   |  |  |  |  |  |

|                         | The Table 3-1 • Flash-Based FPGAs was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                                               |      |  |  |  |  |  |

|                         | The "VersaNet Global Network Distribution" section was updated to include 10 k devices and to note an exception in global lines for nano devices.                                                                                                                                                                            | 49   |  |  |  |  |  |

|                         | Figure 3-2 • Simplified VersaNet Global Network (30 k gates and below) is new.                                                                                                                                                                                                                                               | 50   |  |  |  |  |  |

|                         | The "Spine Architecture" section was updated to clarify support for 10 k and nano devices.                                                                                                                                                                                                                                   | 57   |  |  |  |  |  |

|                         | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                  | 57   |  |  |  |  |  |

|                         | The figure in the CLKBUF_LVDS/LVPECL row of Table 3-8 • Clock Macros was updated to change CLKBIBUF to CLKBUF.                                                                                                                                                                                                               | 62   |  |  |  |  |  |

| v1.3<br>(October 2008)  | A third bullet was added to the beginning of the "Global Architecture" section: In Fusion devices, the west CCC also contains a PLL core. In the two larger devices (AFS600 and AFS1500), the west and east CCCs each contain a PLL.                                                                                         | 47   |  |  |  |  |  |

|                         | The "Global Resource Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                      | 48   |  |  |  |  |  |

|                         | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated to include A3PE600/L in the device column.                                                                                                                                                                                                        | 57   |  |  |  |  |  |

|                         | Table note 1 was revised in Table 3-9 • I/O Standards within CLKBUF to include AFS600 and AFS1500.                                                                                                                                                                                                                           | 63   |  |  |  |  |  |

| v1.2<br>(June 2008)     | <ul><li>The following changes were made to the family descriptions in Table 3-1 • Flash-Based FPGAs:</li><li>ProASIC3L was updated to include 1.5 V.</li></ul>                                                                                                                                                               | 48   |  |  |  |  |  |

|                         | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                                                                                                               |      |  |  |  |  |  |

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

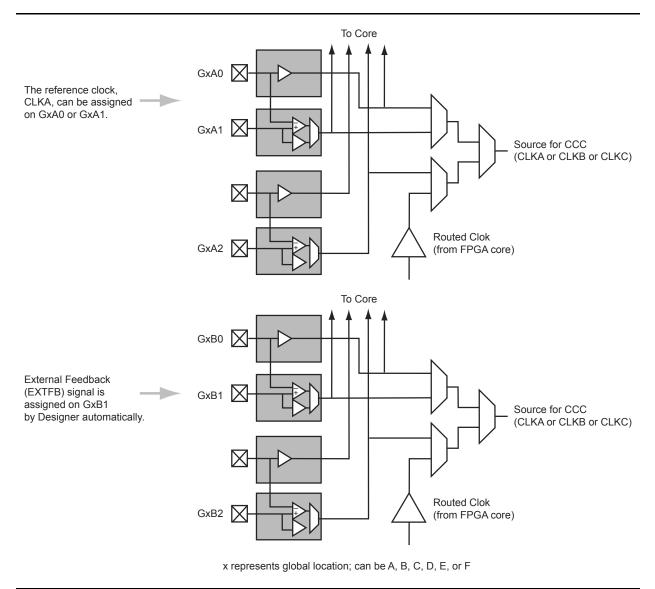

### Implementing EXTFB in ProASIC3/E Devices

When the external feedback (EXTFB) signal of the PLL in the ProASIC3/E devices is implemented, the phase detector of the PLL core receives the reference clock (CLKA) and EXTFB as inputs. EXTFB must be sourced as an INBUF macro and located at the global/chip clock location associated with the target PLL by Designer software. EXTFB cannot be sourced from the FPGA fabric.

The following example shows CLKA and EXTFB signals assigned to two global I/Os in the same global area of ProASIC3E device.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

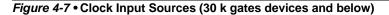

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

Notes:

- Represents the global input pins. Globals have direct access to the clock conditioning block and are not routed via the FPGA fabric. Refer to the "User I/O Naming Conventions in I/O Structures" chapter of the appropriate device user's guide.

- 2. Instantiate the routed clock source input as follows:

- a) Connect the output of a logic element to the clock input of a PLL, CLKDLY, or CLKINT macro.

- b) Do not place a clock source I/O (INBUF or INBUF\_LVPECL/LVDS/B-LVDS/M-LVDS/DDR) in a relevant global pin location.

- 3. IGLOO nano and ProASIC3 nano devices do not support differential inputs.

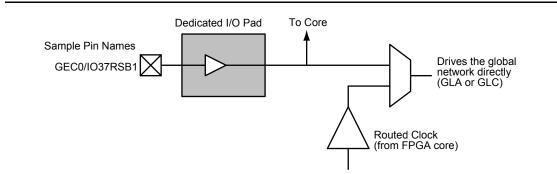

Figure 4-8 • Clock Input Sources Including CLKBUF, CLKBUF\_LVDS/LVPECL, and CLKINT (60 k gates devices and above)

FlashROM in Microsemi's Low Power Flash Devices

# **FlashROM Applications**

The SmartGen core generator is used to configure FlashROM content. You can configure each page independently. SmartGen enables you to create and modify regions within a page; these regions can be 1 to 16 bytes long (Figure 5-4).

|          |   |    |    |    |    | By | /te N | umbe | er in F | Page |   |   |   |   |   |   |   |

|----------|---|----|----|----|----|----|-------|------|---------|------|---|---|---|---|---|---|---|

|          |   | 15 | 14 | 13 | 12 | 11 | 10    | 9    | 8       | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|          | 7 |    |    |    |    |    |       |      |         |      |   |   |   |   |   |   |   |

| <u> </u> | 6 |    |    |    |    |    |       |      |         |      |   |   |   |   |   |   |   |

| he       | 5 |    |    |    |    |    |       |      |         |      |   |   |   |   |   |   |   |

| Numb     | 4 |    |    |    |    |    |       |      |         |      |   |   |   |   |   |   |   |

| ۵<br>ا   | 3 |    |    |    |    |    |       |      |         |      |   |   |   |   |   |   |   |

| Pag      | 2 |    |    |    |    |    |       |      |         |      |   |   |   |   |   |   |   |

| а.       | 1 |    |    |    |    |    |       |      |         |      |   |   |   |   |   |   |   |

|          | 0 |    |    |    |    |    |       |      |         |      |   |   |   |   |   |   |   |

#### Figure 5-4 • FlashROM Configuration

The FlashROM content can be changed independently of the FPGA core content. It can be easily accessed and programmed via JTAG, depending on the security settings of the device. The SmartGen core generator enables each region to be independently updated (described in the "Programming and Accessing FlashROM" section on page 138). This enables you to change the FlashROM content on a per-part basis while keeping some regions "constant" for all parts. These features allow the FlashROM to be used in diverse system applications. Consider the following possible uses of FlashROM:

- Internet protocol (IP) addressing (wireless or fixed)

- System calibration settings

- Restoring configuration after unpredictable system power-down

- · Device serialization and/or inventory control

- Subscription-based business models (e.g., set-top boxes)

- Secure key storage

- Asset management tracking

- Date stamping

- Version management

### **SRAM Features**

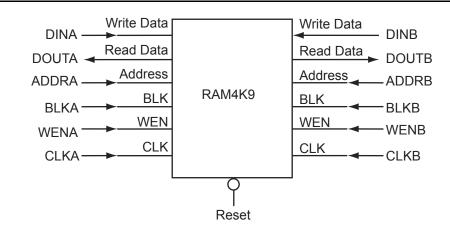

#### RAM4K9 Macro

RAM4K9 is the dual-port configuration of the RAM block (Figure 6-4). The RAM4K9 nomenclature refers to both the deepest possible configuration and the widest possible configuration the dual-port RAM block can assume, and does not denote a possible memory aspect ratio. The RAM block can be configured to the following aspect ratios: 4,096×1, 2,048×2, 1,024×4, and 512×9. RAM4K9 is fully synchronous and has the following features:

- Two ports that allow fully independent reads and writes at different frequencies

- Selectable pipelined or nonpipelined read

- Active-low block enables for each port

- Toggle control between read and write mode for each port

- · Active-low asynchronous reset

- Pass-through write data or hold existing data on output. In pass-through mode, the data written to the write port will immediately appear on the read port.

- Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

*Note:* For timing diagrams of the RAM signals, refer to the appropriate family datasheet. *Figure 6-4* • RAM4K9 Simplified Configuration

#### Signal Descriptions for RAM4K9

Note: Automotive ProASIC3 devices support single-port SRAM capabilities, or dual-port SRAM only under specific conditions. Dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). Since Libero SoC macro libraries support a dual-port macro only, certain modifications must be made. These are detailed below.

The following signals are used to configure the RAM4K9 memory element:

#### WIDTHA and WIDTHB

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 6-2 on page 154).

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WIDTHB should be tied to ground.

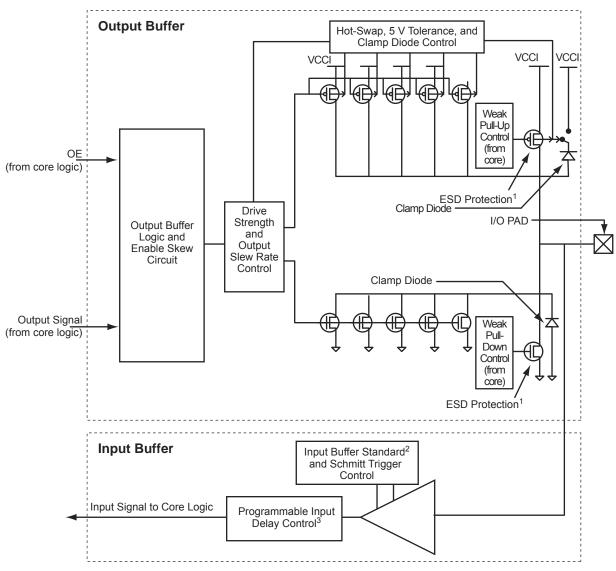

#### Notes:

- 1. All NMOS transistors connected to the I/O pad serve as ESD protection.

- 2. See Table 7-2 on page 177 for available I/O standards.

3. Programmable input delay is applicable only to ProASIC3EL and RT ProASIC3 devices.

Figure 7-4 • Simplified I/O Buffer Circuitry

#### I/O Registers

Each I/O module contains several input, output, and enable registers. Refer to Figure 7-4 for a simplified representation of the I/O block. The number of input registers is selected by a set of switches (not shown in Figure 7-2 on page 181) between registers to implement single-ended or differential data transmission to and from the FPGA core. The Designer software sets these switches for the user. A common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. Input Register 2 does not have a CLR/PRE pin, as this register is used for DDR implementation. The I/O register combining must satisfy certain rules.

I/O Structures in IGLOO and ProASIC3 Devices

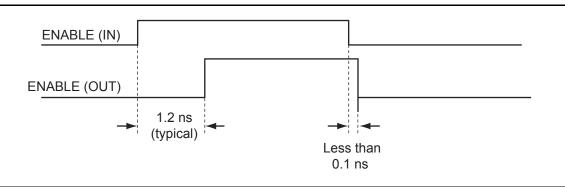

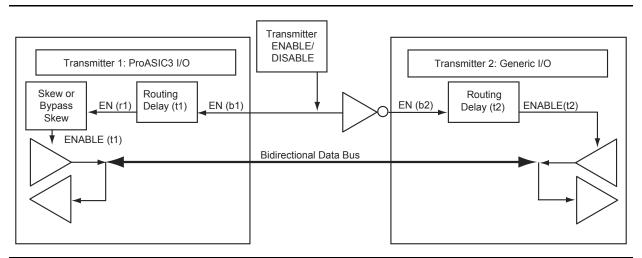

At the system level, the skew circuit can be used in applications where transmission activities on bidirectional data lines need to be coordinated. This circuit, when selected, provides a timing margin that can prevent bus contention and subsequent data loss and/or transmitter over-stress due to transmitter-to-transmitter current shorts. Figure 7-16 presents an example of the skew circuit implementation in a bidirectional communication system. Figure 7-17 on page 201 shows how bus contention is created, and Figure 7-18 on page 201 shows how it can be avoided with the skew circuit.

Figure 7-16 • Example of Implementation of Skew Circuits in Bidirectional Transmission Systems Using IGLOO or ProASIC3 Devices

I/O Structures in IGLOO and ProASIC3 Devices

# **Board-Level Considerations**

Low power flash devices have robust I/O features that can help in reducing board-level components. The devices offer single-chip solutions, which makes the board layout simpler and more immune to signal integrity issues. Although, in many cases, these devices resolve board-level issues, special attention should always be given to overall signal integrity. This section covers important board-level considerations to facilitate optimum device performance.

### **Termination**

Proper termination of all signals is essential for good signal quality. Nonterminated signals, especially clock signals, can cause malfunctioning of the device.

For general termination guidelines, refer to the *Board-Level Considerations* application note for Microsemi FPGAs. Also refer to the "Pin Descriptions" chapter of the appropriate datasheet for termination requirements for specific pins.

Low power flash I/Os are equipped with on-chip pull-up/-down resistors. The user can enable these resistors by instantiating them either in the top level of the design (refer to the *IGLOO, Fusion, and ProASIC3 Macro Library Guide* for the available I/O macros with pull-up/-down) or in the I/O Attribute Editor in Designer if generic input or output buffers are instantiated in the top level. Unused I/O pins are configured as inputs with pull-up resistors.

As mentioned earlier, low power flash devices have multiple programmable drive strengths, and the user can eliminate unwanted overshoot and undershoot by adjusting the drive strengths.

### **Power-Up Behavior**

Low power flash devices are power-up/-down friendly; i.e., no particular sequencing is required for power-up and power-down. This eliminates extra board components for power-up sequencing, such as a power-up sequencer.

During power-up, all I/Os are tristated, irrespective of I/O macro type (input buffers, output buffers, I/O buffers with weak pull-ups or weak pull-downs, etc.). Once I/Os become activated, they are set to the user-selected I/O macros. Refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 373 for details.

### **Drive Strength**

Low power flash devices have up to seven programmable output drive strengths. The user can select the drive strength of a particular output in the I/O Attribute Editor or can instantiate a specialized I/O macro, such as OUTBUF\_S\_12 (slew = low, out\_drive = 12 mA).

The maximum available drive strength is 24 mA per I/O. Though no I/O should be forced to source or sink more than 24 mA indefinitely, I/Os may handle a higher amount of current (refer to the device IBIS model for maximum source/sink current) during signal transition (AC current). Every device package has its own power dissipation limit; hence, power calculation must be performed accurately to determine how much current can be tolerated per I/O within that limit.

### I/O Interfacing

Low power flash devices are 5 V–input– and 5 V–output–tolerant if certain I/O standards are selected (refer to the "5 V Input and Output Tolerance" section on page 194). Along with other low-voltage I/O macros, this 5 V tolerance makes these devices suitable for many types of board component interfacing.

I/O Structures in IGLOOe and ProASIC3E Devices

IGLOOe and ProASIC3E devices support output slew rate control: high and low. Microsemi recommends the high slew rate option to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected.

### **Output Drive**

The output buffers of IGLOOe and ProASIC3E devices can provide multiple drive strengths to meet signal integrity requirements. The LVTTL and LVCMOS (except 1.2 V LVCMOS) standards have selectable drive strengths. Other standards have a preset value.

Drive strength should also be selected according to the design requirements and noise immunity of the system.

The output slew rate and multiple drive strength controls are available in LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V, LVCMOS 2.5 V / 5.0 V input, LVCMOS 1.8 V, and LVCMOS 1.5 V. All other I/O standards have a high output slew rate by default.

For other IGLOOe and ProASIC3E devices, refer to Table 8-15 for more information about the slew rate and drive strength specification.

There will be a difference in timing between the Standard Plus I/O banks and the Advanced I/O banks. Refer to the I/O timing tables in the datasheet for the standards supported by each device.

| I/O Standards      | 2 mA | 4 mA | 6 mA | 8 mA | 12 mA                 | 16 mA | 24 mA | SI   | ew  |

|--------------------|------|------|------|------|-----------------------|-------|-------|------|-----|

| LVTTL/LVCMOS 3.3 V | 1    | 1    | 1    | ~    | ✓                     | 1     | ~     | High | Low |

| LVCMOS 2.5 V       | 1    | 1    | 1    | ~    | ✓                     | 1     | 1     | High | Low |

| LVCMOS 2.5/5.0 V   | 1    | 1    | 1    | 1    | ✓                     | 1     | 1     | High | Low |

| LVCMOS 1.8 V       | 1    | 1    | 1    | 1    | ✓                     | 1     | _     | High | Low |

| LVCMOS 1.5 V       | 1    | 1    | 1    | 1    | <ul> <li>✓</li> </ul> | -     | -     | High | Low |

Table 8-15 • IGLOOe and ProASIC3E I/O Standards—Output Drive and Slew Rate

# List of Changes

| Date        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| August 2012 | This chapter will now be published standalone as an application note in addition to being part of the IGLOO/ProASIC3/Fusion FPGA fabric user's guides (SAR 38769).                                                                                                                                                                                                                                                                          | N/A      |

|             | The "ISP Programming Header Information" section was revised to update the description of FP3-10PIN-ADAPTER-KIT in Table 13-3 • Programming Header Ordering Codes, clarifying that it is the adapter kit used for ProASIC <sup>PLUS</sup> based boards, and also for ProASIC3 based boards where a compact programming header is being used (SAR 36779).                                                                                    | 335      |

| June 2011   | The VPUMP programming mode voltage was corrected in Table 13-2 • Power Supplies. The correct value is 3.15 V to 3.45 V (SAR 30668).                                                                                                                                                                                                                                                                                                         | 329      |

|             | The notes associated with Figure 13-5 • Programming Header (top view) and Figure 13-6 • Board Layout and Programming Header Top View were revised to make clear the fact that IGLOO nano V2 devices can be programmed at 1.2 V (SAR 30787).                                                                                                                                                                                                 | 335, 337 |

|             | Figure 13-6 • Board Layout and Programming Header Top View was revised to include resistors tying TCK and TRST to GND. Microsemi recommends tying off TCK and TRST to GND if JTAG is not used (SAR 22921). RT ProASIC3 was added to the list of device families.                                                                                                                                                                            | 337      |

|             | In the "ISP Programming Header Information" section, the kit for adapting ProASIC <sup>PLUS</sup> devices was changed from FP3-10PIN-ADAPTER-KIT to FP3-26PIN-ADAPTER-KIT (SAR 20878).                                                                                                                                                                                                                                                      | 335      |

| July 2010   | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                                                                                                                                   | N/A      |

|             | References to FlashPro4 and FlashPro3X were added to this chapter, giving distinctions between them. References to SmartGen were deleted and replaced with Libero IDE Catalog.                                                                                                                                                                                                                                                              | N/A      |

|             | The "ISP Architecture" section was revised to indicate that V2 devices can be programmed at 1.2 V VCC with FlashPro4.                                                                                                                                                                                                                                                                                                                       | 327      |

|             | SmartFusion was added to Table 13-1 • Flash-Based FPGAs Supporting ISP.                                                                                                                                                                                                                                                                                                                                                                     | 328      |

|             | The "Programming Voltage (VPUMP) and VJTAG" section was revised and 1.2 V was added to Table 13-2 • Power Supplies.                                                                                                                                                                                                                                                                                                                         | 329      |

|             | The "Nonvolatile Memory (NVM) Programming Voltage" section is new.                                                                                                                                                                                                                                                                                                                                                                          | 329      |

|             | Cortex-M3 was added to the "Cortex-M1 and Cortex-M3 Device Security" section.                                                                                                                                                                                                                                                                                                                                                               | 331      |

|             | In the "ISP Programming Header Information" section, the additional header adapter ordering number was changed from FP3-26PIN-ADAPTER to FP3-10PIN-ADAPTER-KIT, which contains 26-pin migration capability.                                                                                                                                                                                                                                 | 335      |

|             | The description of NC was updated in Figure 13-5 • Programming Header (top view), Table 13-4 • Programming Header Pin Numbers and Description and Figure 13-6 • Board Layout and Programming Header Top View.                                                                                                                                                                                                                               | 335, 336 |

|             | The "Symptoms of a Signal Integrity Problem" section was revised to add that customers are expected to troubleshoot board-level signal integrity issues by measuring voltages and taking scope plots. "FlashPro4/3/3X allows TCK to be lowered from 6 MHz down to 1 MHz to allow you to address some signal integrity problems" formerly read, "from 24 MHz down to 1 MHz." "The Scan Chain command expects to see 0x2" was changed to 0x1. | 337      |

# List of Changes

| Date                   | Changes                                                                                                                                               | Page |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010              | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.             | N/A  |

| v1.1<br>(October 2008) | The "Introduction" was revised to include information about the core supply voltage range of operation in V2 devices.                                 |      |

|                        | IGLOO nano device support was added to Table 14-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit.                                           | 342  |

|                        | The "Circuit Description" section was updated to include IGLOO PLUS core operation from 1.2 V to 1.5 V in 50 mV increments.                           | 343  |

| v1.0<br>(August 2008)  | The "Microsemi's Flash Families Support Voltage Switching Circuit" section was revised to include new families and make the information more concise. | 342  |

UJTAG Applications in Microsemi's Low Power Flash Devices

# **Typical UJTAG Applications**

Bidirectional access to the JTAG port from VersaTiles—without putting the device into test mode creates flexibility to implement many different applications. This section describes a few of these. All are based on importing/exporting data through the UJTAG tiles.

## **Clock Conditioning Circuitry—Dynamic Reconfiguration**

In low power flash devices, CCCs, which include PLLs, can be configured dynamically through either an 81-bit embedded shift register or static flash programming switches. These 81 bits control all the characteristics of the CCC: routing MUX architectures, delay values, divider values, etc. Table 17-3 lists the 81 configuration bits in the CCC.

| Bit Number(s) | Control Function |

|---------------|------------------|

| 80            | RESET ENABLE     |

| 79            | DYNCSEL          |

| 78            | DYNBSEL          |

| 77            | DYNASEL          |

| <76:74>       | VCOSEL [2:0]     |

| 73            | STATCSEL         |

| 72            | STATBSEL         |

| 71            | STATASEL         |

| <70:66>       | DLYC [4:0]       |

| <65:61>       | DLYB {4:0]       |

| <60:56>       | DLYGLC [4:0]     |

| <55:51>       | DLYGLB [4:0]     |

| <50:46>       | DLYGLA [4:0]     |

| 45            | XDLYSEL          |

| <44:40>       | FBDLY [4:0]      |

| <39:38>       | FBSEL            |

| <37:35>       | OCMUX [2:0]      |

| <34:32>       | OBMUX [2:0]      |

| <31:29>       | OAMUX [2:0]      |

| <28:24>       | OCDIV [4:0]      |

| <23:19>       | OBDIV [4:0]      |

| <18:14>       | OADIV [4:0]      |

| <13:7>        | FBDIV [6:0]      |

| <6:0>         | FINDIV [6:0]     |

Table 17-3 • Configuration Bits of Fusion, IGLOO, and ProASIC3 CCC Blocks

The embedded 81-bit shift register (for the dynamic configuration of the CCC) is accessible to the VersaTiles, which, in turn, have access to the UJTAG tiles. Therefore, the CCC configuration shift register can receive and load the new configuration data stream from JTAG.

Dynamic reconfiguration eliminates the need to reprogram the device when reconfiguration of the CCC functional blocks is needed. The CCC configuration can be modified while the device continues to operate. Employing the UJTAG core requires the user to design a module to provide the configuration data and control the CCC configuration shift register. In essence, this is a user-designed TAP Controller requiring chip resources.

Similar reconfiguration capability exists in the ProASIC<sup>PLUS®</sup> family. The only difference is the number of shift register bits controlling the CCC (27 in ProASIC<sup>PLUS</sup> and 81 in IGLOO, ProASIC3, and Fusion).

# 18 – Power-Up/-Down Behavior of Low Power Flash Devices

## Introduction

Microsemi's low power flash devices are flash-based FPGAs manufactured on a 0.13  $\mu$ m process node. These devices offer a single-chip, reprogrammable solution and support Level 0 live at power-up (LAPU) due to their nonvolatile architecture.

Microsemi's low power flash FPGA families are optimized for logic area, I/O features, and performance. IGLOO<sup>®</sup> devices are optimized for power, making them the industry's lowest power programmable solution. IGLOO PLUS FPGAs offer enhanced I/O features beyond those of the IGLOO ultra-low power solution for I/O-intensive low power applications. IGLOO nano devices are the industry's lowest-power cost-effective solution. ProASIC3<sup>®</sup>L FPGAs balance low power with high performance. The ProASIC3 family is Microsemi's high-performance flash FPGA solution. ProASIC3 nano devices offer the lowest-cost solution with enhanced I/O capabilities.

Microsemi's low power flash devices exhibit very low transient current on each power supply during power-up. The peak value of the transient current depends on the device size, temperature, voltage levels, and power-up sequence.

The following devices can have inputs driven in while the device is not powered:

- IGLOO (AGL015 and AGL030)

- IGLOO nano (all devices)

- IGLOO PLUS (AGLP030, AGLP060, AGLP125)

- IGLOOe (AGLE600, AGLE3000)

- ProASIC3L (A3PE3000L)

- ProASIC3 (A3P015, A3P030)

- ProASIC3 nano (all devices)

- ProASIC3E (A3PE600, A3PE1500, A3PE3000)

- Military ProASIC3EL (A3PE600L, A3PE3000L, but not A3P1000)

- RT ProASIC3 (RT3PE600L, RT3PE3000L)

The driven I/Os do not pull up power planes, and the current draw is limited to very small leakage current, making them suitable for applications that require cold-sparing. These devices are hot-swappable, meaning they can be inserted in a live power system.<sup>1</sup>

<sup>1.</sup> For more details on the levels of hot-swap compatibility in Microsemi's low power flash devices, refer to the "Hot-Swap Support" section in the I/O Structures chapter of the FPGA fabric user's guide for the device you are using.

Power-Up/-Down Behavior of Low Power Flash Devices

# **Related Documents**

### Datasheets

ProASIC3 Flash Family FPGAs http://www.microsemi.com/soc/documents/PA3\_DS.pdf ProASIC3E Flash Family FPGAs http://www.microsemi.com/soc/documents/PA3E\_DS.pdf

# List of Changes

| Date                    | Changes                                                                                                                                                                                                                                                                                  | Page |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| v1.2<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to the document as supported device types.                                                                                                                                                                                               |      |

| v1.1<br>(October 2008)  | The "Introduction" section was updated to add Military ProASIC3EL and RT<br>ProASIC3 devices to the list of devices that can have inputs driven in while the<br>device is not powered.                                                                                                   | 373  |

|                         | The "Flash Devices Support Power-Up Behavior" section was revised to include new families and make the information more concise.                                                                                                                                                         | 374  |

|                         | The "Cold-Sparing" section was revised to add Military ProASIC3/EL and RT ProASIC3 devices to the lists of devices with and without cold-sparing support.                                                                                                                                | 382  |

|                         | The "Hot-Swapping" section was revised to add Military ProASIC3/EL and RT<br>ProASIC3 devices to the lists of devices with and without hot-swap support.<br>AGL400 was added to the list of devices that do not support hot-swapping.                                                    | 383  |

| v1.0<br>(August 2008)   | This document was revised, renamed, and assigned a new part number. It now includes data for the IGLOO and ProASIC3L families.                                                                                                                                                           | N/A  |

| v1.3<br>(March 2008)    | The "List of Changes" section was updated to include the three different I/O Structure handbook chapters.                                                                                                                                                                                | 384  |

| v1.2<br>(February 2008) | The first sentence of the "PLL Behavior at Brownout Condition" section was updated to read, "When PLL power supply voltage and/or V <sub>CC</sub> levels drop below the VCC brownout levels (0.75 V $\pm$ 0.25 V), the PLL output lock signal goes low and/or the output clock is lost." | 381  |

| v1.1<br>(January 2008)  | The "PLL Behavior at Brownout Condition" section was added.                                                                                                                                                                                                                              | 381  |

# A – Summary of Changes

# **History of Revision to Chapters**

The following table lists chapters that were affected in each revision of this document. Each chapter includes its own change history because it may appear in other device family user's guides. Refer to the individual chapter for a list of specific changes.

| Revision<br>(month/year)       | Chapter Affected                                                                                                                                                               | List of Changes<br>(page number) |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Revision 4<br>(September 2012) | "Microprocessor Programming of Microsemi's Low Power Flash Devices" was revised.                                                                                               | 356                              |  |  |

| Revision 3<br>(August 2012)    | "FPGA Array Architecture in Low Power Flash Devices" was revised.                                                                                                              | 20                               |  |  |

|                                | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                                                   |                                  |  |  |

|                                | "SRAM and FIFO Memories in Microsemi's Low Power Flash Devices" was revised.                                                                                                   | 173                              |  |  |

|                                | "I/O Structures in IGLOO and ProASIC3 Devices" was revised.                                                                                                                    | 210                              |  |  |

|                                | "I/O Structures in IGLOOe and ProASIC3E Devices" was revised.                                                                                                                  | 249                              |  |  |

|                                | The "Pin Descriptions" and "Packaging" chapters were removed. This information is now published in the datasheet for each product line (SAR 34773).                            |                                  |  |  |

|                                | "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" was revised.                                                                         | 339                              |  |  |

|                                | "Boundary Scan in Low Power Flash Devices" was revised.                                                                                                                        | 362                              |  |  |

| Revision 2<br>(December 2011)  | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                                                   | 129                              |  |  |

|                                | "UJTAG Applications in Microsemi's Low Power Flash Devices" was revised.                                                                                                       | 372                              |  |  |

| Revision 1<br>(June 2011)      | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                                                   | 129                              |  |  |

|                                | "I/O Structures in IGLOO and ProASIC3 Devices" was revised.                                                                                                                    | 210                              |  |  |

|                                | "I/O Structures in IGLOOe and ProASIC3E Devices" was revised.                                                                                                                  | 249                              |  |  |

|                                | "I/O Software Control in Low Power Flash Devices" was revised.                                                                                                                 | 270                              |  |  |

|                                | "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" was revised.                                                                         | 339                              |  |  |

| Revision 0<br>(July 2010)      | The ProASIC3L Flash Family FPGAs Handbook was divided into two parts to<br>create the ProASIC3L Low Power Flash FPGAs Datasheet and the ProASIC3L<br>FPGA Fabric User's Guide. | N/A                              |  |  |

|                                | "Global Resources in Low Power Flash Devices" was revised.                                                                                                                     | 75                               |  |  |

|                                | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                                                   | 129                              |  |  |

|                                | "I/O Software Control in Low Power Flash Devices" was revised.                                                                                                                 | 270                              |  |  |

# **B** – **Product Support**

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

## **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call 800.262.1060 From the rest of the world, call 650.318.4460 Fax, from anywhere in the world, 650.318.8044

# **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

# **Technical Support**

Visit the Customer Support website (www.microsemi.com/soc/support/search/default.aspx) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the website.

## Website

You can browse a variety of technical and non-technical information on the SoC home page, at www.microsemi.com/soc.

## **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

#### Email

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc\_tech@microsemi.com.