Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Active                                                                       |

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | -                                                                            |

| Total RAM Bits                 | 147456                                                                       |

| Number of I/O                  | 177                                                                          |

| Number of Gates                | 1000000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                               |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 256-LBGA                                                                     |

| Supplier Device Package        | 256-FPBGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3p1000l-1fgg256 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

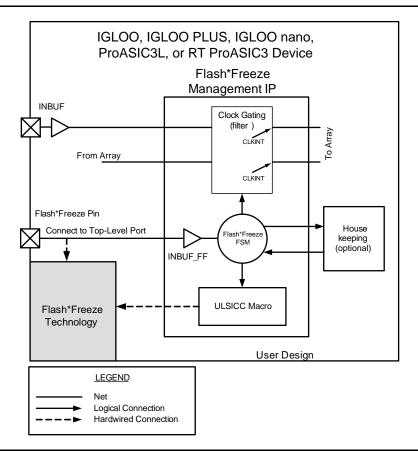

Flash\*Freeze management IP. Additional information on this IP core can be found in the Libero online help.

The Flash\*Freeze management IP is comprised of three blocks: the Flash\*Freeze finite state machine (FSM), the clock gating (filter) block, and the ULSICC macro, as shown in Figure 2-10.

Figure 2-10 • Flash\*Freeze Management IP Block Diagram

#### Flash\*Freeze Management FSM

The Flash\*Freeze FSM block is a simple, robust, fully encoded 3-bit state machine that ensures clean entrance to and exit from Flash\*Freeze mode by controlling activities of the clock gating, ULSICC, and optional housekeeping blocks. The state diagram for the FSM is shown in Figure 2-11 on page 38. In normal operation, the state machine waits for Flash\*Freeze pin assertion, and upon detection of a request, it waits for a short period of time to ensure the assertion persists; then it asserts WAIT\_HOUSEKEEPING (active High) synchronous to the user's designated system clock. This flag can be used by user logic to perform any needed shutdown processes prior to entering Flash\*Freeze mode, such as storing data into SRAM, notifying other system components of the request, or timing/validating the Flash\*Freeze request. The FSM also asserts Flash\_Freeze\_Enabled whenever the device enters Flash\*Freeze mode. This occurs after all housekeeping and clock gating functions have completed. The Flash Freeze Enabled signal remains asserted, even during Flash\*Freeze mode, until the Flash\*Freeze pin is deasserted. Use the Flash Freeze Enabled signal to drive any logic in the design that needs to be in a particular state during Flash\*Freeze mode. The DONE\_HOUSEKEEPING (active High) signal should be asserted to notify the FSM when all the housekeeping tasks are completed. If the user chooses not to use housekeeping, the Flash\*Freeze management IP core generator in Libero SoC will connect WAIT\_HOUSEKEEPING to DONE\_HOUSEKEEPING.

Revision 4 37

UJTAG Applications in Microsemi's Low Power Flash Devices

## Conclusion

Microsemi low power flash FPGAs offer many unique advantages, such as security, nonvolatility, reprogrammablity, and low power—all in a single chip. In addition, Fusion, IGLOO, and ProASIC3 devices provide access to the JTAG port from core VersaTiles while the device is in normal operating mode. A wide range of available user-defined JTAG opcodes allows users to implement various types of applications, exploiting this feature of these devices. The connection between the JTAG port and core tiles is implemented through an embedded and hardwired UJTAG tile. A UJTAG tile can be instantiated in designs using the UJTAG library cell. This document presents multiple examples of UJTAG applications, such as dynamic reconfiguration, silicon test and debug, fine-tuning of the design, and RAM initialization. Each of these applications offers many useful advantages.

### **Related Documents**

## **Application Notes**

RAM Initialization and ROM Emulation in ProASICPLUS Devices http://www.microsemi.com/soc/documents/APA\_RAM\_Initd\_AN.pdf

# List of Changes

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                    | Page |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| December 2011           | Information on the drive strength and slew rate of TDO pins was added to the "Silicon Testing and Debugging" section (SAR 31749).                                                                          | 370  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                  | N/A  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 17-1 • Flash-Based FPGAs.                                                                                                                         | 364  |

| v1.3<br>(October 2008)  | The "UJTAG Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                              | 364  |

|                         | The title of Table 17-3 • Configuration Bits of Fusion, IGLOO, and ProASIC3 CCC Blocks was revised to include Fusion.                                                                                      | 368  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 17-1 • Flash-Based FPGAs:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six. | 364  |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                                                                                      | N/A  |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                | 364  |

372 Revision 4