Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | ·                                                                           |

| Total RAM Bits                 | 147456                                                                      |

| Number of I/O                  | 177                                                                         |

| Number of Gates                | 1000000                                                                     |

| Voltage - Supply               | 1.14V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 256-LBGA                                                                    |

| Supplier Device Package        | 256-FPBGA (17x17)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3p1000l-fgg256 |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Introduction

# Contents

This user's guide contains information to help designers understand and use Microsemi's ProASIC<sup>®</sup>3L devices. Each chapter addresses a specific topic. Most of these chapters apply to other Microsemi device families as well. When a feature or description applies only to a specific device family, this is made clear in the text.

# **Revision History**

The revision history for each chapter is listed at the end of the chapter. Most of these chapters were formerly included in device handbooks. Some were originally application notes or information included in device datasheets.

A "Summary of Changes" table at the end of this user's guide lists the chapters that were changed in each revision of the document, with links to the "List of Changes" sections for those chapters.

# **Related Information**

Refer to the *ProASIC3L Flash Family FPGAs* datasheet for detailed specifications, timing, and package and pin information.

The website page for ProASIC3L devices is /www.microsemi.com/soc/products/pa3l/default.aspx.

FPGA Array Architecture in Low Power Flash Devices

# **FPGA Array Architecture Support**

The flash FPGAs listed in Table 1-1 support the architecture features described in this document.

#### Table 1-1 • Flash-Based FPGAs

| Series                 | Family <sup>*</sup>  | Description                                                                                                                                                                                    |

|------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO <sup>®</sup>     | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|                        | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|                        | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|                        | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC <sup>®</sup> 3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|                        | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|                        | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|                        | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|                        | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|                        | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|                        | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion                 | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

FPGA Array Architecture in Low Power Flash Devices

Note: + Flash\*Freeze mode is supported on IGLOO devices.

Note: Flash\*Freeze technology only applies to IGLOO and ProASIC3L families.

Note: \* AGLP030 does not contain a PLL or support AES security.

Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks

|            |               | VersaTiles |           | Memory Rows |         | Entire Die |           |

|------------|---------------|------------|-----------|-------------|---------|------------|-----------|

| Device     |               | Min.       | Max.      | Bottom      | Тор     | Min.       | Max.      |

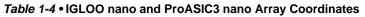

| IGLOO nano | ProASIC3 nano | (x, y)     | (x, y)    | (x, y)      | (x, y)  | (x, y)     | (x, y)    |

| AGLN010    | A3P010        | (0, 2)     | (32, 5)   | None        | None    | (0, 0)     | (34, 5)   |

| AGLN015    | A3PN015       | (0, 2)     | (32, 9)   | None        | None    | (0, 0)     | (34, 9)   |

| AGLN020    | A3PN020       | (0, 2)     | 32, 13)   | None        | None    | (0, 0)     | (34, 13)  |

| AGLN060    | A3PN060       | (3, 2)     | (66, 25)  | None        | (3, 26) | (0, 0)     | (69, 29)  |

| AGLN125    | A3PN125       | (3, 2)     | (130, 25) | None        | (3, 26) | (0, 0)     | (133, 29) |

| AGLN250    | A3PN250       | (3, 2)     | (130, 49) | None        | (3, 50) | (0, 0)     | (133, 49) |

Note: The vertical I/O tile coordinates are not shown. West-side coordinates are {(0, 2) to (2, 2)} to {(0, 77) to (2, 77)}; east-side coordinates are {(195, 2) to (197, 2)} to {(195, 77) to (197, 77)}.

*Figure 1-9* • Array Coordinates for AGL600, AGLE600, A3P600, and A3PE600

Flash\*Freeze Technology and Low Power Modes

# Flash Families Support the Flash\*Freeze Feature

The low power flash FPGAs listed in Table 2-1 support the Flash\*Freeze feature and the functions described in this document.

#### Table 2-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 2-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

#### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 2-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

Flash\*Freeze Technology and Low Power Modes

Table 2-4 summarizes the Flash\*Freeze mode implementations.

| Flash*Freeze<br>Mode Type         | Description                                   | Flash*Freeze<br>Pin State | Instantiate<br>ULSICC Macro | LSICC<br>Signal | Operating Mode    |

|-----------------------------------|-----------------------------------------------|---------------------------|-----------------------------|-----------------|-------------------|

|                                   | Flash*Freeze mode is                          |                           | No                          | N/A             | Normal operation  |

| controlled only by the<br>FF pin. |                                               | Asserted                  | No                          | N/A             | Flash*Freeze mode |

|                                   | Flash*Freeze mode is                          |                           | Yes                         | Deasserted      | Normal operation  |

|                                   | controlled by the FF<br>pin and LSICC signal. | Deasserted                | Yes                         | "Don't care"    | Normal operation  |

|                                   |                                               | Asserted                  | Yes                         | Asserted        | Flash*Freeze mode |

| Table 2-4 • | Flash*Freeze | Mode Usage |

|-------------|--------------|------------|

|-------------|--------------|------------|

Note: Refer to Table 2-3 on page 26 for Flash\*Freeze pin and LSICC signal assertion and deassertion values.

# IGLOO, ProASIC3L, and RT ProASIC3 I/O State in Flash\*Freeze Mode

In IGLOO and ProASIC3L devices, when the device enters Flash\*Freeze mode, I/Os become tristated. If the weak pull-up or pull-down feature is used, the I/Os will maintain the configured weak pull-up or pull-down status. This feature enables the design to set the I/O state to a certain level that is determined by the pull-up/-down configuration.

Table 2-5 shows the I/O pad state based on the configuration and buffer type.

Note that configuring weak pull-up or pull-down for the FF pin is not allowed. The FF pin can be configured as a Schmitt trigger input in IGLOOe, IGLOO nano, IGLOO PLUS, and ProASIC3EL devices.

#### Table 2-5 • IGLOO, ProASIC3L, and RT ProASIC3 Flash\*Freeze Mode (type 1 and type 2)—I/O Pad State

| Buffer Type              |                  | I/O Pad Weak<br>Pull-Up/-Down | I/O Pad State in Flash*Freeze Mode |  |

|--------------------------|------------------|-------------------------------|------------------------------------|--|

| Input/Global             |                  | Enabled                       | Weak pull-up/pull-down*            |  |

|                          |                  | Disabled                      | Tristate*                          |  |

| Output                   |                  | Enabled                       | Weak pull-up/pull-down             |  |

|                          |                  | Disabled                      | Tristate                           |  |

| Bidirectional / Tristate | E = 0            | Enabled                       | Weak pull-up/pull-down*            |  |

| Buffer                   | (input/tristate) | Disabled                      | Tristate*                          |  |

|                          | E = 1 (output)   | Enabled                       | Weak pull-up/pull-down             |  |

|                          |                  | Disabled                      | Tristate                           |  |

\* Internal core logic driven by this input/global buffer will be tied High as long as the device is in Flash\*Freeze mode.

Global Resources in Low Power Flash Devices

| I/О Туре               | Beginning of I/O Name | Notes                                                        |

|------------------------|-----------------------|--------------------------------------------------------------|

| Single-Ended           | GFAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFA1/IOuxwByVz        | global at a time.                                            |

|                        | GFA2/IOuxwByVz        |                                                              |

|                        | GFBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFB1/IOuxwByVz        | global at a time.                                            |

|                        | GFB2/IOuxwByVz        |                                                              |

|                        | GFC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFC1/IOuxwByVz        | global at a time.                                            |

|                        | GFC2/IOuxwByVz        |                                                              |

|                        | GCAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCA1/IOuxwByVz        | global at a time.                                            |

|                        | GCA2/IOuxwByVz        |                                                              |

|                        | GCBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCB1/IOuxwByVz        | global at a time.                                            |

|                        | GCB2/IOuxwByVz        |                                                              |

|                        | GCC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCC1/IOuxwByVz        | global at a time.                                            |

|                        | GCC2/IOuxwByVz        |                                                              |

| Differential I/O Pairs | GFAO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFA1/IOuxwByVz        |                                                              |

|                        | GFBO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFB1/IOuxwByVz        |                                                              |

|                        | GFCO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFC1/IOuxwByVz        |                                                              |

|                        | GCAO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCA1/IOuxwByVz        |                                                              |

|                        | GCBO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCB1/IOuxwByVz        |                                                              |

|                        | GCCO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCC1/IOuxwByVz        |                                                              |

#### Table 3-2 • Chip Global Pin Name

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

Global Resources in Low Power Flash Devices

The following will happen during demotion of a global signal to regular nets:

- CLKBUF\_x becomes INBUF\_x; CLKINT is removed from the netlist.

- The essential global macro, such as the output of the Clock Conditioning Circuit, cannot be demoted.

- No automatic buffering will happen.

Since no automatic buffering happens when a signal is demoted, this net may have a high delay due to large fanout. This may have a negative effect on the quality of the results. Microsemi recommends that the automatic global demotion only be used on small-fanout nets. Use clock networks for high-fanout nets to improve timing and routability.

## **Spine Assignment**

The low power flash device architecture allows the global networks to be segmented and used as clock spines. These spines, also called local clock networks, enable the use of PDC or MVN to assign a signal to a spine.

PDC syntax to promote a net to a spine/local clock:

assign\_local\_clock -net netname -type [quadrant|chip] Tn|Bn|Tn:Bm

If the net is driven by a clock macro, Designer automatically demotes the clock net to a regular net before it is assigned to a spine. Nets driven by a PLL or CLKDLY macro cannot be assigned to a local clock.

When assigning a signal to a spine or quadrant global network using PDC (pre-compile), the Designer software will legalize the shared instances. The number of shared instances to be legalized can be controlled by compile options. If these networks are created in MVN (only quadrant globals can be created), no legalization is done (as it is post-compile). Designer does not do legalization between non-clock nets.

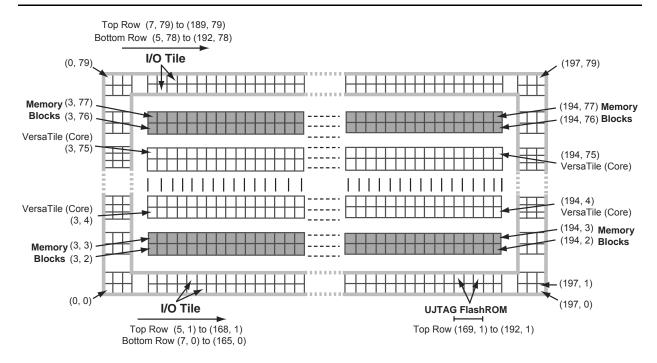

As an example, consider two nets, net\_clk and net\_reset, driving the same flip-flop. The following PDC constraints are used:

#### assign\_local\_clock -net net\_clk -type chip T3

assign\_local\_clock -net net\_reset -type chip T1:T2

During Compile, Designer adds a buffer in the reset net and places it in the T1 or T2 region, and places the flip-flop in the T3 spine region (Figure 3-16).

assign\_local\_clock -net net\_clk -type chip T3 assign\_local\_clock -net net\_reset -type chip T1:T2

Figure 3-16 • Adding a Buffer for Shared Instances

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

Dividers n and m (the input divider and feedback divider, respectively) provide integer frequency division factors from 1 to 128. The output dividers u, v, and w provide integer division factors from 1 to 32. Frequency scaling of the reference clock CLKA is performed according to the following formulas:

$$f_{GLA} = f_{CLKA} \times m / (n \times u) - GLA Primary PLL Output Clock$$

$$EQ 4-1$$

$$f_{GLB} = f_{YB} = f_{CLKA} \times m / (n \times v) - GLB Secondary 1 PLL Output Clock(s)$$

$$EQ 4-2$$

$$f_{GLC} = f_{YC} = f_{CLKA} \times m / (n \times w) - GLC$$

Secondary 2 PLL Output Clock(s)

EQ 4-3

SmartGen provides a user-friendly method of generating the configured PLL netlist, which includes automatically setting the division factors to achieve the closest possible match to the requested frequencies. Since the five output clocks share the *n* and *m* dividers, the achievable output frequencies are interdependent and related according to the following formula:

$$f_{GLA} = f_{GLB} \times (v / u) = f_{GLC} \times (w / u)$$

EQ 4-4

## **Clock Delay Adjustment**

There are a total of seven configurable delay elements implemented in the PLL architecture.

Two of the delays are located in the feedback path, entitled System Delay and Feedback Delay. System Delay provides a fixed delay of 2 ns (typical), and Feedback Delay provides selectable delay values from 0.6 ns to 5.56 ns in 160 ps increments (typical). For PLLs, delays in the feedback path will effectively advance the output signal from the PLL core with respect to the reference clock. Thus, the System and Feedback delays generate negative delay on the output clock. Additionally, each of these delays can be independently bypassed if necessary.

The remaining five delays perform traditional time delay and are located at each of the outputs of the PLL. Besides the fixed global driver delay of 0.755 ns for each of the global networks, the global multiplexer outputs (GLA, GLB, and GLC) each feature an additional selectable delay value, as given in Table 4-7.

| Device                | Typical Starting Values Incremen |               | Increments | Ending Value |

|-----------------------|----------------------------------|---------------|------------|--------------|

| ProASIC3              | 200 ps                           | 0 to 735 ps   | 200 ps     | 6.735 ns     |

| IGLOO/ProASIC3L 1.5 V | 360 ps                           | 0 to 1.610 ns | 360 ps     | 12.410 ns    |

| IGLOO/ProASIC3L 1.2 V | 580 ps                           | 0 to 2.880 ns | 580 ps     | 20.280 ns    |

Table 4-7 • Delay Values in Libero SoC Software per Device Family

The additional YB and YC signals have access to a selectable delay from 0.6 ns to 5.56 ns in 160 ps increments (typical). This is the same delay value as the CLKDLY macro. It is similar to CLKDLY, which bypasses the PLL core just to take advantage of the phase adjustment option with the delay value.

The following parameters must be taken into consideration to achieve minimum delay at the outputs (GLA, GLB, GLC, YB, and YC) relative to the reference clock: routing delays from the PLL core to CCC outputs, core outputs and global network output delays, and the feedback path delay. The feedback path delay acts as a time advance of the input clock and will offset any delays introduced beyond the PLL core output. The routing delays are determined from back-annotated simulation and are configuration-dependent.

When SmartGen is used to define the configuration that will be shifted in via the serial interface, SmartGen prints out the values of the 81 configuration bits. For ease of use, several configuration bits are automatically inferred by SmartGen when the dynamic PLL core is generated; however, <71:73> (STATASEL, STATBSEL, STATCSEL) and <77:79> (DYNASEL, DYNBSEL, DYNCSEL) depend on the input clock source of the corresponding CCC. Users must first run Layout in Designer to determine the exact setting for these ports. After Layout is complete, generate the "CCC\_Configuration" report by choosing **Tools** > **Reports** > **CCC\_Configuration** in the Designer software. Refer to "PLL Configuration Bits Description" on page 106 for descriptions of the PLL configuration bits. For simulation purposes, bits <71:73> and <78:80> are "don't care." Therefore, it is strongly suggested that SmartGen be used to generate the correct configuration bit settings for the dynamic PLL core.

After setting all the required parameters, users can generate one or more PLL configurations with HDL or EDIF descriptions by clicking the **Generate** button. SmartGen gives the option of saving session results and messages in a log file:

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* Macro Parameters

| ****              | -<br>-           |                |

|-------------------|------------------|----------------|

|                   |                  |                |

| Name              | :                | dyn_pll_hardio |

| Family            |                  | ProASIC3E      |

| Output Format     | :                | VERILOG        |

| Туре              |                  | Dynamic CCC    |

| Input Freq(MHz)   |                  | 30.000         |

| CLKA Source       |                  | Hardwired I/O  |

| Feedback Delay N  |                  |                |

| Feedback Mux Sel  |                  | 1              |

| XDLY Mux Select   |                  | No             |

| Primary Freq(MHz  |                  | 33.000         |

| Primary PhaseShi  |                  | 0              |

| Primary Delay Va  |                  |                |

| Primary Mux Sele  |                  | -              |

| Secondary1 Freq(  |                  | 40.000         |

| Use GLB           |                  | YES            |

| Use YB            |                  | NO             |

| GLB Delay Value   |                  | 1              |

| YB Delay Value I  |                  | 1              |

| Secondaryl Phase  |                  | 0              |

| Secondary1 Mux S  |                  | 0              |

| Secondary1 Input  |                  | 40.000         |

| CLKB Source       | <b>1</b> · · · · | Hardwired I/O  |

|                   |                  | 50.000         |

| Secondary2 Freq(  |                  |                |

| Use GLC           |                  | YES<br>NO      |

| Use YC            |                  |                |

| GLC Delay Value   |                  | 1              |

| YC Delay Value I  |                  | 1              |

| Secondary2 Phase  |                  | 0              |

| Secondary2 Mux S  |                  | 0              |

| Secondary2 Input  | -                | 50.000         |

| CLKC Source       | :                | Hardwired I/O  |

| den filmentine pi | h                |                |

| Configuration Bi  |                  |                |

| FINDIV[6:0]       | 0000101          |                |

| FBDIV[6:0]        | 0100000          |                |

|                   | 00100            |                |

|                   | 00000            |                |

| OCDIV[4:0]        | 00000            |                |

| OAMUX[2:0]        | 100              |                |

|                   | 000              |                |

| OCMUX[2:0]        | 000              |                |

|                   | 01               |                |

| FBDLY[4:0]        | 00000            |                |

| XDLYSEL           | 0                |                |

00000

00000

DLYGLA[4:0] DLYGLB[4:0]

# Conclusion

The advanced CCCs of the IGLOO and ProASIC3 devices are ideal for applications requiring precise clock management. They integrate easily with the internal low-skew clock networks and provide flexible frequency synthesis, clock deskewing, and/or time-shifting operations.

# **Related Documents**

## **Application Notes**

Board-Level Considerations http://www.microsemi.com/soc/documents/ALL\_AC276\_AN.pdf

## Datasheets

Fusion Family of Mixed Signal FPGAs http://www.microsemi.com/soc/documents/Fusion\_DS.pdf

## **User's Guides**

IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide http://www.microsemi.com/soc/documents/pa3 libguide ug.pdf

# List of Changes

The following table lists critical changes that were made in each revision of the chapter.

| Date          | Changes                                                                                                                                                                                                                                 | Page             |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| August 2012   | The "Implementing EXTFB in ProASIC3/E Devices" section is new (SAR 36647).                                                                                                                                                              | 86               |

|               | Table 4-7 • Delay Values in Libero SoC Software per Device Family was added to the "Clock Delay Adjustment" section (SAR 22709).                                                                                                        | 102              |

|               | The "Phase Adjustment" section was rewritten to explain better why the visual CCC shows both the actual phase and the actual delay that is equivalent to this phase shift (SAR 29647).                                                  | 103              |

|               | The hyperlink for the <i>Board-Level Considerations</i> application note was corrected (SAR 36663)                                                                                                                                      | 128, 129         |

| December 2011 | Figure 4-20 • PLL Block Diagram, Figure 4-22 • CCC Block Control Bits – Graphical Representation of Assignments, and Table 4-12 • MUXA, MUXB, MUXC were revised to change the phase shift assignments for PLLs 4 through 7 (SAR 33791). | 101,<br>105, 109 |

| June 2011     | The description for RESETEN in Table 4-8 • Configuration Bit Descriptions for the CCC Blocks was revised. The phrase "and should not be modified via dynamic configuration" was deleted because RESETEN is read only (SAR 25949).       | 106              |

| July 2010     | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                               | N/A              |

|               | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                                                                               | N/A              |

Table 7-19 shows some high-level interfacing examples using low power flash devices.

|                    | Clock        |                 |       | I/O          |              |                 |  |

|--------------------|--------------|-----------------|-------|--------------|--------------|-----------------|--|

| Interface          | Туре         | Frequency       | Туре  | Signals In   | Signals Out  | Data I/O        |  |

| GM                 | Src Sync     | 125 MHz         | LVTTL | 8            | 8            | 125 Mbps        |  |

| ТВІ                | Src Sync     | 125 MHz         | LVTTL | 10           | 10           | 125 Mbps        |  |

| XSBI               | Src Sync     | 644 MHz         | LVDS  | 16           | 16           | 644 Mbps        |  |

| XGMI               | Src Sync DDR | 156 MHz         | HSTL1 | 32           | 32           | 312 Mbps        |  |

| FlexBus 3          | Sys Sync     | 104 MHz         | LVTTL | ≤ <b>32</b>  | ≤ <b>32</b>  | ≤ 104           |  |

| Pos-PHY3/SPI-3     | Sys Sync     | 104             | LVTTL | 8, 16, 32    | 8, 16, 32    | $\leq$ 104 Mbps |  |

| FlexBus 4/SPI-4.1  | Src Sync     | 200 MHz         | HSTL1 | 16,64        | 16,64        | 200 Mbps        |  |

| Pos-PHY4/SPI-4.2   | Src Sync DDR | ≥ 311 MHz       | LVDS  | 16           | 16           | $\geq$ 622 Mbps |  |

| SFI-4.1            | Src Sync     | 622 MHz         | LVDS  | 16           | 16           | 622 Mbps        |  |

| CSIX L1            | Sys Sync     | $\leq$ 250 MHz  | HSTL1 | 32,64,96,128 | 32,64,96,128 | $\leq$ 250 Mbps |  |

| Hyper Transport    | Sys Sync DDR | $\leq$ 800 MHz  | LVDS  | 2,4,8,16     | 2,4,8,16     | $\leq$ 1.6 Gbps |  |

| Rapid I/O Parallel | Sys Sync DDR | 250 MHz – 1 GHz | LVDS  | 8,16         | 8,16         | $\leq$ 2 Gbps   |  |

| Star Fabric        | CDR          |                 | LVDS  | 4            | 4            | 622 Mbps        |  |

Table 7-19 • High-Level Interface Examples

Note: Sys Sync = System Synchronous Clocking, Src Sync = Source Synchronous Clocking, and CDR = Clock and Data Recovery.

# Conclusion

IGLOO and ProASIC3 support for multiple I/O standards minimizes board-level components and makes possible a wide variety of applications. The Microsemi Designer software, integrated with Libero SoC, presents a clear visual display of I/O assignments, allowing users to verify I/O and board-level design requirements before programming the device. The IGLOO and ProASIC3 device I/O features and functionalities ensure board designers can produce low-cost and low power FPGA applications fulfilling the complexities of contemporary design needs.

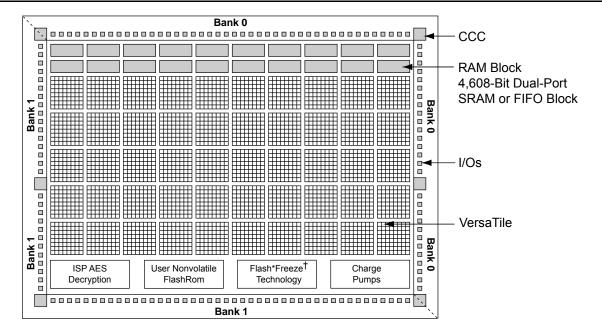

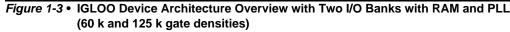

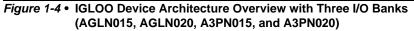

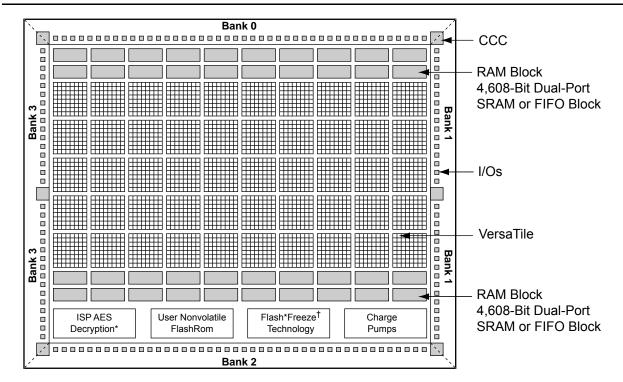

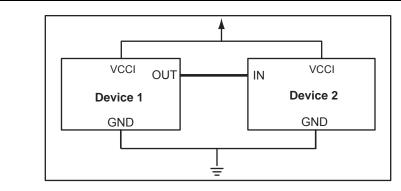

## I/O Bank Structure

Low power flash device I/Os are divided into multiple technology banks. The number of banks is device-dependent. The IGLOOe, ProASIC3EL, and ProASIC3E devices have eight banks (two per side); and IGLOO, ProASIC3L, and ProASIC3 devices have two to four banks. Each bank has its own  $V_{CCI}$  power supply pin. Multiple I/O standards can co-exist within a single I/O bank.

In IGLOOe, ProASIC3EL, and ProASIC3E devices, each I/O bank is subdivided into  $V_{REF}$  minibanks. These are used by voltage-referenced I/Os. VREF minibanks contain 8 to 18 I/Os. All I/Os in a given minibank share a common VREF line (only one VREF pin is needed per VREF minibank). Therefore, if an I/O in a VREF minibank is configured as a VREF pin, the remaining I/Os in that minibank will be able to use the voltage assigned to that pin. If the location of the VREF pin is selected manually in the software, the user must satisfy VREF rules (refer to the "I/O Software Control in Low Power Flash Devices" section on page 251). If the user does not pick the VREF pin manually, the software automatically assigns it.

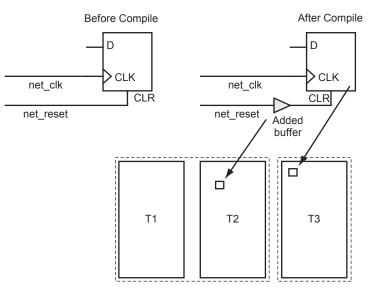

Figure 8-4 is a snapshot of a section of the I/O ring, showing the basic elements of an I/O tile, as viewed from the Designer place-and-route tool's MultiView Navigator (MVN).

Figure 8-4 • Snapshot of an I/O Tile

Low power flash device I/Os are implemented using two tile types: I/O and differential I/O (diffio).

The diffio tile is built up using two I/O tiles, which form an I/O pair (P side and N side). These I/O pairs are used according to differential I/O standards. Both the P and N sides of the diffio tile include an I/O buffer and two I/O logic blocks (auxiliary and main logic).

Every minibank (E devices only) is built up from multiple diffio tiles. The number of the minibank depends on the different-size dies. Refer to the "Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E" section on page 215 for an illustration of the minibank structure.

Figure 8-5 on page 222 shows a simplified diagram of the I/O buffer circuitry. The Output Enable signal (OE) enables the output buffer to pass the signal from the core logic to the pin. The output buffer contains ESD protection circuitry, an n-channel transistor that shunts all ESD surges (up to the limit of the device ESD specification) to GND. This transistor also serves as an output pull-down resistor.

Each output buffer also contains programmable slew rate, drive strength, programmable power-up state (pull-up/-down resistor), hot-swap, 5 V tolerance, and clamp diode control circuitry. Multiple flash switches (not shown in Figure 8-5 on page 222) are programmed by user selections in the software to activate different I/O features.

# I/O Standards

## **Single-Ended Standards**

These I/O standards use a push-pull CMOS output stage with a voltage referenced to system ground to designate logical states. The input buffer configuration, output drive, and I/O supply voltage ( $V_{CCI}$ ) vary among the I/O standards (Figure 8-6).

#### *Figure 8-6 •* Single-Ended I/O Standard Topology

The advantage of these standards is that a common ground can be used for multiple I/Os. This simplifies board layout and reduces system cost. Their low-edge-rate (dv/dt) data transmission causes less electromagnetic interference (EMI) on the board. However, they are not suitable for high-frequency (>200 MHz) switching due to noise impact and higher power consumption.

## LVTTL (Low-Voltage TTL)

This is a general-purpose standard (EIA/JESD8-B) for 3.3 V applications. It uses an LVTTL input buffer and a push-pull output buffer. The LVTTL output buffer can have up to six different programmable drive strengths. The default drive strength is 12 mA. VCCI is 3.3 V. Refer to "I/O Programmable Features" on page 227 for details.

## LVCMOS (Low-Voltage CMOS)

The low power flash devices provide four different kinds of LVCMOS: LVCMOS 3.3 V, LVCMOS 2.5 V, LVCMOS 1.8 V, and LVCMOS 1.5 V. LVCMOS 3.3 V is an extension of the LVCMOS standard (JESD8-B-compliant) used for general-purpose 3.3 V applications. LVCMOS 2.5 V is an extension of the LVCMOS standard (JESD8-5-compliant) used for general-purpose 2.5 V applications. LVCMOS 2.5 V for the 30 k gate devices has a clamp diode to VCCI, but for all other devices there is no clamp diode.

There is yet another standard supported by IGLOO and ProASIC3 devices (except A3P030): LVCMOS 2.5/5.0 V. This standard is similar to LVCMOS 2.5 V, with the exception that it can support up to 3.3 V on the input side (2.5 V output drive).

LVCMOS 1.8 V is an extension of the LVCMOS standard (JESD8-7–compliant) used for general-purpose 1.8 V applications. LVCMOS 1.5 V is an extension of the LVCMOS standard (JESD8-11–compliant) used for general-purpose 1.5 V applications.

The VCCI values for these standards are 3.3 V, 2.5 V, 1.8 V, and 1.5 V, respectively. Like LVTTL, the output buffer has up to seven different programmable drive strengths (2, 4, 6, 8, 12, 16, and 24 mA). Refer to "I/O Programmable Features" on page 227 for details.

### 3.3 V PCI (Peripheral Component Interface)

This standard specifies support for both 33 MHz and 66 MHz PCI bus applications. It uses an LVTTL input buffer and a push-pull output buffer. With the aid of an external resistor, this I/O standard can be 5 V–compliant for low power flash devices. It does not have programmable drive strength.

### 3.3 V PCI-X (Peripheral Component Interface Extended)

An enhanced version of the PCI specification, 3.3 V PCI-X can support higher average bandwidths; it increases the speed that data can move within a computer from 66 MHz to 133 MHz. It is backward-

I/O Structures in IGLOOe and ProASIC3E Devices

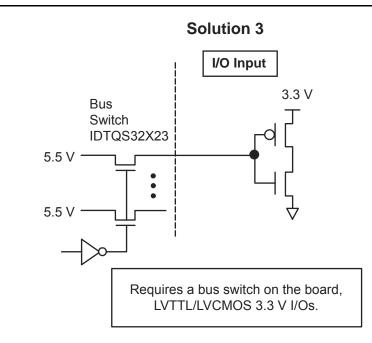

#### Solution 3

The board-level design must ensure that the reflected waveform at the pad does not exceed the voltage overshoot/undershoot limits provided in the datasheet. This is a requirement to ensure long-term reliability.

This scheme will also work for a 3.3 V PCI/PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the bus switch, as shown in Figure 8-12. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

Figure 8-12 • Solution 3

DDR for Microsemi's Low Power Flash Devices

```

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

TRIBUFF_F_8U_0_inst : TRIBUFF_F_8U

port map(D => Q, E => TrienAux, PAD => PAD);

```

end DEF\_ARCH;

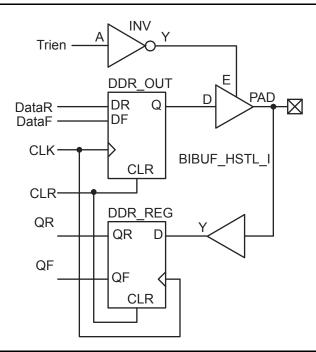

## **DDR Bidirectional Buffer**

Figure 10-8 • DDR Bidirectional Buffer, LOW Output Enable (HSTL Class II)

#### Verilog

module DDR\_BiDir\_HSTL\_I\_LowEnb(DataR,DataF,CLR,CLK,Trien,QR,QF,PAD);

```

input DataR, DataF, CLR, CLK, Trien;

output QR, QF;

inout PAD;

wire TrienAux, D, Q;

INV Inv_Tri(.A(Trien), .Y(TrienAux));

DDR_OUT DDR_OUT_0_inst(.DR(DataR),.DF(DataF),.CLK(CLK),.CLR(CLR),.Q(Q));

DDR_REG DDR_REG_0_inst(.D(D),.CLK(CLK),.CLR(CLR),.QR(QR),.QF(QF));

BIBUF_HSTL_I BIBUF_HSTL_I_0_inst(.PAD(PAD),.D(Q),.E(TrienAux),.Y(D));

```

endmodule

Security in Low Power Flash Devices

Figure 12-10 • All Silicon Features Selected for IGLOO and ProASIC3 Devices

Figure 12-11 • All Silicon Features Selected for Fusion

Note: The settings in this figure are used to show the generation of an AES-encrypted programming file for the FPGA array, FlashROM, and FB contents. One or all locations may be selected for encryption.

#### Figure 12-17 • Settings to Program a Device Secured with FlashLock and using AES Encryption

Choose the **High** security level to reprogram devices using both the FlashLock Pass Key and AES key protection (Figure 12-18 on page 321). Enter the AES key and click **Next**.

A device that has already been secured with FlashLock and has an AES key loaded must recognize the AES key to program the device and generate a valid bitstream in authentication. The FlashLock Key is only required to unlock the device and change the security settings.

This is what makes it possible to program in an untrusted environment. The AES key is protected inside the device by the FlashLock Key, so you can only program if you have the correct AES key. In fact, the AES key is not in the programming file either. It is the key used to encrypt the data in the file. The same key previously programmed with the FlashLock Key matches to decrypt the file.

An AES-encrypted file programmed to a device without FlashLock would not be secure, since without FlashLock to protect the AES key, someone could simply reprogram the AES key first, then program with any AES key desired or no AES key at all. This option is therefore not available in the software.

Power-Up/-Down Behavior of Low Power Flash Devices

## **Internal Pull-Up and Pull-Down**

Low power flash device I/Os are equipped with internal weak pull-up/-down resistors that can be used by designers. If used, these internal pull-up/-down resistors will be activated during power-up, once both VCC and VCCI are above their functional activation level. Similarly, during power-down, these internal pull-up/-down resistors will turn off once the first supply voltage falls below its brownout deactivation level.

# **Cold-Sparing**

In cold-sparing applications, voltage can be applied to device I/Os before and during power-up. Coldsparing applications rely on three important characteristics of the device:

- 1. I/Os must be tristated before and during power-up.

- 2. Voltage applied to the I/Os must not power up any part of the device.

- 3. VCCI should not exceed 3.6 V, per datasheet specifications.

As described in the "Power-Up to Functional Time" section on page 378, Microsemi's low power flash I/Os are tristated before and during power-up until the last voltage supply (VCC or VCCI) is powered up past its functional level. Furthermore, applying voltage to the FPGA I/Os does not pull up VCC or VCCI and, therefore, does not partially power up the device. Table 18-4 includes the cold-sparing test results on A3PE600-PQ208 devices. In this test, leakage current on the device I/O and residual voltage on the power supply rails were measured while voltage was applied to the I/O before power-up.

|            | Residual Voltage (V) |       |                 |

|------------|----------------------|-------|-----------------|

| Device I/O | VCC                  | VCCI  | Leakage Current |

| Input      | 0                    | 0.003 | <1 µA           |

| Output     | 0                    | 0.003 | <1 µA           |

Table 18-4 • Cold-Sparing Test Results for A3PE600 Devices

VCCI must not exceed 3.6 V, as stated in the datasheet specification. Therefore, ProASIC3E devices meet all three requirements stated earlier in this section and are suitable for cold-sparing applications. The following devices and families support cold-sparing:

IGLOO: AGL015 and AGL030

- All IGLOO nano

- All IGLOO PLUS

- All IGLOOe

- ProASIC3L: A3PE3000L

- ProASIC3: A3P015 and A3P030

- All ProASIC3 nano

- All ProASIC3E

- Military ProASIC3EL: A3PE600L and A3PE3000L

- RT ProASIC3: RT3PE600L and RT3PE3000L