Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                     |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 110592                                                                     |

| Number of I/O                  | 235                                                                        |

| Number of Gates                | 600000                                                                     |

| Voltage - Supply               | 1.14V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                            |

| Package / Case                 | 484-BGA                                                                    |

| Supplier Device Package        | 484-FPBGA (23x23)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3p600l-1fg484 |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table of Contents

|    | Boundary Scan Chain                                       |     |

|----|-----------------------------------------------------------|-----|

|    | Board-Level Recommendations                               |     |

|    | Advanced Boundary Scan Register Settings                  |     |

|    | List of Changes                                           | 362 |

| 17 | UJTAG Applications in Microsemi's Low Power Flash Devices | 363 |

|    | Introduction                                              | 363 |

|    | UJTAG Support in Flash-Based Devices                      | 364 |

|    | UJTAG Macro                                               | 365 |

|    | UJTAG Operation                                           | 366 |

|    | Typical UJTAG Applications                                | 368 |

|    | Conclusion                                                | 372 |

|    | Related Documents                                         | 372 |

|    | List of Changes                                           | 372 |

| 18 | Power-Up/-Down Behavior of Low Power Flash Devices        | 373 |

|    | Introduction                                              | 373 |

|    | Flash Devices Support Power-Up Behavior                   | 374 |

|    | Power-Up/-Down Sequence and Transient Current             | 375 |

|    | I/O Behavior at Power-Up/-Down                            | 377 |

|    | Cold-Sparing                                              | 382 |

|    | Hot-Swapping                                              | 383 |

|    | Conclusion                                                | 383 |

|    | Related Documents                                         | 384 |

|    | List of Changes                                           | 384 |

| А  | Summary of Changes.                                       | 385 |

|    | History of Revision to Chapters                           | 385 |

| B  | Product Support                                           | 387 |

| Б  | Customer Service                                          |     |

|    | Customer Technical Support Center                         |     |

|    | Technical Support                                         |     |

|    | Website                                                   |     |

|    | Contacting the Customer Technical Support Center          |     |

|    | ITAR Technical Support                                    |     |

|    |                                                           | 500 |

|    | Index                                                     | 389 |

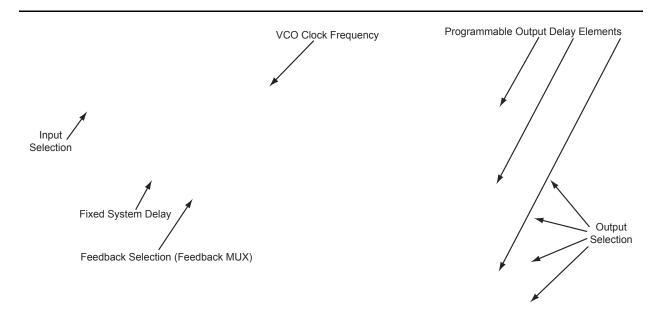

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## **Software Configuration**

SmartGen automatically generates the desired CCC functional block by configuring the control bits, and allows the user to select two CCC modes: Static PLL and Delayed Clock (CLKDLY).

## **Static PLL Configuration**

The newly implemented Visual PLL Configuration Wizard feature provides the user a quick and easy way to configure the PLL with the desired settings (Figure 4-23). The user can invoke SmartGen to set the parameters and generate the netlist file with the appropriate flash configuration bits set for the CCCs. As mentioned in "PLL Macro Block Diagram" on page 85, the input reference clock CLKA can be configured to be driven by Hardwired I/O, External I/O, or Core Logic. The user enters the desired settings for all the parameters (output frequency, output selection, output phase adjustment, clock delay, feedback delay, and system delay). Notice that the actual values (divider values, output frequency, delay values, and phase) are shown to aid the user in reaching the desired design frequency in real time. These values are typical-case data. Best- and worst-case data can be observed through static timing analysis in SmartTime within Designer.

For dynamic configuration, the CCC parameters are defined using either the external JTAG port or an internally defined serial interface via the built-in dynamic shift register. This feature provides the ability to compensate for changes in the external environment.

Figure 4-23 • Visual PLL Configuration Wizard

ProASIC3L FPGA Fabric User's Guide

| Date                   | Changes                                                                                                                                                                                                                                                                                  | Page |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| v1.2<br>(June 2008)    | <ul> <li>The following changes were made to the family descriptions in Figure 4-1 • Overview of the CCCs Offered in Fusion, IGLOO, and ProASIC3:</li> <li>• ProASIC3L was updated to include 1.5 V.</li> <li>• The number of PLLs for ProASIC3E was changed from five to six.</li> </ul> | 77   |

| v1.1<br>(March 2008)   | Table 4-1 • Flash-Based FPGAs and the associated text were updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                         | 79   |

|                        | The "Global Input Selections" section was updated to include 15 k gate devices as supported I/O types for globals, for CCC only.                                                                                                                                                         | 87   |

|                        | Table 4-5 • Number of CCCs by Device Size and Package was revised to include ProASIC3L, IGLOO PLUS, A3P015, AGL015, AGLP030, AGLP060, and AGLP125.                                                                                                                                       | 94   |

|                        | The "IGLOO and ProASIC3 CCC Locations" section was revised to include 15 k gate devices in the exception statements, as they do not contain PLLs.                                                                                                                                        | 97   |

| v1.0<br>(January 2008) | Information about unlocking the PLL was removed from the "Dynamic PLL Configuration" section.                                                                                                                                                                                            | 103  |

|                        | In the "Dynamic PLL Configuration" section, information was added about running Layout and determining the exact setting of the ports.                                                                                                                                                   | 116  |

|                        | In Table 4-8 • Configuration Bit Descriptions for the CCC Blocks, the following bits were updated to delete "transport to the user" and reference the footnote at the bottom of the table: 79 to 71.                                                                                     | 106  |

FlashROM in Microsemi's Low Power Flash Devices

# **FlashROM Applications**

The SmartGen core generator is used to configure FlashROM content. You can configure each page independently. SmartGen enables you to create and modify regions within a page; these regions can be 1 to 16 bytes long (Figure 5-4).

|          |   |    | Byte Number in Page |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----------|---|----|---------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|          |   | 15 | 14                  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|          | 7 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| <u> </u> | 6 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| he       | 5 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Numb     | 4 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| ۵<br>ا   | 3 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Pag      | 2 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| а.       | 1 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|          | 0 |    |                     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

### Figure 5-4 • FlashROM Configuration

The FlashROM content can be changed independently of the FPGA core content. It can be easily accessed and programmed via JTAG, depending on the security settings of the device. The SmartGen core generator enables each region to be independently updated (described in the "Programming and Accessing FlashROM" section on page 138). This enables you to change the FlashROM content on a per-part basis while keeping some regions "constant" for all parts. These features allow the FlashROM to be used in diverse system applications. Consider the following possible uses of FlashROM:

- Internet protocol (IP) addressing (wireless or fixed)

- System calibration settings

- Restoring configuration after unpredictable system power-down

- · Device serialization and/or inventory control

- Subscription-based business models (e.g., set-top boxes)

- Secure key storage

- Asset management tracking

- Date stamping

- Version management

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

#### Table 6-2 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

| WIDTHA[1:0] | WIDTHB[1:0] | D×W   |

|-------------|-------------|-------|

| 00          | 00          | 4k×1  |

| 01          | 01          | 2k×2  |

| 10          | 10          | 1k×4  |

| 11          | 11          | 512×9 |

Note: The aspect ratio settings are constant and cannot be changed on the fly.

### BLKA and BLKB

These signals are active-low and will enable the respective ports when asserted. When a BLKx signal is deasserted, that port's outputs hold the previous value.

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, BLKB should be tied to ground.

#### WENA and WENB

These signals switch the RAM between read and write modes for the respective ports. A LOW on these signals indicates a write operation, and a HIGH indicates a read.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WENB should be tied to ground.

### **CLKA and CLKB**

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

Note: For Automotive ProASIC3 devices, dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). For use of this macro as a single-port SRAM, the inputs and clock of one port should be tied off (grounded) to prevent errors during design compile.

### PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A LOW on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the corresponding output in the next clock cycle.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, PIPEB should be tied to ground. For use in dual-port mode, the same clock with an inversion between the two clock pins of the macro should be used in the design to prevent errors during compile.

#### WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A LOW on these signals makes the output retain data from the previous read. A HIGH indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WMODEB should be tied to ground.

#### RESET

This active-low signal resets the control logic, forces the output hold state registers to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory array.

While the RESET signal is active, read and write operations are disabled. As with any asynchronous reset signal, care must be taken not to assert it too close to the edges of active read and write clocks.

### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 6-3 on page 155).

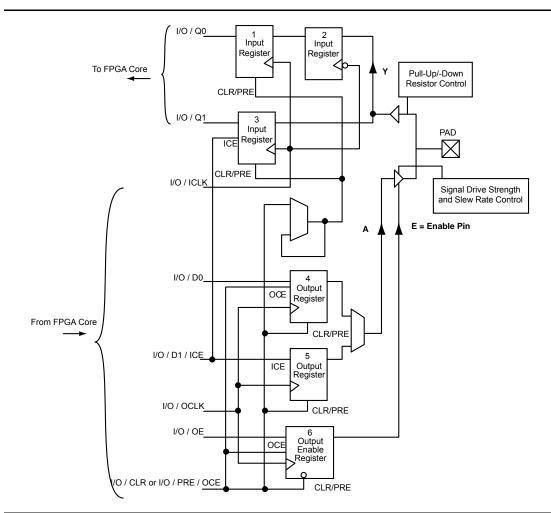

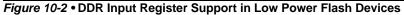

## I/O Architecture

## I/O Tile

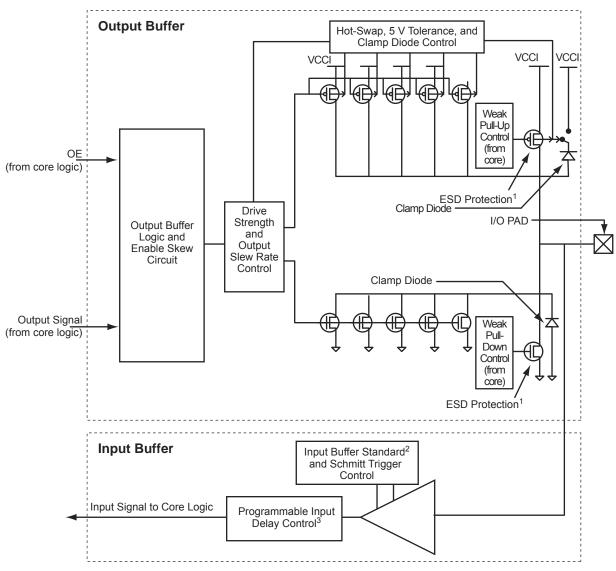

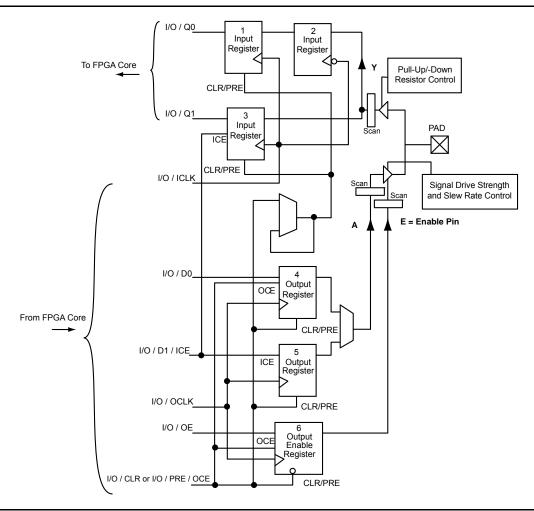

The I/O tile provides a flexible, programmable structure for implementing a large number of I/O standards. In addition, the registers available in the I/O tile can be used to support high-performance register inputs and outputs, with register enable if desired (Figure 7-2). The registers can also be used to support the JESD-79C Double Data Rate (DDR) standard within the I/O structure (see the "DDR for Microsemi's Low Power Flash Devices" section on page 271 for more information). In addition, the registers available in the I/O tile can be used to support high-performance register inputs and outputs, with register enable if desired (Figure 7-2).

As depicted in Figure 7-2, all I/O registers share one CLR port. The output register and output enable register share one CLK port.

Figure 7-2 • DDR Configured I/O Block Logical Representation

### Notes:

- 1. All NMOS transistors connected to the I/O pad serve as ESD protection.

- 2. See Table 7-2 on page 177 for available I/O standards.

3. Programmable input delay is applicable only to ProASIC3EL and RT ProASIC3 devices.

Figure 7-4 • Simplified I/O Buffer Circuitry

### I/O Registers

Each I/O module contains several input, output, and enable registers. Refer to Figure 7-4 for a simplified representation of the I/O block. The number of input registers is selected by a set of switches (not shown in Figure 7-2 on page 181) between registers to implement single-ended or differential data transmission to and from the FPGA core. The Designer software sets these switches for the user. A common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. Input Register 2 does not have a CLR/PRE pin, as this register is used for DDR implementation. The I/O register combining must satisfy certain rules.

### Table 7-8 • Hot-Swap Level 1

| Description                              | Cold-swap                                                                                                                                                                                                                                     |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | No                                                                                                                                                                                                                                            |

| Bus State                                | -                                                                                                                                                                                                                                             |

| Card Ground Connection                   | -                                                                                                                                                                                                                                             |

| Device Circuitry Connected to Bus Pins   | -                                                                                                                                                                                                                                             |

| Example Application                      | System and card with Microsemi FPGA chip are<br>powered down, and the card is plugged into the<br>system. Then the power supplies are turned on for<br>the system but not for the FPGA on the card.                                           |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices: Compliant<br>Other IGLOO/ProASIC3 devices: Compliant if bus<br>switch used to isolate FPGA I/Os from rest of<br>system<br>IGLOOe/ProASIC3E devices: Compliant I/Os can<br>but do not have to be set to hot-insertion mode. |

Table 7-9 • Hot-Swap Level 2

| Description                              | Hot-swap while reset                                                                                                                                                  |  |  |  |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Power Applied to Device                  | Yes                                                                                                                                                                   |  |  |  |  |

| Bus State                                | Held in reset state                                                                                                                                                   |  |  |  |  |

| Card Ground Connection                   | Reset must be maintained for 1 ms before, during and after insertion/removal.                                                                                         |  |  |  |  |

| Device Circuitry Connected to Bus Pins   | -                                                                                                                                                                     |  |  |  |  |

| Example Application                      | In the PCI hot-plug specification, reset control circuitry isolates the card busses until the card supplies are at their nominal operating levels and stable.         |  |  |  |  |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices, all IGLOOe/ProASIC3E<br>devices: Compliant I/Os can but do not have to be<br>set to hot-insertion mode.<br>Other IGLOO/ProASIC3 devices: Compliant |  |  |  |  |

# 8 – I/O Structures in IGLOOe and ProASIC3E Devices

## Introduction

Low power flash devices feature a flexible I/O structure, supporting a range of mixed voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V) through bank-selectable voltages. IGLOO<sup>®</sup>e, ProASIC<sup>®</sup>3EL, and ProASIC3E families support Pro I/Os.

Users designing I/O solutions are faced with a number of implementation decisions and configuration choices that can directly impact the efficiency and effectiveness of their final design. The flexible I/O structure, supporting a wide variety of voltages and I/O standards, enables users to meet the growing challenges of their many diverse applications. The Libero SoC software provides an easy way to implement I/O that will result in robust I/O design.

This document first describes the two different I/O types in terms of the standards and features they support. It then explains the individual features and how to implement them in Libero SoC.

Figure 8-1 • DDR Configured I/O Block Logical Representation

I/O Structures in IGLOOe and ProASIC3E Devices

# Low Power Flash Device I/O Support

The low power flash FPGAs listed in Table 8-1 support I/Os and the functions described in this document.

#### Table 8-1 • Flash-Based FPGAs

| Series                                                  | Family <sup>*</sup> | Description                                                              |

|---------------------------------------------------------|---------------------|--------------------------------------------------------------------------|

| IGLOO                                                   | IGLOOe              | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |

| ProASIC3                                                | ProASIC3E           | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |

|                                                         | ProASIC3L           | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |

| Military ProASIC3/EL Military temperature A3PE600L, A3P |                     | Military temperature A3PE600L, A3P1000, and A3PE3000L                    |

|                                                         | RT ProASIC3         | Radiation-tolerant RT3PE600L and RT3PE3000L                              |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

I/O Structures in IGLOOe and ProASIC3E Devices

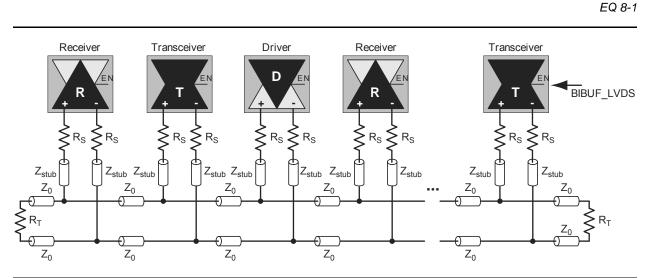

## B-LVDS/M-LVDS

Bus LVDS (B-LVDS) refers to bus interface circuits based on LVDS technology. Multipoint LVDS (M-LVDS) specifications extend the LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The driver requires series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus, since the driver can be located anywhere on the bus. These configurations can be implemented using TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 8-9. The input and output buffer delays are available in the LVDS sections in the datasheet.

Example: For a bus consisting of 20 equidistant loads, the terminations given in EQ 8-1 provide the required differential voltage, in worst case industrial operating conditions, at the farthest receiver:

$R_S = 60 \Omega$ ,  $R_T = 70 \Omega$ , given  $Z_O = 50 \Omega$  (2") and  $Z_{stub} = 50 \Omega$  (~1.5").

Figure 8-9 • A B-LVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

I/O Structures in IGLOOe and ProASIC3E Devices

## Conclusion

IGLOOe and ProASIC3E support for multiple I/O standards minimizes board-level components and makes possible a wide variety of applications. The Microsemi Designer software, integrated with Libero SoC, presents a clear visual display of I/O assignments, allowing users to verify I/O and board-level design requirements before programming the device. The IGLOOe and ProASIC3E device I/O features and functionalities ensure board designers can produce low-cost and low power FPGA applications fulfilling the complexities of contemporary design needs.

## **Related Documents**

## **Application Notes**

Board-Level Considerations http://www.microsemi.com/soc/documents/ALL\_AC276\_AN.pdf

## **User's Guides**

ProASIC3 FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/PA3\_UG.pdf ProASIC3E FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/PA3E\_UG.pdf IGLOOe FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/IGLOOe\_UG.pdf Libero SoC User's Guide http://www.microsemi.com/soc/documents/libero\_ug.pdf IGLOO, Fusion, and ProASIC3 Macro Library Guide http://www.microsemi.com/soc/documents/pa3\_libguide\_ug.pdf SmartGen Core Reference Guide http://www.microsemi.com/soc/documents/genguide\_ug.pdf

I/O Software Control in Low Power Flash Devices

# **List of Changes**

The following table lists critical changes that were made in each revision of the document.

| Date                    | Changes                                                                                                                                                                         | Page |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| August 2012             | The notes in Table 9-2 • Designer State (resulting from I/O attribute modification) were revised to clarify which device families support programmable input delay (SAR 39666). | 253  |

| June 2011               | Figure 9-2 • SmartGen Catalog was updated (SAR 24310). Figure 8-3 • Expanded I/O Section and the step associated with it were deleted to reflect changes in the software.       | 254  |

|                         | The following rule was added to the "VREF Rules for the Implementation of Voltage-Referenced I/O Standards" section:                                                            | 265  |

|                         | Only minibanks that contain input or bidirectional I/Os require a VREF. A VREF is not needed for minibanks composed of output or tristated I/Os (SAR 24310).                    |      |

| July 2010               | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                       | N/A  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 9-1 • Flash-Based FPGAs.                                                                                               | 252  |

|                         | The notes for Table 9-2 • Designer State (resulting from I/O attribute modification) were revised to indicate that skew control and input delay do not apply to nano devices.   | 253  |

| v1.3<br>(October 2008)  | The "Flash FPGAs I/O Support" section was revised to include new families and make the information more concise.                                                                | 252  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 9-1 • Flash-<br>Based FPGAs:                                                                                | 252  |

|                         | ProASIC3L was updated to include 1.5 V.                                                                                                                                         |      |

|                         | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                  |      |

| v1.1<br>(March 2008)    | This document was previously part of the <i>I/O Structures in IGLOO and ProASIC3 Devices</i> document. The content was separated and made into a new document.                  | N/A  |

|                         | Table 9-2 • Designer State (resulting from I/O attribute modification) was updated to include note 2 for IGLOO PLUS.                                                            | 253  |

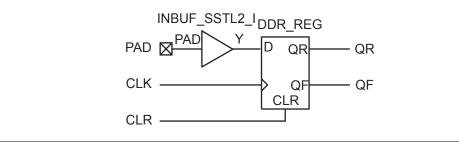

# Input Support for DDR

The basic structure to support a DDR input is shown in Figure 10-2. Three input registers are used to capture incoming data, which is presented to the core on each rising edge of the I/O register clock. Each I/O tile supports DDR inputs.

# **Output Support for DDR**

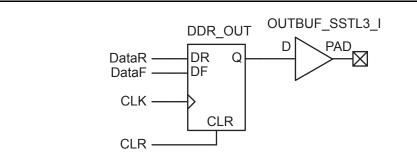

The basic DDR output structure is shown in Figure 10-1 on page 271. New data is presented to the output every half clock cycle.

Note: DDR macros and I/O registers do not require additional routing. The combiner automatically recognizes the DDR macro and pushes its registers to the I/O register area at the edge of the chip. The routing delay from the I/O registers to the I/O buffers is already taken into account in the DDR macro.

Figure 10-3 • DDR Output Register (SSTL3 Class I)

# List of Changes

| Date                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                     |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                                                                                                                                                                                      | N/A                      |

|                         | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                                                                                                                                                                                                                                                                                                                                      | N/A                      |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 10-1 • Flash-Based FPGAs.                                                                                                                                                                                                                                                                                                                                                                                                             | 272                      |

|                         | The "I/O Cell Architecture" section was updated with information applicable to nano devices.                                                                                                                                                                                                                                                                                                                                                                                                   | 273                      |

|                         | The output buffer (OUTBUF_SSTL3_I) input was changed to D, instead of Q, in Figure 10-1 • DDR Support in Low Power Flash Devices, Figure 10-3 • DDR Output Register (SSTL3 Class I), Figure 10-6 • DDR Output Register (SSTL3 Class I), Figure 10-7 • DDR Tristate Output Register, LOW Enable, 8 mA, Pull-Up (LVTTL), and the output from the DDR_OUT macro was connected to the input of the TRIBUFF macro in Figure 10-7 • DDR Tristate Output Register, LOW Enable, 8 mA, Pull-Up (LVTTL). | 271,<br>275,<br>278, 279 |

| v1.3<br>(October 2008)  | The "Double Data Rate (DDR) Architecture" section was updated to include mention of the AFS600 and AFS1500 devices.                                                                                                                                                                                                                                                                                                                                                                            | 271                      |

|                         | The "DDR Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                                                                                                                                                                                                    | 272                      |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 10-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul>                                                                                                                                                                                                                                                     | 272                      |

| v1.1<br>(March 2008)    | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                                                                                                                                                                                                                                                                    | 272                      |

The following table lists critical changes that were made in each revision of the chapter.

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

errors, but this list is intended to show where problems can occur. FlashPro4/3/3X allows TCK to be lowered from 6 MHz down to 1 MHz to allow you to address some signal integrity problems that may occur with impedance mismatching at higher frequencies. Customers are expected to troubleshoot board-level signal integrity issues by measuring voltages and taking scope plots.

### Scan Chain Failure

Normally, the FlashPro4/3/3X Scan Chain command expects to see 0x1 on the TDO pin. If the command reports reading 0x0 or 0x3, it is seeing the TDO pin stuck at 0 or 1. The only time the TDO pin comes out of tristate is when the JTAG TAP state machine is in the Shift-IR or Shift-DR state. If noise or reflections on the TCK or TMS lines have disrupted the correct state transitions, the device's TAP state controller might not be in one of these two states when the programmer tries to read the device. When this happens, the output is floating when it is read and does not match the expected data value. This can also be caused by a broken TDO net. Only a small amount of data is read from the device during the Scan Chain command, so marginal problems may not always show up during this command. Occasionally a faulty programmer can cause intermittent scan chain failures.

### Exit 11

This error occurs during the verify stage of programming a device. After programming the design into the device, the device is verified to ensure it is programmed correctly. The verification is done by shifting the programming data into the device. An internal comparison is performed within the device to verify that all switches are programmed correctly. Noise induced by poor signal integrity can disrupt the writes and reads or the verification process and produce a verification error. While technically a verification error, the root cause is often related to signal integrity.

Refer to the *FlashPro User's Guide* for other error messages and solutions. For the most up-to-date known issues and solutions, refer to http://www.microsemi.com/soc/support.

## Conclusion

IGLOO, ProASIC3, SmartFusion, and Fusion devices offer a low-cost, single-chip solution that is live at power-up through nonvolatile flash technology. The FlashLock Pass Key and 128-bit AES Key security features enable secure ISP in an untrusted environment. On-chip FlashROM enables a host of new applications, including device serialization, subscription-based applications, and IP addressing. Additionally, as the FlashROM is nonvolatile, all of these services can be provided without battery backup.

## **Related Documents**

### **User's Guides**

FlashPro User's Guide http://www.microsemi.com/soc/documents/flashpro\_ug.pdf

## STAPL vs. DirectC

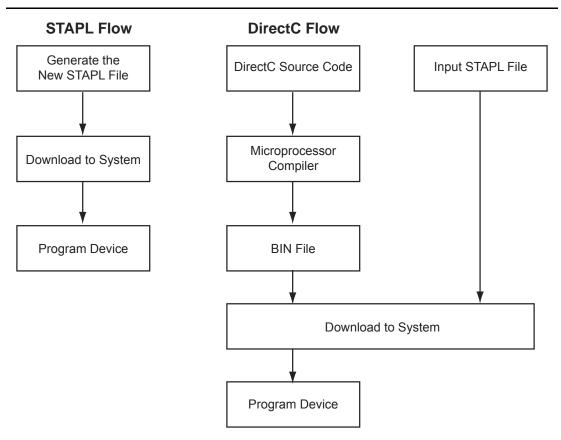

Programming the low power flash devices is performed using DirectC or the STAPL player. Both tools use the STAPL file as an input. DirectC is a compiled language, whereas STAPL is an interpreted language. Microprocessors will be able to load the FPGA using DirectC much more quickly than STAPL. This speed advantage becomes more apparent when lower clock speeds of 8- or 16-bit microprocessors are used. DirectC also requires less memory than STAPL, since the programming algorithm is directly implemented. STAPL does have one advantage over DirectC—the ability to upgrade. When a new programming algorithm is required, the STAPL user simply needs to regenerate a STAPL file using the latest version of the Designer software and download it to the system. The DirectC user must download the latest version of DirectC from Microsemi, compile everything, and download the result into the system (Figure 15-4).

Figure 15-4 • STAPL vs. DirectC

Microprocessor Programming of Microsemi's Low Power Flash Devices

# List of Changes

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                             | Page |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| September 2012          | The "Security" section was modified to clarify that Microsemi does not support read-back of FPGA core-programmed data (SAR 41235).                                                                                                                  | 354  |  |  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                           |      |  |  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 15-1 • Flash-<br>Based FPGAs.                                                                                                                                                              | 350  |  |  |

| v1.3<br>(October 2008)  | The "Microprocessor Programming Support in Flash Devices" section was revised to include new families and make the information more concise.                                                                                                        | 350  |  |  |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 15-1 •</li> <li>Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul> | 350  |  |  |

| v1.1<br>(March 2008)    | The "Microprocessor Programming Support in Flash Devices" section was updated to include information on the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                          | 350  |  |  |

Boundary Scan in Low Power Flash Devices

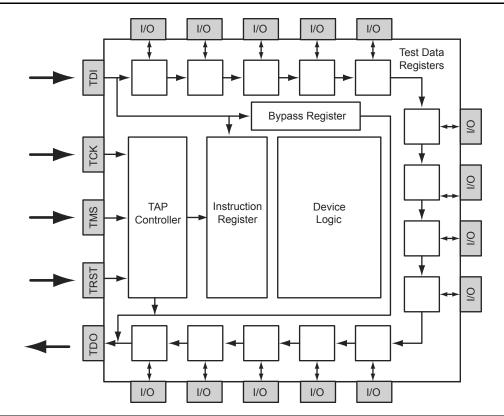

Figure 16-2 • Boundary Scan Chain

## **Board-Level Recommendations**

Table 16-3 gives pull-down recommendations for the TRST and TCK pins.

### Table 16-3 • TRST and TCK Pull-Down Recommendations

| VJTAG          | Tie-Off Resistance* |

|----------------|---------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ       |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ       |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ       |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ       |

| VJTAG at 1.2 V | TBD                 |

Note: Equivalent parallel resistance if more than one device is on JTAG chain (Figure 16-3)

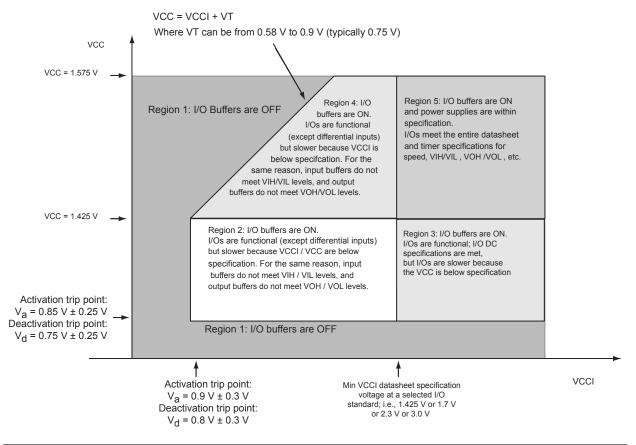

Figure 18-4 • I/O State as a Function of VCCI and VCC Voltage Levels for IGLOO V5, IGLOO nano V5, IGLOO PLUS V5, ProASIC3L, and ProASIC3 Devices Running at VCC = 1.5 V ± 0.075 V