Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Active                                                                       |

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | -                                                                            |

| Total RAM Bits                 | 110592                                                                       |

| Number of I/O                  | 235                                                                          |

| Number of Gates                | 600000                                                                       |

| Voltage - Supply               | 1.14V ~ 1.575V                                                               |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 484-BGA                                                                      |

| Supplier Device Package        | 484-FPBGA (23x23)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3p600l-1fgg484i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 – Flash\*Freeze Technology and Low Power Modes

### Flash\*Freeze Technology and Low Power Modes

Microsemi IGLOO,<sup>®</sup> IGLOO nano, IGLOO PLUS, ProASIC<sup>®</sup>3L, and Radiation-Tolerant (RT) ProASIC3 FPGAs with Flash\*Freeze technology are designed to meet the most demanding power and area challenges of today's portable electronics products with a reprogrammable, small-footprint, full-featured flash FPGA. These devices offer lower power consumption in static and dynamic modes, utilizing the unique Flash\*Freeze technology, than any other FPGA or CPLD.

IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 devices offer various power-saving modes that enable every system to utilize modes that achieve the lowest total system power. Low Power Active capability (static idle) allows for ultra-low power consumption while the device is operational in the system by maintaining SRAM, registers, I/Os, and logic functions.

Flash\*Freeze technology provides an ultra-low power static mode (Flash\*Freeze mode) that retains all SRAM and register information with rapid recovery to Active (operating) mode. IGLOO nano and IGLOO PLUS devices have an additional feature when operating in Flash\*Freeze mode, allowing them to retain I/O states as well as SRAM and register states. This mechanism enables the user to quickly (within 1  $\mu$ s) enter and exit Flash\*Freeze mode by activating the Flash\*Freeze (FF) pin while all power supplies are kept in their original states. In addition, I/Os and clocks connected to the FPGA can still be toggled without impact on device power consumption. While in Flash\*Freeze mode, the device retains all core register states and SRAM information. This mode can be configured so that no power is consumed by the I/O banks, clocks, JTAG pins, or PLLs; and the IGLOO and IGLOO PLUS devices consume as little as 5  $\mu$ W, while IGLOO nano devices consume as little as 2  $\mu$ W. Microsemi offers a state management IP core to aid users in gating clocks and managing data before entering Flash\*Freeze mode.

This document will guide users in selecting the best low power mode for their applications, and introduces Microsemi's Flash\*Freeze management IP core.

## Low Power Modes Overview

Table 2-2 summarizes the low power modes that achieve power consumption reduction when the FPGA or system is idle.

| Mode     | lode                   |     | vcc | Core | Clocks | ULSICC<br>Macro                          | To Enter<br>Mode                         | To Resume<br>Operation                 | Trigger  |

|----------|------------------------|-----|-----|------|--------|------------------------------------------|------------------------------------------|----------------------------------------|----------|

| Active   |                        | On  | On  | On   | On     | N/A                                      | Initiate clock                           | None                                   | _        |

| Static   | ldle                   | On  | On  | On   | Off    | N/A                                      | Stop clock                               | Initiate<br>clock                      | External |

|          | Flash*Freeze<br>type 1 | On  | On  | On   | On*    | N/A                                      | Assert FF<br>pin                         | Deassert<br>FF pin                     | External |

|          | Flash*Freeze<br>type 2 | On  | On  | On   | On*    | Used to<br>enter<br>Flash*Freeze<br>mode | Assert FF<br>pin and<br>assert<br>LSICC  | Deassert<br>FF pin                     | External |

| Sleep    |                        | On  | Off | Off  | Off    | N/A                                      | Shut down<br>VCC                         | Turn on<br>VCC supply                  | External |

| Shutdown |                        | Off | Off | Off  | Off    | N/A                                      | Shut down<br>VCC and<br>VCCI<br>supplies | Turn on<br>VCC and<br>VCCI<br>supplies | External |

#### Table 2-2 • Power Modes Summary

\* External clocks can be left toggling while the device is in Flash\*Freeze mode. Clocks generated by the embedded PLL will be turned off automatically.

# Static (Idle) Mode

In Static (Idle) mode, none of the clock inputs is switching, and static power is the only power consumed by the device. This mode can be achieved by switching off the incoming clocks to the FPGA, thus benefitting from reduced power consumption. In addition, I/Os draw only minimal leakage current. In this mode, embedded SRAM, I/Os, and registers retain their values so the device can enter and exit this mode just by switching the clocks on or off.

If the device-embedded PLL is used as the clock source, Static (Idle) mode can easily be entered by pulling the PLL POWERDOWN pin LOW (active Low), which will turn off the PLL.

# Chip and Quadrant Global I/Os

The following sections give an overview of naming conventions and other related I/O information.

### Naming of Global I/Os

In low power flash devices, the global I/Os have access to certain clock conditioning circuitry and have direct access to the global network. Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities to those of regular I/Os. Due to the comprehensive and flexible nature of the I/Os in low power flash devices, a naming scheme is used to show the details of the I/O. The global I/O uses the generic name Gmn/IOuxwByVz. Note that Gmn refers to a global input pin and IOuxwByVz refers to a regular I/O Pin, as these I/Os can be used as either global or regular I/Os. Refer to the I/O Structures chapter of the user's guide for the device that you are using for more information on this naming convention.

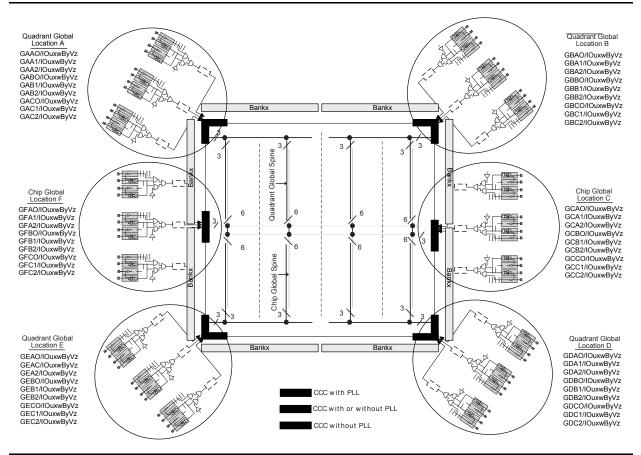

Figure 3-4 represents the global input pins connection. It shows all 54 global pins available to access the 18 global networks in ProASIC3E families.

Figure 3-4 • Global Connections Details

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

### **Dynamic PLL Configuration**

To generate a dynamically reconfigurable CCC, the user should select **Dynamic CCC** in the configuration section of the SmartGen GUI (Figure 4-26). This will generate both the CCC core and the configuration shift register / control bit MUX.

#### Figure 4-26 • SmartGen GUI

Even if dynamic configuration is selected in SmartGen, the user must still specify the static configuration data for the CCC (Figure 4-27). The specified static configuration is used whenever the MODE signal is set to LOW and the CCC is required to function in the static mode. The static configuration data can be used as the default behavior of the CCC where required.

Figure 4-27 • Dynamic CCC Configuration in SmartGen

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

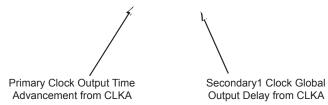

Primary Clock Output Delay from CLKA -3.020 Secondary1 Clock frequency 40.000 Secondary1 Clock Phase Shift 0.000 Secondary1 Clock Global Output Delay from CLKA 2.515

Next, perform simulation in Model*Sim* to verify the correct delays. Figure 4-30 shows the simulation results. The delay values match those reported in the SmartGen PLL Wizard.

#### Figure 4-30 • Model Sim Simulation Results

The timing can also be analyzed using SmartTime in Designer. The user should import the synthesized netlist to Designer, perform Compile and Layout, and then invoke SmartTime. Go to **Tools** > **Options** and change the maximum delay operating conditions to **Typical Case**. Then expand the Clock-to-Out paths of GLA and GLB and the individual components of the path delays are shown. The path of GLA is shown in Figure 4-31 on page 123 displaying the same delay value.

FlashROM in Microsemi's Low Power Flash Devices

# **Programming and Accessing FlashROM**

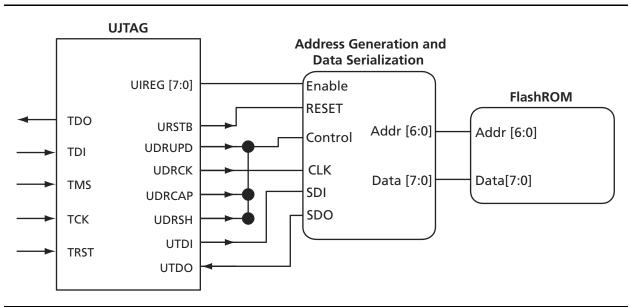

The FlashROM content can only be programmed via JTAG, but it can be read back selectively through the JTAG programming interface, the UJTAG interface, or via direct FPGA core addressing. The pages of the FlashROM can be made secure to prevent read-back via JTAG. In that case, read-back on these secured pages is only possible by the FPGA core fabric or via UJTAG.

A 7-bit address from the FPGA core defines which of the eight pages (three MSBs) is being read, and which of the 16 bytes within the selected page (four LSBs) are being read. The FlashROM content can be read on a random basis; the access time is 10 ns for a device supporting commercial specifications. The FPGA core will be powered down during writing of the FlashROM content. FPGA power-down during FlashROM programming is managed on-chip, and FPGA core functionality is not available during programming of the FlashROM. Table 5-2 summarizes various FlashROM access scenarios.

| Access Mode | FlashROM Read | FlashROM Write |

|-------------|---------------|----------------|

| JTAG        | Yes           | Yes            |

| UJTAG       | Yes           | No             |

| FPGA core   | Yes           | No             |

Figure 5-6 shows the accessing of the FlashROM using the UJTAG macro. This is similar to FPGA core access, where the 7-bit address defines which of the eight pages (three MSBs) is being read and which of the 16 bytes within the selected page (four LSBs) are being read. Refer to the "UJTAG Applications in Microsemi's Low Power Flash Devices" section on page 363 for details on using the UJTAG macro to read the FlashROM.

Figure 5-7 on page 139 and Figure 5-8 on page 139 show the FlashROM access from the JTAG port. The FlashROM content can be read on a random basis. The three-bit address defines which page is being read or updated.

Figure 5-6 • Block Diagram of Using UJTAG to Read FlashROM Contents

### **SRAM Features**

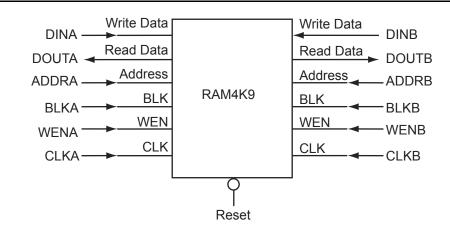

#### RAM4K9 Macro

RAM4K9 is the dual-port configuration of the RAM block (Figure 6-4). The RAM4K9 nomenclature refers to both the deepest possible configuration and the widest possible configuration the dual-port RAM block can assume, and does not denote a possible memory aspect ratio. The RAM block can be configured to the following aspect ratios: 4,096×1, 2,048×2, 1,024×4, and 512×9. RAM4K9 is fully synchronous and has the following features:

- Two ports that allow fully independent reads and writes at different frequencies

- Selectable pipelined or nonpipelined read

- Active-low block enables for each port

- Toggle control between read and write mode for each port

- · Active-low asynchronous reset

- Pass-through write data or hold existing data on output. In pass-through mode, the data written to the write port will immediately appear on the read port.

- Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

*Note:* For timing diagrams of the RAM signals, refer to the appropriate family datasheet. *Figure 6-4* • RAM4K9 Simplified Configuration

### Signal Descriptions for RAM4K9

Note: Automotive ProASIC3 devices support single-port SRAM capabilities, or dual-port SRAM only under specific conditions. Dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). Since Libero SoC macro libraries support a dual-port macro only, certain modifications must be made. These are detailed below.

The following signals are used to configure the RAM4K9 memory element:

#### WIDTHA and WIDTHB

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 6-2 on page 154).

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WIDTHB should be tied to ground.

#### Table 6-10 • RAM and FIFO Memory Block Consumption

|       |    |               |                                 |                                |                                |                                                | Depth                                           |                                                 |                                                    |                                                    |                                                   |                                                    |

|-------|----|---------------|---------------------------------|--------------------------------|--------------------------------|------------------------------------------------|-------------------------------------------------|-------------------------------------------------|----------------------------------------------------|----------------------------------------------------|---------------------------------------------------|----------------------------------------------------|

|       | Ì  |               | 2                               | 56                             | 512                            | 1,024                                          | 2,048                                           | 4,096                                           | 8,192                                              | 16,384                                             | 32,768                                            | 65,536                                             |

|       | 1  |               | Two-Port                        | Dual-Port                      | Dual-Port                      | Dual-Port                                      | Dual-Port                                       | Dual-Port                                       | Dual-Port                                          | Dual-Port                                          | Dual-Port                                         | Dual-Port                                          |

|       | 1  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 1                                               | 1                                               | 2                                                  | 4                                                  | 8                                                 | 16 × 1                                             |

|       |    | Configuration | Any                             | Any                            | Any                            | 1,024 × 4                                      | 2,048 × 2                                       | 4,096 × 1                                       | 2 × (4,096 × 1)<br>Cascade Deep                    | 4 × (4,096 × 1)<br>Cascade Deep                    | 8 × (4,096 × 1)<br>Cascade Deep                   | 16 × (4,096 × 1)<br>Cascade Deep                   |

|       | 2  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 1                                               | 2                                               | 4                                                  | 8                                                  | 16                                                | 32                                                 |

|       |    | Configuration | Any                             | Any                            | Any                            | 1,024×4                                        | 2,048 × 2                                       | 2 × (4,096 × 1)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 2 Wide   | 8 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 2 Wide   | 16 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 2 Wide | 32 × (4,096 × 1)<br>Cascaded 16<br>Deep and 2 Wide |

|       | 4  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 2                                               | 4                                               | 8                                                  | 16                                                 | 32                                                | 64                                                 |

|       |    | Configuration | Any                             | Any                            | Any                            | 1,024 × 4                                      | 2 × (2,048 × 2)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 4 Wide   | 16 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 4 Wide  | 32 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 4 Wide | 64 × (4,096 × 1)<br>Cascaded 16<br>Deep and 4 Wide |

|       | 8  | Number Block  | 1                               | 1                              | 1                              | 2                                              | 4                                               | 8                                               | 16                                                 | 32                                                 | 64                                                |                                                    |

|       |    | Configuration | Any                             | Any                            | Any                            | 2 × (1,024 × 4)<br>Cascaded Wide               | 4 × (2,048 × 2)<br>Cascaded Wide                | 8 × (4,096 × 1)<br>Cascaded Wide                | 16 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 8 Wide  | 32 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 8 Wide  | 64 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 8 Wide |                                                    |

|       | 9  | Number Block  | 1                               | 1                              | 1                              | 2                                              | 4                                               | 8                                               | 16                                                 | 32                                                 |                                                   |                                                    |

|       |    | Configuration | Any                             | Any                            | Any                            | 2 × (512 × 9)<br>Cascaded Deep                 | 4 × (512 × 9)<br>Cascaded Deep                  | 8 × (512 × 9)<br>Cascaded Deep                  | 16 × (512 × 9)<br>Cascaded Deep                    | 32 × (512 × 9)<br>Cascaded Deep                    |                                                   |                                                    |

|       | 16 | Number Block  | 1                               | 1                              | 1                              | 4                                              | 8                                               | 16                                              | 32                                                 | 64                                                 |                                                   |                                                    |

| Width |    | Configuration | 256 × 18                        | 256 × 18                       | 256 × 18                       | 4 × (1,024 × 4)<br>Cascaded Wide               | 8 × (2,048 × 2)<br>Cascaded Wide                | 16 × (4,096 × 1)<br>Cascaded Wide               | 32 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 16 Wide | 32 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 16 Wide |                                                   |                                                    |

|       | 18 | Number Block  | 1                               | 2                              | 2                              | 4                                              | 8                                               | 18                                              | 32                                                 |                                                    |                                                   |                                                    |

|       |    | Configuration | 256 × 8                         | 2 × (512 × 9)<br>Cascaded Wide | 2 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded 2 Deep<br>and 2 Wide | 8 × (512 × 9)<br>Cascaded 4 Deep<br>and 2 Wide  | 16 × (512 × 9)<br>Cascaded 8 Deep<br>and 2 Wide | 16 × (512 × 9)<br>Cascaded 16<br>Deep and 2 Wide   |                                                    |                                                   |                                                    |

|       | 32 | Number Block  | 2                               | 4                              | 4                              | 8                                              | 16                                              | 32                                              | 64                                                 |                                                    |                                                   |                                                    |

|       |    | Configuration | 2 × (256 × 18)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 8 × (1,024 × 4)<br>Cascaded Wide               | 16 × (2,048 × 2)<br>Cascaded Wide               | 32 × (4,096 × 1)<br>Cascaded Wide               | 64 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 32 Wide |                                                    |                                                   |                                                    |

|       | 36 | Number Block  | 2                               | 4                              | 4                              | 8                                              | 16                                              | 32                                              |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 2 × (256 × 18)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded 2 Deep<br>and 4 Wide | 16 × (512 × 9)<br>Cascaded 4 Deep<br>and 4 Wide | 16 × (512 × 9)<br>Cascaded 8 Deep<br>and 4 Wide |                                                    |                                                    |                                                   |                                                    |

|       | 64 | Number Block  | 4                               | 8                              | 8                              | 16                                             | 32                                              | 64                                              |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 4 × (256 × 18)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 16 × (1,024 × 4)<br>Cascaded Wide              | 32 × (2,048 × 2)<br>Cascaded Wide               | 64 × (4,096 × 1)<br>Cascaded Wide               |                                                    |                                                    |                                                   |                                                    |

|       | 72 | Number Block  | 4                               | 8                              | 8                              | 16                                             | 32                                              |                                                 |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 4 × (256 × 18)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 16 × (512 × 9)<br>Cascaded Wide                | 16 × (512 × 9)<br>Cascaded 4 Deep<br>and 8 Wide |                                                 |                                                    |                                                    |                                                   |                                                    |

|       |    | 11            |                                 |                                |                                | -                                              | -                                               |                                                 |                                                    |                                                    |                                                   |                                                    |

Note: Memory configurations represented by grayed cells are not supported.

|                    |           | Maximum Performance                                         |                                            |

|--------------------|-----------|-------------------------------------------------------------|--------------------------------------------|

| Specification      | ProASIC3E | IGLOOe V2 or V5<br>Devices, 1.5 V DC Core<br>Supply Voltage | IGLOOe V2, 1.2 V DC<br>Core Supply Voltage |

| LVTTL/LVCMOS 3.3 V | 200 MHz   | 180 MHz                                                     | TBD                                        |

| LVCMOS 2.5 V       | 250 MHz   | 230 MHz                                                     | TBD                                        |

| LVCMOS 1.8 V       | 200 MHz   | 180 MHz                                                     | TBD                                        |

| LVCMOS 1.5 V       | 130 MHz   | 120 MHz                                                     | TBD                                        |

| PCI                | 200 MHz   | 180 MHz                                                     | TBD                                        |

| PCI-X              | 200 MHz   | 180 MHz                                                     | TBD                                        |

| HSTL-I             | 300 MHz   | 275 MHz                                                     | TBD                                        |

| HSTL-II            | 300 MHz   | 275 MHz                                                     | TBD                                        |

| SSTL2-I            | 300 MHz   | 275 MHz                                                     | TBD                                        |

| SSTL2-II           | 300 MHz   | 275 MHz                                                     | TBD                                        |

| SSTL3-I            | 300 MHz   | 275 MHz                                                     | TBD                                        |

| SSTL3-II           | 300 MHz   | 275 MHz                                                     | TBD                                        |

| GTL+ 3.3 V         | 300 MHz   | 275 MHz                                                     | TBD                                        |

| GTL+ 2.5 V         | 300 MHz   | 275 MHz                                                     | TBD                                        |

| GTL 3.3 V          | 300 MHz   | 275 MHz                                                     | TBD                                        |

| GTL 2.5 V          | 300 MHz   | 275 MHz                                                     | TBD                                        |

| LVDS               | 350 MHz   | 300 MHz                                                     | TBD                                        |

| M-LVDS             | 200 MHz   | 180 MHz                                                     | TBD                                        |

| B LVDS             | 200 MHz   | 180 MHz                                                     | TBD                                        |

| LVPECL             | 350 MHz   | 300 MHz                                                     | TBD                                        |

#### Table 8-7 • Maximum I/O Frequency for Single-Ended and Differential I/Os in All Banks in ProASIC3E Devices (maximum drive strength and high slew selected)

-

ProASIC3L FPGA Fabric User's Guide

Refer to Table 8-16 on page 242 for SLEW and OUT\_DRIVE settings. Table 8-18 on page 244 lists the voltages for the supported I/O standards.

| I/O Standard         | SLEW (output only) | OUT_DRIVE (output only) | SKEW (tribuf and bibuf only) | RES_PULL | OUT_LOAD (output only) | <b>COMBINE_REGISTER</b> | IN_DELAY (input only) | IN_DELAY_VAL (input only) | SCHMITT_TRIGGER (input only) |

|----------------------|--------------------|-------------------------|------------------------------|----------|------------------------|-------------------------|-----------------------|---------------------------|------------------------------|

| LVTTL/LVCMOS 3.3 V   | See<br>Table 8-15  | See<br>Table 8-15 on    | Off                          | None     | 35 pF                  | -                       | Off                   | 0                         | Off                          |

| LVCMOS 2.5 V         | on page 240        | page 240                | Off                          | None     | 35 pF                  | _                       | Off                   | 0                         | Off                          |

| LVCMOS 2.5/5.0 V     |                    |                         | Off                          | None     | 35 pF                  | -                       | Off                   | 0                         | Off                          |

| LVCMOS 1.8 V         |                    |                         | Off                          | None     | 35 pF                  | _                       | Off                   | 0                         | Off                          |

| LVCMOS 1.5 V         |                    |                         | Off                          | None     | 35 pF                  | -                       | Off                   | 0                         | Off                          |

| PCI (3.3 V)          |                    |                         | Off                          | None     | 10 pF                  | -                       | Off                   | 0                         | Off                          |

| PCI-X (3.3 V)        |                    |                         | Off                          | None     | 10 pF                  | -                       | Off                   | 0                         | Off                          |

| GTL+ (3.3 V)         |                    |                         | Off                          | None     | 10 pF                  | -                       | Off                   | 0                         | Off                          |

| GTL+ (2.5 V)         |                    |                         | Off                          | None     | 10 pF                  | -                       | Off                   | 0                         | Off                          |

| GTL (3.3 V)          |                    |                         | Off                          | None     | 10 pF                  | _                       | Off                   | 0                         | Off                          |

| GTL (2.5 V)          |                    |                         | Off                          | None     | 10 pF                  | _                       | Off                   | 0                         | Off                          |

| HSTL Class I         |                    |                         | Off                          | None     | 20 pF                  | _                       | Off                   | 0                         | Off                          |

| HSTL Class II        |                    |                         | Off                          | None     | 20 pF                  | _                       | Off                   | 0                         | Off                          |

| SSTL2 Class I and II |                    |                         | Off                          | None     | 30 pF                  | _                       | Off                   | 0                         | Off                          |

| SSTL3 Class I and II |                    |                         | Off                          | None     | 30 pF                  | -                       | Off                   | 0                         | Off                          |

| LVDS, B-LVDS, M-LVDS |                    |                         | Off                          | None     | 0 pF                   | -                       | Off                   | 0                         | Off                          |

| LVPECL               |                    |                         | Off                          | None     | 0 pF                   | -                       | Off                   | 0                         | Off                          |

#### Table 8-17 • IGLOOe and ProASIC3E I/O Default Attributes

Т

Г

The procedure is as follows:

- 1. Select the bank to which you want VCCI to be assigned from the **Choose Bank** list.

- 2. Select the I/O standards for that bank. If you select any standard, the tool will automatically show all compatible standards that have a common VCCI voltage requirement.

- 3. Click Apply.

- 4. Repeat steps 1–3 to assign VCCI voltages to other banks. Refer to Figure 9-11 on page 263 to find out how many I/O banks are needed for VCCI bank assignment.

#### Manually Assigning VREF Pins

Voltage-referenced inputs require an input reference voltage (VREF). The user must assign VREF pins before running Layout. Before assigning a VREF pin, the user must set a VREF technology for the bank to which the pin belongs.

# VREF Rules for the Implementation of Voltage-Referenced I/O Standards

The VREF rules are as follows:

- 1. Any I/O (except JTAG I/Os) can be used as a V<sub>REF</sub> pin.

- One V<sub>REF</sub> pin can support up to 15 I/Os. It is recommended, but not required, that eight of them be on one side and seven on the other side (in other words, all 15 can still be on one side of VREF).

- 3. SSTL3 (I) and (II): Up to 40 I/Os per north or south bank in any position

- 4. LVPECL / GTL+ 3.3 V / GTL 3.3 V: Up to 48 I/Os per north or south bank in any position (not applicable for IGLOO nano and ProASIC3 nano devices)

- 5. SSTL2 (I) and (II) / GTL + 2.5 V / GTL 2.5 V: Up to 72 I/Os per north or south bank in any position

- 6. VREF minibanks partition rule: Each I/O bank is physically partitioned into VREF minibanks. The VREF pins within a VREF minibank are interconnected internally, and consequently, only one VREF voltage can be used within each VREF minibank. If a bank does not require a VREF signal, the VREF pins of that bank are available as user I/Os.

- The first VREF minibank includes all I/Os starting from one end of the bank to the first power triple and eight more I/Os after the power triple. Therefore, the first VREF minibank may contain (0 + 8), (2 + 8), (4 + 8), (6 + 8), or (8 + 8) I/Os.

The second VREF minibank is adjacent to the first VREF minibank and contains eight I/Os, a power triple, and eight more I/Os after the triple. An analogous rule applies to all other VREF minibanks but the last.

The last VREF minibank is adjacent to the previous one but contains eight I/Os, a power triple, and all I/Os left at the end of the bank. This bank may also contain (8 + 0), (8 + 2), (8 + 4), (8 + 6), or (8 + 8) available I/Os.

#### Example:

4 l/Os  $\rightarrow$  Triple  $\rightarrow$  8 l/Os, 8 l/Os  $\rightarrow$  Triple  $\rightarrow$  8 l/Os, 8 l/Os  $\rightarrow$  Triple  $\rightarrow$  2 l/Os

That is, minibank A = (4 + 8) I/Os, minibank B = (8 + 8) I/Os, minibank C = (8 + 2) I/Os.

Only minibanks that contain input or bidirectional I/Os require a VREF. A VREF is not needed for minibanks composed of output or tristated I/Os.

### Assigning the VREF Voltage to a Bank

When importing the PDC file, the VREF voltage can be assigned to the I/O bank. The PDC command is as follows:

set\_iobank -vref [value]

Another method for assigning VREF is by using **MVN** > **Edit** > **I/O Bank Settings** (Figure 9-13 on page 266).

# Microsemi

DDR for Microsemi's Low Power Flash Devices

# **DDR Support in Flash-Based Devices**

The flash FPGAs listed in Table 10-1 support the DDR feature and the functions described in this document.

#### Table 10-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 10-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 10-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

# Input Support for DDR

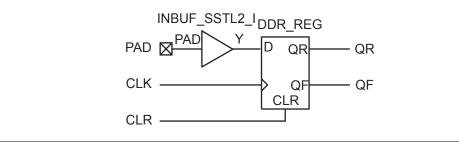

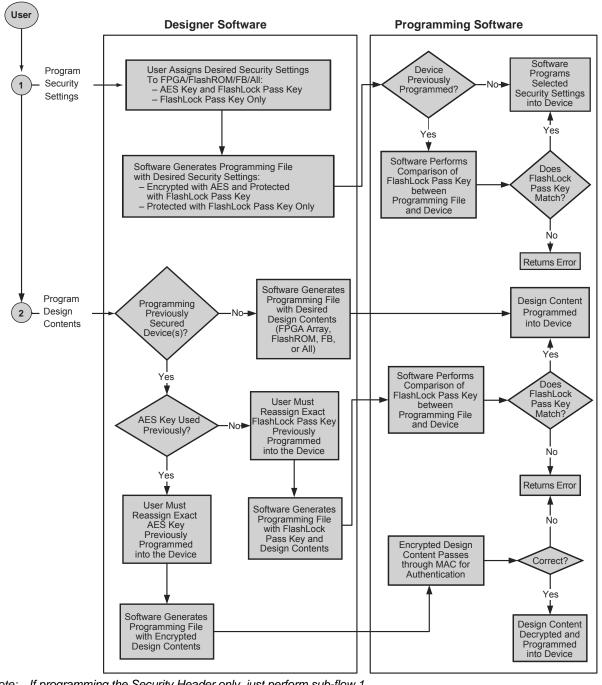

The basic structure to support a DDR input is shown in Figure 10-2. Three input registers are used to capture incoming data, which is presented to the core on each rising edge of the I/O register clock. Each I/O tile supports DDR inputs.

# **Output Support for DDR**

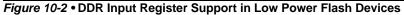

The basic DDR output structure is shown in Figure 10-1 on page 271. New data is presented to the output every half clock cycle.

Note: DDR macros and I/O registers do not require additional routing. The combiner automatically recognizes the DDR macro and pushes its registers to the I/O register area at the edge of the chip. The routing delay from the I/O registers to the I/O buffers is already taken into account in the DDR macro.

Figure 10-3 • DDR Output Register (SSTL3 Class I)

DDR for Microsemi's Low Power Flash Devices

# **Instantiating DDR Registers**

Using SmartGen is the simplest way to generate the appropriate RTL files for use in the design. Figure 10-4 shows an example of using SmartGen to generate a DDR SSTL2 Class I input register. SmartGen provides the capability to generate all of the DDR I/O cells as described. The user, through the graphical user interface, can select from among the many supported I/O standards. The output formats supported are Verilog, VHDL, and EDIF.

Figure 10-5 on page 277 through Figure 10-8 on page 280 show the I/O cell configured for DDR using SSTL2 Class I technology. For each I/O standard, the I/O pad is buffered by a special primitive that indicates the I/O standard type.

Figure 10-4 • Example of Using SmartGen to Generate a DDR SSTL2 Class I Input Register

Microsemi

Security in Low Power Flash Devices

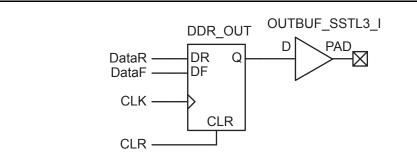

Note: If programming the Security Header only, just perform sub-flow 1. If programming design content only, just perform sub-flow 2.

Figure 12-9 • Security Programming Flows

Table 12-6 and Table 12-7 show all available options. If you want to implement custom levels, refer to the "Advanced Options" section on page 322 for information on each option and how to set it.

3. When done, click **Finish** to generate the Security Header programming file.

| Security Option       | FlashROM Only | FPGA Core Only | Both FlashROM<br>and FPGA |

|-----------------------|---------------|----------------|---------------------------|

| No AES / no FlashLock | 1             | 1              | ✓                         |

| FlashLock only        | 1             | 1              | ✓                         |

| AES and FlashLock     | 1             | 1              | ✓                         |

Note:  $\checkmark$  = options that may be used

#### Table 12-7 • All Fusion Header File Security Options

| Security Option       | FlashROM Only | FPGA Core Only | FB Core Only | All |

|-----------------------|---------------|----------------|--------------|-----|

| No AES / No FlashLock | $\checkmark$  | 1              | ~            | 1   |

| FlashLock             | 1             | 1              | ~            | 1   |

| AES and FlashLock     | ~             | 1              | 1            | 1   |

### Generation of Programming Files with AES Encryption— Application 3

This section discusses how to generate design content programming files needed specifically at unsecured or remote locations to program devices with a Security Header (FlashLock Pass Key and AES key) already programmed ("Application 2: Nontrusted Environment—Unsecured Location" section on page 309 and "Application 3: Nontrusted Environment—Field Updates/Upgrades" section on page 310). In this case, the encrypted programming file must correspond to the AES key already programmed into the device. If AES encryption was previously selected to encrypt the FlashROM, FBs, and FPGA array, AES encryption must be set when generating the programming file for them. AES encryption can be applied to the FlashROM only, the FBs only, the FPGA array only, or all. The user must ensure both the FlashLock Pass Key and the AES key match those already programmed to the device(s), and all security settings must match what was previously programmed. Otherwise, the encryption and/or device unlocking will not be recognized when attempting to program the device with the programming file.

The generated programming file will be AES-encrypted.

In this scenario, generate the programming file as follows:

1. Deselect **Security settings** and select the portion of the device to be programmed (Figure 12-17 on page 320). Select **Programming previously secured device(s**). Click **Next**.

### Microsemi

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

errors, but this list is intended to show where problems can occur. FlashPro4/3/3X allows TCK to be lowered from 6 MHz down to 1 MHz to allow you to address some signal integrity problems that may occur with impedance mismatching at higher frequencies. Customers are expected to troubleshoot board-level signal integrity issues by measuring voltages and taking scope plots.

#### Scan Chain Failure

Normally, the FlashPro4/3/3X Scan Chain command expects to see 0x1 on the TDO pin. If the command reports reading 0x0 or 0x3, it is seeing the TDO pin stuck at 0 or 1. The only time the TDO pin comes out of tristate is when the JTAG TAP state machine is in the Shift-IR or Shift-DR state. If noise or reflections on the TCK or TMS lines have disrupted the correct state transitions, the device's TAP state controller might not be in one of these two states when the programmer tries to read the device. When this happens, the output is floating when it is read and does not match the expected data value. This can also be caused by a broken TDO net. Only a small amount of data is read from the device during the Scan Chain command, so marginal problems may not always show up during this command. Occasionally a faulty programmer can cause intermittent scan chain failures.

#### Exit 11

This error occurs during the verify stage of programming a device. After programming the design into the device, the device is verified to ensure it is programmed correctly. The verification is done by shifting the programming data into the device. An internal comparison is performed within the device to verify that all switches are programmed correctly. Noise induced by poor signal integrity can disrupt the writes and reads or the verification process and produce a verification error. While technically a verification error, the root cause is often related to signal integrity.

Refer to the *FlashPro User's Guide* for other error messages and solutions. For the most up-to-date known issues and solutions, refer to http://www.microsemi.com/soc/support.

### Conclusion

IGLOO, ProASIC3, SmartFusion, and Fusion devices offer a low-cost, single-chip solution that is live at power-up through nonvolatile flash technology. The FlashLock Pass Key and 128-bit AES Key security features enable secure ISP in an untrusted environment. On-chip FlashROM enables a host of new applications, including device serialization, subscription-based applications, and IP addressing. Additionally, as the FlashROM is nonvolatile, all of these services can be provided without battery backup.

### **Related Documents**

### **User's Guides**

FlashPro User's Guide http://www.microsemi.com/soc/documents/flashpro\_ug.pdf

# List of Changes

| Date                   | Changes                                                                                                                                               | Page |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010              | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.             | N/A  |

| v1.1<br>(October 2008) | The "Introduction" was revised to include information about the core supply voltage range of operation in V2 devices.                                 | 341  |

|                        | IGLOO nano device support was added to Table 14-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit.                                           | 342  |

|                        | The "Circuit Description" section was updated to include IGLOO PLUS core operation from 1.2 V to 1.5 V in 50 mV increments.                           | 343  |

| v1.0<br>(August 2008)  | The "Microsemi's Flash Families Support Voltage Switching Circuit" section was revised to include new families and make the information more concise. | 342  |

The following table lists critical changes that were made in each revision of the chapter.

## **Boundary Scan Support in Low Power Devices**

The information in this document applies to all Fusion, IGLOO, and ProASIC3 devices. For IGLOO, IGLOO PLUS, and ProASIC3L devices, the Flash\*Freeze pin must be deasserted for successful boundary scan operations. Devices cannot enter JTAG mode directly from Flash\*Freeze mode.

## **Boundary Scan Opcodes**

Low power flash devices support all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD, and BYPASS) and the optional IDCODE instruction (Table 16-2).

#### Table 16-2 • Boundary Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| HIGHZ          | 07         |

| USERCODE       | 0E         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | 0F         |

| CLAMP          | 05         |

| BYPASS         | FF         |

### **Boundary Scan Chain**

The serial pins are used to serially connect all the boundary scan register cells in a device into a boundary scan register chain (Figure 16-2 on page 360), which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic I/O tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Each test section is accessed through the TAP, which has five associated pins: TCK (test clock input), TDI, TDO (test data input and output), TMS (test mode selector), and TRST (test reset input). TMS, TDI, and TRST are equipped with pull-up resistors to ensure proper operation when no input data is supplied to them. These pins are dedicated for boundary scan test usage. Refer to the "JTAG Pins" section in the "Pin Descriptions and Packaging" chapter of the appropriate device datasheet for pull-up/-down recommendations for TCK and TRST pins. Pull-down recommendations are also given in Table 16-3 on page 360

### Microsemi

Boundary Scan in Low Power Flash Devices

# **List of Changes**

| Date                    | Changes                                                                                                                                                                                                                                         | Page |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| August 2012             | In the "Boundary Scan Chain" section, the reference made to the datasheet for pull-up/-down recommendations was changed to mention TCK and TRST pins rather than TDO and TCK pins. TDO is an output, so no pull resistor is needed (SAR 35937). | 359  |

|                         | The "Advanced Boundary Scan Register Settings" section is new (SAR 38432).                                                                                                                                                                      | 361  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                       | N/A  |

|                         | Table 16-3 • TRST and TCK Pull-Down Recommendations was revised to add VJTAG at 1.2 V.                                                                                                                                                          | 360  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 16-1 • Flash-Based FPGAs.                                                                                                                                                              | 358  |

| v1.3<br>(October 2008)  | The "Boundary Scan Support in Low Power Devices" section was revised to include new families and make the information more concise.                                                                                                             | 359  |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 16-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul>      | 358  |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                                                                                                                           | N/A  |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                     | 358  |

The following table lists critical changes that were made in each revision of the chapter.