Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

ĿXF

| Detuns                         |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 110592                                                                      |

| Number of I/O                  | 177                                                                         |

| Number of Gates                | 600000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 144-LBGA                                                                    |

| Supplier Device Package        | 144-FPBGA (13x13)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3p600l-fgg144i |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- · The device is reset upon exiting Flash\*Freeze mode or internal state saving is not required.

- State saving is required, but data and clock management is performed external to the FPGA. In other words, incoming data is externally guaranteed and held valid prior to entering Flash\*Freeze mode.

Type 2 Flash\*Freeze mode is ideally suited for applications with the following design criteria:

- Entering Flash\*Freeze mode is dependent on an internal or external signal in addition to the external FF pin.

- State saving is required and incoming data is not externally guaranteed valid.

- The designer wants to use his/her own Flash\*Freeze management IP for clock and data management.

- The designer wants to use his/her own Flash\*Freeze management logic for clock and data management.

- Internal housekeeping is required prior to entering Flash\*Freeze mode. Housekeeping activities

may include loading data to SRAM, system shutdown, completion of current task, or ensuring

valid Flash\*Freeze pin assertion.

There is no downside to type 2 mode, and Microsemi's Flash\*Freeze management IP offers a very low tile count clock and data management solution. Microsemi's recommendation for most designs is to use type 2 Flash\*Freeze mode with Flash\*Freeze management IP.

## **Design Solutions**

### Clocks

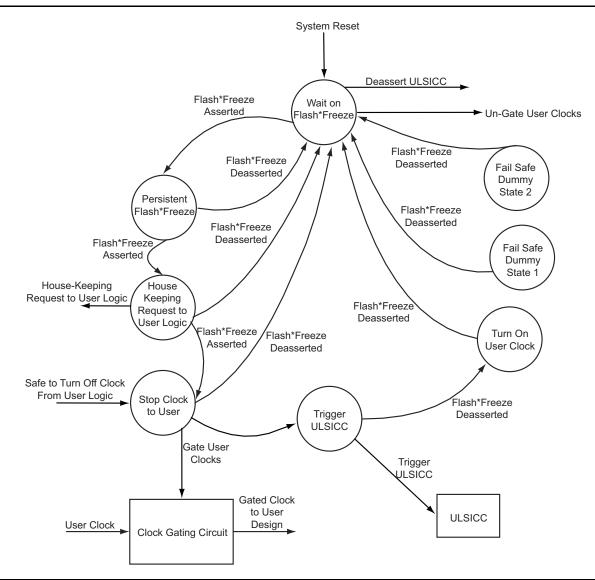

- Microsemi recommends using a completely synchronous design in Type 2 mode with Flash\*Freeze management IP cleanly gating all internal and external clocks. This will prevent narrow pulses upon entrance and exit from Flash\*Freeze mode (Figure 2-5 on page 30).

- Upon entering Flash\*Freeze mode, external clocks become tied off High, internal to the clock pin (unless hold state is used on IGLOO nano or IGLOO PLUS), and PLLs are turned off. Any clock that is externally Low will realize a Low to High transition internal to the device while entering Flash\*Freeze. If clocks will float during Flash\*Freeze mode, Microsemi recommends using the weak pull-up feature. If clocks will continue to drive the device during Flash\*Freeze mode, the clock gating (filter) available in Flash\*Freeze management IP can help to filter unwanted narrow clock pulses upon Flash\*Freeze mode entry and exit.

- Clocks may continue to drive FPGA pins while the device is in Flash\*Freeze mode, with virtually

no power consumption. The weak pull-up/-down configuration will result in unnecessary power

consumption if used in this scenario.

- Floating clocks can cause totem pole currents on the input I/O circuitry when the device is in

active mode. If clocks are externally gated prior to entering Flash\*Freeze mode, Microsemi

recommends gating them to a known value (preferably '1', to avoid a possible narrow pulse upon

Flash\*Freeze mode exit), and not leaving them floating. However, during Flash\*Freeze mode, all

inputs and clocks are internally tied off to prevent totem pole currents, so they can be left floating.

- Upon exiting Flash\*Freeze mode, the design must allow maximum acquisition time for the PLL to acquire the lock signal, and for a PLL clock to become active. If a PLL output clock is used as the primary clock for Flash\*Freeze management IP, it is important to note that the clock gating circuit will only release other clocks after the primary PLL output clock becomes available.

Flash\*Freeze Technology and Low Power Modes

Figure 2-11 • FSM State Diagram

Flash\*Freeze Technology and Low Power Modes

| Date                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page          |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| v1.2<br>(continued)     | Figure 2-3 • Flash*Freeze Mode Type 2 – Controlled by Flash*Freeze Pin and Internal Logic (LSICC signal) was updated.                                                                                                                                                                                                                                                                                                                                                                                                           | 27            |

|                         | Figure 2-4 • Flash*Freeze Mode Type 2 – Timing Diagram was revised to show deasserting LSICC after the device has exited Flash*Freeze mode.                                                                                                                                                                                                                                                                                                                                                                                     |               |

|                         | The "IGLOO nano and IGLOO PLUS I/O State in Flash*Freeze Mode" section was added to include information for IGLOO PLUS devices. Table 2-6 • IGLOO nano and IGLOO PLUS Flash*Freeze Mode (type 1 and type 2)—I/O Pad State is new.                                                                                                                                                                                                                                                                                               | 28, 29        |

|                         | The "During Flash*Freeze Mode" section was revised to include a new bullet pertaining to output behavior for IGLOO PLUS. The bullet on JTAG operation was revised to provide more detail.                                                                                                                                                                                                                                                                                                                                       | 31            |

|                         | Figure 2-6 • Controlling Power-On/-Off State Using Microprocessor and Power FET and Figure 2-7 • Controlling Power-On/-Off State Using Microprocessor and Voltage Regulator were updated to include IGLOO PLUS.                                                                                                                                                                                                                                                                                                                 | 33, 33        |

|                         | The first sentence of the "Shutdown Mode" section was updated to list the devices for which it is supported.                                                                                                                                                                                                                                                                                                                                                                                                                    | 32            |

|                         | The first paragraph of the "Power-Up/-Down Behavior" section was revised. The second sentence was changed to, "The I/Os remain tristated until the last voltage supply ( $V_{CC}$ or $V_{CCI}$ ) is powered to its activation level." The word "activation" replaced the word "functional." The sentence, "During power-down, device I/Os become tristated once the first power supply ( $V_{CC}$ or $V_{CCI}$ ) drops below its deactivation voltage level" was revised. The word "deactivation" replaced the word "brownout." | 33            |

|                         | The "Prototyping for IGLOO and ProASIC3L Devices Using ProASIC3" section was revised to state that prototyping in ProASIC3 does not apply for the IGLOO PLUS family.                                                                                                                                                                                                                                                                                                                                                            | 2-21          |

|                         | Table 2-8 • Prototyping/Migration Solutions, Table 2-9 • Device Migration—IGLOO Supported Packages in ProASIC3 Devices, and Table 2-10 • Device Migration—<br>ProASIC3L Supported Packages in ProASIC3 Devices were updated with a table note stating that device migration is not supported for IGLOO PLUS devices.                                                                                                                                                                                                            | 2-21,<br>2-23 |

|                         | The text following Table 2-10 • Device Migration—ProASIC3L Supported Packages in ProASIC3 Devices was moved to a new section: the "Flash*Freeze Design Guide" section.                                                                                                                                                                                                                                                                                                                                                          | 34            |

| v1.1<br>(February 2008) | Table 2-1 • Flash-Based FPGAs was updated to remove the ProASIC3, ProASIC3E, and Automotive ProASIC3 families, which were incorrectly included.                                                                                                                                                                                                                                                                                                                                                                                 | 22            |

| v1.0<br>(January 2008)  | Detailed descriptions of low power modes are described in the advanced datasheets. This application note was updated to describe how to use the features in an IGLOO/e application.                                                                                                                                                                                                                                                                                                                                             | N/A           |

|                         | Figure 2-1 • Flash*Freeze Mode Type 1 – Controlled by the Flash*Freeze Pin was updated.                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25            |

|                         | Figure 2-2 • Flash*Freeze Mode Type 1 – Timing Diagram is new.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25            |

|                         | Steps 4 and 5 are new in the "Flash*Freeze Type 2: Control by Dedicated Flash*Freeze Pin and Internal Logic" section.                                                                                                                                                                                                                                                                                                                                                                                                           | 26            |

Global Resources in Low Power Flash Devices

#### Figure 3-18 • Globals Management GUI in Designer

- 3. Occasionally, the synthesis tool assigns a global macro to clock nets, even though the fanout is significantly less than other asynchronous signals. Select **Demote global nets whose fanout is less than** and enter a reasonable value for fanouts. This frees up some global networks from the signals that have very low fanouts. This can also be done using PDC.

- 4. Use a local clock network for the signals that do not need to go to the whole chip but should have low skew. This local clock network assignment can only be done using PDC.

- 5. Assign the I/O buffer using MVN if you have fixed I/O assignment. As shown in Figure 3-10 on page 61, there are three sets of global pins that have a hardwired connection to each global network. Do not try to put multiple CLKBUF macros in these three sets of global pins. For example, do not assign two CLKBUFs to GAA0x and GAA2x pins.

- 6. You must click **Commit** at the end of MVN assignment. This runs the pre-layout checker and checks the validity of global assignment.

- 7. Always run Compile with the **Keep existing physical constraints** option on. This uses the quadrant clock network assignment in the MVN assignment and checks if you have the desired signals on the global networks.

- 8. Run Layout and check the timing.

| Config.<br>Bits | Signal              | Name                             | Description                                                                                                                                              |

|-----------------|---------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 83              | RXCSEL <sup>1</sup> | CLKC input selection             | Select the CLKC input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 110). <sup>2</sup>                          |

| 82              | RXBSEL <sup>1</sup> | CLKB input selection             | Select the CLKB input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 110). <sup>2</sup>                          |

| 81              | RXASEL <sup>1</sup> | CLKA input selection             | Select the CLKA input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 110). <sup>2</sup>                          |

| 80              | RESETEN             | Reset Enable                     | Enables (active high) the synchronization of<br>PLL output dividers after dynamic<br>reconfiguration (SUPDATE). The Reset<br>Enable signal is READ-ONLY. |

| 79              | DYNCSEL             | Clock Input C Dynamic<br>Select  | Configures clock input C to be sent to GLC for dynamic control. <sup>2</sup>                                                                             |

| 78              | DYNBSEL             | Clock Input B Dynamic<br>Select  | Configures clock input B to be sent to GLB for dynamic control. <sup>2</sup>                                                                             |

| 77              | DYNASEL             | Clock Input A Dynamic<br>Select  | Configures clock input A for dynamic PLL configuration. <sup>2</sup>                                                                                     |

| <76:74>         | VCOSEL[2:0]         | VCO Gear Control                 | Three-bit VCO Gear Control for four frequency ranges (refer to Table 4-19 on page 111 and Table 4-20 on page 111).                                       |

| 73              | STATCSEL            | MUX Select on Input C            | MUX selection for clock input C <sup>2</sup>                                                                                                             |

| 72              | STATBSEL            | MUX Select on Input B            | MUX selection for clock input B <sup>2</sup>                                                                                                             |

| 71              | STATASEL            | MUX Select on Input A            | MUX selection for clock input A <sup>2</sup>                                                                                                             |

| <70:66>         | DLYC[4:0]           | YC Output Delay                  | Sets the output delay value for YC.                                                                                                                      |

| <65:61>         | DLYB[4:0]           | YB Output Delay                  | Sets the output delay value for YB.                                                                                                                      |

| <60:56>         | DLYGLC[4:0]         | GLC Output Delay                 | Sets the output delay value for GLC.                                                                                                                     |

| <55:51>         | DLYGLB[4:0]         | GLB Output Delay                 | Sets the output delay value for GLB.                                                                                                                     |

| <50:46>         | DLYGLA[4:0]         | Primary Output Delay             | Primary GLA output delay                                                                                                                                 |

| 45              | XDLYSEL             | System Delay Select              | When selected, inserts System Delay in the feedback path in Figure 4-20 on page 101.                                                                     |

| <44:40>         | FBDLY[4:0]          | Feedback Delay                   | Sets the feedback delay value for the feedback element in Figure 4-20 on page 101.                                                                       |

| <39:38>         | FBSEL[1:0]          | Primary Feedback Delay<br>Select | Controls the feedback MUX: no delay, include programmable delay element, or use external feedback.                                                       |

| <37:35>         | OCMUX[2:0]          | Secondary 2 Output<br>Select     | Selects from the VCO's four phase outputs for GLC/YC.                                                                                                    |

| <34:32>         | OBMUX[2:0]          | Secondary 1 Output<br>Select     | Selects from the VCO's four phase outputs for GLB/YB.                                                                                                    |

#### Table 4-8 • Configuration Bit Descriptions for the CCC Blocks (continued)

Notes:

1. The <88:81> configuration bits are only for the Fusion dynamic CCC.

This value depends on the input clock source, so Layout must complete before these bits can be set. After completing Layout in Designer, generate the "CCC\_Configuration" report by choosing Tools > Report > CCC\_Configuration. The report contains the appropriate settings for these bits.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

#### **External Feedback Configuration**

For certain applications, such as those requiring generation of PCB clocks that must be matched with existing board delays, it is useful to implement an external feedback, EXTFB. The Phase Detector of the PLL core will receive CLKA and EXTFB as inputs. EXTFB may be processed by the fixed System Delay element as well as the *M* divider element. The EXTFB option is currently not supported.

After setting all the required parameters, users can generate one or more PLL configurations with HDL or EDIF descriptions by clicking the **Generate** button. SmartGen gives the option of saving session results and messages in a log file:

| Name                                          | : test_pll            |

|-----------------------------------------------|-----------------------|

| Family                                        | : ProASIC3E           |

| Output Format                                 | : VHDL                |

| Type                                          | : Static PLL          |

| Input Freq(MHz)                               | : 10.000              |

| CLKA Source                                   | : Hardwired I/O       |

| Feedback Delay Value Index                    | : 1                   |

| Feedback Mux Select                           | : 2                   |

| XDLY Mux Select                               | -<br>: No             |

| Primary Freq(MHz)                             | : 33.000              |

| Primary PhaseShift                            | : 0                   |

| Primary Delay Value Index                     | : 1                   |

| Primary Mux Select                            | : 4                   |

| Secondary1 Freq(MHz)                          | : 66.000              |

| Use GLB                                       | : YES                 |

| Use YB                                        | : YES                 |

| GLB Delay Value Index                         | : 1                   |

| YB Delay Value Index                          | · 1                   |

| Secondaryl PhaseShift                         | : 0                   |

| Secondary1 Mux Select                         | : 4                   |

| Secondary1 Mux Select<br>Secondary2 Freq(MHz) | : 101.000             |

| Use GLC                                       | : YES                 |

| Use YC                                        | : NO                  |

| GLC Delay Value Index                         | : NO<br>: 1           |

| YC Delay Value Index                          | · 1                   |

| _                                             | : 0                   |

| Secondary2 PhaseShift                         | : 4                   |

| Secondary2 Mux Select                         | • 4                   |

|                                               |                       |

|                                               |                       |

|                                               |                       |

|                                               |                       |

|                                               |                       |

| Primary Clock frequency 33.333                |                       |

| Primary Clock Phase Shift 0.000               |                       |

| Primary Clock Output Delay from               | n CLKA U.180          |

|                                               |                       |

| Secondaryl Clock frequency 66.6               |                       |

| Secondaryl Clock Phase Shift 0.               |                       |

| Secondaryl Clock Global Output                |                       |

| Secondaryl Clock Core Output De               | elay from CLKA 0.625  |

|                                               | 000                   |

| Secondary2 Clock frequency 100.               |                       |

| Secondary2 Clock Phase Shift 0.               |                       |

| Secondary2 Clock Global Output                | Delay from CLKA 0.180 |

|                                               |                       |

Below is an example Verilog HDL description of a legal PLL core configuration generated by SmartGen:

module test\_pll(POWERDOWN,CLKA,LOCK,GLA); input POWERDOWN, CLKA; output LOCK,GLA;

FlashROM in Microsemi's Low Power Flash Devices

# **Programming and Accessing FlashROM**

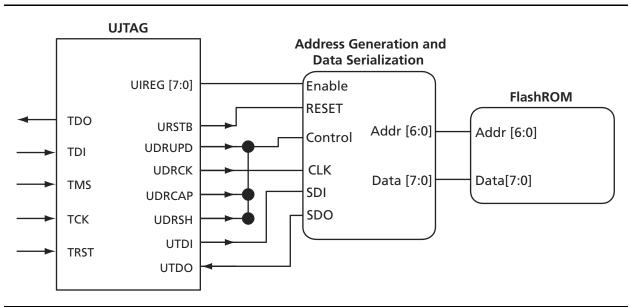

The FlashROM content can only be programmed via JTAG, but it can be read back selectively through the JTAG programming interface, the UJTAG interface, or via direct FPGA core addressing. The pages of the FlashROM can be made secure to prevent read-back via JTAG. In that case, read-back on these secured pages is only possible by the FPGA core fabric or via UJTAG.

A 7-bit address from the FPGA core defines which of the eight pages (three MSBs) is being read, and which of the 16 bytes within the selected page (four LSBs) are being read. The FlashROM content can be read on a random basis; the access time is 10 ns for a device supporting commercial specifications. The FPGA core will be powered down during writing of the FlashROM content. FPGA power-down during FlashROM programming is managed on-chip, and FPGA core functionality is not available during programming of the FlashROM. Table 5-2 summarizes various FlashROM access scenarios.

| Access Mode | FlashROM Read | FlashROM Write |

|-------------|---------------|----------------|

| JTAG        | Yes           | Yes            |

| UJTAG       | Yes           | No             |

| FPGA core   | Yes           | No             |

Figure 5-6 shows the accessing of the FlashROM using the UJTAG macro. This is similar to FPGA core access, where the 7-bit address defines which of the eight pages (three MSBs) is being read and which of the 16 bytes within the selected page (four LSBs) are being read. Refer to the "UJTAG Applications in Microsemi's Low Power Flash Devices" section on page 363 for details on using the UJTAG macro to read the FlashROM.

Figure 5-7 on page 139 and Figure 5-8 on page 139 show the FlashROM access from the JTAG port. The FlashROM content can be read on a random basis. The three-bit address defines which page is being read or updated.

Figure 5-6 • Block Diagram of Using UJTAG to Read FlashROM Contents

# I/O Software Support

In Microsemi's Libero software, default settings have been defined for the various I/O standards supported. Changes can be made to the default settings via the use of attributes; however, not all I/O attributes are applicable for all I/O standards. Table 7-17 list the valid I/O attributes that can be manipulated by the user for each I/O standard.

Single-ended I/O standards in low power flash devices support up to five different drive strengths.

| I/O Standard         | SLEW<br>(output<br>only) | OUT_DRIVE<br>(output only) | SKEW<br>(all macros<br>with OE) | RES_PULL | OUT_LOAD<br>(output only) | COMBINE_REGISTER |

|----------------------|--------------------------|----------------------------|---------------------------------|----------|---------------------------|------------------|

| LVTTL/LVCMOS 3.3 V   | 1                        | ✓                          | 1                               | ✓        | ✓                         | 1                |

| LVCMOS 2.5 V         | 1                        | ✓                          | 1                               | <i>✓</i> | ✓                         | 1                |

| LVCMOS 2.5/5.0 V     | 1                        | 1                          | 1                               | 1        | ✓                         | ✓                |

| LVCMOS 1.8 V         | 1                        | 1                          | 1                               | 1        | ✓                         | 1                |

| LVCMOS 1.5 V         | 1                        | 1                          | 1                               | 1        | 1                         | ✓                |

| PCI (3.3 V)          |                          |                            | 1                               |          | 1                         | ✓                |

| PCI-X (3.3 V)        | 1                        |                            | 1                               |          | ✓                         | ✓                |

| LVDS, B-LVDS, M-LVDS |                          |                            | 1                               |          |                           | 1                |

| LVPECL               |                          |                            |                                 |          |                           | ✓                |

Table 7-17 • IGLOO and ProASIC3 I/O Attributes vs. I/O Standard Applications

Note: Applies to all 30 k gate devices.

Table 7-18 lists the default values for the above selectable I/O attributes as well as those that are preset for that I/O standard. See Table 7-14 on page 203 to Table 7-16 on page 203 for SLEW and OUT\_DRIVE settings.

| Table 7-18 • IGLOO and ProASIC3 I/O Default Attributes | 5 |

|--------------------------------------------------------|---|

|--------------------------------------------------------|---|

| I/O Standards           | SLEW<br>(output only)           | OUT_DRIVE<br>(output only)                   | SKEW<br>(tribuf and<br>bibuf<br>only) | RES_PULL | OUT_LOAD<br>(output<br>only) | COMBINE_REGISTER |

|-------------------------|---------------------------------|----------------------------------------------|---------------------------------------|----------|------------------------------|------------------|

| LVTTL/LVCMOS 3.3 V      |                                 |                                              | Off                                   | None     | 35 pF                        | -                |

| LVCMOS 2.5 V            | on page 203 to<br>Table 7-16 on | on page 203 to<br>Table 7-16 on<br>page 203. | Off                                   | None     | 35 pF                        | -                |

| LVCMOS 2.5/5.0 V        | page 203.                       |                                              | Off                                   | None     | 35 pF                        | -                |

| LVCMOS 1.8 V            | 1-0                             |                                              | Off                                   | None     | 35 pF                        | -                |

| LVCMOS 1.5 V            |                                 |                                              | Off                                   | None     | 35 pF                        | -                |

| PCI (3.3 V)             |                                 |                                              | Off                                   | None     | 10 pF                        | -                |

| PCI-X (3.3 V)           |                                 |                                              | Off                                   | None     | 10 pF                        | -                |

| LVDS, B-LVDS,<br>M-LVDS |                                 |                                              | Off                                   | None     | 0 pF                         | -                |

| LVPECL                  | 1                               |                                              | Off                                   | None     | 0 pF                         | -                |

Table 7-19 shows some high-level interfacing examples using low power flash devices.

|                    | (            | Clock           | I/O   |              |              |                 |

|--------------------|--------------|-----------------|-------|--------------|--------------|-----------------|

| Interface          | Туре         | Frequency       | Туре  | Signals In   | Signals Out  | Data I/O        |

| GM                 | Src Sync     | 125 MHz         | LVTTL | 8            | 8            | 125 Mbps        |

| ТВІ                | Src Sync     | 125 MHz         | LVTTL | 10           | 10           | 125 Mbps        |

| XSBI               | Src Sync     | 644 MHz         | LVDS  | 16           | 16           | 644 Mbps        |

| XGMI               | Src Sync DDR | 156 MHz         | HSTL1 | 32           | 32           | 312 Mbps        |

| FlexBus 3          | Sys Sync     | 104 MHz         | LVTTL | ≤ <b>32</b>  | ≤ <b>32</b>  | ≤ 104           |

| Pos-PHY3/SPI-3     | Sys Sync     | 104             | LVTTL | 8, 16, 32    | 8, 16, 32    | $\leq$ 104 Mbps |

| FlexBus 4/SPI-4.1  | Src Sync     | 200 MHz         | HSTL1 | 16,64        | 16,64        | 200 Mbps        |

| Pos-PHY4/SPI-4.2   | Src Sync DDR | ≥ 311 MHz       | LVDS  | 16           | 16           | $\geq$ 622 Mbps |

| SFI-4.1            | Src Sync     | 622 MHz         | LVDS  | 16           | 16           | 622 Mbps        |

| CSIX L1            | Sys Sync     | $\leq$ 250 MHz  | HSTL1 | 32,64,96,128 | 32,64,96,128 | $\leq$ 250 Mbps |

| Hyper Transport    | Sys Sync DDR | $\leq$ 800 MHz  | LVDS  | 2,4,8,16     | 2,4,8,16     | $\leq$ 1.6 Gbps |

| Rapid I/O Parallel | Sys Sync DDR | 250 MHz – 1 GHz | LVDS  | 8,16         | 8,16         | $\leq$ 2 Gbps   |

| Star Fabric        | CDR          |                 | LVDS  | 4            | 4            | 622 Mbps        |

Table 7-19 • High-Level Interface Examples

Note: Sys Sync = System Synchronous Clocking, Src Sync = Source Synchronous Clocking, and CDR = Clock and Data Recovery.

## Conclusion

IGLOO and ProASIC3 support for multiple I/O standards minimizes board-level components and makes possible a wide variety of applications. The Microsemi Designer software, integrated with Libero SoC, presents a clear visual display of I/O assignments, allowing users to verify I/O and board-level design requirements before programming the device. The IGLOO and ProASIC3 device I/O features and functionalities ensure board designers can produce low-cost and low power FPGA applications fulfilling the complexities of contemporary design needs.

|                    | Maximum Performance |                                                             |                                            |  |  |

|--------------------|---------------------|-------------------------------------------------------------|--------------------------------------------|--|--|

| Specification      | ProASIC3E           | IGLOOe V2 or V5<br>Devices, 1.5 V DC Core<br>Supply Voltage | IGLOOe V2, 1.2 V DC<br>Core Supply Voltage |  |  |

| LVTTL/LVCMOS 3.3 V | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |

| LVCMOS 2.5 V       | 250 MHz             | 230 MHz                                                     | TBD                                        |  |  |

| LVCMOS 1.8 V       | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |

| LVCMOS 1.5 V       | 130 MHz             | 120 MHz                                                     | TBD                                        |  |  |

| PCI                | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |

| PCI-X              | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |

| HSTL-I             | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |

| HSTL-II            | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |

| SSTL2-I            | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |

| SSTL2-II           | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |

| SSTL3-I            | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |

| SSTL3-II           | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |

| GTL+ 3.3 V         | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |

| GTL+ 2.5 V         | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |

| GTL 3.3 V          | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |

| GTL 2.5 V          | 300 MHz             | 275 MHz                                                     | TBD                                        |  |  |

| LVDS               | 350 MHz             | 300 MHz                                                     | TBD                                        |  |  |

| M-LVDS             | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |

| B LVDS             | 200 MHz             | 180 MHz                                                     | TBD                                        |  |  |

| LVPECL             | 350 MHz             | 300 MHz                                                     | TBD                                        |  |  |

### Table 8-7 • Maximum I/O Frequency for Single-Ended and Differential I/Os in All Banks in ProASIC3E Devices (maximum drive strength and high slew selected)

#### Table 8-11 • Hot-Swap Level 3

| Description                              | Hot-swap while bus idle                                                                                                                                                                                       |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | Yes                                                                                                                                                                                                           |

| Bus State                                | Held idle (no ongoing I/O processes during insertion/removal)                                                                                                                                                 |

| Card Ground Connection                   | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                                                                                |

| Device Circuitry Connected to Bus Pins   | Must remain glitch-free during power-up or power-<br>down                                                                                                                                                     |

| Example Application                      | Board bus shared with card bus is "frozen," and<br>there is no toggling activity on the bus. It is critical<br>that the logic states set on the bus signal not be<br>disturbed during card insertion/removal. |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices, all IGLOOe/ProASIC3E<br>devices: Compliant with two levels of staging (first:<br>GND; second: all other pins)                                                                              |

|                                          | Other IGLOO/ProASIC3 devices: Compliant:                                                                                                                                                                      |

|                                          | Option A – Two levels of staging (first: GND; second: all other pins) together with bus switch on the I/Os                                                                                                    |

|                                          | Option B – Three levels of staging (first: GND; second: supplies; third: all other pins)                                                                                                                      |

### Table 8-12 • Hot-Swap Level 4

| Description                              | Hot-swap on an active bus                                                                                                                           |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                  | Yes                                                                                                                                                 |

| Bus State                                | Bus may have active I/O processes ongoing, but device being inserted or removed must be idle.                                                       |

| Card Ground Connection                   | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                      |

| Device Circuitry Connected to Bus Pins   | Must remain glitch-free during power-up or power-<br>down                                                                                           |

| Example Application                      | There is activity on the system bus, and it is critical that the logic states set on the bus signal not be disturbed during card insertion/removal. |

| Compliance of IGLOO and ProASIC3 Devices | 30 k gate devices, all IGLOOe/ProASIC3E<br>devices: Compliant with two levels of staging (first:<br>GND; second: all other pins)                    |

|                                          | Other IGLOO/ProASIC3 devices: Compliant:                                                                                                            |

|                                          | Option A – Two levels of staging (first: GND;<br>second: all other pins) together with bus switch on<br>the I/Os                                    |

|                                          | Option B – Three levels of staging (first: GND; second: supplies; third: all other pins)                                                            |

I/O Structures in IGLOOe and ProASIC3E Devices

# Conclusion

IGLOOe and ProASIC3E support for multiple I/O standards minimizes board-level components and makes possible a wide variety of applications. The Microsemi Designer software, integrated with Libero SoC, presents a clear visual display of I/O assignments, allowing users to verify I/O and board-level design requirements before programming the device. The IGLOOe and ProASIC3E device I/O features and functionalities ensure board designers can produce low-cost and low power FPGA applications fulfilling the complexities of contemporary design needs.

# **Related Documents**

## **Application Notes**

Board-Level Considerations http://www.microsemi.com/soc/documents/ALL\_AC276\_AN.pdf

### **User's Guides**

ProASIC3 FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/PA3\_UG.pdf ProASIC3E FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/PA3E\_UG.pdf IGLOOe FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/IGLOOe\_UG.pdf Libero SoC User's Guide http://www.microsemi.com/soc/documents/libero\_ug.pdf IGLOO, Fusion, and ProASIC3 Macro Library Guide http://www.microsemi.com/soc/documents/pa3\_libguide\_ug.pdf SmartGen Core Reference Guide http://www.microsemi.com/soc/documents/genguide\_ug.pdf

### I/O Bank Resource Usage

This is an important portion of the report. The user must meet the requirements stated in this table. Figure 9-10 shows the I/O Bank Resource Usage table included in the I/O bank report:

#### Figure 9-10 • I/O Bank Resource Usage Table

The example in Figure 9-10 shows that none of the I/O macros is assigned to the bank because more than one VCCI is detected.

### I/O Voltage Usage

The I/O Voltage Usage table provides the number of VREF (E devices only) and  $V_{CCI}$  assignments required in the design. If the user decides to make I/O assignments manually (PDC or MVN), the issues listed in this table must be resolved before proceeding to Layout. As stated earlier, VREF assignments must be made if there are any voltage-referenced I/Os.

Figure 9-11 shows the I/O Voltage Usage table included in the I/O bank report.

### Figure 9-11 • I/O Voltage Usage Table

The table in Figure 9-11 indicates that there are two voltage-referenced I/Os used in the design. Even though both of the voltage-referenced I/O technologies have the same VCCI voltage, their VREF voltages are different. As a result, two I/O banks are needed to assign the VCCI and VREF voltages.

In addition, there are six single-ended I/Os used that have the same VCCI voltage. Since two banks are already assigned with the same VCCI voltage and there are enough unused bonded I/Os in

DDR for Microsemi's Low Power Flash Devices

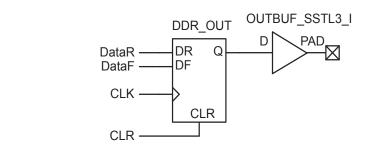

## **DDR Output Register**

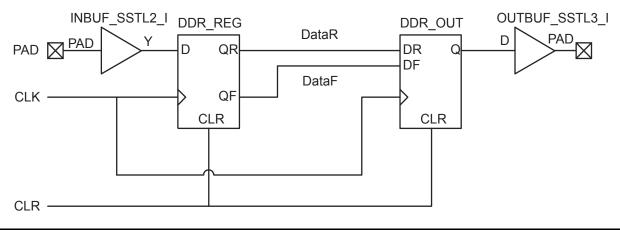

#### Figure 10-6 • DDR Output Register (SSTL3 Class I)

### Verilog

```

module DDR_OutBuf_SSTL3_I(DataR,DataF,CLR,CLK,PAD);

```

input DataR, DataF, CLR, CLK; output PAD;

wire Q, VCC;

```

VCC VCC_1_net(.Y(VCC));

DDR_OUT DDR_OUT_0_inst(.DR(DataR),.DF(DataF),.CLK(CLK),.CLR(CLR),.Q(Q));

OUTBUF_SSTL3_I OUTBUF_SSTL3_I_0_inst(.D(Q),.PAD(PAD));

```

endmodule

### VHDL

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3; use proasic3.all;

entity DDR_OutBuf_SSTL3_I is

port(DataR, DataF, CLR, CLK : in std_logic; PAD : out std_logic) ;

end DDR_OutBuf_SSTL3_I;

architecture DEF_ARCH of DDR_OutBuf_SSTL3_I is

component DDR_OUT

port(DR, DF, CLK, CLR : in std_logic := 'U'; Q : out std_logic) ;

end component;

component OUTBUF_SSTL3_I

port(D : in std_logic := 'U'; PAD : out std_logic) ;

end component;

component VCC

port( Y : out std_logic);

end component;

signal Q, VCC_1_net : std_logic ;

```

begin

```

VCC_2_net : VCC port map(Y => VCC_1_net);

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

OUTBUF_SSTL3_I_0_inst : OUTBUF_SSTL3_I

port map(D => Q, PAD => PAD);

```

end DEF\_ARCH;

DDR for Microsemi's Low Power Flash Devices

```

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

TRIBUFF_F_8U_0_inst : TRIBUFF_F_8U

port map(D => Q, E => TrienAux, PAD => PAD);

```

end DEF\_ARCH;

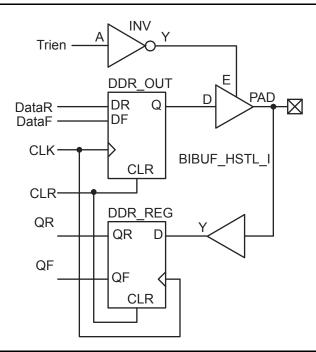

## **DDR Bidirectional Buffer**

Figure 10-8 • DDR Bidirectional Buffer, LOW Output Enable (HSTL Class II)

### Verilog

module DDR\_BiDir\_HSTL\_I\_LowEnb(DataR,DataF,CLR,CLK,Trien,QR,QF,PAD);

```

input DataR, DataF, CLR, CLK, Trien;

output QR, QF;

inout PAD;

wire TrienAux, D, Q;

INV Inv_Tri(.A(Trien), .Y(TrienAux));

DDR_OUT DDR_OUT_0_inst(.DR(DataR),.DF(DataF),.CLK(CLK),.CLR(CLR),.Q(Q));

DDR_REG DDR_REG_0_inst(.D(D),.CLK(CLK),.CLR(CLR),.QR(QR),.QF(QF));

BIBUF_HSTL_I BIBUF_HSTL_I_0_inst(.PAD(PAD),.D(Q),.E(TrienAux),.Y(D));

```

endmodule

DDR for Microsemi's Low Power Flash Devices

# **Design Example**

Figure 10-9 shows a simple example of a design using both DDR input and DDR output registers. The user can copy the HDL code in Libero SoC software and go through the design flow. Figure 10-10 and Figure 10-11 on page 283 show the netlist and ChipPlanner views of the ddr\_test design. Diagrams may vary slightly for different families.

Figure 10-9 • Design Example

Figure 10-10 • DDR Test Design as Seen by NetlistViewer for IGLOO/e Devices

DDR for Microsemi's Low Power Flash Devices

```

module ddr_test(DIN, CLK, CLR, DOUT);

input DIN, CLK, CLR;

output DOUT;

Inbuf_ddr Inbuf_ddr (.PAD(DIN), .CLR(clr), .CLK(clk), .QR(qr), .QF(qf));

Outbuf_ddr Outbuf_ddr (.DataR(qr),.DataF(qf), .CLR(clr), .CLK(clk),.PAD(DOUT));

INBUF INBUF_CLR (.PAD(CLR), .Y(clr));

INBUF INBUF_CLK (.PAD(CLK), .Y(clk));

```

endmodule

## **Simulation Consideration**

Microsemi DDR simulation models use inertial delay modeling by default (versus transport delay modeling). As such, pulses that are shorter than the actual gate delays should be avoided, as they will not be seen by the simulator and may be an issue in post-routed simulations. The user must be aware of the default delay modeling and must set the correct delay model in the simulator as needed.

## Conclusion

Fusion, IGLOO, and ProASIC3 devices support a wide range of DDR applications with different I/O standards and include built-in DDR macros. The powerful capabilities provided by SmartGen and its GUI can simplify the process of including DDR macros in designs and minimize design errors. Additional considerations should be taken into account by the designer in design floorplanning and placement of I/O flip-flops to minimize datapath skew and to help improve system timing margins. Other system-related issues to consider include PLL and clock partitioning.

# **Generating Programming Files**

## Generation of the Programming File in a Trusted Environment— Application 1

As discussed in the "Application 1: Trusted Environment" section on page 309, in a trusted environment, the user can choose to program the device with plaintext bitstream content. It is possible to use plaintext for programming even when the FlashLock Pass Key option has been selected. In this application, it is not necessary to employ AES encryption protection. For AES encryption settings, refer to the next sections.

The generated programming file will include the security setting (if selected) and the plaintext programming file content for the FPGA array, FlashROM, and/or FBs. These options are indicated in Table 12-2 and Table 12-3.

| Security Protection   | FlashROM Only | FPGA Core Only | Both FlashROM<br>and FPGA |

|-----------------------|---------------|----------------|---------------------------|

| No AES / no FlashLock | 1             | ✓              | ✓                         |

| FlashLock only        | 1             | ✓              | ✓                         |

| AES and FlashLock     | _             | _              | _                         |

#### Table 12-2 • IGLOO and ProASIC3 Plaintext Security Options, No AES

#### Table 12-3 • Fusion Plaintext Security Options

| Security Protection   | FlashROM Only | FPGA Core Only | FB Core Only | All |

|-----------------------|---------------|----------------|--------------|-----|

| No AES / no FlashLock | ✓             | 1              | 1            | 1   |

| FlashLock             | ✓             | 1              | 1            | 1   |

| AES and FlashLock     | _             | _              | _            | _   |

Note: For all instructions, the programming of Flash Blocks refers to Fusion only.

For this scenario, generate the programming file as follows:

1. Select the **Silicon features to be programmed** (Security Settings, FPGA Array, FlashROM, Flash Memory Blocks), as shown in Figure 12-10 on page 314 and Figure 12-11 on page 314. Click **Next**.

If **Security Settings** is selected (i.e., the FlashLock security Pass Key feature), an additional dialog will be displayed to prompt you to select the security level setting. If no security setting is selected, you will be directed to Step 3.

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

# Microsemi's Flash Families Support Voltage Switching Circuit

The flash FPGAs listed in Table 14-1 support the voltage switching circuit feature and the functions described in this document.

Table 14-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit

| Series   | Family <sup>*</sup>  | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 14-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 14-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*