Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                               |  |

|--------------------------------|-------------------------------------------------------------------------------|--|

| Product Status                 | Obsolete                                                                      |  |

| Number of LABs/CLBs            | -                                                                             |  |

| Number of Logic Elements/Cells | -                                                                             |  |

| Total RAM Bits                 | 516096                                                                        |  |

| Number of I/O                  | 147                                                                           |  |

| Number of Gates                | 300000                                                                        |  |

| Voltage - Supply               | 1.14V ~ 1.575V                                                                |  |

| Mounting Type                  | Surface Mount                                                                 |  |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                            |  |

| Package / Case                 | 208-BFQFP                                                                     |  |

| Supplier Device Package        | 208-PQFP (28x28)                                                              |  |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe3000l-1pq208i |  |

|                                |                                                                               |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Flash\*Freeze Technology and Low Power Modes

The INBUF\_FF must be driven by a top-level input port of the design.

The INBUF\_FF AND the ULSICC macro must be used to enable type 2 Flash\*Freeze mode.

For type 2 Flash\*Freeze mode, the INBUF\_FF MUST drive some logic in the design.

For type 1 Flash\*Freeze mode, the INBUF\_FF may drive some logic in the design, but it may also be left floating.

Only one INBUF\_FF may be instantiated in a device.

The FF pin threshold voltages are defined by VCCI and the supported single-ended I/O standard in the corresponding I/O bank.

The FF pin Schmitt trigger option may be configured in the I/O attribute editor in Microsemi's Designer software. The Schmitt trigger optionaly available for IGLOOe, IGLOO nano, IGLOO PLUS, ProASIC3EL, and RT ProASIC3 devices.

A 2 ns glitch filter resides in the Flash\*Fr $\overline{\mathbf{e}}\mathbf{z}\mathbf{e}$ nology block to filter unwanted glitches on the FF pin.

## ULSICC

The User Low Static ICC (ULSICC) macro allows the FPGA core to access the Flash\*Freeze Technology block so that entering and exiting Flash\*Freezedemoan be controlled by the user's design. The ULSICC macro enables a hard block with an available LSICC input port, as showing unre 2-3 on page 27 and Figure 2-10 on page 37 Design rules for the ULSICC macro are as follows:

The ULSICC macro by itself cannot enable Flash\*Freeze mode. The INBUF\_FF AND the ULSICC macro must both be used **eo**able type 2 Flash\*Freeze mode.

The ULSICC controls entering the Flash\*Freezeode by asserting the LSICC input (logic '1') of the ULSICC macro. The FF pin must also be assed (logic '0') to enter Flash\*Freeze mode.

When the LSICC signal is 'O', the device cathmenter Flash\*Freeze mode; and if already in Flash\*Freeze mode, it will exit.

When the ULSICC macro is not instantiated enulster's design, the LSICC port will be tied High.

#### Flash\*Freeze Management IP

The Flash\*Freeze management IP can be configuredhytithe Libero (or SmartGen) core generator in a simple, intuitive intercefe. With the core configution tool, users can select the number of clocks to be gated, and select whether or not to implements the eping. All port names on the Flash\*Freeze management IP block can be renamed by the user.

The clock gating (filter) block bloc

When housekeeping is NOT used, the WAIT\_HOUSEKEEPING signal will be automatically fed back into DONE\_HOUSEKEEPING inside the core, and the ports will not be available at the IP core interface.

The INBUF\_FF macro is automatically instantiated within the IP core.

The INBUF\_FF port (default name is "Flash\_Freeze\_N") must be connected to a top-level input port of the design.

The ULSICC macro is automatical instantiated within the IP carred the LSICC signal is driven by the FSM.

Timing analysis can be performed on the clock domatithe source clock (i.e., input to the clock gating filters). For example, GEK in becomes CLK in\_gated, the timing can be performed on the CLK in domain in SmartTime.

The gated clocks can be added to the clock listheifuser wishes tagnalyze these clocks specifically. The user can locatable gated clocks by looking foostance names such as those below:

Top/ff1/ff\_1\_wrapper\_inst/user\_ff\_1\_wrapper/Primary\_Filter\_Instance/ Latch\_For\_Clock\_Gating:Q Top/ff1/ff\_1\_wrapper\_inst/user\_ff\_1\_wrapper/genblk1.genblk2.secondary\_filter[0]. seconday\_filter\_instance/Latch\_For\_Clock\_Gating:Q Top/ff1/ff\_1\_wrapper\_inst/user\_ff\_1\_wrapper/genblk1.genblk2.secondary\_filter[1]. seconday\_filter\_instance/Latch\_For\_Clock\_Gating:Q

ProASIC3L FPGA Fabric User s Guide

During Layout, Designer will assign two of the signals to quadrant global locations.

## Step 3 (optional)

You can also assign the QCLK1\_c and QCLK2\_c nets to quadrant regions using the following PDC commands:

$assign\_local\_clock \ net \ QCLK1\_c \ type \ quadrant \ UL \\ assign\_local\_clock \ net \ QCLK2\_c \ type \ quadrant \ LL \\$

### Step 4

Import this PDC with the netlist and run Compile. Again will see the following in the Compile report:

The following nets have been assigned to a global resource: Fanout Type Name

-----

| 1536                                                                          | INT_NET   | Net     | : EN_ALL_c                |  |

|-------------------------------------------------------------------------------|-----------|---------|---------------------------|--|

|                                                                               |           |         | Driver: EN_ALL_pad_CLKINT |  |

|                                                                               |           |         | Source: AUTO PROMOTED     |  |

| 1536                                                                          | SET/RESET | _NET N  | et : ACLR_c               |  |

|                                                                               |           |         | Driver: ACLR_pad_CLKINT   |  |

|                                                                               |           |         | Source: AUTO PROMOTED     |  |

| 256                                                                           | CLK_NET   | Net     | : QCLK3_c                 |  |

|                                                                               |           |         | Driver: QCLK3_pad_CLKINT  |  |

|                                                                               |           |         | Source: AUTO PROMOTED     |  |

| 256                                                                           | CLK_NET   | Net     | : \$1N14                  |  |

|                                                                               |           |         | Driver: \$1I5/Core        |  |

|                                                                               |           |         | Source: ESSENTIAL         |  |

| 256                                                                           | CLK_NET   | Net     | : \$1N12                  |  |

|                                                                               |           |         | Driver: \$116/Core        |  |

|                                                                               |           |         | Source: ESSENTIAL         |  |

| 256                                                                           | CLK_NET   | Net     | : \$1N1O                  |  |

|                                                                               |           |         | Driver: \$116/Core        |  |

|                                                                               |           |         | Source: ESSENTIAL         |  |

| The following nets have been assigned to a quadrant clock resource using PDC: |           |         |                           |  |

| Fanout                                                                        | Туре      | Name    |                           |  |

| 256                                                                           | CLK_NET   | <br>Net |                           |  |

| 200                                                                           | OEK_NET   | Not     | Driver: QCLK1_pad_CLKINT  |  |

|                                                                               |           |         | Region: quadrant_UL       |  |

| 256                                                                           | CLK_NET   | Net     | : QCLK2_c                 |  |

| 200                                                                           | SER_RET   |         | Driver: QCLK2_pad_CLKINT  |  |

|                                                                               |           |         | Region: guadrant_LL       |  |

|                                                                               |           |         | tog.on quantini_EE        |  |

#### Step 5

Run Layout.

# Global Management in PLL Design

This section describes the legal global network coimmecto PLLs in the low power flash devices. For detailed information on using PLLs, referctock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" section on page 77 Microsemi recommends that you use the dedicated global pins to directly drive the reference clock input earlier offer the flexibility to connect other signals to reference clock inputs. Each PLL is associated with three global net Figures 3-5 on page 52 There are some limitations, such as when tryings to the global and PLL at the same time:

If you use a PLL with only primary output, you can still use the remaining two free global networks.

If you use three globals associated with a PLLtion ayou cannot use tReL on that location.

If the YB or YC output is used standalone ill to acupy one global, even though this signal does not go to the global network.

I/O Structures in IGLOOe and ProASIC3E Devices

## 5 V Output Tolerance

IGLOO and ProASIC3 I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, the I/Os can directly drive signals into 5 V TTL receivers. In fact, VOL = 0.4 V and VOH = 2.4 V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceeds the VIL = 0.8 V and VIH = 2 V level requirements of 5 V TTL receivers. Therefore, level 1 and level 0 will be recognized correctly by 5 V TTL receivers.

# **Schmitt Trigger**

A Schmitt trigger is a buffer used to convert a slow or noisy input signal into a clean one before passing it to the FPGA. Using Schmitt trigger buffers guarantees a fast, noise-free input signal to the FPGA.

ProASIC3E devices have Schmitt triggers built into their I/O circuitry. The Schmitt trigger is available for the LVTTL, LVCMOS, and 3.3 V PCI I/O standards.

This feature can be implemented by using a Physical Design Constraints (PDC) command (Table 8-6 on page 218) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

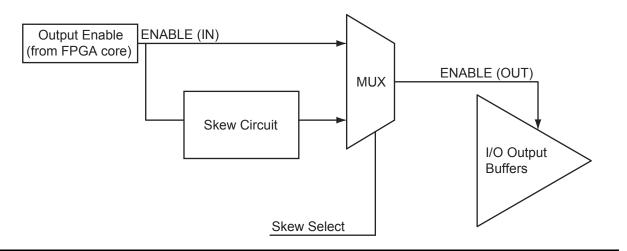

# Selectable Skew between Output Buffer Enable and Disable Times

Low power flash devices have a configurable skew block in the output buffer circuitry that can be enabled to delay output buffer assertion without affecting deassertion time. Since this skew block is only available for the OE signal, the feature can be used in tristate and bidirectional buffers. A typical 1.2 ns delay is added to the OE signal to prevent potential bus contention. Refer to the appropriate family datasheet for detailed timing diagrams and descriptions.

The Skew feature is available for all I/O standards.

This feature can be implemented by using a PDC command (Table 8-6 on page 218) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

The configurable skew block is used to delay output buffer assertion (enable) without affecting deassertion (disable) time.