Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells |                                                                             |

| Total RAM Bits                 | 516096                                                                      |

| Number of I/O                  | 620                                                                         |

| Number of Gates                | 300000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 896-BGA                                                                     |

| Supplier Device Package        | 896-FBGA (31x31)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe3000l-fg896 |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

FPGA Array Architecture in Low Power Flash Devices

### **Routing Architecture**

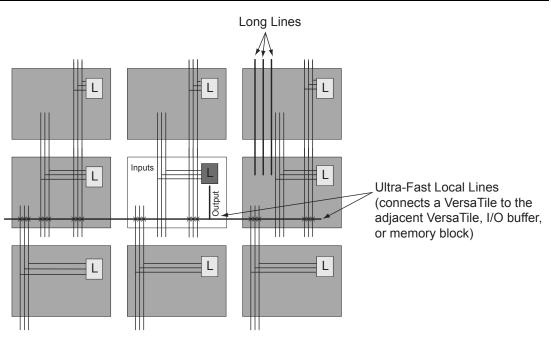

The routing structure of low power flash devices is designed to provide high performance through a flexible four-level hierarchy of routing resources: ultra-fast local resources; efficient long-line resources; high-speed, very-long-line resources; and the high-performance VersaNet networks.

The ultra-fast local resources are dedicated lines that allow the output of each VersaTile to connect directly to every input of the eight surrounding VersaTiles (Figure 1-10). The exception to this is that the SET/CLR input of a VersaTile configured as a D-flip-flop is driven only by the VersaTile global network.

The efficient long-line resources provide routing for longer distances and higher-fanout connections. These resources vary in length (spanning one, two, or four VersaTiles), run both vertically and horizontally, and cover the entire device (Figure 1-11 on page 19). Each VersaTile can drive signals onto the efficient long-line resources, which can access every input of every VersaTile. Routing software automatically inserts active buffers to limit loading effects.

The high-speed, very-long-line resources, which span the entire device with minimal delay, are used to route very long or high-fanout nets: length  $\pm 12$  VersaTiles in the vertical direction and length  $\pm 16$  in the horizontal direction from a given core VersaTile (Figure 1-12 on page 19). Very long lines in low power flash devices have been enhanced over those in previous ProASIC families. This provides a significant performance boost for long-reach signals.

The high-performance VersaNet global networks are low-skew, high-fanout nets that are accessible from external pins or internal logic. These nets are typically used to distribute clocks, resets, and other high-fanout nets requiring minimum skew. The VersaNet networks are implemented as clock trees, and signals can be introduced at any junction. These can be employed hierarchically, with signals accessing every input of every VersaTile. For more details on VersaNets, refer to the "Global Resources in Low Power Flash Devices" section on page 47.

Note: Input to the core cell for the D-flip-flop set and reset is only available via the VersaNet global network connection.

Figure 1-10 • Ultra-Fast Local Lines Connected to the Eight Nearest Neighbors

FPGA Array Architecture in Low Power Flash Devices

# **Related Documents**

## **User's Guides**

Designer User's Guide

http://www.microsemi.com/soc/documents/designer\_ug.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                                                                                                          | Page   |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|

| August 2012             | The "I/O State of Newly Shipped Devices" section is new (SAR 39542).                                                                                                                                                                                                                                                             |        |  |  |  |  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                        |        |  |  |  |  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 1-1 • Flash-Based FPGAs.                                                                                                                                                                                                                                                | 10     |  |  |  |  |

|                         | Figure 1-2 • IGLOO and ProASIC3 nano Device Architecture Overview with Two I/O<br>Banks (applies to 10 k and 30 k device densities, excluding IGLOO PLUS devices)<br>through Figure 1-5 • IGLOO, IGLOO nano, ProASIC3 nano, and ProASIC3/L Device<br>Architecture Overview with Four I/O Banks (AGL600 device is shown) are new. | 11, 12 |  |  |  |  |

|                         | Table 1-4 • IGLOO nano and ProASIC3 nano Array Coordinates is new.                                                                                                                                                                                                                                                               | 17     |  |  |  |  |

| v1.3<br>(October 2008)  | The title of this document was changed from "Core Architecture of IGLOO and ProASIC3 Devices" to "FPGA Array Architecture in Low Power Flash Devices."                                                                                                                                                                           | 9      |  |  |  |  |

|                         | The "FPGA Array Architecture Support" section was revised to include new families and make the information more concise.                                                                                                                                                                                                         | 10     |  |  |  |  |

|                         | Table 1-2 • IGLOO and ProASIC3 Array Coordinates was updated to include Military ProASIC3/EL and RT ProASIC3 devices.                                                                                                                                                                                                            | 16     |  |  |  |  |

| v1.2<br>(June 2008)     | <ul> <li>The following changes were made to the family descriptions in Table 1-1 • Flash-Based FPGAs:</li> <li>ProASIC3L was updated to include 1.5 V.</li> <li>The number of PLLs for ProASIC3E was changed from five to six.</li> </ul>                                                                                        | 10     |  |  |  |  |

| v1.1<br>(March 2008)    | Table 1-1 • Flash-Based FPGAs and the accompanying text was updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "Device Overview" section are new.                                                                                                                                                     | 10     |  |  |  |  |

|                         | The "Device Overview" section was updated to note that 15 k devices do not support SRAM or FIFO.                                                                                                                                                                                                                                 | 11     |  |  |  |  |

|                         | Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks is new.                                                                                                                                                                                                                                                 | 13     |  |  |  |  |

|                         | Table 1-2 • IGLOO and ProASIC3 Array Coordinates was updated to add A3P015 and AGL015.                                                                                                                                                                                                                                           | 16     |  |  |  |  |

|                         | Table 1-3 • IGLOO PLUS Array Coordinates is new.                                                                                                                                                                                                                                                                                 | 16     |  |  |  |  |

| /О Туре      | Beginning of I/O Name | Notes                                                    |

|--------------|-----------------------|----------------------------------------------------------|

| Single-Ended | GAAO/IOuxwByVz        | Only one of the I/Os can be directly connected to        |

|              | GAA1/IOuxwByVz        | quadrant global at a time                                |

|              | GAA2/IOuxwByVz        |                                                          |

|              | GABO/IOuxwByVz        | Only one of the I/Os can be directly connected to        |

|              | GAB1/IOuxwByVz        | quadrant global at a time.                               |

|              | GAB2/IOuxwByVz        |                                                          |

|              | GAC0/IOuxwByVz        | Only one of the I/Os can be directly connected to        |

|              | GAC1/IOuxwByVz        | quadrant global at a time.                               |

|              | GAC2/IOuxwByVz        |                                                          |

|              | GBAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GBA1/IOuxwByVz        | at a time.                                               |

|              | GBA2/IOuxwByVz        |                                                          |

|              | GBBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GBB1/IOuxwByVz        | at a time.                                               |

|              | GBB2/IOuxwByVz        |                                                          |

|              | GBC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GBC1/IOuxwByVz        | at a time.                                               |

|              | GBC2/IOuxwByVz        |                                                          |

|              | GDAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GDA1/IOuxwByVz        | at a time.                                               |

|              | GDA2/IOuxwByVz        |                                                          |

|              | GDBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GDB1/IOuxwByVz        | at a time.                                               |

|              | GDB2/IOuxwByVz        |                                                          |

|              | GDC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GDC1/IOuxwByVz        | at a time.                                               |

|              | GDC2/IOuxwByVz        |                                                          |

|              | GEAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GEA1/IOuxwByVz        | at a time.                                               |

|              | GEA2/IOuxwByVz        |                                                          |

|              | GEBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GEB1/IOuxwByVz        | at a time.                                               |

|              | GEB2/IOuxwByVz        |                                                          |

|              | GEC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a glob |

|              | GEC1/IOuxwByVz        | at a time.                                               |

|              | GEC2/IOuxwByVz        |                                                          |

### Table 3-3 • Quadrant Global Pin Name

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

Global Resources in Low Power Flash Devices

# **Design Recommendations**

The following sections provide design flow recommendations for using a global network in a design.

- "Global Macros and I/O Standards"

- "Global Macro and Placement Selections" on page 64

- "Using Global Macros in Synplicity" on page 66

- "Global Promotion and Demotion Using PDC" on page 67

- "Spine Assignment" on page 68

- "Designer Flow for Global Assignment" on page 69

- "Simple Design Example" on page 71

- "Global Management in PLL Design" on page 73

- "Using Spines of Occupied Global Networks" on page 74

### **Global Macros and I/O Standards**

The larger low power flash devices have six chip global networks and four quadrant global networks. However, the same clock macros are used for assigning signals to chip globals and quadrant globals. Depending on the clock macro placement or assignment in the Physical Design Constraint (PDC) file or MultiView Navigator (MVN), the signal will use the chip global network or quadrant network. Table 3-8 lists the clock macros available for low power flash devices. Refer to the *IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide* for details.

| Macro Name         | Description                                                                                                   | Symbol                                        |

|--------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| CLKBUF             | Input macro for Clock Network                                                                                 |                                               |

| CLKBUF_x           | Input macro for Clock Network with specific I/O standard                                                      |                                               |

| CLKBUF_LVDS/LVPECL | LVDS or LVPECL input macro<br>for Clock Network (not<br>supported for IGLOO nano or<br>ProASIC3 nano devices) | PADP<br>CLKBUF LVDS Y<br>PADN<br>PADN<br>PADN |

| CLKINT             | Macro for internal clock interface                                                                            |                                               |

| CLKBIBUF           | Bidirectional macro with input<br>dedicated to routed Clock<br>Network                                        |                                               |

Use these available macros to assign a signal to the global network. In addition to these global macros, PLL and CLKDLY macros can also drive the global networks. Use I/O–standard–specific clock macros (CLKBUF\_x) to instantiate a specific I/O standard for the global signals. Table 3-9 on page 63 shows the list of these I/O–standard–specific macros. Note that if you use these I/O–standard–specific clock macros, you cannot change the I/O standard later in the design stage. If you use the regular CLKBUF macro, you can use MVN or the PDC file in Designer to change the I/O standard. The default I/O

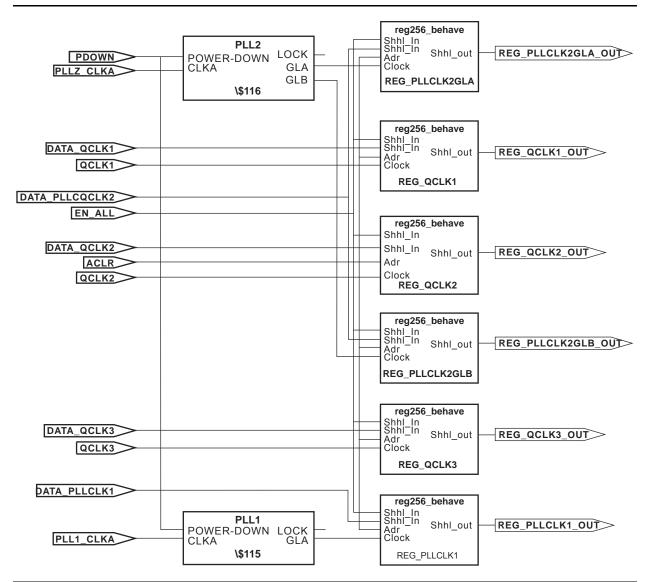

## Simple Design Example

Consider a design consisting of six building blocks (shift registers) and targeted for an A3PE600-PQ208 (Figure 3-16 on page 68). The example design consists of two PLLs (PLL1 has GLA only; PLL2 has both GLA and GLB), a global reset (ACLR), an enable (EN\_ALL), and three external clock domains (QCLK1, QCLK2, and QCLK3) driving the different blocks of the design. Note that the PQ208 package only has two PLLs (which access the chip global network). Because of fanout, the global reset and enable signals need to be assigned to the chip global resources. There is only one free chip global for the remaining global (QCLK1, QCLK2, QCLK3). Place two of these signals on the quadrant global resource. The design example demonstrates manually assignment of QCLK1 and QCLK2 to the quadrant global using the PDC command.

Figure 3-19 • Block Diagram of the Global Management Example Design

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

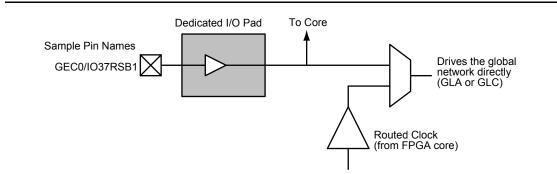

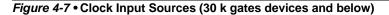

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

Notes:

- Represents the global input pins. Globals have direct access to the clock conditioning block and are not routed via the FPGA fabric. Refer to the "User I/O Naming Conventions in I/O Structures" chapter of the appropriate device user's guide.

- 2. Instantiate the routed clock source input as follows:

- a) Connect the output of a logic element to the clock input of a PLL, CLKDLY, or CLKINT macro.

- b) Do not place a clock source I/O (INBUF or INBUF\_LVPECL/LVDS/B-LVDS/M-LVDS/DDR) in a relevant global pin location.

- 3. IGLOO nano and ProASIC3 nano devices do not support differential inputs.

Figure 4-8 • Clock Input Sources Including CLKBUF, CLKBUF\_LVDS/LVPECL, and CLKINT (60 k gates devices and above)

```

wire VCC, GND;

VCC VCC_1_net(.Y(VCC));

GND GND_1_net(.Y(GND));

PLL Core(.CLKA(CLKA), .EXTFB(GND), .POWERDOWN(POWERDOWN),

.GLA(GLA), .LOCK(LOCK), .GLB(), .YB(), .GLC(), .YC(),

.OADIV0(GND), .OADIV1(GND), .OADIV2(GND), .OADIV3(GND),

.OADIV4(GND), .OAMUX0(GND), .OAMUX1(GND), .OAMUX2(VCC),

.DLYGLA0(GND), .DLYGLA1(GND), .DLYGLA2(GND), .DLYGLA3(GND)

, .DLYGLA4(GND), .OBDIV0(GND), .OBDIV1(GND), .OBDIV2(GND),

.OBDIV3(GND), .OBDIV4(GND), .OBMUX0(GND), .OBMUX1(GND),

.OBMUX2(GND), .DLYYB0(GND), .DLYYB1(GND), .DLYYB2(GND),

.DLYYB3(GND), .DLYYB4(GND), .DLYGLB0(GND), .DLYGLB1(GND),

.DLYGLB2(GND), .DLYGLB3(GND), .DLYGLB4(GND), .OCDIV0(GND),

.OCDIV1(GND), .OCDIV2(GND), .OCDIV3(GND), .OCDIV4(GND),

.OCMUX0(GND), .OCMUX1(GND), .OCMUX2(GND), .DLYYC0(GND),

.DLYYC1(GND), .DLYYC2(GND), .DLYYC3(GND), .DLYYC4(GND),

.DLYGLC0(GND), .DLYGLC1(GND), .DLYGLC2(GND), .DLYGLC3(GND)

, .DLYGLC4(GND), .FINDIV0(VCC), .FINDIV1(GND), .FINDIV2(

VCC), .FINDIV3(GND), .FINDIV4(GND), .FINDIV5(GND),

.FINDIV6(GND), .FBDIV0(VCC), .FBDIV1(GND), .FBDIV2(VCC),

.FBDIV3(GND), .FBDIV4(GND), .FBDIV5(GND), .FBDIV6(GND),

.FBDLY0(GND), .FBDLY1(GND), .FBDLY2(GND), .FBDLY3(GND),

.FBDLY4(GND), .FBSEL0(VCC), .FBSEL1(GND), .XDLYSEL(GND),

.VCOSEL0(GND), .VCOSEL1(GND), .VCOSEL2(GND));

defparam Core.VCOFREQUENCY = 33.000;

endmodule

```

The "PLL Configuration Bits Description" section on page 106 provides descriptions of the PLL configuration bits for completeness. The configuration bits are shown as busses only for purposes of illustration. They will actually be broken up into individual pins in compilation libraries and all simulation models. For example, the FBSEL[1:0] bus will actually appear as pins FBSEL1 and FBSEL0. The setting of these select lines for the static PLL configuration is performed by the software and is completely transparent to the user.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, ADDRB should be tied to ground.

|       | ADDRx   |        |  |  |

|-------|---------|--------|--|--|

| D×W   | Unused  | Used   |  |  |

| 4k×1  | None    | [11:0] |  |  |

| 2k×2  | [11]    | [10:0] |  |  |

| 1k×4  | [11:10] | [9:0]  |  |  |

| 512×9 | [11:9]  | [8:0]  |  |  |

Note: The "x" in ADDRx implies A or B.

### DINA and DINB

These are the input data signals, and they are nine bits wide. Not all nine bits are valid in all configurations. When a data width less than nine is specified, unused high-order signals must be grounded (Table 6-4).

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, DINB should be tied to ground.

### DOUTA and DOUTB

These are the nine-bit output data signals. Not all nine bits are valid in all configurations. As with DINA and DINB, high-order bits may not be used (Table 6-4). The output data on unused pins is undefined.

|       | DINx/DOUTx |       |  |  |

|-------|------------|-------|--|--|

| D×W   | Unused     | Used  |  |  |

| 4k×1  | [8:1]      | [0]   |  |  |

| 2k×2  | [8:2]      | [1:0] |  |  |

| 1k×4  | [8:4]      | [3:0] |  |  |

| 512×9 | None       | [8:0] |  |  |

Note: The "x" in DINx or DOUTx implies A or B.

### RAM512X18 Macro

RAM512X18 is the two-port configuration of the same RAM block (Figure 6-5 on page 156). Like the RAM4K9 nomenclature, the RAM512X18 nomenclature refers to both the deepest possible configuration and the widest possible configuration the two-port RAM block can assume. In two-port mode, the RAM block can be configured to either the 512×9 aspect ratio or the 256×18 aspect ratio. RAM512X18 is also fully synchronous and has the following features:

- Dedicated read and write ports

- · Active-low read and write enables

- · Selectable pipelined or nonpipelined read

- Active-low asynchronous reset

- Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

Table 6-8 and Table 6-9 show the maximum potential width and depth configuration for each device. Note that 15 k and 30 k gate devices do not support RAM or FIFO.

| Device                            |                                        |                   | Maximum Potential Width <sup>1</sup> |                | Maximum Potential Depth <sup>2</sup> |       |

|-----------------------------------|----------------------------------------|-------------------|--------------------------------------|----------------|--------------------------------------|-------|

| IGLOO<br>IGLOO nano<br>IGLOO PLUS | ProASIC3<br>ProASIC3 nano<br>ProASIC3L | RAM<br>Block<br>s | Depth                                | Width          | Depth                                | Width |

| AGL060<br>AGLN060<br>AGLP060      | A3P060<br>A3PN060                      | 4                 | 256                                  | 72 (4×18)      | 16,384 (4,096×4)                     | 1     |

| AGL125<br>AGLN125<br>AGLP125      | A3P125<br>A3PN125                      | 8                 | 256                                  | 144 (8×18)     | 32,768 (4,094×8)                     | 1     |

| AGL250<br>AGLN250                 | A3P250/L<br>A3PN250                    | 8                 | 256                                  | 144 (8×18)     | 32,768 (4,096×8)                     | 1     |

| AGL400                            | A3P400                                 | 12                | 256                                  | 216 (12×18)    | 49,152 (4,096×12)                    | 1     |

| AGL600                            | A3P600/L                               | 24                | 256                                  | 432 (24×18)    | 98,304 (4,096×24)                    | 1     |

| AGL1000                           | A3P1000/L                              | 32                | 256                                  | 576 (32×18)    | 131,072 (4,096×32)                   | 1     |

| AGLE600                           | A3PE600                                | 24                | 256                                  | 432 (24×18)    | 98,304 (4,096×24)                    | 1     |

|                                   | A3PE1500                               | 60                | 256                                  | 1,080 (60×18)  | 245,760 (4,096×60)                   | 1     |

| AGLE3000                          | A3PE3000/L                             | 112               | 256                                  | 2,016 (112×18) | 458,752 (4,096×112)                  | 1     |

Notes:

1. Maximum potential width uses the two-port configuration.

2. Maximum potential depth uses the dual-port configuration.

### Table 6-9 • Memory Availability per Fusion Device

|         |            | Maximu      | m Potential Width <sup>1</sup> | Maximum Potential  | Depth <sup>2</sup> |

|---------|------------|-------------|--------------------------------|--------------------|--------------------|

| Device  | RAM Blocks | Depth Width |                                | Depth              | Width              |

| AFS090  | 6          | 256         | 108 (6×18)                     | 24,576 (4,094×6)   | 1                  |

| AFS250  | 8          | 256         | 144 (8×18)                     | 32,768 (4,094×8)   | 1                  |

| AFS600  | 24         | 256         | 432 (24×18)                    | 98,304 (4,096×24)  | 1                  |

| AFS1500 | 60         | 256         | 1,080 (60×18)                  | 245,760 (4,096×60) | 1                  |

Notes:

1. Maximum potential width uses the two-port configuration.

2. Maximum potential depth uses the dual-port configuration.

# ProASIC3L FPGA Fabric User's Guide

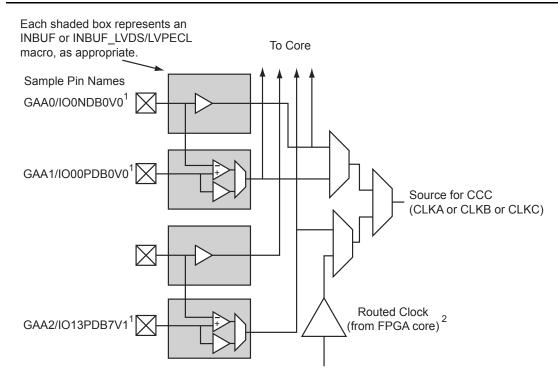

Example: For a bus consisting of 20 equidistant loads, the terminations given in EQ 1 provide the required differential voltage, in worst-case industrial operating conditions, at the farthest receiver:

$$R_S$$

= 60  $\Omega,\,R_T$  = 70  $\Omega,\,$  given  $Z_O$  = 50  $\Omega$  (2") and  $Z_{stub}$  = 50  $\Omega$  (~1.5").

EQ 1

Figure 7-8 • A B-LVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

I/O Structures in IGLOOe and ProASIC3E Devices

## I/O Banks and I/O Standards Compatibility

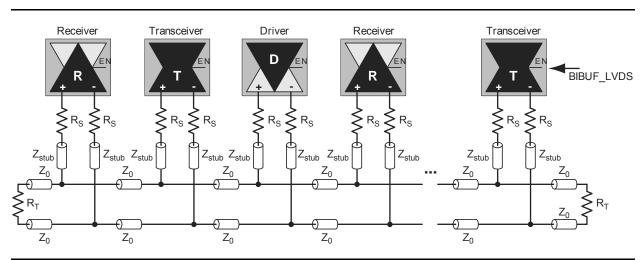

I/Os are grouped into I/O voltage banks.

Each I/O voltage bank has dedicated I/O supply and ground voltages (VMV/GNDQ for input buffers and  $V_{CCI}$ /GND for output buffers). Because of these dedicated supplies, only I/Os with compatible standards can be assigned to the same I/O voltage bank. Table 8-3 on page 217 shows the required voltage compatibility values for each of these voltages.

There are eight I/O banks (two per side).

Every I/O bank is divided into minibanks. Any user I/O in a VREF minibank (a minibank is the region of scope of a VREF pin) can be configured as a VREF pin (Figure 8-2). Only one  $V_{REF}$  pin is needed to control the entire  $V_{REF}$  minibank. The location and scope of the  $V_{REF}$  minibanks can be determined by the I/O name. For details, see the user I/O naming conventions for "IGLOOe and ProASIC3E" on page 245. Table 8-5 on page 217 shows the I/O standards supported by IGLOOe and ProASIC3E devices, and the corresponding voltage levels.

I/O standards are compatible if they comply with the following:

- Their VCCI and VMV values are identical.

- Both of the standards need a VREF, and their VREF values are identical.

- All inputs and disabled outputs are voltage tolerant up to 3.3 V.

For more information about I/O and global assignments to I/O banks in a device, refer to the specific pin table for the device in the packaging section of the datasheet, and see the user I/O naming conventions for "IGLOOe and ProASIC3E" on page 245.

Figure 8-2 • Typical IGLOOe and ProASIC3E I/O Bank Detail Showing VREF Minibanks

## I/O Register Combining

Every I/O has several embedded registers in the I/O tile that are close to the I/O pads. Rather than using the internal register from the core, the user has the option of using these registers for faster clock-to-out timing, and external hold and setup. When combining these registers at the I/O buffer, some architectural rules must be met. Provided these rules are met, the user can enable register combining globally during Compile (as shown in the "Compiling the Design" section on page 261).

This feature is supported by all I/O standards.

### Rules for Registered I/O Function

- 1. The fanout between an I/O pin (D, Y, or E) and a register must be equal to one for combining to be considered on that pin.

- 2. All registers (Input, Output, and Output Enable) connected to an I/O must share the same clear or preset function:

- If one of the registers has a CLR pin, all the other registers that are candidates for combining in the I/O must have a CLR pin.

- If one of the registers has a PRE pin, all the other registers that are candidates for combining in the I/O must have a PRE pin.

- If one of the registers has neither a CLR nor a PRE pin, all the other registers that are candidates for combining must have neither a CLR nor a PRE pin.

- If the clear or preset pins are present, they must have the same polarity.

- If the clear or preset pins are present, they must be driven by the same signal (net).

- 3. Registers connected to an I/O on the Output and Output Enable pins must have the same clock and enable function:

- Both the Output and Output Enable registers must have an E pin (clock enable), or none at all.

- If the E pins are present, they must have the same polarity. The CLK pins must also have the same polarity.

In some cases, the user may want registers to be combined with the input of a bibuf while maintaining the output as-is. This can be achieved by using PDC commands as follows:

```

set_io <signal name> -REGISTER yes -----register will combine

set_preserve <signal name> ----register will not combine

```

## Weak Pull-Up and Weak Pull-Down Resistors

When the I/O is pulled up, it is connected to the VCCI of its corresponding I/O bank. When it is pulled down, it is connected to GND. Refer to the datasheet for more information.

For low power applications, configuration of the pull-up or pull-down of the I/O can be used to set the I/O to a known state while the device is in Flash\*Freeze mode. Refer to the "Flash\*Freeze Technology and Low Power Modes in IGLOO and ProASIC3L Devices" chapter in the *IGLOOe FPGA Fabric User's Guide* or *ProASIC3E FPGA Fabric User's Guide* for more information.

The Flash\*Freeze (FF) pin cannot be configured with a weak pull-down or pull-up I/O attribute, as the signal needs to be driven at all times.

### **Output Slew Rate Control**

The slew rate is the amount of time an input signal takes to get from logic LOW to logic HIGH or vice versa.

It is commonly defined as the propagation delay between 10% and 90% of the signal's voltage swing. Slew rate control is available for the output buffers of low power flash devices. The output buffer has a programmable slew rate for both HIGH-to-LOW and LOW-to-HIGH transitions. Slew rate control is available for LVTTL, LVCMOS, and PCI-X I/O standards. The other I/O standards have a preset slew value.

The slew rate can be implemented by using a PDC command (Table 8-6 on page 218), setting it "High" or "Low" in the I/O Attribute Editor in Designer, or instantiating a special I/O macro. The default slew rate value is "High."

The procedure is as follows:

- 1. Select the bank to which you want VCCI to be assigned from the **Choose Bank** list.

- 2. Select the I/O standards for that bank. If you select any standard, the tool will automatically show all compatible standards that have a common VCCI voltage requirement.

- 3. Click Apply.

- 4. Repeat steps 1–3 to assign VCCI voltages to other banks. Refer to Figure 9-11 on page 263 to find out how many I/O banks are needed for VCCI bank assignment.

### Manually Assigning VREF Pins

Voltage-referenced inputs require an input reference voltage (VREF). The user must assign VREF pins before running Layout. Before assigning a VREF pin, the user must set a VREF technology for the bank to which the pin belongs.

# VREF Rules for the Implementation of Voltage-Referenced I/O Standards

The VREF rules are as follows:

- 1. Any I/O (except JTAG I/Os) can be used as a V<sub>REF</sub> pin.

- One V<sub>REF</sub> pin can support up to 15 I/Os. It is recommended, but not required, that eight of them be on one side and seven on the other side (in other words, all 15 can still be on one side of VREF).

- 3. SSTL3 (I) and (II): Up to 40 I/Os per north or south bank in any position

- 4. LVPECL / GTL+ 3.3 V / GTL 3.3 V: Up to 48 I/Os per north or south bank in any position (not applicable for IGLOO nano and ProASIC3 nano devices)

- 5. SSTL2 (I) and (II) / GTL + 2.5 V / GTL 2.5 V: Up to 72 I/Os per north or south bank in any position

- 6. VREF minibanks partition rule: Each I/O bank is physically partitioned into VREF minibanks. The VREF pins within a VREF minibank are interconnected internally, and consequently, only one VREF voltage can be used within each VREF minibank. If a bank does not require a VREF signal, the VREF pins of that bank are available as user I/Os.

- The first VREF minibank includes all I/Os starting from one end of the bank to the first power triple and eight more I/Os after the power triple. Therefore, the first VREF minibank may contain (0 + 8), (2 + 8), (4 + 8), (6 + 8), or (8 + 8) I/Os.

The second VREF minibank is adjacent to the first VREF minibank and contains eight I/Os, a power triple, and eight more I/Os after the triple. An analogous rule applies to all other VREF minibanks but the last.

The last VREF minibank is adjacent to the previous one but contains eight I/Os, a power triple, and all I/Os left at the end of the bank. This bank may also contain (8 + 0), (8 + 2), (8 + 4), (8 + 6), or (8 + 8) available I/Os.

### Example:

4 l/Os  $\rightarrow$  Triple  $\rightarrow$  8 l/Os, 8 l/Os  $\rightarrow$  Triple  $\rightarrow$  8 l/Os, 8 l/Os  $\rightarrow$  Triple  $\rightarrow$  2 l/Os

That is, minibank A = (4 + 8) I/Os, minibank B = (8 + 8) I/Os, minibank C = (8 + 2) I/Os.

Only minibanks that contain input or bidirectional I/Os require a VREF. A VREF is not needed for minibanks composed of output or tristated I/Os.

### Assigning the VREF Voltage to a Bank

When importing the PDC file, the VREF voltage can be assigned to the I/O bank. The PDC command is as follows:

set\_iobank -vref [value]

Another method for assigning VREF is by using MVN > Edit > I/O Bank Settings (Figure 9-13 on page 266).

DDR for Microsemi's Low Power Flash Devices

# **Design Example**

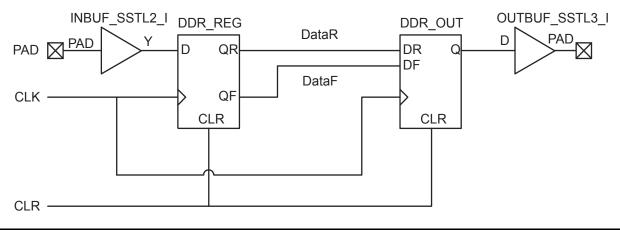

Figure 10-9 shows a simple example of a design using both DDR input and DDR output registers. The user can copy the HDL code in Libero SoC software and go through the design flow. Figure 10-10 and Figure 10-11 on page 283 show the netlist and ChipPlanner views of the ddr\_test design. Diagrams may vary slightly for different families.

Figure 10-9 • Design Example

Figure 10-10 • DDR Test Design as Seen by NetlistViewer for IGLOO/e Devices

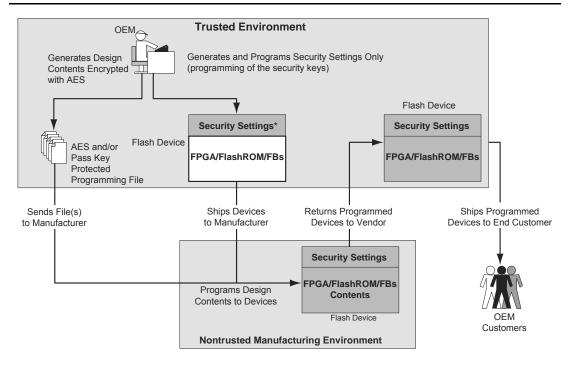

## Application 1: Trusted Environment

As illustrated in Figure 12-7, this application allows the programming of devices at design locations where research and development take place. Therefore, encryption is not necessary and is optional to the user. This is often a secure way to protect the design, since the design program files are not sent elsewhere. In situations where production programming is not available at the design location, programming centers (such as Microsemi In-House Programming) provide a way of programming designs at an alternative, secure, and trusted location. In this scenario, the user generates a STAPL programming file from the Designer software in plaintext format, containing information on the entire design or the portion of the design. Once the design is programmed to unprogrammed devices, the design is protected by this FlashLock Pass Key. If no future programming is needed, the user can consider permanently securing the IGLOO and ProASIC3 device, as discussed in the "Permanent FlashLock" section on page 307.

## **Application 2: Nontrusted Environment—Unsecured Location**

Often, programming of devices is not performed in the same location as actual design implementation, to reduce manufacturing cost. Overseas programming centers and contract manufacturers are examples of this scenario.

To achieve security in this case, the AES key and the FlashLock Pass Key can be initially programmed in-house (trusted environment). This is done by generating a programming file with only the security settings and no design contents. The design FPGA core, FlashROM, and (for Fusion) FB contents are generated in a separate programming file. This programming file must be set with the same AES key that was used to program to the device previously so the device will correctly decrypt this encrypted programming file. As a result, the encrypted design content programming file can be safely sent off-site to nontrusted programming locations for design programming. Figure 12-7 shows a more detailed flow for this application.

Notes:

1. Programmed portion indicated with dark gray.

2. Programming of FBs applies to Fusion only.

Figure 12-7 • Application 2: Device Programming in a Nontrusted Environment

# List of Changes

| Date        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| August 2012 | This chapter will now be published standalone as an application note in addition to being part of the IGLOO/ProASIC3/Fusion FPGA fabric user's guides (SAR 38769).                                                                                                                                                                                                                                                                          | N/A      |

|             | The "ISP Programming Header Information" section was revised to update the description of FP3-10PIN-ADAPTER-KIT in Table 13-3 • Programming Header Ordering Codes, clarifying that it is the adapter kit used for ProASIC <sup>PLUS</sup> based boards, and also for ProASIC3 based boards where a compact programming header is being used (SAR 36779).                                                                                    | 335      |

| June 2011   | The VPUMP programming mode voltage was corrected in Table 13-2 • Power Supplies. The correct value is 3.15 V to 3.45 V (SAR 30668).                                                                                                                                                                                                                                                                                                         | 329      |

|             | The notes associated with Figure 13-5 • Programming Header (top view) and Figure 13-6 • Board Layout and Programming Header Top View were revised to make clear the fact that IGLOO nano V2 devices can be programmed at 1.2 V (SAR 30787).                                                                                                                                                                                                 | 335, 337 |

|             | Figure 13-6 • Board Layout and Programming Header Top View was revised to include resistors tying TCK and TRST to GND. Microsemi recommends tying off TCK and TRST to GND if JTAG is not used (SAR 22921). RT ProASIC3 was added to the list of device families.                                                                                                                                                                            | 337      |

|             | In the "ISP Programming Header Information" section, the kit for adapting ProASIC <sup>PLUS</sup> devices was changed from FP3-10PIN-ADAPTER-KIT to FP3-26PIN-ADAPTER-KIT (SAR 20878).                                                                                                                                                                                                                                                      | 335      |

| July 2010   | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                                                                                                                                   | N/A      |

|             | References to FlashPro4 and FlashPro3X were added to this chapter, giving distinctions between them. References to SmartGen were deleted and replaced with Libero IDE Catalog.                                                                                                                                                                                                                                                              | N/A      |

|             | The "ISP Architecture" section was revised to indicate that V2 devices can be programmed at 1.2 V VCC with FlashPro4.                                                                                                                                                                                                                                                                                                                       | 327      |

|             | SmartFusion was added to Table 13-1 • Flash-Based FPGAs Supporting ISP.                                                                                                                                                                                                                                                                                                                                                                     | 328      |

|             | The "Programming Voltage (VPUMP) and VJTAG" section was revised and 1.2 V was added to Table 13-2 • Power Supplies.                                                                                                                                                                                                                                                                                                                         | 329      |

|             | The "Nonvolatile Memory (NVM) Programming Voltage" section is new.                                                                                                                                                                                                                                                                                                                                                                          | 329      |

|             | Cortex-M3 was added to the "Cortex-M1 and Cortex-M3 Device Security" section.                                                                                                                                                                                                                                                                                                                                                               | 331      |

|             | In the "ISP Programming Header Information" section, the additional header adapter ordering number was changed from FP3-26PIN-ADAPTER to FP3-10PIN-ADAPTER-KIT, which contains 26-pin migration capability.                                                                                                                                                                                                                                 | 335      |

|             | The description of NC was updated in Figure 13-5 • Programming Header (top view), Table 13-4 • Programming Header Pin Numbers and Description and Figure 13-6 • Board Layout and Programming Header Top View.                                                                                                                                                                                                                               | 335, 336 |

|             | The "Symptoms of a Signal Integrity Problem" section was revised to add that customers are expected to troubleshoot board-level signal integrity issues by measuring voltages and taking scope plots. "FlashPro4/3/3X allows TCK to be lowered from 6 MHz down to 1 MHz to allow you to address some signal integrity problems" formerly read, "from 24 MHz down to 1 MHz." "The Scan Chain command expects to see 0x2" was changed to 0x1. | 337      |

The following table lists critical changes that were made in each revision of the chapter.

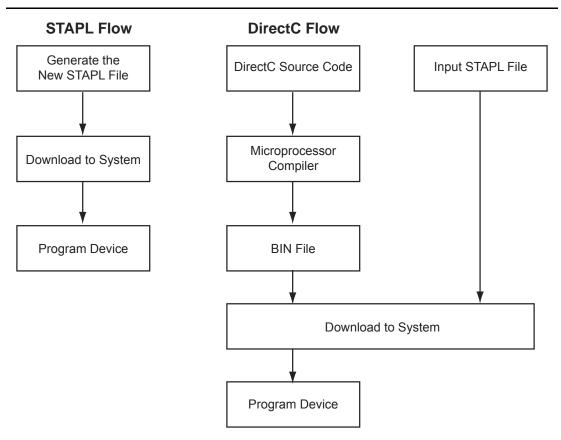

## STAPL vs. DirectC

Programming the low power flash devices is performed using DirectC or the STAPL player. Both tools use the STAPL file as an input. DirectC is a compiled language, whereas STAPL is an interpreted language. Microprocessors will be able to load the FPGA using DirectC much more quickly than STAPL. This speed advantage becomes more apparent when lower clock speeds of 8- or 16-bit microprocessors are used. DirectC also requires less memory than STAPL, since the programming algorithm is directly implemented. STAPL does have one advantage over DirectC—the ability to upgrade. When a new programming algorithm is required, the STAPL user simply needs to regenerate a STAPL file using the latest version of the Designer software and download it to the system. The DirectC user must download the latest version of DirectC from Microsemi, compile everything, and download the result into the system (Figure 15-4).

Figure 15-4 • STAPL vs. DirectC

# **Boundary Scan Support in Low Power Devices**

The information in this document applies to all Fusion, IGLOO, and ProASIC3 devices. For IGLOO, IGLOO PLUS, and ProASIC3L devices, the Flash\*Freeze pin must be deasserted for successful boundary scan operations. Devices cannot enter JTAG mode directly from Flash\*Freeze mode.

## **Boundary Scan Opcodes**

Low power flash devices support all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD, and BYPASS) and the optional IDCODE instruction (Table 16-2).

### Table 16-2 • Boundary Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| HIGHZ          | 07         |

| USERCODE       | 0E         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | 0F         |

| CLAMP          | 05         |

| BYPASS         | FF         |

## **Boundary Scan Chain**

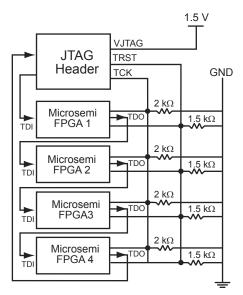

The serial pins are used to serially connect all the boundary scan register cells in a device into a boundary scan register chain (Figure 16-2 on page 360), which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic I/O tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Each test section is accessed through the TAP, which has five associated pins: TCK (test clock input), TDI, TDO (test data input and output), TMS (test mode selector), and TRST (test reset input). TMS, TDI, and TRST are equipped with pull-up resistors to ensure proper operation when no input data is supplied to them. These pins are dedicated for boundary scan test usage. Refer to the "JTAG Pins" section in the "Pin Descriptions and Packaging" chapter of the appropriate device datasheet for pull-up/-down recommendations for TCK and TRST pins. Pull-down recommendations are also given in Table 16-3 on page 360

Note: TCK is correctly wired with an equivalent tie-off resistance of  $500 \Omega$ , which satisfies the table for VJTAG of 1.5 V. The resistor values for TRST are not appropriate in this case, as the tie-off resistance of  $375 \Omega$  is below the recommended minimum for VJTAG = 1.5 V, but would be appropriate for a VJTAG setting of 2.5 V or 3.3 V.

### Figure 16-3 • Parallel Resistance on JTAG Chain of Devices

## **Advanced Boundary Scan Register Settings**

You will not be able to control the order in which I/Os are released from boundary scan control. Testing has produced cases where, depending on I/O placement and FPGA routing, a 5 ns glitch has been seen on exiting programming mode. The following setting is recommended to prevent such I/O glitches:

- 1. In the FlashPro software, configure the advanced BSR settings for **Specify I/O Settings During Programming**.

- 2. Set the input BSR cell to **Low** for the input I/O.

Index

FlashLock IGLOO and ProASIC devices 307 permanent 307 FlashROM access using JTAG port 139 architecture 333 architecture of user nonvolatile 133 configuration 136 custom serialization 145 design flow 140 generation 141 programming and accessing 138 programming file 143 programming files 333 SmartGen 142 FlashROM read-back 371

### G

global architecture 47 global buffers no programmable delays 80 with PLL function 83 with programmable delays 80 global macros Synplicity 66 globals designer flow 69 networks 74 spines and rows 57

### Η

HLD code instantiating 258 hot-swapping 383

### Ι

I/O banks standards 56 I/O standards 93 global macros 62 I/Os assigning technologies 264 assignments defined in PDC file 259 automatically assigning 268 behavior at power-up/-down 377 buffer schematic cell 257 cell architecture 273 configuration with SmartGen 254 global, naming 51 manually assigning technologies 264 software-controlled attributes 253 user I/O assignment flow chart 251 idle mode 23 INBUF\_FF 39 ISP 289, 290 architecture 327 board-level considerations 337

circuit 343 microprocessor 349

### J

JTAG 1532 327 JTAG interface 351

### L

layout device-specific 94 LTC3025 linear voltage regulator 343

### М

MAC validation/authentication 354 macros CLKBUF 93 CLKBUF\_LVDS/LVPECL 93 CLKDLY 81, 89 FIFO4KX18 157 **PLL 89** PLL macro signal descriptions 84 RAM4K9 153 RAM512X18 155 supported basic RAM macros 152 UJTAG 365 **ULSICC 40** MCU FPGA programming model 352 memory availability 162 memory blocks 151 microprocessor programming 349 Microsemi SoC Products Group email 387 web-based technical support 387 website 387

## 0

OTP 289

### Ρ

PDC global promotion and demotion 67 place-and-route 259 PLL behavior at brownout condition 381 configuration bits 106 core specifications 100 dynamic PLL configuration 103 functional description 101 power supply decoupling scheme 128 PLL block signals 84 PLL macro block diagram 85 power conservation 41 power modes Flash\*Freeze 24 idle 23 shutdown 32