Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                             |

| Number of Logic Elements/Cells | -                                                                             |

| Total RAM Bits                 | 516096                                                                        |

| Number of I/O                  | 341                                                                           |

| Number of Gates                | 300000                                                                        |

| Voltage - Supply               | 1.14V ~ 1.575V                                                                |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                            |

| Package / Case                 | 484-BGA                                                                       |

| Supplier Device Package        | 484-FPBGA (23x23)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe3000l-fgg484i |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Using Sleep and Shutdown Modes in the System

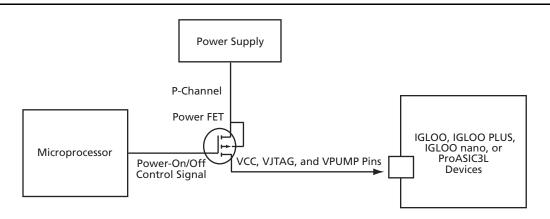

Depending on the power supply and the components used in an application, there are many ways to power on or off the power supplies connected to the device. For example, Figure 2-6 shows how a microprocessor can be used to control a power FET. Microsemi recommends that power FETs with low resistance be used to perform the switching action.

Figure 2-6 • Controlling Power-On/-Off State Using Microprocessor and Power FET

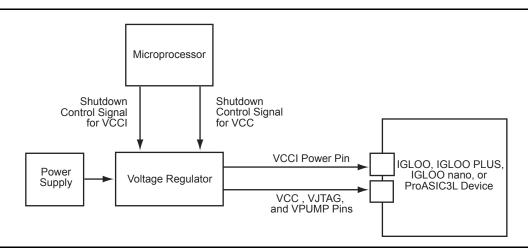

Figure 2-7 shows how a microprocessor can be used with a voltage regulator's shutdown pin to turn on or off the power supplies connected to the device.

Figure 2-7 • Controlling Power-On/-Off State Using Microprocessor and Voltage Regulator

## Power-Up/-Down Behavior

By design, all IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3L, and RT ProASIC3 I/Os are in tristate mode before device power-up. The I/Os remain tristated until the last voltage supply ( $V_{CC}$  or  $V_{CCI}$ ) is powered to its activation level. After the last supply reaches its functional level, the outputs exit the tristate mode and drive the logic at the input of the output buffer. The behavior of user I/Os is independent of the  $V_{CC}$  and  $V_{CCI}$  sequence or the state of other voltage supplies of the FPGA ( $V_{PUMP}$  and  $V_{JTAG}$ ). During power-down, device I/Os become tristated once the first power supply ( $V_{CC}$  or  $V_{CCI}$ ) drops below its deactivation voltage level. The I/O behavior during power-down is also independent of voltage supply sequencing.

Figure 2-8 on page 34 shows a timing diagram when the V<sub>CC</sub> power supply crosses the activation and deactivation trip points in a typical application when the V<sub>CC</sub> power supply ramp-rate is 100  $\mu$ s (ramping from 0 V to 1.5 V in this example). This is the timing diagram for the FPGA entering and exiting Sleep mode, as this function is dependent on powering V<sub>CC</sub> down or up. Depending on the ramp-rate of the

## **CCC Support in Microsemi's Flash Devices**

The flash FPGAs listed in Table 4-1 support the CCC feature and the functions described in this document.

| Series   | Family <sup>*</sup>  | Description                                                                                                                                                                       |

|----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                 |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                             |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                        |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                               |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                           |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                          |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                               |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                             |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                       |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                             |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                              |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex™-M1 soft processors, and flash memory into a monolithic device |

#### Table 4-1 • Flash-Based FPGAs

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

| Config.<br>Bits | Signal              | Name                             | Description                                                                                                                                              |  |

|-----------------|---------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 83              | RXCSEL <sup>1</sup> | CLKC input selection             | Select the CLKC input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 110). <sup>2</sup>                          |  |

| 82              | RXBSEL <sup>1</sup> | CLKB input selection             | Select the CLKB input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 110). <sup>2</sup>                          |  |

| 81              | RXASEL <sup>1</sup> | CLKA input selection             | Select the CLKA input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 110). <sup>2</sup>                          |  |

| 80              | RESETEN             | Reset Enable                     | Enables (active high) the synchronization of<br>PLL output dividers after dynamic<br>reconfiguration (SUPDATE). The Reset<br>Enable signal is READ-ONLY. |  |

| 79              | DYNCSEL             | Clock Input C Dynamic<br>Select  | Configures clock input C to be sent to GLC for dynamic control. <sup>2</sup>                                                                             |  |

| 78              | DYNBSEL             | Clock Input B Dynamic<br>Select  | Configures clock input B to be sent to GLB for dynamic control. <sup>2</sup>                                                                             |  |

| 77              | DYNASEL             | Clock Input A Dynamic<br>Select  | Configures clock input A for dynamic PLL configuration. <sup>2</sup>                                                                                     |  |

| <76:74>         | VCOSEL[2:0]         | VCO Gear Control                 | Three-bit VCO Gear Control for four frequer<br>ranges (refer to Table 4-19 on page 111 an<br>Table 4-20 on page 111).                                    |  |

| 73              | STATCSEL            | MUX Select on Input C            | MUX selection for clock input C <sup>2</sup>                                                                                                             |  |

| 72              | STATBSEL            | MUX Select on Input B            | MUX selection for clock input B <sup>2</sup>                                                                                                             |  |

| 71              | STATASEL            | MUX Select on Input A            | MUX selection for clock input A <sup>2</sup>                                                                                                             |  |

| <70:66>         | DLYC[4:0]           | YC Output Delay                  | Sets the output delay value for YC.                                                                                                                      |  |

| <65:61>         | DLYB[4:0]           | YB Output Delay                  | Sets the output delay value for YB.                                                                                                                      |  |

| <60:56>         | DLYGLC[4:0]         | GLC Output Delay                 | Sets the output delay value for GLC.                                                                                                                     |  |

| <55:51>         | DLYGLB[4:0]         | GLB Output Delay                 | Sets the output delay value for GLB.                                                                                                                     |  |

| <50:46>         | DLYGLA[4:0]         | Primary Output Delay             | Primary GLA output delay                                                                                                                                 |  |

| 45              | XDLYSEL             | System Delay Select              | When selected, inserts System Delay in the feedback path in Figure 4-20 on page 101.                                                                     |  |

| <44:40>         | FBDLY[4:0]          | Feedback Delay                   | Sets the feedback delay value for the feedback element in Figure 4-20 on page 101.                                                                       |  |

| <39:38>         | FBSEL[1:0]          | Primary Feedback Delay<br>Select | Controls the feedback MUX: no delay, include programmable delay element, or use external feedback.                                                       |  |

| <37:35>         | OCMUX[2:0]          | Secondary 2 Output<br>Select     | Selects from the VCO's four phase outputs for GLC/YC.                                                                                                    |  |

| <34:32>         | OBMUX[2:0]          | Secondary 1 Output<br>Select     | Selects from the VCO's four phase outputs for GLB/YB.                                                                                                    |  |

#### Table 4-8 • Configuration Bit Descriptions for the CCC Blocks (continued)

Notes:

1. The <88:81> configuration bits are only for the Fusion dynamic CCC.

This value depends on the input clock source, so Layout must complete before these bits can be set. After completing Layout in Designer, generate the "CCC\_Configuration" report by choosing Tools > Report > CCC\_Configuration. The report contains the appropriate settings for these bits.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

#### **External Feedback Configuration**

For certain applications, such as those requiring generation of PCB clocks that must be matched with existing board delays, it is useful to implement an external feedback, EXTFB. The Phase Detector of the PLL core will receive CLKA and EXTFB as inputs. EXTFB may be processed by the fixed System Delay element as well as the *M* divider element. The EXTFB option is currently not supported.

After setting all the required parameters, users can generate one or more PLL configurations with HDL or EDIF descriptions by clicking the **Generate** button. SmartGen gives the option of saving session results and messages in a log file:

| Name                                          | : test_pll            |

|-----------------------------------------------|-----------------------|

| Family                                        | : ProASIC3E           |

| Output Format                                 | : VHDL                |

| Type                                          | : Static PLL          |

| Input Freq(MHz)                               | : 10.000              |

| CLKA Source                                   | : Hardwired I/O       |

| Feedback Delay Value Index                    | : 1                   |

| Feedback Mux Select                           | : 2                   |

| XDLY Mux Select                               | -<br>: No             |

| Primary Freq(MHz)                             | : 33.000              |

| Primary PhaseShift                            | : 0                   |

| Primary Delay Value Index                     | : 1                   |

| Primary Mux Select                            | : 4                   |

| Secondary1 Freq(MHz)                          | : 66.000              |

| Use GLB                                       | : YES                 |

| Use YB                                        | : YES                 |

| GLB Delay Value Index                         | : 1                   |

| YB Delay Value Index                          | · 1                   |

| Secondaryl PhaseShift                         | : 0                   |

| Secondary1 Mux Select                         | : 4                   |

| Secondary1 Mux Select<br>Secondary2 Freq(MHz) | : 101.000             |

| Use GLC                                       | : YES                 |

| Use YC                                        | : NO                  |

| GLC Delay Value Index                         | : NO<br>: 1           |

| YC Delay Value Index                          | · 1                   |

| _                                             | : 0                   |

| Secondary2 PhaseShift                         | : 4                   |

| Secondary2 Mux Select                         | • 4                   |

|                                               |                       |

|                                               |                       |

|                                               |                       |

|                                               |                       |

|                                               |                       |

| Primary Clock frequency 33.333                |                       |

| Primary Clock Phase Shift 0.000               |                       |

| Primary Clock Output Delay from               | n CLKA U.180          |

|                                               |                       |

| Secondaryl Clock frequency 66.6               |                       |

| Secondaryl Clock Phase Shift 0.               |                       |

| Secondaryl Clock Global Output                |                       |

| Secondaryl Clock Core Output De               | elay from CLKA 0.625  |

|                                               | 000                   |

| Secondary2 Clock frequency 100.               |                       |

| Secondary2 Clock Phase Shift 0.               |                       |

| Secondary2 Clock Global Output                | Delay from CLKA 0.180 |

|                                               |                       |

Below is an example Verilog HDL description of a legal PLL core configuration generated by SmartGen:

module test\_pll(POWERDOWN,CLKA,LOCK,GLA); input POWERDOWN, CLKA; output LOCK,GLA;

## **SRAM Features**

### RAM4K9 Macro

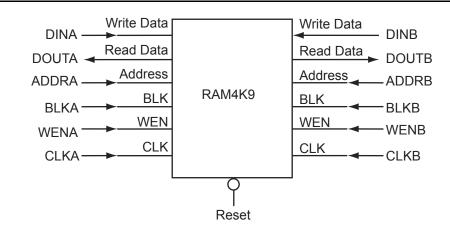

RAM4K9 is the dual-port configuration of the RAM block (Figure 6-4). The RAM4K9 nomenclature refers to both the deepest possible configuration and the widest possible configuration the dual-port RAM block can assume, and does not denote a possible memory aspect ratio. The RAM block can be configured to the following aspect ratios: 4,096×1, 2,048×2, 1,024×4, and 512×9. RAM4K9 is fully synchronous and has the following features:

- Two ports that allow fully independent reads and writes at different frequencies

- Selectable pipelined or nonpipelined read

- Active-low block enables for each port

- Toggle control between read and write mode for each port

- · Active-low asynchronous reset

- Pass-through write data or hold existing data on output. In pass-through mode, the data written to the write port will immediately appear on the read port.

- Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

*Note:* For timing diagrams of the RAM signals, refer to the appropriate family datasheet. *Figure 6-4* • RAM4K9 Simplified Configuration

### Signal Descriptions for RAM4K9

Note: Automotive ProASIC3 devices support single-port SRAM capabilities, or dual-port SRAM only under specific conditions. Dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). Since Libero SoC macro libraries support a dual-port macro only, certain modifications must be made. These are detailed below.

The following signals are used to configure the RAM4K9 memory element:

#### WIDTHA and WIDTHB

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 6-2 on page 154).

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WIDTHB should be tied to ground.

256×18 FIFO is full, even though a 128×18 FIFO was requested. For this example, the Almost-Full flag can be used instead of the Full flag to signal when the 128th data word is reached.

To accommodate different aspect ratios, the almost-full and almost-empty values are expressed in terms of data bits instead of data words. SmartGen translates the user's input, expressed in data words, into data bits internally. SmartGen allows the user to select the thresholds for the Almost-Empty and Almost-Full flags in terms of either the read data words or the write data words, and makes the appropriate conversions for each flag.

After the empty or full states are reached, the FIFO can be configured so the FIFO counters either stop or continue counting. For timing numbers, refer to the appropriate family datasheet.

### Signal Descriptions for FIFO4K18

The following signals are used to configure the FIFO4K18 memory element:

#### WW and RW

These signals enable the FIFO to be configured in one of the five allowable aspect ratios (Table 6-6).

| WW[2:0]       | RW[2:0]       | D×W      |

|---------------|---------------|----------|

| 000           | 000           | 4k×1     |

| 001           | 001           | 2k×2     |

| 010           | 010           | 1k×4     |

| 011           | 011           | 512×9    |

| 100           | 100           | 256×18   |

| 101, 110, 111 | 101, 110, 111 | Reserved |

#### Table 6-6 • Aspect Ratio Settings for WW[2:0]

#### WBLK and RBLK

These signals are active-low and will enable the respective ports when LOW. When the RBLK signal is HIGH, that port's outputs hold the previous value.

#### WEN and REN

Read and write enables. WEN is active-low and REN is active-high by default. These signals can be configured as active-high or -low.

#### WCLK and RCLK

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

# Note: For the Automotive ProASIC3 FIFO4K18, for the same clock, 180° out of phase (inverted) between clock pins should be used.

#### RPIPE

This signal is used to specify pipelined read on the output. A LOW on RPIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the output in the next clock cycle.

#### RESET

This active-low signal resets the control logic and forces the output hold state registers to zero when asserted. It does not reset the contents of the memory array (Table 6-7 on page 160).

While the RESET signal is active, read and write operations are disabled. As with any asynchronous RESET signal, care must be taken not to assert it too close to the edges of active read and write clocks.

#### WD

This is the input data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. When a data width less than 18 is specified, unused higher-order signals must be grounded (Table 6-7 on page 160).

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

RD

This is the output data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. Like the WD bus, high-order bits become unusable if the data width is less than 18. The output data on unused pins is undefined (Table 6-7).

| D×W    | WD/RD Unused       |

|--------|--------------------|

| 4k×1   | WD[17:1], RD[17:1] |

| 2k×2   | WD[17:2], RD[17:2] |

| 1k×4   | WD[17:4], RD[17:4] |

| 512×9  | WD[17:9], RD[17:9] |

| 256×18 | -                  |

### ESTOP, FSTOP

ESTOP is used to stop the FIFO read counter from further counting once the FIFO is empty (i.e., the EMPTY flag goes HIGH). A HIGH on this signal inhibits the counting.

FSTOP is used to stop the FIFO write counter from further counting once the FIFO is full (i.e., the FULL flag goes HIGH). A HIGH on this signal inhibits the counting.

For more information on these signals, refer to the "ESTOP and FSTOP Usage" section.

#### FULL, EMPTY

When the FIFO is full and no more data can be written, the FULL flag asserts HIGH. The FULL flag is synchronous to WCLK to inhibit writing immediately upon detection of a full condition and to prevent overflows. Since the write address is compared to a resynchronized (and thus time-delayed) version of the read address, the FULL flag will remain asserted until two WCLK active edges after a read operation eliminates the full condition.

When the FIFO is empty and no more data can be read, the EMPTY flag asserts HIGH. The EMPTY flag is synchronous to RCLK to inhibit reading immediately upon detection of an empty condition and to prevent underflows. Since the read address is compared to a resynchronized (and thus time-delayed) version of the write address, the EMPTY flag will remain asserted until two RCLK active edges after a write operation removes the empty condition.

For more information on these signals, refer to the "FIFO Flag Usage Considerations" section on page 161.

#### AFULL, AEMPTY

These are programmable flags and will be asserted on the threshold specified by AFVAL and AEVAL, respectively.

When the number of words stored in the FIFO reaches the amount specified by AEVAL while reading, the AEMPTY output will go HIGH. Likewise, when the number of words stored in the FIFO reaches the amount specified by AFVAL while writing, the AFULL output will go HIGH.

#### AFVAL, AEVAL

The AEVAL and AFVAL pins are used to specify the almost-empty and almost-full threshold values. They are 12-bit signals. For more information on these signals, refer to the "FIFO Flag Usage Considerations" section on page 161.

### FIFO Usage

#### ESTOP and FSTOP Usage

The ESTOP pin is used to stop the read counter from counting any further once the FIFO is empty (i.e., the EMPTY flag goes HIGH). Likewise, the FSTOP pin is used to stop the write counter from counting any further once the FIFO is full (i.e., the FULL flag goes HIGH).

The FIFO counters in the device start the count at zero, reach the maximum depth for the configuration (e.g., 511 for a 512×9 configuration), and then restart at zero. An example application for ESTOP, where the read counter keeps counting, would be writing to the FIFO once and reading the same content over and over without doing another write.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

```

//

addr_counter counter_1 (.Clock(data_update), .Q(wr_addr), .Aset(rst_n),

.Enable(enable));

addr_counter counter_2 (.Clock(test_clk), .Q(rd_addr), .Aset(rst_n),

.Enable( test_active));

```

endmodule

### Interface Block / UJTAG Wrapper

This example is a sample wrapper, which connects the interface block to the UJTAG and the memory blocks.

```

// WRAPPER

module top_init (TDI, TRSTB, TMS, TCK, TDO, test, test_clk, test_ out);

input TDI, TRSTB, TMS, TCK;

output TDO;

input test, test_clk;

output [3:0] test_out;

wire [7:0] IR;

wire reset, DR_shift, DR_cap, init_clk, DR_update, data_in, data_out;

wire clk out, wen, ren;

wire [3:0] word_in, word_out;

wire [1:0] write_addr, read_addr;

UJTAG UJTAG_U1 (.UIREG0(IR[0]), .UIREG1(IR[1]), .UIREG2(IR[2]), .UIREG3(IR[3]),

.UIREG4(IR[4]), .UIREG5(IR[5]), .UIREG6(IR[6]), .UIREG7(IR[7]), .URSTB(reset),

.UDRSH(DR_shift), .UDRCAP(DR_cap), .UDRCK(init_clk), .UDRUPD(DR_update),

.UT-DI(data_in), .TDI(TDI), .TMS(TMS), .TCK(TCK), .TRSTB(TRSTB), .TDO(TDO),

.UT-DO(data_out));

mem_block RAM_block (.DO(word_out), .RCLOCK(clk_out), .WCLOCK(clk_out), .DI(word_in),

.WRB(wen), .RDB(ren), .WAD-DR(write_addr), .RADDR(read_addr));

interface init_block (.IR(IR), .rst_n(reset), .data_shift(DR_shift), .clk_in(init_clk),

.data_update(DR_update), .din_ser(data_in), .dout_ser(data_out), .test(test),

.test_out(test_out), .test_clk(test_clk), .clk_out(clk_out), .wr_en(wen),

.rd_en(ren), .write_word(word_in), .read_word(word_out), .rd_addr(read_addr),

.wr_addr(write_addr));

```

endmodule

### Address Counter

module addr\_counter (Clock, Q, Aset, Enable);

```

input Clock;

output [1:0] Q;

input Aset;

input Enable;

reg [1:0] Qaux;

always @(posedge Clock or negedge Aset)

begin

if (!Aset) Qaux <= 2'b11;

else if (Enable) Qaux <= Qaux + 1;

end

assign Q = Qaux;

endmodule

```

## I/O Standards

## **Single-Ended Standards**

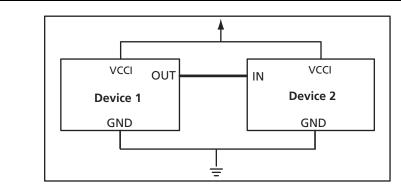

These I/O standards use a push-pull CMOS output stage with a voltage referenced to system ground to designate logical states. The input buffer configuration, output drive, and I/O supply voltage (VCCI) vary among the I/O standards (Figure 7-5).

#### *Figure 7-5* • Single-Ended I/O Standard Topology

The advantage of these standards is that a common ground can be used for multiple I/Os. This simplifies board layout and reduces system cost. Their low-edge-rate (dv/dt) data transmission causes less electromagnetic interference (EMI) on the board. However, they are not suitable for high-frequency (>200 MHz) switching due to noise impact and higher power consumption.

### LVTTL (Low-Voltage TTL)

This is a general-purpose standard (EIA/JESD8-B) for 3.3 V applications. It uses an LVTTL input buffer and a push-pull output buffer. The LVTTL output buffer can have up to six different programmable drive strengths. The default drive strength is 12 mA. VCCI is 3.3 V. Refer to "I/O Programmable Features" on page 188 for details.

## LVCMOS (Low-Voltage CMOS)

The low power flash devices provide four different kinds of LVCMOS: LVCMOS 3.3 V, LVCMOS 2.5 V, LVCMOS 1.8 V, and LVCMOS 1.5 V. LVCMOS 3.3 V is an extension of the LVCMOS standard (JESD8-B-compliant) used for general-purpose 3.3 V applications.

LVCMOS 2.5 V is an extension of the LVCMOS standard (JESD8-5–compliant) used for general-purpose 2.5 V applications.

There is yet another standard supported by IGLOO and ProASIC3 devices (except A3P030): LVCMOS 2.5/5.0 V. This standard is similar to LVCMOS 2.5 V, with the exception that it can support up to 3.3 V on the input side (2.5 V output drive).

LVCMOS 1.8 V is an extension of the LVCMOS standard (JESD8-7–compliant) used for general-purpose 1.8 V applications. LVCMOS 1.5 V is an extension of the LVCMOS standard (JESD8-11–compliant) used for general-purpose 1.5 V applications.

The VCCI values for these standards are 3.3 V, 2.5 V, 1.8 V, and 1.5 V, respectively. Like LVTTL, the output buffer has up to seven different programmable drive strengths (2, 4, 6, 8, 12, 16, and 24 mA). Refer to "I/O Programmable Features" on page 188 for details.

### 3.3 V PCI (Peripheral Component Interface)

This standard specifies support for both 33 MHz and 66 MHz PCI bus applications. It uses an LVTTL input buffer and a push-pull output buffer. With the aid of an external resistor, this I/O standard can be 5 V–compliant for low power flash devices. It does not have programmable drive strength.

### 3.3 V PCI-X (Peripheral Component Interface Extended)

An enhanced version of the PCI specification, 3.3 V PCI-X can support higher average bandwidths; it increases the speed that data can move within a computer from 66 MHz to 133 MHz. It is backward-

## Software-Controlled I/O Attributes

Users may modify these programmable I/O attributes using the I/O Attribute Editor. Modifying an I/O attribute may result in a change of state in Designer. Table 9-2 details which steps have to be re-run as a function of modified I/O attribute.

|                           | Designer States <sup>1</sup> |        |      |        |       |

|---------------------------|------------------------------|--------|------|--------|-------|

| I/O Attribute             | Compile                      | Layout | Fuse | Timing | Power |

| Slew Control <sup>2</sup> | No                           | No     | Yes  | Yes    | Yes   |

| Output Drive (mA)         | No                           | No     | Yes  | Yes    | Yes   |

| Skew Control              | No                           | No     | Yes  | Yes    | Yes   |

| Resistor Pull             | No                           | No     | Yes  | Yes    | Yes   |

| Input Delay               | No                           | No     | Yes  | Yes    | Yes   |

| Schmitt Trigger           | No                           | No     | Yes  | Yes    | Yes   |

| OUT_LOAD                  | No                           | No     | No   | Yes    | Yes   |

| COMBINE_REGISTER          | Yes                          | Yes    | N/A  | N/A    | N/A   |

Table 9-2 • Designer State (resulting from I/O attribute modification)

Notes:

1. No = Remains the same, Yes = Re-run the step, N/A = Not applicable

2. Skew control does not apply to IGLOO nano, IGLOO PLUS, and ProASIC3 nano devices.

3. Programmable input delay is applicable only for ProASIC3E, ProASIC3EL, RT ProASIC3, and IGLOOe devices.

I/O Software Control in Low Power Flash Devices

### **Output Buffers**

There are two variations: Regular and Special.

If the **Regular** variation is selected, only the Width (1 to 128) needs to be entered. The default value for Width is 1.

The Special variation has Width, Technology, Output Drive, and Slew Rate options.

#### **Bidirectional Buffers**

There are two variations: Regular and Special.

The Regular variation has Enable Polarity (Active High, Active Low) in addition to the Width option.

The **Special** variation has Width, Technology, Output Drive, Slew Rate, and Resistor Pull-Up/-Down options.

#### **Tristate Buffers**

Same as Bidirectional Buffers.

#### DDR

There are eight variations: DDR with Regular Input Buffers, Special Input Buffers, Regular Output Buffers, Special Output Buffers, Regular Tristate Buffers, Special Tristate Buffers, Regular Bidirectional Buffers, and Special Bidirectional Buffers.

These variations resemble the options of the previous I/O macro. For example, the Special Input Buffers variation has Width, Technology, Voltage Level, and Resistor Pull-Up/-Down options. DDR is not available on IGLOO PLUS devices.

- 4. Once the desired configuration is selected, click the **Generate** button. The Generate Core window opens (Figure 9-4).

- 5. Enter a name for the macro. Click **OK**. The core will be generated and saved to the appropriate location within the project files (Figure 9-5 on page 257).

Figure 9-4 • Generate Core Window

6. Instantiate the I/O macro in the top-level code.

The user must instantiate the DDR\_REG or DDR\_OUT macro in the design. Use SmartGen to generate both these macros and then instantiate them in your top level. To combine the DDR macros with the I/O, the following rules must be met:

I/O Software Control in Low Power Flash Devices

### Instantiating in HDL code

All the supported I/O macros can be instantiated in the top-level HDL code (refer to the *IGLOO*, *ProASIC3*, *SmartFusion*, *and Fusion Macro Library Guide* for a detailed list of all I/O macros). The following is an example:

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3e;

entity TOP is

port(IN2, IN1 : in std_logic; OUT1 : out std_logic);

end TOP;

architecture DEF_ARCH of TOP is

component INBUF_LVCMOS5U

port(PAD : in std_logic := 'U'; Y : out std_logic);

end component;

component INBUF_LVCMOS5

port(PAD : in std_logic := 'U'; Y : out std_logic);

end component;

component OUTBUF_SSTL3_II

port(D : in std_logic := 'U'; PAD : out std_logic);

end component;

Other component ....

signal x, y, z.....other signals : std_logic;

begin

I1 : INBUF_LVCMOS5U

port map(PAD => IN1, Y =>x);

12 : INBUF LVCMOS5

port map(PAD => IN2, Y => y);

I3 : OUTBUF_SSTL3_II

port map(D => z, PAD => OUT1);

```

other port mapping ...

end DEF\_ARCH;

## Synthesizing the Design

Libero SoC integrates with the Synplify<sup>®</sup> synthesis tool. Other synthesis tools can also be used with Libero SoC. Refer to the *Libero SoC User's Guide* or Libero online help for details on how to set up the Libero tool profile with synthesis tools from other vendors.

During synthesis, the following rules apply:

- Generic macros:

- Users can instantiate generic INBUF, OUTBUF, TRIBUF, and BIBUF macros.

- Synthesis will automatically infer generic I/O macros.

- The default I/O technology for these macros is LVTTL.

- Users will need to use the I/O Attribute Editor in Designer to change the default I/O standard if needed (see Figure 9-6 on page 259).

- Technology-specific I/O macros:

- Technology-specific I/O macros, such as INBUF\_LVCMO25 and OUTBUF\_GTL25, can be instantiated in the design. Synthesis will infer these I/O macros in the netlist.

If the assignment is not successful, an error message appears in the Output window.

To undo the I/O bank assignments, choose **Undo** from the **Edit** menu. Undo removes the I/O technologies assigned by the IOBA. It does not remove the I/O technologies previously assigned.

To redo the changes undone by the Undo command, choose Redo from the Edit menu.

To clear I/O bank assignments made before using the Undo command, manually unassign or reassign I/O technologies to banks. To do so, choose **I/O Bank Settings** from the **Edit** menu to display the I/O Bank Settings dialog box.

## Conclusion

Fusion, IGLOO, and ProASIC3 support for multiple I/O standards minimizes board-level components and makes possible a wide variety of applications. The Microsemi Designer software, integrated with Libero SoC, presents a clear visual display of I/O assignments, allowing users to verify I/O and board-level design requirements before programming the device. The device I/O features and functionalities ensure board designers can produce low-cost and low power FPGA applications fulfilling the complexities of contemporary design needs.

## **Related Documents**

## **User's Guides**

Libero SoC User's Guide http://www.microsemi.com/soc/documents/libero\_ug.pdf IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide http://www.microsemi.com/soc/documents/pa3\_libguide\_ug.pdf SmartGen Core Reference Guide http://www.microsemi.com/soc/documents/genguide ug.pdf

DDR for Microsemi's Low Power Flash Devices

## **Instantiating DDR Registers**

Using SmartGen is the simplest way to generate the appropriate RTL files for use in the design. Figure 10-4 shows an example of using SmartGen to generate a DDR SSTL2 Class I input register. SmartGen provides the capability to generate all of the DDR I/O cells as described. The user, through the graphical user interface, can select from among the many supported I/O standards. The output formats supported are Verilog, VHDL, and EDIF.

Figure 10-5 on page 277 through Figure 10-8 on page 280 show the I/O cell configured for DDR using SSTL2 Class I technology. For each I/O standard, the I/O pad is buffered by a special primitive that indicates the I/O standard type.

Figure 10-4 • Example of Using SmartGen to Generate a DDR SSTL2 Class I Input Register

Security in Low Power Flash Devices

## **Security in Action**

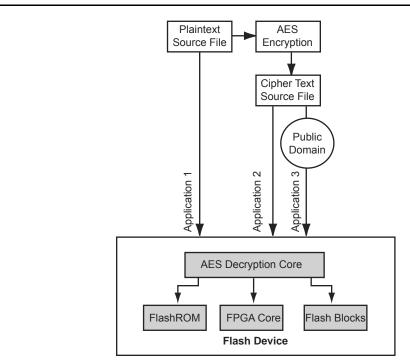

This section illustrates some applications of the security advantages of Microsemi's devices (Figure 12-6).

Note: Flash blocks are only used in Fusion devices

Figure 12-6 • Security Options

## Application 1: Trusted Environment

As illustrated in Figure 12-7, this application allows the programming of devices at design locations where research and development take place. Therefore, encryption is not necessary and is optional to the user. This is often a secure way to protect the design, since the design program files are not sent elsewhere. In situations where production programming is not available at the design location, programming centers (such as Microsemi In-House Programming) provide a way of programming designs at an alternative, secure, and trusted location. In this scenario, the user generates a STAPL programming file from the Designer software in plaintext format, containing information on the entire design or the portion of the design. Once the design is programmed to unprogrammed devices, the design is protected by this FlashLock Pass Key. If no future programming is needed, the user can consider permanently securing the IGLOO and ProASIC3 device, as discussed in the "Permanent FlashLock" section on page 307.

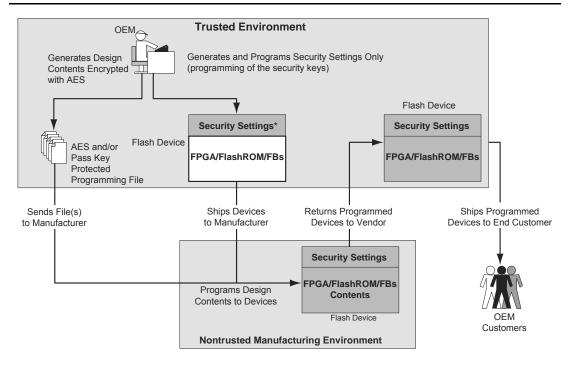

## **Application 2: Nontrusted Environment—Unsecured Location**

Often, programming of devices is not performed in the same location as actual design implementation, to reduce manufacturing cost. Overseas programming centers and contract manufacturers are examples of this scenario.

To achieve security in this case, the AES key and the FlashLock Pass Key can be initially programmed in-house (trusted environment). This is done by generating a programming file with only the security settings and no design contents. The design FPGA core, FlashROM, and (for Fusion) FB contents are generated in a separate programming file. This programming file must be set with the same AES key that was used to program to the device previously so the device will correctly decrypt this encrypted programming file. As a result, the encrypted design content programming file can be safely sent off-site to nontrusted programming locations for design programming. Figure 12-7 shows a more detailed flow for this application.

Notes:

1. Programmed portion indicated with dark gray.

2. Programming of FBs applies to Fusion only.

Figure 12-7 • Application 2: Device Programming in a Nontrusted Environment

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

## IEEE 1532 (JTAG) Interface

The supported industry-standard IEEE 1532 programming interface builds on the IEEE 1149.1 (JTAG) standard. IEEE 1532 defines the standardized process and methodology for ISP. Both silicon and software issues are addressed in IEEE 1532 to create a simplified ISP environment. Any IEEE 1532 compliant programmer can be used to program low power flash devices. Device serialization is not supported when using the IEEE1532 standard. Refer to the standard for detailed information about IEEE 1532.

## Security

Unlike SRAM-based FPGAs that require loading at power-up from an external source such as a microcontroller or boot PROM, Microsemi nonvolatile devices are live at power-up, and there is no bitstream required to load the device when power is applied. The unique flash-based architecture prevents reverse engineering of the programmed code on the device, because the programmed data is stored in nonvolatile memory cells. Each nonvolatile memory cell is made up of small capacitors and any physical deconstruction of the device will disrupt stored electrical charges.

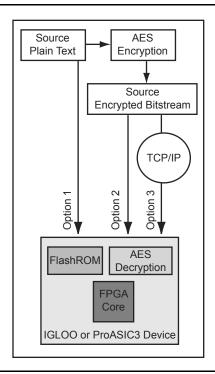

Each low power flash device has a built-in 128-bit Advanced Encryption Standard (AES) decryption core, except for the 30 k gate devices and smaller. Any FPGA core or FlashROM content loaded into the device can optionally be sent as encrypted bitstream and decrypted as it is loaded. This is particularly suitable for applications where device updates must be transmitted over an unsecured network such as the Internet. The embedded AES decryption core can prevent sensitive data from being intercepted (Figure 13-1 on page 331). A single 128-bit AES Key (32 hex characters) is used to encrypt FPGA core programming data and/or FlashROM programming data in the Microsemi tools. The low power flash devices also decrypt with a single 128-bit AES Key. In addition, low power flash devices support a Message Authentication Code (MAC) for authentication of the encrypted bitstream on-chip. This allows the encrypted bitstream to be authenticated and prevents erroneous data from being programmed into the device. The FPGA core, FlashROM, and Flash Memory Blocks (FBs), in Fusion only, can be updated independently using a programming file that is AES-encrypted (cipher text) or uses plain text.

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

Figure 13-2 shows different applications for ISP programming.

- 1. In a trusted programming environment, you can program the device using the unencrypted (plaintext) programming file.

- 2. You can program the AES Key in a trusted programming environment and finish the final programming in an untrusted environment using the AES-encrypted (cipher text) programming file.

- 3. For the remote ISP updating/reprogramming, the AES Key stored in the device enables the encrypted programming bitstream to be transmitted through the untrusted network connection.

Microsemi low power flash devices also provide the unique Microsemi FlashLock feature, which protects the Pass Key and AES Key. Unless the original FlashLock Pass Key is used to unlock the device, security settings cannot be modified. Microsemi does not support read-back of FPGA core-programmed data; however, the FlashROM contents can selectively be read back (or disabled) via the JTAG port based on the security settings established by the Microsemi Designer software. Refer to the "Security in Low Power Flash Devices" section on page 301 for more information.

Figure 13-2 • Different ISP Use Models

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

| Date                     | Changes                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010<br>(continued) | The "Chain Integrity Test Error Analyze Chain Failure" section was renamed to the "Scan Chain Failure" section, and the Analyze Chain command was changed to Scan Chain. It was noted that occasionally a faulty programmer can cause scan chain failures.                                                                                                                                   | 338  |

| v1.5<br>(August 2009)    | The "CoreMP7 Device Security" section was removed from "Security in ARM-<br>Enabled Low Power Flash Devices", since M7-enabled devices are no longer<br>supported.                                                                                                                                                                                                                           | 331  |

| v1.4<br>(December 2008)  | The "ISP Architecture" section was revised to include information about core voltage for IGLOO V2 and ProASIC3L devices, as well as 50 mV increments allowable in Designer software.                                                                                                                                                                                                         | 327  |

|                          | IGLOO nano and ProASIC3 nano devices were added to Table 13-1 • Flash-Based FPGAs Supporting ISP.                                                                                                                                                                                                                                                                                            | 328  |

|                          | A second capacitor was added to Figure 13-6 • Board Layout and Programming Header Top View.                                                                                                                                                                                                                                                                                                  | 337  |

| v1.3<br>(October 2008)   | The "ISP Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                                                                                                  | 328  |

| v1.2<br>(June 2008)      | <ul> <li>The following changes were made to the family descriptions in Table 13-1 • Flash-Based FPGAs Supporting ISP:</li> <li>ProASIC3L was updated to include 1.5 V.</li> </ul>                                                                                                                                                                                                            | 328  |

|                          | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                                                                                                                                                                               |      |

| v1.1<br>(March 2008)     | The "ISP Architecture" section was updated to included the IGLOO PLUS family in the discussion of family-specific support. The text, "When 1.2 V is used, the device can be reprogrammed in-system at 1.5 V only," was revised to state, "Although the device can operate at 1.2 V core voltage, the device can only be reprogrammed when all supplies (VCC, VCCI, and VJTAG) are at 1.5 V." | 327  |

|                          | The "ISP Support in Flash-Based Devices" section and Table 13-1 • Flash-Based FPGAs Supporting ISP were updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                | 328  |

|                          | The "Security" section was updated to mention that 15 k gate devices do not have a built-in 128-bit decryption core.                                                                                                                                                                                                                                                                         | 330  |

|                          | Table 13-2 • Power Supplies was revised to remove the Normal Operation column and add a table note stating, "All supply voltages should be at 1.5 V or higher, regardless of the setting during normal operation."                                                                                                                                                                           | 329  |

|                          | The "ISP Programming Header Information" section was revised to change FP3-26PIN-ADAPTER to FP3-10PIN-ADAPTER-KIT. Table 13-3 • Programming Header Ordering Codes was updated with the same change, as well as adding the part number FFSD-05-D-06.00-01-N, a 10-pin cable with 50-mil-pitch sockets.                                                                                        | 335  |

|                          | The "Board-Level Considerations" section was updated to describe connecting two capacitors in parallel across VPUMP and GND for proper programming.                                                                                                                                                                                                                                          | 337  |

| v1.0<br>(January 2008)   | Information was added to the "Programming Voltage (VPUMP) and VJTAG" section about the JTAG interface pin.                                                                                                                                                                                                                                                                                   | 329  |

| 51900055-2/7.06          | ACTgen was changed to SmartGen.                                                                                                                                                                                                                                                                                                                                                              | N/A  |

|                          | In Figure 13-6 • Board Layout and Programming Header Top View, the order of the text was changed to:<br>VJTAG from the target board<br>VCCI from the target board                                                                                                                                                                                                                            | 337  |

|                          | VCC from the target board                                                                                                                                                                                                                                                                                                                                                                    |      |

# Index

### A

AES encryption 305 architecture 147 four I/O banks 13 global 47 IGLOO 12 IGLOO nano 11 IGLOO PLUS 13 IGLOOE 14 ProASIC3 nano 11 ProASIC3E 14 routing 18 spine 57 SRAM and FIFO 151 architecture overview 11 array coordinates 16

## В

boundary scan 357 board-level recommendations 360 chain 359 opcodes 359 brownout voltage 381

## С

CCC 98 board-level considerations 128 cascading 125 **Fusion locations 99** global resources 78 hardwired I/O clock input 124 **IGLOO** locations 97 **IGLOOe** locations 98 locations 96 overview 77 ProASIC3 locations 97 ProASIC3E locations 98 programming 78 software configuration 112 with integrated PLLs 95 without integrated PLLs 95 chip global aggregation 59 CLKDLY macro 81 clock aggregation 60 clock macros 62 clock sources core logic 92 PLL and CLKDLY macros 89 clocks delay adjustment 102 detailed usage information 120 multipliers and dividers 101 phase adjustment 103 physical constraints for quadrant clocks 124 SmartGen settings 121 static timing analysis 123 cold-sparing 382 compiling 261 report 261 contacting Microsemi SoC Products Group customer service 387 email 387 web-based technical support 387 context save and restore 34 customer service 387

## D

DDR architecture 271 design example 282 I/O options 273 input/output support 275 instantiating registers 276 design example 71 design recommendations 62 device architecture 147 DirectC 346 DirectC code 351

### Ε

efficient long-line resources 19 encryption 355

### F

FIFO features 157 initializing 164 memory block consumption 163 software support 170 usage 160 flash switch for programming 9 Flash\*Freeze design flow 39 design guide 34 device behavior 30 I/O state 28 management IP 36 pin locations 31 type 1 24 type 2 26 **ULSICC 40** Flash\*Freeze mode 24