Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Active                                                                       |

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | -                                                                            |

| Total RAM Bits                 | 516096                                                                       |

| Number of I/O                  | 147                                                                          |

| Number of Gates                | 3000000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                               |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 208-BFQFP                                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe3000l-pqg208 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table of Contents

|    | Introduction                                                             | . 213 |

|----|--------------------------------------------------------------------------|-------|

|    | Low Power Flash Device I/O Support                                       | . 214 |

|    | Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E                               | . 215 |

|    | I/O Architecture                                                         | . 220 |

|    | I/O Standards                                                            | . 223 |

|    | I/O Features                                                             | . 227 |

|    | Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout | . 241 |

|    | I/O Software Support                                                     | . 242 |

|    | User I/O Naming Convention                                               | . 245 |

|    | Board-Level Considerations                                               | . 246 |

|    | Conclusion                                                               | . 248 |

|    | Related Documents                                                        | . 248 |

|    | List of Changes                                                          | . 249 |

| _  | W0.0 %                                                                   | 05.   |

| 9  | I/O Software Control in Low Power Flash Devices                          |       |

|    | Flash FPGAs I/O Support                                                  |       |

|    | Software-Controlled I/O Attributes                                       |       |

|    | Implementing I/Os in Microsemi Software                                  |       |

|    | Assigning Technologies and VREF to I/O Banks                             |       |

|    | Conclusion                                                               |       |

|    | Related Documents                                                        |       |

|    | List of Changes                                                          | . 270 |

| 10 | DDR for Microsemi's Low Power Flash Devices                              | 271   |

|    | Introduction                                                             |       |

|    | Double Data Rate (DDR) Architecture                                      |       |

|    | DDR Support in Flash-Based Devices                                       |       |

|    | I/O Cell Architecture                                                    |       |

|    | Input Support for DDR                                                    |       |

|    | Output Support for DDR                                                   |       |

|    | Instantiating DDR Registers                                              |       |

|    | Design Example                                                           | . 282 |

|    | Conclusion                                                               | . 284 |

|    | List of Changes                                                          | . 285 |

|    |                                                                          |       |

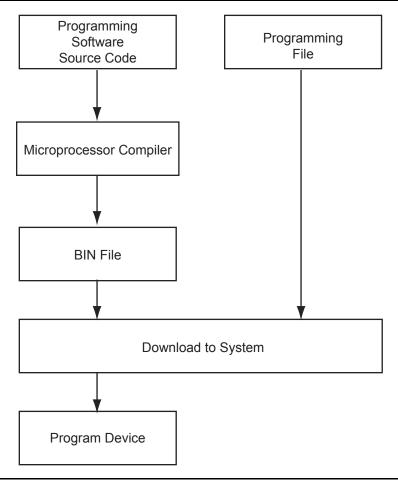

| 11 | Programming Flash Devices                                                |       |

|    | Introduction                                                             |       |

|    | Summary of Programming Support                                           |       |

|    | Programming Support in Flash Devices                                     |       |

|    | General Flash Programming Information                                    |       |

|    | Important Programming Guidelines                                         |       |

|    | Related Documents                                                        |       |

|    | List of Changes                                                          | . 298 |

| 12 | Security in Low Power Flash Devices                                      | 301   |

| _  | Security in Programmable Logic                                           |       |

|    | Security Support in Flash-Based Devices                                  |       |

|    | Security Architecture                                                    |       |

|    | Security Features                                                        |       |

|    | Security in Action                                                       | . 308 |

## Table of Contents

|    | Boundary Scan Chain                                       |       |

|----|-----------------------------------------------------------|-------|

|    | Board-Level Recommendations                               |       |

|    | Advanced Boundary Scan Register Settings                  |       |

|    | List of Changes                                           | . 362 |

| 17 | UJTAG Applications in Microsemi's Low Power Flash Devices | . 363 |

|    | Introduction                                              | . 363 |

|    | UJTAG Support in Flash-Based Devices                      | . 364 |

|    | UJTAG Macro                                               | . 365 |

|    | UJTAG Operation                                           |       |

|    | Typical UJTAG Applications                                |       |

|    | Conclusion                                                |       |

|    | Related Documents                                         |       |

|    | List of Changes                                           |       |

| 10 | Power-Up/-Down Behavior of Low Power Flash Devices        | 272   |

| 10 | ·                                                         |       |

|    | Introduction                                              |       |

|    | Flash Devices Support Power-Up Behavior                   |       |

|    | Power-Up/-Down Sequence and Transient Current             |       |

|    | I/O Behavior at Power-Up/-Down                            |       |

|    | Cold-Sparing                                              |       |

|    | Hot-Swapping                                              |       |

|    | Conclusion                                                |       |

|    | Related Documents                                         |       |

|    | List of Changes                                           | . 384 |

| Α  | Summary of Changes                                        | . 385 |

|    | History of Revision to Chapters                           | . 385 |

| В  | Product Support                                           | . 387 |

|    | Customer Service                                          |       |

|    | Customer Technical Support Center                         |       |

|    | Technical Support                                         |       |

|    | Website                                                   |       |

|    | Contacting the Customer Technical Support Center          |       |

|    | ITAR Technical Support                                    |       |

|    | TIAIX Technical Support                                   | . 500 |

|    | Index                                                     | 200   |

Table 3-2 • Chip Global Pin Name

| I/O Type               | Beginning of I/O Name | Notes                                                        |  |

|------------------------|-----------------------|--------------------------------------------------------------|--|

| Single-Ended           | GFAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |  |

|                        | GFA1/IOuxwByVz        | global at a time.                                            |  |

|                        | GFA2/IOuxwByVz        |                                                              |  |

|                        | GFBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a          |  |

|                        | GFB1/IOuxwByVz        | global at a time.                                            |  |

|                        | GFB2/IOuxwByVz        |                                                              |  |

|                        | GFC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |  |

|                        | GFC1/IOuxwByVz        | global at a time.                                            |  |

|                        | GFC2/IOuxwByVz        |                                                              |  |

|                        | GCAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |  |

|                        | GCA1/IOuxwByVz        | global at a time.                                            |  |

|                        | GCA2/IOuxwByVz        |                                                              |  |

|                        | GCBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |  |

|                        | GCB1/IOuxwByVz        | global at a time.                                            |  |

|                        | GCB2/IOuxwByVz        |                                                              |  |

|                        | GCC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |  |

|                        | GCC1/IOuxwByVz        | global at a time.                                            |  |

|                        | GCC2/IOuxwByVz        |                                                              |  |

| Differential I/O Pairs | GFAO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |

|                        | GFA1/IOuxwByVz        |                                                              |  |

|                        | GFBO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |

|                        | GFB1/IOuxwByVz        |                                                              |  |

|                        | GFCO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |

|                        | GFC1/IOuxwByVz        |                                                              |  |

|                        | GCAO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |

|                        | GCA1/IOuxwByVz        |                                                              |  |

|                        | GCBO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |

|                        | GCB1/IOuxwByVz        |                                                              |  |

|                        | GCCO/IOuxwByVz        | The output of the different pair will drive the chip global. |  |

|                        | GCC1/IOuxwByVz        |                                                              |  |

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

# **Spine Access**

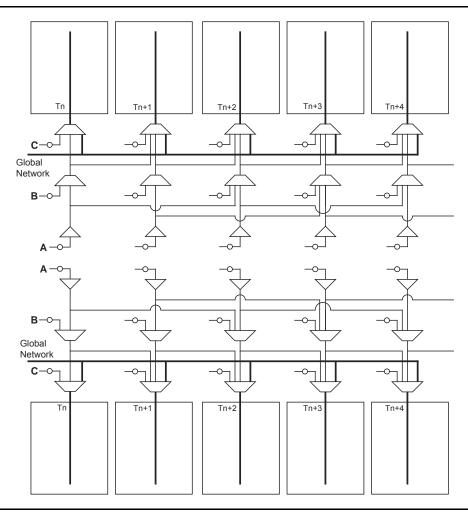

The physical location of each spine is identified by the letter T (top) or B (bottom) and an accompanying number (Tn or Bn). The number n indicates the horizontal location of the spine; 1 refers to the first spine on the left side of the die. Since there are six chip spines in each spine tree, there are up to six spines available for each combination of T (or B) and n (for example, six T1 spines). Similarly, there are three quadrant spines available for each combination of T (or B) and n (for example, four T1 spines), as shown in Figure 3-7.

Figure 3-7 • Chip Global Aggregation

A spine is also called a local clock network, and is accessed by the dedicated global MUX architecture. These MUXes define how a particular spine is driven. Refer to Figure 3-8 on page 60 for the global MUX architecture. The MUXes for each chip global spine are located in the middle of the die. Access to the top and bottom chip global spine is available from the middle of the die. There is no control dependency between the top and bottom spines. If a top spine, T1, of a chip global network is assigned to a net, B1 is not wasted and can be used by the global clock network. The signal assigned only to the top or bottom spine cannot access the middle two rows of the architecture. However, if a spine is using the top and bottom at the same time (T1 and B1, for instance), the previous restriction is lifted.

The MUXes for each quadrant global spine are located in the north and south sides of the die. Access to the top and bottom quadrant global spines is available from the north and south sides of the die. Since the MUXes for quadrant spines are located in the north and south sides of the die, you should not try to drive T1 and B1 quadrant spines from the same signal.

standard for CLKBUF is LVTTL in the current Microsemi Libero $^{\circledR}$  System-on-Chip (SoC) and Designer software.

Table 3-9 • I/O Standards within CLKBUF

| Name             | Description                                                    |  |  |

|------------------|----------------------------------------------------------------|--|--|

| CLKBUF_LVCMOS5   | LVCMOS clock buffer with 5.0 V CMOS voltage level              |  |  |

| CLKBUF_LVCMOS33  | LVCMOS clock buffer with 3.3 V CMOS voltage level              |  |  |

| CLKBUF_LVCMOS25  | LVCMOS clock buffer with 2.5 V CMOS voltage level <sup>1</sup> |  |  |

| CLKBUF_LVCMOS18  | LVCMOS clock buffer with 1.8 V CMOS voltage level              |  |  |

| CLKBUF_LVCMOS15  | LVCMOS clock buffer with 1.5 V CMOS voltage level              |  |  |

| CLKBUF_LVCMOS12  | LVCMOS clock buffer with 1.2 V CMOS voltage level              |  |  |

| CLKBUF_PCI       | PCI clock buffer                                               |  |  |

| CLKBUF_PCIX      | PCIX clock buffer                                              |  |  |

| CLKBUF_GTL25     | GTL clock buffer with 2.5 V CMOS voltage level <sup>1</sup>    |  |  |

| CLKBUF_GTL33     | GTL clock buffer with 3.3 V CMOS voltage level <sup>1</sup>    |  |  |

| CLKBUF_GTLP25    | GTL+ clock buffer with 2.5 V CMOS voltage level <sup>1</sup>   |  |  |

| CLKBUF_GTLP33    | GTL+ clock buffer with 3.3 V CMOS voltage level <sup>1</sup>   |  |  |

| CLKBUF_ HSTL _I  | HSTL Class I clock buffer <sup>1</sup>                         |  |  |

| CLKBUF_ HSTL _II | HSTL Class II clock buffer <sup>1</sup>                        |  |  |

| CLKBUF_SSTL2_I   | SSTL2 Class I clock buffer <sup>1</sup>                        |  |  |

| CLKBUF_SSTL2_II  | SSTL2 Class II clock buffer <sup>1</sup>                       |  |  |

| CLKBUF_SSTL3_I   | SSTL3 Class I clock buffer <sup>1</sup>                        |  |  |

| CLKBUF_SSTL3_II  | SSTL3 Class II clock buffer <sup>1</sup>                       |  |  |

#### Notes:

- 1. Supported in only the IGLOOe, ProASIC3E, AFS600, and AFS1500 devices

- 2. By default, the CLKBUF macro uses the 3.3 V LVTTL I/O technology.

The current synthesis tool libraries only infer the CLKBUF or CLKINT macros in the netlist. All other global macros must be instantiated manually into your HDL code. The following is an example of CLKBUF LVCMOS25 global macro instantiations that you can copy and paste into your code:

#### **VHDL**

```

component clkbuf_lvcmos25

port (pad : in std_logic; y : out std_logic);

end component

begin

-- concurrent statements

u2 : clkbuf_lvcmos25 port map (pad => ext_clk, y => int_clk);

end

Verilog

module design (_____);

input ____;

output ____;

clkbuf_lvcmos25 u2 (.y(int_clk), .pad(ext_clk);

endmodule

```

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **Global Buffers with No Programmable Delays**

Access to the global / quadrant global networks can be configured directly from the global I/O buffer, bypassing the CCC functional block (as indicated by the dotted lines in Figure 4-1 on page 77). Internal signals driven by the FPGA core can use the global / quadrant global networks by connecting via the routed clock input of the multiplexer tree.

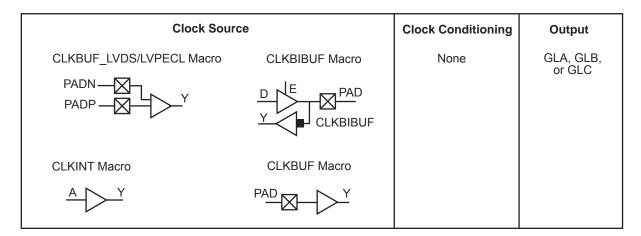

There are many specific CLKBUF macros supporting the wide variety of single-ended I/O inputs (CLKBUF) and differential I/O standards (CLKBUF\_LVDS/LVPECL) in the low power flash families. They are used when connecting global I/Os directly to the global/quadrant networks.

Note: IGLOO nano and ProASIC nano devices do not support differential inputs.

When an internal signal needs to be connected to the global/quadrant network, the CLKINT macro is used to connect the signal to the routed clock input of the network's MUX tree.

To utilize direct connection from global I/Os or from internal signals to the global/quadrant networks, CLKBUF, CLKBUF LVPECL/LVDS, and CLKINT macros are used (Figure 4-2).

- The CLKBUF and CLKBUF\_LVPECL/LVDS<sup>1</sup> macros are composite macros that include an I/O macro driving a global buffer, which uses a hardwired connection.

- The CLKBUF, CLKBUF\_LVPECL/LVDS<sup>1</sup> and CLKINT macros are pass-through clock sources and do not use the PLL or provide any programmable delay functionality.

- The CLKINT macro provides a global buffer function driven internally by the FPGA core.

The available CLKBUF macros are described in the *IGLOO*, *ProASIC3*, *SmartFusion*, and *Fusion Macro Library Guide*.

Note: IGLOO nano and ProASIC nano devices do not support differential inputs.

Figure 4-2 • CCC Options: Global Buffers with No Programmable Delay

# **Global Buffer with Programmable Delay**

Clocks requiring clock adjustments can utilize the programmable delay cores before connecting to the global / quadrant global networks. A maximum of 18 CCC global buffers can be instantiated in a device—three per CCC and up to six CCCs per device.

Each CCC functional block contains a programmable delay element for each of the global networks (up to three), and users can utilize these features by using the corresponding macro (Figure 4-3 on page 81).

<sup>1.</sup> B-LVDS and M-LVDS are supported with the LVDS macro.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **PLL Macro Signal Descriptions**

The PLL macro supports two inputs and up to six outputs. Table 4-3 gives a description of each signal.

Table 4-3 • Input and Output Signals of the PLL Block

| Signal    | Name                                  | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------|---------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLKA      | Reference Clock                       | Input  | Reference clock input for PLL core; input clock for primary output clock, GLA                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| OADIVRST  | Reset Signal for the Output Divider A | Input  | For Fusion only. OADIVRST can be used when you bypass the PLL core (i.e., OAMUX = 001). The purpose of the OADIVRST signals is to reset the output of the final clock divider to synchronize it with the input to that divider when the PLL is bypassed. The signal is active on a low to high transition. The signal must be low for at least one divider input. If PLL core is used, this signal is "don't care" and the internal circuitry will generate the reset signal for the synchronization purpose. |  |

| OADIVHALF | Output A Division by<br>Half          | Input  | For Fusion only. Active high. Division by half feature. This feature can only be used when users bypass the PLL core (i.e., OAMUX = 001) and the RC Oscillator (RCOSC) drives the CLKA input. This can be used to divide the 100 MHz RC oscillator by a factor of 1.5, 2.5, 3.5, 4.5 14.5). Refer to Table 4-18 on page 111 for more information.                                                                                                                                                             |  |

| EXTFB     | External Feedback                     | Input  | Allows an external signal to be compared to a reference clock in the PLL core's phase detector.                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| POWERDOWN | Power Down                            | Input  | Active low input that selects power-down mode and disables the PLL. With the POWERDOWN signal asserted, the PLL core sends 0 V signals on all of the outputs.                                                                                                                                                                                                                                                                                                                                                 |  |

| GLA       | Primary Output                        | Output | Primary output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| GLB       | Secondary 1 Output                    | Output | Secondary 1 output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| YB        | Core 1 Output                         | Output | Core 1 output clock to local routing network                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| GLC       | Secondary 2 Output                    | Output | Secondary 2 output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| YC        | Core 2 Output                         | Output | Core 2 output clock to local routing network                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| LOCK      | PLL Lock Indicator                    | Output | Active high signal indicating that steady-state lock has been achieved between CLKA and the PLL feedback signal                                                                                                                                                                                                                                                                                                                                                                                               |  |

#### Input Clock

The inputs to the input reference clock (CLKA) of the PLL can come from global input pins, regular I/O pins, or internally from the core. For Fusion families, the input reference clock can also be from the embedded RC oscillator or crystal oscillator.

# **Global Output Clocks**

GLA (Primary), GLB (Secondary 1), and GLC (Secondary 2) are the outputs of Global Multiplexer 1, Global Multiplexer 2, and Global Multiplexer 3, respectively. These signals (GLx) can be used to drive the high-speed global and quadrant networks of the low power flash devices.

A global multiplexer block consists of the input routing for selecting the input signal for the GLx clock and the output multiplexer, as well as delay elements associated with that clock.

# **Core Output Clocks**

YB and YC are known as Core Outputs and can be used to drive internal logic without using global network resources. This is especially helpful when global network resources must be conserved and utilized for other timing-critical paths.

ProASIC3L FPGA Fabric User's Guide

Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- · 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection (not applicable for IGLOO nano and ProASIC3 nano devices)

- · The FPGA core

Since the architecture of the devices varies as size increases, the following list details I/O types supported for globals:

#### IGLOO and ProASIC3

- LVDS-based clock sources are available only on 250 k gate devices and above (IGLOO nano and ProASIC3 nano devices do not support differential inputs).

- 60 k and 125 k gate devices support single-ended clock sources only.

- 15 k and 30 k gate devices support these inputs for CCC only and do not contain a PLL.

- · nano devices:

- 10 k, 15 k, and 20 k devices do not contain PLLs in the CCCs, and support only CLKBUF and CLKINT.

- 60 k, 125 k, and 250 k devices support one PLL in the middle left CCC position. In the absence of the PLL, this CCC can be used by CLKBUF, CLKINT, and CLKDLY macros. The corner CCCs support CLKBUF, CLKINT, and CLKDLY.

#### **Fusion**

- AFS600 and AFS1500: All single-ended, differential, and voltage-referenced I/O standards (Pro I/O).

- AFS090 and AFS250: All single-ended and differential I/O standards.

#### Clock Sources for PLL and CLKDLY Macros

The input reference clock (CLKA for a PLL macro, CLK for a CLKDLY macro) can be accessed from different sources via the associated clock multiplexer tree. Each CCC has the option of choosing the source of the input clock from one of the following:

- Hardwired I/O

- External I/O

- Core Logic

- RC Oscillator (Fusion only)

- · Crystal Oscillator (Fusion only)

The SmartGen macro builder tool allows users to easily create the PLL and CLKDLY macros with the desired settings. Microsemi strongly recommends using SmartGen to generate the CCC macros.

#### Hardwired I/O Clock Source

Hardwired I/O refers to global input pins that are hardwired to the multiplexer tree, which directly accesses the CCC global buffers. These global input pins have designated pin locations and are indicated with the I/O naming convention Gmn (m refers to any one of the positions where the PLL core is available, and n refers to any one of the three global input MUXes and the pin number of the associated global location, m). Choosing this option provides the benefit of directly connecting to the CCC reference clock input, which provides less delay. See Figure 4-9 on page 90 for an example illustration of the connections, shown in red. If a CLKDLY macro is initiated to utilize the programmable delay element of the CCC, the clock input can be placed at one of nine dedicated global input pin locations. In other words, if Hardwired I/O is chosen as the input source, the user can decide to place the input pin in one of the GmA0, GmA1, GmA2, GmB0, GmB1, GmB2, GmC0, GmC1, or GmC2 locations of the low power flash devices. When a PLL macro is used to utilize the PLL core in a CCC location, the clock input of the PLL can only be connected to one of three GmA\* global pin locations: GmA0, GmA1, or GmA2.

#### Figure 4-34 • Cascade PLL Configuration

Using internal feedback, we know from EQ 4-1 on page 102 that the maximum achievable output frequency from the primary output is

$$f_{GLA} = f_{CLKA} \times m / (n \times u) = 2 MHz \times 128 / (1 \times 1) = 256 MHz$$

EQ 4-5

Figure 4-35 shows the settings of the initial PLL. When configuring the initial PLL, specify the input to be either Hardwired I/O–Driven or External I/O–Driven. This generates a netlist with the initial PLL routed from an I/O. Do not specify the input to be Core Logic–Driven, as this prohibits the connection from the I/O pin to the input of the PLL.

Figure 4-35 • First-Stage PLL Showing Input of 2 MHz and Output of 256 MHz

A second PLL can be connected serially to achieve the required frequency. EQ 4-1 on page 102 to EQ 4-3 on page 102 are extended as follows:

$$f_{GLA2} = f_{GLA} \times m_2 / (n_2 \times u_2) = f_{CLKA1} \times m_1 \times m_2 / (n_1 \times u_1 \times n_2 \times u_2) - Primary PLL Output Clock$$

EQ 4-6

$$f_{GLB2} = f_{YB2} = f_{CLKA1} \times m_1 \times m_2 / (n_1 \times n_2 \times v_1 \times v_2) - \text{Secondary 1 PLL Output Clock(s)}$$

EQ 4-7

$$f_{GLC2} = f_{YC2} = f_{CLKA1} \times m_1 \times m_2 / (n_1 \times n_2 \times w_1 \times w_2) - \text{Secondary 2 PLL Output Clock(s)}$$

EQ 4-8

In the example, the final output frequency ( $f_{output}$ ) from the primary output of the second PLL will be as follows (EQ 4-9):

$$f_{output} = f_{GLA2} = f_{GLA} \times m_2 / (n_2 \times u_2) = 256 \text{ MHz} \times 70 / (64 \times 1) = 280 \text{ MHz}$$

EQ 4-9

Figure 4-36 on page 127 shows the settings of the second PLL. When configuring the second PLL (or any subsequent-stage PLLs), specify the input to be Core Logic—Driven. This generates a netlist with the second PLL routed internally from the core. Do not specify the input to be Hardwired I/O—Driven or External I/O—Driven, as these options prohibit the connection from the output of the first PLL to the input of the second PLL.

## ProASIC3L FPGA Fabric User's Guide

| Date                     | Change                                                                                                                                                                                                                                          | Page |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| June 2011<br>(continued) | The following sentence was removed from the "LVCMOS (Low-Voltage CMOS)" section (SAR 22634): "All these versions use a 3.3 V-tolerant CMOS input buffer and a push-pull output buffer."                                                         | 184  |

|                          | Hot-insertion was changed to "No" for other IGLOO and all ProASIC3 devices in Table 7-12 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in IGLOO and ProASIC3 Devices (SAR 24526).                                                         | 193  |

|                          | The "Electrostatic Discharge Protection" section was revised to remove references to tolerances (refer to the <i>Reliability Report</i> for tolerances). The Machine Model (MM) is not supported and was deleted from this section (SAR 24385). | 192  |

|                          | The "I/O Interfacing" section was revised to state that low power flash devices are 5 V—input— and 5 V—output—tolerant if certain I/O standards are selected, removing "without adding any extra circuitry," which was incorrect (SAR 21404).   | 208  |

| July 2010                | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                       |      |

| v1.4<br>(December 2008)  | The terminology in the "Low Power Flash Device I/O Support" section was revised.                                                                                                                                                                | 176  |

| v1.3<br>(October 2008)   | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                           |      |

| v1.2<br>(June 2008)      | The following changes were made to the family descriptions in Table 7-1 • Flash-Based FPGAs:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six.                                       | 176  |

| v1.1<br>(March 2008)     | Originally, this document contained information on all IGLOO and ProASIC3 families. With the addition of new families and to highlight the differences between the features, the document has been separated into 3 documents:                  | N/A  |

|                          | This document contains information specific to IGLOO, ProASIC3, and ProASIC3L.                                                                                                                                                                  |      |

|                          | "I/O Structures in IGLOOe and ProASIC3E Devices" in the <i>ProASIC3E FPGA Fabric User's Guide</i> contains information specific to IGLOOe, ProASIC3E, and ProASIC3EL I/O features.                                                              |      |

|                          | "I/O Structures in IGLOO PLUS Devices" in the <i>IGLOO PLUS FPGA Fabric User's Guide</i> contains information specific to IGLOO PLUS I/O features.                                                                                              |      |

# I/O Banks and I/O Standards Compatibility

I/Os are grouped into I/O voltage banks.

Each I/O voltage bank has dedicated I/O supply and ground voltages (VMV/GNDQ for input buffers and  $V_{CCI}$ /GND for output buffers). Because of these dedicated supplies, only I/Os with compatible standards can be assigned to the same I/O voltage bank. Table 8-3 on page 217 shows the required voltage compatibility values for each of these voltages.

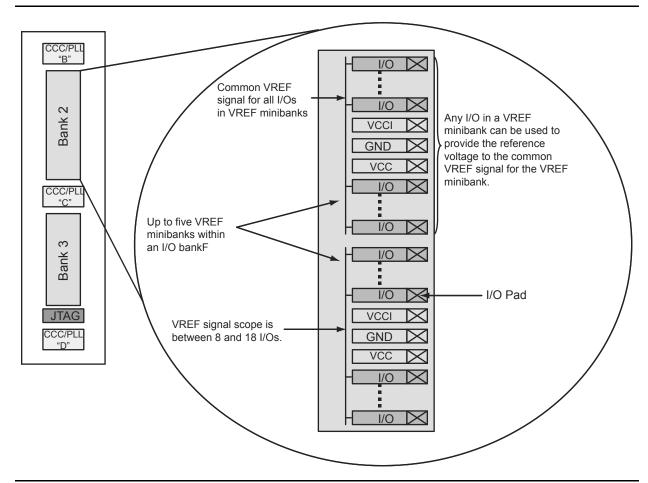

There are eight I/O banks (two per side).

Every I/O bank is divided into minibanks. Any user I/O in a VREF minibank (a minibank is the region of scope of a VREF pin) can be configured as a VREF pin (Figure 8-2). Only one  $V_{REF}$  pin is needed to control the entire  $V_{REF}$  minibank. The location and scope of the  $V_{REF}$  minibanks can be determined by the I/O name. For details, see the user I/O naming conventions for "IGLOOe and ProASIC3E" on page 245. Table 8-5 on page 217 shows the I/O standards supported by IGLOOe and ProASIC3E devices, and the corresponding voltage levels.

I/O standards are compatible if they comply with the following:

- · Their VCCI and VMV values are identical.

- Both of the standards need a VREF, and their VREF values are identical.

- All inputs and disabled outputs are voltage tolerant up to 3.3 V.

For more information about I/O and global assignments to I/O banks in a device, refer to the specific pin table for the device in the packaging section of the datasheet, and see the user I/O naming conventions for "IGLOOe and ProASIC3E" on page 245.

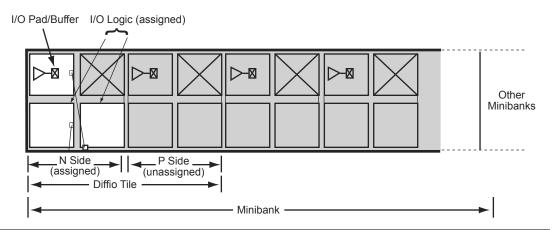

Figure 8-2 • Typical IGLOOe and ProASIC3E I/O Bank Detail Showing V<sub>REF</sub> Minibanks

#### I/O Bank Structure

Low power flash device I/Os are divided into multiple technology banks. The number of banks is device-dependent. The IGLOOe, ProASIC3EL, and ProASIC3E devices have eight banks (two per side); and IGLOO, ProASIC3L, and ProASIC3 devices have two to four banks. Each bank has its own V<sub>CCI</sub> power supply pin. Multiple I/O standards can co-exist within a single I/O bank.

In IGLOOe, ProASIC3EL, and ProASIC3E devices, each I/O bank is subdivided into  $V_{REF}$  minibanks. These are used by voltage-referenced I/Os. VREF minibanks contain 8 to 18 I/Os. All I/Os in a given minibank share a common VREF line (only one VREF pin is needed per VREF minibank). Therefore, if an I/O in a VREF minibank is configured as a VREF pin, the remaining I/Os in that minibank will be able to use the voltage assigned to that pin. If the location of the VREF pin is selected manually in the software, the user must satisfy VREF rules (refer to the "I/O Software Control in Low Power Flash Devices" section on page 251). If the user does not pick the VREF pin manually, the software automatically assigns it.

Figure 8-4 is a snapshot of a section of the I/O ring, showing the basic elements of an I/O tile, as viewed from the Designer place-and-route tool's MultiView Navigator (MVN).

Figure 8-4 • Snapshot of an I/O Tile

Low power flash device I/Os are implemented using two tile types: I/O and differential I/O (diffio).

The diffio tile is built up using two I/O tiles, which form an I/O pair (P side and N side). These I/O pairs are used according to differential I/O standards. Both the P and N sides of the diffio tile include an I/O buffer and two I/O logic blocks (auxiliary and main logic).

Every minibank (E devices only) is built up from multiple diffio tiles. The number of the minibank depends on the different-size dies. Refer to the "Pro I/Os—IGLOOe, ProASIC3EL, and ProASIC3E" section on page 215 for an illustration of the minibank structure.

Figure 8-5 on page 222 shows a simplified diagram of the I/O buffer circuitry. The Output Enable signal (OE) enables the output buffer to pass the signal from the core logic to the pin. The output buffer contains ESD protection circuitry, an n-channel transistor that shunts all ESD surges (up to the limit of the device ESD specification) to GND. This transistor also serves as an output pull-down resistor.

Each output buffer also contains programmable slew rate, drive strength, programmable power-up state (pull-up/-down resistor), hot-swap, 5 V tolerance, and clamp diode control circuitry. Multiple flash switches (not shown in Figure 8-5 on page 222) are programmed by user selections in the software to activate different I/O features.

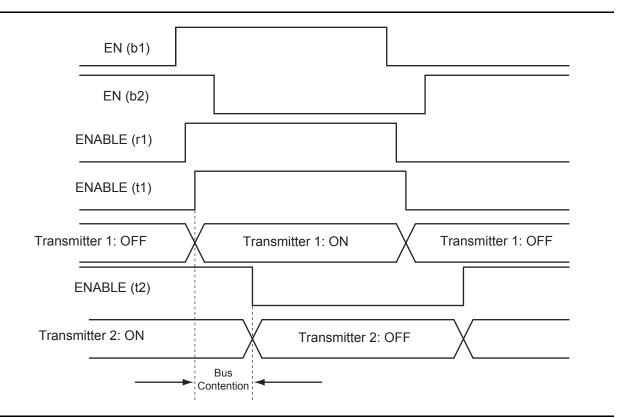

Figure 8-18 • Timing Diagram (bypasses skew circuit)

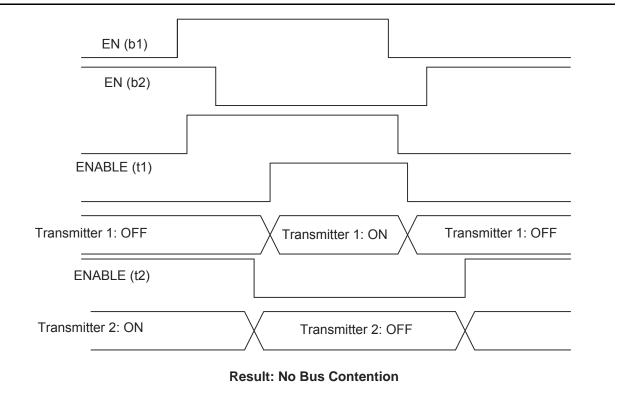

Figure 8-19 • Timing Diagram (with skew circuit selected)

# Implementing I/Os in Microsemi Software

Microsemi Libero SoC software is integrated with design entry tools such as the SmartGen macro builder, the ViewDraw schematic entry tool, and an HDL editor. It is also integrated with the synthesis and Designer tools. In this section, all necessary steps to implement the I/Os are discussed.

# **Design Entry**

There are three ways to implement I/Os in a design:

- Use the SmartGen macro builder to configure I/Os by generating specific I/O library macros and then instantiating them in top-level code. This is especially useful when creating I/O bus structures.

- 2. Use an I/O buffer cell in a schematic design.

- 3. Manually instantiate specific I/O macros in the top-level code.

If technology-specific macros, such as INBUF\_LVCMOS33 and OUTBUF\_PCI, are used in the HDL code or schematic, the user will not be able to change the I/O standard later on in Designer. If generic I/O macros are used, such as INBUF, OUTBUF, TRIBUF, CLKBUF, and BIBUF, the user can change the I/O standard using the Designer I/O Attribute Editor tool.

# Using SmartGen for I/O Configuration

The SmartGen tool in Libero SoC provides a GUI-based method of configuring the I/O attributes. The user can select certain I/O attributes while configuring the I/O macro in SmartGen. The steps to configure an I/O macro with specific I/O attributes are as follows:

- 1. Open Libero SoC.

- 2. On the left-hand side of the Catalog View, select I/O, as shown in Figure 9-2.

Figure 9-2 • SmartGen Catalog

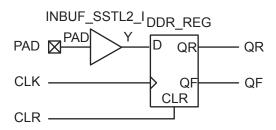

# **DDR Input Register**

Figure 10-5 • DDR Input Register (SSTL2 Class I)

The corresponding structural representations, as generated by SmartGen, are shown below:

### Verilog

end DEF\_ARCH;

```

module DDR_InBuf_SSTL2_I(PAD,CLR,CLK,QR,QF);

PAD, CLR, CLK;

output QR, QF;

wire Y;

INBUF_SSTL2_I INBUF_SSTL2_I_0_inst(.PAD(PAD),.Y(Y));

DDR_REG_DDR_REG_O_inst(.D(Y),.CLK(CLK),.CLR(CLR),.QR(QR),.QF(QF));

endmodule

VHDL

library ieee;

use ieee.std_logic_1164.all;

--The correct library will be inserted automatically by SmartGen

library proasic3; use proasic3.all;

--library fusion; use fusion.all;

--library igloo; use igloo.all;

entity DDR_InBuf_SSTL2_I is

port(PAD, CLR, CLK : in std_logic; QR, QF : out std_logic);

end DDR_InBuf_SSTL2_I;

architecture DEF_ARCH of DDR_InBuf_SSTL2_I is

component INBUF_SSTL2_I

port(PAD : in std_logic := 'U'; Y : out std_logic) ;

end component;

component DDR_REG

port(D, CLK, CLR : in std_logic := 'U'; QR, QF : out std_logic);

end component;

signal Y : std_logic ;

begin

INBUF_SSTL2_I_0_inst : INBUF_SSTL2_I

port map(PAD => PAD, Y => Y);

DDR_REG_0_inst : DDR_REG

\texttt{port map}(\texttt{D => Y, CLK => CLK, CLR => CLR, QR => QR, QF => QF);}

```

#### **VHDL**

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3; use proasic3.all;

entity DDR_BiDir_HSTL_I_LowEnb is

port(DataR, DataF, CLR, CLK, Trien : in std_logic; QR, QF : out std_logic;

PAD : inout std_logic) ;

end DDR_BiDir_HSTL_I_LowEnb;

architecture DEF_ARCH of DDR_BiDir_HSTL_I_LowEnb is

component INV

port(A : in std_logic := 'U'; Y : out std_logic);

end component;

component DDR_OUT

port(DR, DF, CLK, CLR : in std_logic := 'U'; Q : out std_logic);

end component;

component DDR_REG

port(D, CLK, CLR : in std_logic := 'U'; QR, QF : out std_logic);

end component;

component BIBUF_HSTL_I

port(PAD : inout std_logic := 'U'; D, E : in std_logic := 'U'; Y : out std_logic);

end component;

signal TrienAux, D, Q : std_logic ;

begin

Inv_Tri : INV

port map(A => Trien, Y => TrienAux);

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

DDR_REG_0_inst : DDR_REG

port map(D => D, CLK => CLK, CLR => CLR, QR => QR, QF => QF);

BIBUF_HSTL_I_0_inst : BIBUF_HSTL_I

port map(PAD => PAD, D => Q, E => TrienAux, Y => D);

end DEF_ARCH;

```

# 13 – In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

# Introduction

Microsemi's low power flash devices are all in-system programmable. This document describes the general requirements for programming a device and specific requirements for the FlashPro4/3/3X programmers<sup>1</sup>.

IGLOO, ProASIC3, SmartFusion, and Fusion devices offer a low power, single-chip, live-at-power-up solution with the ASIC advantages of security and low unit cost through nonvolatile flash technology. Each device contains 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications such as Internet Protocol (IP) addressing, user system preference storage, device serialization, or subscription-based business models. IGLOO, ProASIC3, SmartFusion, and Fusion devices offer the best in-system programming (ISP) solution, FlashLock® security features, and AES-decryption-based ISP.

# **ISP Architecture**

Low power flash devices support ISP via JTAG and require a single VPUMP voltage of 3.3 V during programming. In addition, programming via a microcontroller in a target system is also supported.

Refer to the "Microprocessor Programming of Microsemi's Low Power Flash Devices" chapter of an appropriate FPGA fabric user's guide.

Family-specific support:

- ProASIC3, ProASIC3E, SmartFusion, and Fusion devices support ISP.

- ProASIC3L devices operate using a 1.2 V core voltage; however, programming can be done only at 1.5 V. Voltage switching is required in-system to switch from a 1.2 V core to 1.5 V core for programming.

- IGLOO and IGLOOe V5 devices can be programmed in-system when the device is using a 1.5 V supply voltage to the FPGA core.

- IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only) or 1.5 V. IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V. Voltage switching is required in-system to switch from a 1.2 V supply (VCC,VCCI, and VJTAG) to 1.5 V for programming. The exception is that V2 devices can be programmed at 1.2 V VCC with FlashPro4.

IGLOO devices cannot be programmed in-system when the device is in Flash\*Freeze mode. The device should exit Flash\*Freeze mode and be in normal operation for programming to start. Programming operations in IGLOO devices can be achieved when the device is in normal operating mode and a 1.5 V core voltage is used.

#### **JTAG 1532**

IGLOO, ProASIC3, SmartFusion, and Fusion devices support the JTAG-based IEEE 1532 standard for ISP. To start JTAG operations, the IGLOO device must exit Flash\*Freeze mode and be in normal operation before starting to send JTAG commands to the device. As part of this support, when a device is in an unprogrammed state, all user I/O pins are disabled. This is achieved by keeping the global IO\_EN

<sup>1.</sup> FlashPro4 replaced FlashPro3/3X in 2010 and is backward compatible with FlashPro3/3X as long as there is no connection to pin 4 on the JTAG header on the board. On FlashPro3/3X, there is no connection to pin 4 on the JTAG header; however, pin 4 is used for programming mode (Prog\_Mode) on FlashPro4. When converting from FlashPro3/3X to FlashPro4, users should make sure that JTAG connectors on system boards do not have any connection to pin 4. FlashPro3X supports discrete TCK toggling that is needed to support non-JTAG compliant devices in the chain. This feature is included in FlashPro4.

# **Circuit Description**

All IGLOO devices as well as the ProASIC3L product family are available in two versions: V5 devices, which are powered by a 1.5 V supply and V2 devices, which are powered by a supply anywhere in the range of 1.2 V to 1.5 V in 50 mV increments. Applications that use IGLOO or ProASIC3L devices powered by a 1.2 V core supply must have a mechanism that switches the core voltage from 1.2 V (or other voltage below 1.5 V) to 1.5 V during in-system programming (ISP). There are several possible techniques to meet this requirement. Microsemi recommends utilizing a linear voltage regulator, a resistor voltage divider, and an N-Channel Digital FET to set the appropriate VCC voltage, as shown in Figure 14-1.

Where 1.2 V is mentioned in the following text, the meaning applies to any voltage below the 1.5 V range. Resistor values in the figures have been calculated for 1.2 V, so refer to power regulator datasheets if a different core voltage is required.

The main component of Microsemi's recommended circuit is the LTC3025 linear voltage regulator from LinearTech. The output voltage of the LTC3025 on the OUT pin is set by the ratio of two external resistors, R37 and R38, in a voltage divider. The linear voltage regulator adjusts the voltage on the OUT pin to maintain the ADJ pin voltage at 0.4 V (referenced to ground). By using an R38 value of 40.2 k $\Omega$  and an R37 value of 80.6 k $\Omega$ , the output voltage on the OUT pin is 1.2 V. To achieve 1.5 V on the OUT pin, R44 can be used in parallel with R38. The OUT pin can now be used as a switchable source for the VCC supply. Refer to the *LTC3025 Linear Voltage Regulator datasheet* for more information.

In Figure 14-1, the N-Channel Digital FET is used to enable and disable R44. This FET is controlled by the JTAG TRST signal driven by the FlashPro3 programmer. During programming of the device, the TRST signal is driven HIGH by the FlashPro3, and turns the N-Channel Digital FET ON. When the FET is ON, R44 becomes enabled as a parallel resistance to R38, which forces the regulator to set OUT to 1.5 V.

When the FlashPro3 is connected and not in programming mode or when it is not connected, the pull-down resistor, R10, will pull the TRST signal LOW. When this signal is LOW, the N-Channel Digital FET is "open" and R44 is not part of the resistance seen by the LTC3025. The new resistance momentarily changes the voltage value on the ADJ pin, which in turn causes the output of the LTC3025 to compensate by setting OUT to 1.2 V. Now the device will run in regular active mode at the regular 1.2 V core voltage.

Figure 14-1 • Circuit Diagram

Figure 15-3 • MCU FPGA Programming Model

#### **FlashROM**

Microsemi low power flash devices have 1 kbit of user-accessible, nonvolatile, FlashROM on-chip. This nonvolatile FlashROM can be programmed along with the core or on its own using the standard IEEE 1532 JTAG programming interface.

The FlashROM is architected as eight pages of 128 bits. Each page can be individually programmed (erased and written). Additionally, on-chip AES security decryption can be used selectively to load data securely into the FlashROM (e.g., over public or private networks, such as the Internet). Refer to the "FlashROM in Microsemi's Low Power Flash Devices" section on page 133.