Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | AVR                                                                          |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 66MHz                                                                        |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                        |

| Number of I/O              | 110                                                                          |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.75V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 144-LQFP                                                                     |

| Supplier Device Package    | 144-LQFP (20x20)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a3128s-alur |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 3-1.

GPIO Controller Function Multiplexing

|     |     |                    |      | G<br>P |        | PIN  | GPIO function  |                   |                     |   |

|-----|-----|--------------------|------|--------|--------|------|----------------|-------------------|---------------------|---|

| BGA | QFP | BGA                |      |        |        | Туре |                |                   |                     |   |

| 144 | 144 | 100                | PIN  | 0      | Supply | (2)  | Α              | В                 | С                   | D |

| L6  | 84  | H9 <sup>(1)</sup>  | PX18 | 69     | VDDIO  | x2   | EBI - ADDR[16] | DMACA - DMAACK[1] | TC0 - A2            |   |

| D5  | 35  | F1 <sup>(1)</sup>  | PX19 | 70     | VDDIO  | x2   | EBI - ADDR[15] | EIC - SCAN[0]     | TC0 - B2            |   |

| L4  | 73  | H6 <sup>(1)</sup>  | PX20 | 71     | VDDIO  | x2   | EBI - ADDR[14] | EIC - SCAN[1]     | TC0 - CLK0          |   |

| М5  | 80  | H2                 | PX21 | 72     | VDDIO  | x2   | EBI - ADDR[13] | EIC - SCAN[2]     | TC0 - CLK1          |   |

| M1  | 72  | K10 <sup>(1)</sup> | PX22 | 73     | VDDIO  | x2   | EBI - ADDR[12] | EIC - SCAN[3]     | TC0 - CLK2          |   |

| M6  | 85  | K1                 | PX23 | 74     | VDDIO  | x2   | EBI - ADDR[11] | EIC - SCAN[4]     | SSC - TX_CLOCK      |   |

| M7  | 86  | J2                 | PX24 | 75     | VDDIO  | x2   | EBI - ADDR[10] | EIC - SCAN[5]     | SSC - TX_DATA       |   |

| M8  | 92  | H4                 | PX25 | 76     | VDDIO  | x2   | EBI - ADDR[9]  | EIC - SCAN[6]     | SSC - RX_DATA       |   |

| L9  | 90  | J3                 | PX26 | 77     | VDDIO  | x2   | EBI - ADDR[8]  | EIC - SCAN[7]     | SSC - RX_FRAME_SYNC |   |

| К9  | 89  | K2                 | PX27 | 78     | VDDIO  | x2   | EBI - ADDR[7]  | SPI0 - MISO       | SSC - TX_FRAME_SYNC |   |

| L10 | 91  | K3                 | PX28 | 79     | VDDIO  | x2   | EBI - ADDR[6]  | SPIO - MOSI       | SSC - RX_CLOCK      |   |

| K11 | 94  | J4                 | PX29 | 80     | VDDIO  | x2   | EBI - ADDR[5]  | SPI0 - SPCK       |                     |   |

| M11 | 96  | G5                 | PX30 | 81     | VDDIO  | x2   | EBI - ADDR[4]  | SPI0 - NPCS[0]    |                     |   |

| M10 | 97  | H5                 | PX31 | 82     | VDDIO  | x2   | EBI - ADDR[3]  | SPI0 - NPCS[1]    |                     |   |

| М9  | 93  | K4 <sup>(1)</sup>  | PX32 | 83     | VDDIO  | x2   | EBI - ADDR[2]  | SPI0 - NPCS[2]    |                     |   |

| M12 | 95  |                    | PX33 | 84     | VDDIO  | x2   | EBI - ADDR[1]  | SPI0 - NPCS[3]    |                     |   |

| J3  | 61  |                    | PX34 | 85     | VDDIO  | x2   | EBI - ADDR[0]  | SPI1 - MISO       | PM - GCLK[0]        |   |

| C2  | 38  |                    | PX35 | 86     | VDDIO  | x2   | EBI - DATA[15] | SPI1 - MOSI       | PM - GCLK[1]        |   |

| D3  | 44  |                    | PX36 | 87     | VDDIO  | x2   | EBI - DATA[14] | SPI1 - SPCK       | PM - GCLK[2]        |   |

| D2  | 45  |                    | PX37 | 88     | VDDIO  | x2   | EBI - DATA[13] | SPI1 - NPCS[0]    | PM - GCLK[3]        |   |

| E1  | 51  |                    | PX38 | 89     | VDDIO  | x2   | EBI - DATA[12] | SPI1 - NPCS[1]    | USART1 - DCD        |   |

| F1  | 52  |                    | PX39 | 90     | VDDIO  | x2   | EBI - DATA[11] | SPI1 - NPCS[2]    | USART1 - DSR        |   |

| A1  | 36  |                    | PX40 | 91     | VDDIO  | x2   |                | MCI - CLK         |                     |   |

| M2  | 71  |                    | PX41 | 92     | VDDIO  | x2   | EBI - CAS      |                   |                     |   |

| М3  | 69  |                    | PX42 | 93     | VDDIO  | x2   | EBI - RAS      |                   |                     |   |

| L7  | 88  |                    | PX43 | 94     | VDDIO  | x2   | EBI - SDA10    | USART1 - RI       |                     |   |

| К2  | 66  |                    | PX44 | 95     | VDDIO  | x2   | EBI - SDWE     | USART1 - DTR      |                     |   |

| L3  | 70  | J7 <sup>(1)</sup>  | PX45 | 96     | VDDIO  | x3   | EBI - SDCK     |                   |                     |   |

| K4  | 74  | G6 <sup>(1)</sup>  | PX46 | 97     | VDDIO  | x2   | EBI - SDCKE    |                   |                     |   |

| D4  | 39  | E1 <sup>(1)</sup>  | PX47 | 98     | VDDIO  | x2   | EBI - NANDOE   | ADC - TRIGGER     | MCI - DATA[11]      |   |

| F5  | 41  |                    | PX48 | 99     | VDDIO  | x2   | EBI - ADDR[23] | USB - VBOF        | MCI - DATA[10]      |   |

| F4  | 43  |                    | PX49 | 100    | VDDIO  | x2   | EBI - CFRNW    | USB - ID          | MCI - DATA[9]       |   |

| G4  | 75  |                    | PX50 | 101    | VDDIO  | x2   | EBI - CFCE2    | TC1 - B2          | MCI - DATA[8]       |   |

| G5  | 77  |                    | PX51 | 102    | VDDIO  | x2   | EBI - CFCE1    | DMACA - DMAACK[0] | MCI - DATA[15]      |   |

| K7  | 87  |                    | PX52 | 103    | VDDIO  | x2   | EBI - NCS[3]   | DMACA - DMARQ[0]  | MCI - DATA[14]      |   |

| E4  | 42  | D4 <sup>(1)</sup>  | PX53 | 104    | VDDIO  | x2   | EBI - NCS[2]   |                   | MCI - DATA[13]      |   |

| E3  | 46  |                    | PX54 | 105    | VDDIO  | x2   | EBI - NWAIT    | USART3 - TXD      | MCI - DATA[12]      |   |

| J5  | 79  |                    | PX55 | 106    | VDDIO  | x2   | EBI - ADDR[22] | EIC - SCAN[3]     | USART2 - RXD        |   |

# 3.3 Signal Descriptions

The following table gives details on signal name classified by peripheral.

| Signal Name             | Function                                    | Туре            | Active<br>Level | Comments       |  |  |  |  |

|-------------------------|---------------------------------------------|-----------------|-----------------|----------------|--|--|--|--|

| Power                   |                                             |                 |                 |                |  |  |  |  |

| VDDIO                   | I/O Power Supply                            | Power           |                 | 3.0 to 3.6V    |  |  |  |  |

| VDDANA                  | Analog Power Supply                         | Power           |                 | 3.0 to 3.6V    |  |  |  |  |

| VDDIN                   | Voltage Regulator Input Supply              | Power           |                 | 3.0 to 3.6V    |  |  |  |  |

| VDDCORE                 | Voltage Regulator Output for Digital Supply | Power<br>Output |                 | 1.65 to 1.95 V |  |  |  |  |

| GNDANA                  | Analog Ground                               | Ground          |                 |                |  |  |  |  |

| GNDIO                   | I/O Ground                                  | Ground          |                 |                |  |  |  |  |

| GNDCORE                 | Digital Ground                              | Ground          |                 |                |  |  |  |  |

| GNDPLL                  | PLL Ground                                  | Ground          |                 |                |  |  |  |  |

|                         | Clocks, Oscillators                         | , and PLL's     | •               |                |  |  |  |  |

| XIN0, XIN1, XIN32       | Crystal 0, 1, 32 Input                      | Analog          |                 |                |  |  |  |  |

| XOUT0, XOUT1,<br>XOUT32 | Crystal 0, 1, 32 Output                     | Analog          |                 |                |  |  |  |  |

|                         | JTAG                                        |                 |                 |                |  |  |  |  |

| ТСК                     | Test Clock                                  | Input           |                 |                |  |  |  |  |

| TDI                     | Test Data In                                | Input           |                 |                |  |  |  |  |

| TDO                     | Test Data Out                               | Output          |                 |                |  |  |  |  |

| TMS                     | Test Mode Select                            | Input           |                 |                |  |  |  |  |

|                         | Auxiliary Port                              | - AUX           | •               | 1              |  |  |  |  |

| МСКО                    | Trace Data Output Clock                     | Output          |                 |                |  |  |  |  |

| MDO[5:0]                | Trace Data Output                           | Output          |                 |                |  |  |  |  |

| MSEO[1:0]               | Trace Frame Control                         | Output          |                 |                |  |  |  |  |

| EVTI_N                  | Event In                                    | Input           | Low             |                |  |  |  |  |

| EVTO_N                  | Event Out                                   | Output          | Low             |                |  |  |  |  |

|                         | Power Manage                                | r - PM          |                 |                |  |  |  |  |

| GCLK[3:0]               | Generic Clock Pins                          | Output          |                 |                |  |  |  |  |

# Table 3-6.Signal Description List

| Signal Name | Function                               | Туре   | Active<br>Level | Comments                                                                                                                                                                                        |

|-------------|----------------------------------------|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMHS        | USB High Speed Data -                  | Analog |                 |                                                                                                                                                                                                 |

| DPHS        | USB High Speed Data +                  | Analog |                 |                                                                                                                                                                                                 |

| USB_VBIAS   | USB VBIAS reference                    | Analog |                 | Connect to the ground through a<br>6810 ohms (+/- 1%) resistor in<br>parallel with a 10pf capacitor.<br>If USB hi-speed feature is not<br>required, leave this pin<br>unconnected to save power |

| USB_VBUS    | USB VBUS signal                        | Output |                 |                                                                                                                                                                                                 |

| VBOF        | USB VBUS on/off bus power control port | Output |                 |                                                                                                                                                                                                 |

| ID          | ID Pin fo the USB bus                  | Input  |                 |                                                                                                                                                                                                 |

## 3.4 I/O Line Considerations

#### 3.4.1 JTAG Pins

TMS and TDI pins have pull-up resistors. TDO pin is an output, driven at up to VDDIO, and has no pull-up resistor.

#### 3.4.2 RESET\_N Pin

The RESET\_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIO. As the product integrates a power-on reset cell, the RESET\_N pin can be left unconnected in case no reset from the system needs to be applied to the product.

#### 3.4.3 TWI Pins

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation and inputs with inputs with spike filtering. When used as GPIO pins or used for other peripherals, the pins have the same characteristics as other GPIO pins.

### 3.4.4 GPIO Pins

All the I/O lines integrate a programmable pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the I/O Controller. After reset, I/O lines default as inputs with pull-up resistors disabled, except when indicated otherwise in the column "Reset State" of the I/O Controller multiplexing tables.

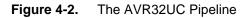

# 4. Processor and Architecture

Rev: 1.4.2.0

This chapter gives an overview of the AVR32UC CPU. AVR32UC is an implementation of the AVR32 architecture. A summary of the programming model, instruction set, and MPU is presented. For further details, see the AVR32 Architecture Manual and the AVR32UC Technical Reference Manual.

## 4.1 Features

- 32-bit load/store AVR32A RISC architecture

- 15 general-purpose 32-bit registers

- 32-bit Stack Pointer, Program Counter and Link Register reside in register file

- Fully orthogonal instruction set

- Privileged and unprivileged modes enabling efficient and secure Operating Systems

- Innovative instruction set together with variable instruction length ensuring industry leading code density

- DSP extention with saturating arithmetic, and a wide variety of multiply instructions

- 3-stage pipeline allows one instruction per clock cycle for most instructions

- Byte, halfword, word and double word memory access

- Multiple interrupt priority levels

- MPU allows for operating systems with memory protection

## 4.2 AVR32 Architecture

AVR32 is a high-performance 32-bit RISC microprocessor architecture, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption and high code density. In addition, the instruction set architecture has been tuned to allow a variety of microarchitectures, enabling the AVR32 to be implemented as low-, mid-, or high-performance processors. AVR32 extends the AVR family into the world of 32- and 64-bit applications.

Through a quantitative approach, a large set of industry recognized benchmarks has been compiled and analyzed to achieve the best code density in its class. In addition to lowering the memory requirements, a compact code size also contributes to the core's low power characteristics. The processor supports byte and halfword data types without penalty in code size and performance.

Memory load and store operations are provided for byte, halfword, word, and double word data with automatic sign- or zero extension of halfword and byte data. The C-compiler is closely linked to the architecture and is able to exploit code optimization features, both for size and speed.

In order to reduce code size to a minimum, some instructions have multiple addressing modes. As an example, instructions with immediates often have a compact format with a smaller immediate, and an extended format with a larger immediate. In this way, the compiler is able to use the format giving the smallest code size.

Another feature of the instruction set is that frequently used instructions, like add, have a compact format with two operands as well as an extended format with three operands. The larger format increases performance, allowing an addition and a data move in the same instruction in a single cycle. Load and store instructions have several different formats in order to reduce code size and speed up execution.

### 4.3.2 AVR32A Microarchitecture Compliance

AVR32UC implements an AVR32A microarchitecture. The AVR32A microarchitecture is targeted at cost-sensitive, lower-end applications like smaller microcontrollers. This microarchitecture does not provide dedicated hardware registers for shadowing of register file registers in interrupt contexts. Additionally, it does not provide hardware registers for the return address registers and return status registers. Instead, all this information is stored on the system stack. This saves chip area at the expense of slower interrupt handling.

Upon interrupt initiation, registers R8-R12 are automatically pushed to the system stack. These registers are pushed regardless of the priority level of the pending interrupt. The return address and status register are also automatically pushed to stack. The interrupt handler can therefore use R8-R12 freely. Upon interrupt completion, the old R8-R12 registers and status register are restored, and execution continues at the return address stored popped from stack.

The stack is also used to store the status register and return address for exceptions and *scall*. Executing the *rete* or *rets* instruction at the completion of an exception or system call will pop this status register and continue execution at the popped return address.

#### 4.3.3 Java Support

AVR32UC does not provide Java hardware acceleration.

## 4.3.4 Memory Protection

The MPU allows the user to check all memory accesses for privilege violations. If an access is attempted to an illegal memory address, the access is aborted and an exception is taken. The MPU in AVR32UC is specified in the AVR32UC Technical Reference manual.

#### 4.3.5 Unaligned Reference Handling

AVR32UC does not support unaligned accesses, except for doubleword accesses. AVR32UC is able to perform word-aligned *st.d* and *ld.d*. Any other unaligned memory access will cause an address exception. Doubleword-sized accesses with word-aligned pointers will automatically be performed as two word-sized accesses.

The following table shows the instructions with support for unaligned addresses. All other instructions require aligned addresses.

**Table 4-1.** Instructions with Unaligned Reference Support

| Instruction | Supported alignment |

|-------------|---------------------|

| ld.d        | Word                |

| st.d        | Word                |

#### 4.3.6 Unimplemented Instructions

The following instructions are unimplemented in AVR32UC, and will cause an Unimplemented Instruction Exception if executed:

- All SIMD instructions

- All coprocessor instructions if no coprocessors are present

- retj, incjosp, popjc, pushjc

- tlbr, tlbs, tlbw

- cache

#### 4.3.7 CPU and Architecture Revision

Three major revisions of the AVR32UC CPU currently exist.

The Architecture Revision field in the CONFIG0 system register identifies which architecture revision is implemented in a specific device.

AVR32UC CPU revision 3 is fully backward-compatible with revisions 1 and 2, ie. code compiled for revision 1 or 2 is binary-compatible with revision 3 CPUs.

|         | System Re | egisters (Continue | 50)                                    |

|---------|-----------|--------------------|----------------------------------------|

| Reg #   | Address   | Name               | Function                               |

| 92      | 368       | MPUPSR4            | MPU Privilege Select Register region 4 |

| 93      | 372       | MPUPSR5            | MPU Privilege Select Register region 5 |

| 94      | 376       | MPUPSR6            | MPU Privilege Select Register region 6 |

| 95      | 380       | MPUPSR7            | MPU Privilege Select Register region 7 |

| 96      | 384       | MPUCRA             | Unused in this version of AVR32UC      |

| 97      | 388       | MPUCRB             | Unused in this version of AVR32UC      |

| 98      | 392       | MPUBRA             | Unused in this version of AVR32UC      |

| 99      | 396       | MPUBRB             | Unused in this version of AVR32UC      |

| 100     | 400       | MPUAPRA            | MPU Access Permission Register A       |

| 101     | 404       | MPUAPRB            | MPU Access Permission Register B       |

| 102     | 408       | MPUCR              | MPU Control Register                   |

| 103-191 | 448-764   | Reserved           | Reserved for future use                |

| 192-255 | 768-1020  | IMPL               | IMPLEMENTATION DEFINED                 |

Table 4-3.

System Registers (Continued)

## 4.5 Exceptions and Interrupts

AVR32UC incorporates a powerful exception handling scheme. The different exception sources, like Illegal Op-code and external interrupt requests, have different priority levels, ensuring a well-defined behavior when multiple exceptions are received simultaneously. Additionally, pending exceptions of a higher priority class may preempt handling of ongoing exceptions of a lower priority class.

When an event occurs, the execution of the instruction stream is halted, and execution control is passed to an event handler at an address specified in Table 4-4 on page 33. Most of the handlers are placed sequentially in the code space starting at the address specified by EVBA, with four bytes between each handler. This gives ample space for a jump instruction to be placed there, jumping to the event routine itself. A few critical handlers have larger spacing between them, allowing the entire event routine to be placed directly at the address specified by the EVBA-relative offset generated by hardware. All external interrupt sources have autovectored interrupt service routine (ISR) addresses. This allows the interrupt controller to directly specify the ISR address as an address relative to EVBA. The autovector offset has 14 address bits, giving an offset of maximum 16384 bytes. The target address of the event handler is calculated as (EVBA | event\_handler\_offset), not (EVBA + event\_handler\_offset), so EVBA and exception code segments must be set up appropriately. The same mechanisms are used to service all different types of events, including external interrupt requests, yielding a uniform event handling scheme.

An interrupt controller does the priority handling of the external interrupts and provides the autovector offset to the CPU.

## 4.5.1 System Stack Issues

Event handling in AVR32UC uses the system stack pointed to by the system stack pointer, SP\_SYS, for pushing and popping R8-R12, LR, status register, and return address. Since event code may be timing-critical, SP\_SYS should point to memory addresses in the IRAM section, since the timing of accesses to this memory section is both fast and deterministic.

# AT32UC3A3

| Priority | Handler Address        | Name                        | Event source   | Stored Return Address           |

|----------|------------------------|-----------------------------|----------------|---------------------------------|

| 1        | 0x8000_0000            | Reset                       | External input | Undefined                       |

| 2        | Provided by OCD system | OCD Stop CPU                | OCD system     | First non-completed instruction |

| 3        | EVBA+0x00              | Unrecoverable exception     | Internal       | PC of offending instruction     |

| 4        | EVBA+0x04              | TLB multiple hit            | MPU            |                                 |

| 5        | EVBA+0x08              | Bus error data fetch        | Data bus       | First non-completed instruction |

| 6        | EVBA+0x0C              | Bus error instruction fetch | Data bus       | First non-completed instruction |

| 7        | EVBA+0x10              | NMI                         | External input | First non-completed instruction |

| 8        | Autovectored           | Interrupt 3 request         | External input | First non-completed instruction |

| 9        | Autovectored           | Interrupt 2 request         | External input | First non-completed instruction |

| 10       | Autovectored           | Interrupt 1 request         | External input | First non-completed instruction |

| 11       | Autovectored           | Interrupt 0 request         | External input | First non-completed instruction |

| 12       | EVBA+0x14              | Instruction Address         | CPU            | PC of offending instruction     |

| 13       | EVBA+0x50              | ITLB Miss                   | MPU            |                                 |

| 14       | EVBA+0x18              | ITLB Protection             | MPU            | PC of offending instruction     |

| 15       | EVBA+0x1C              | Breakpoint                  | OCD system     | First non-completed instruction |

| 16       | EVBA+0x20              | Illegal Opcode              | Instruction    | PC of offending instruction     |

| 17       | EVBA+0x24              | Unimplemented instruction   | Instruction    | PC of offending instruction     |

| 18       | EVBA+0x28              | Privilege violation         | Instruction    | PC of offending instruction     |

| 19       | EVBA+0x2C              | Floating-point              | UNUSED         |                                 |

| 20       | EVBA+0x30              | Coprocessor absent          | Instruction    | PC of offending instruction     |

| 21       | EVBA+0x100             | Supervisor call             | Instruction    | PC(Supervisor Call) +2          |

| 22       | EVBA+0x34              | Data Address (Read)         | CPU            | PC of offending instruction     |

| 23       | EVBA+0x38              | Data Address (Write)        | CPU            | PC of offending instruction     |

| 24       | EVBA+0x60              | DTLB Miss (Read)            | MPU            |                                 |

| 25       | EVBA+0x70              | DTLB Miss (Write)           | MPU            |                                 |

| 26       | EVBA+0x3C              | DTLB Protection (Read)      | MPU            | PC of offending instruction     |

| 27       | EVBA+0x40              | DTLB Protection (Write)     | MPU            | PC of offending instruction     |

| 28       | EVBA+0x44              | DTLB Modified               | UNUSED         |                                 |

# Table 4-4. Priority and Handler Addresses for Events

# 5. Memories

# 5.1 Embedded Memories

## • Internal High-Speed Flash

- 256KBytes (AT32UC3A3256/S)

- 128Kbytes (AT32UC3A3128/S)

- 64 Kbytes (AT32UC3A364/S)

- 0 wait state access at up to 42MHz in worst case conditions

- 1 wait state access at up to 84MHz in worst case conditions

- Pipelined Flash architecture, allowing burst reads from sequential Flash locations, hiding penalty of 1 wait state access

- Pipelined Flash architecture typically reduces the cycle penalty of 1 wait state operation to only 15% compared to 0 wait state operation

- 100 000 write cycles, 15-year data retention capability

- Sector lock capabilities, Bootloader protection, Security Bit

- 32 Fuses, Erased During Chip Erase

- User page for data to be preserved during Chip Erase

- Internal High-Speed SRAM

- 64KBytes, Single-cycle access at full speed on CPU Local Bus and accessible through the High Speed Bud (HSB) matrix

- 2x32 KBytes, accessible independently through the High Speed Bud (HSB) matrix

# 5.2 Physical Memory Map

The System Bus is implemented as a bus matrix. All system bus addresses are fixed, and they are never remapped in any way, not even in boot.

Note that AVR32 UC CPU uses unsegmented translation, as described in the AVR32UC Technical Architecture Manual.

The 32-bit physical address space is mapped as follows:

|                            |                  | Size                                                           | Size                                                           | Size                                                       |

|----------------------------|------------------|----------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------|

| Device                     | Start<br>Address | AT32UC3A3256S<br>AT32UC3A3256<br>AT32UC3A4256S<br>AT32UC3A4256 | AT32UC3A3128S<br>AT32UC3A3128<br>AT32UC3A4128S<br>AT32UC3A4128 | AT32UC3A364S<br>AT32UC3A364<br>AT32UC3A464S<br>AT32UC3A464 |

| Embedded CPU SRAM          | 0x00000000       | 64KByte                                                        | 64KByte                                                        | 64KByte                                                    |

| Embedded Flash             | 0x80000000       | 256KByte                                                       | 128KByte                                                       | 64KByte                                                    |

| EBI SRAM CS0               | 0xC0000000       | 16MByte                                                        | 16MByte                                                        | 16MByte                                                    |

| EBI SRAM CS2               | 0xC8000000       | 16MByte                                                        | 16MByte                                                        | 16MByte                                                    |

| EBI SRAM CS3               | 0xCC000000       | 16MByte                                                        | 16MByte                                                        | 16MByte                                                    |

| EBI SRAM CS4               | 0xD8000000       | 16MByte                                                        | 16MByte                                                        | 16MByte                                                    |

| EBI SRAM CS5               | 0xDC000000       | 16MByte                                                        | 16MByte                                                        | 16MByte                                                    |

| EBI SRAM CS1<br>/SDRAM CS0 | 0xD0000000       | 128MByte                                                       | 128MByte                                                       | 128MByte                                                   |

| USB Data                   | 0xE0000000       | 64KByte                                                        | 64KByte                                                        | 64KByte                                                    |

Table 5-1.AT32UC3A3A4 Physical Memory Map

# AT32UC3A3

|                 |                  | Size                                                            | Size                                                            | Size                                                       |

|-----------------|------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------|

| Device          | Start<br>Address | AT32UC3A3256S<br>AT32UC3A3256<br>AT32UC3A4256S<br>AT32UC3A4256S | AT32UC3A3128S<br>AT32UC3A3128<br>AT32UC3A4128S<br>AT32UC3A4128S | AT32UC3A364S<br>AT32UC3A364<br>AT32UC3A464S<br>AT32UC3A464 |

| HRAMC0          | 0xFF000000       | 32KByte                                                         | 32KByte                                                         | 32KByte                                                    |

| HRAMC1          | 0xFF008000       | 32KByte                                                         | 32KByte                                                         | 32KByte                                                    |

| HSB-PB Bridge A | 0xFFFF0000       | 64KByte                                                         | 64KByte                                                         | 64KByte                                                    |

| HSB-PB Bridge B | 0xFFFE0000       | 64KByte                                                         | 64KByte                                                         | 64KByte                                                    |

Table 5-1.

AT32UC3A3A4 Physical Memory Map

# 5.3 Peripheral Address Map

# Table 5-2. Peripheral Address Mapping

| Address    |         | Peripheral Name                                           |

|------------|---------|-----------------------------------------------------------|

| 0xFF100000 | DMACA   | DMA Controller - DMACA                                    |

| 0xFFFD0000 | AES     | Advanced Encryption Standard - AES                        |

| 0xFFFE0000 | USB     | USB 2.0 Device and Host Interface - USB                   |

| 0xFFFE1000 | HMATRIX | HSB Matrix - HMATRIX                                      |

| 0xFFFE1400 | FLASHC  | Flash Controller - FLASHC                                 |

| 0xFFFE1C00 | SMC     | Static Memory Controller - SMC                            |

| 0xFFFE2000 | SDRAMC  | SDRAM Controller - SDRAMC                                 |

| 0xFFFE2400 | ECCHRS  | Error code corrector Hamming and Reed Solomon -<br>ECCHRS |

| 0xFFFE2800 | BUSMON  | Bus Monitor module - BUSMON                               |

| 0xFFFE4000 | MCI     | Mulitmedia Card Interface - MCI                           |

| 0xFFFE8000 | MSI     | Memory Stick Interface - MSI                              |

| 0xFFFF0000 | PDCA    | Peripheral DMA Controller - PDCA                          |

| 0xFFFF0800 | INTC    | Interrupt controller - INTC                               |

Table 5-2.

Peripheral Address Mapping

| 0xFFFF5000 | TWIS0 | Two-wire Slave Interface - TWIS0 |

|------------|-------|----------------------------------|

| 0xFFFF5400 | TWIS1 | Two-wire Slave Interface - TWIS1 |

## 5.4 CPU Local Bus Mapping

Some of the registers in the GPIO module are mapped onto the CPU local bus, in addition to being mapped on the Peripheral Bus. These registers can therefore be reached both by accesses on the Peripheral Bus, and by accesses on the local bus.

Mapping these registers on the local bus allows cycle-deterministic toggling of GPIO pins since the CPU and GPIO are the only modules connected to this bus. Also, since the local bus runs at CPU speed, one write or read operation can be performed per clock cycle to the local busmapped GPIO registers.

The following GPIO registers are mapped on the local bus:

Table 5-3.

Local Bus Mapped GPIO Registers

| Port | Register                             | Mode   | Local Bus<br>Address | Access     |

|------|--------------------------------------|--------|----------------------|------------|

| 0    | Output Driver Enable Register (ODER) | WRITE  | 0x40000040           | Write-only |

|      |                                      | SET    | 0x40000044           | Write-only |

|      |                                      | CLEAR  | 0x40000048           | Write-only |

|      |                                      | TOGGLE | 0x4000004C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000050           | Write-only |

|      |                                      | SET    | 0x40000054           | Write-only |

|      |                                      | CLEAR  | 0x40000058           | Write-only |

|      |                                      | TOGGLE | 0x4000005C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000060           | Read-only  |

| 1    | Output Driver Enable Register (ODER) | WRITE  | 0x40000140           | Write-only |

|      |                                      | SET    | 0x40000144           | Write-only |

|      |                                      | CLEAR  | 0x40000148           | Write-only |

|      |                                      | TOGGLE | 0x4000014C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000150           | Write-only |

|      |                                      | SET    | 0x40000154           | Write-only |

|      |                                      | CLEAR  | 0x40000158           | Write-only |

|      |                                      | TOGGLE | 0x4000015C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000160           | Read-only  |

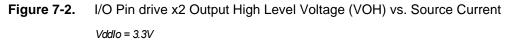

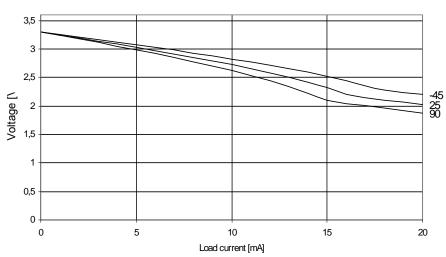

## 7.2.1 I/O Pin Output Level Typical Characteristics

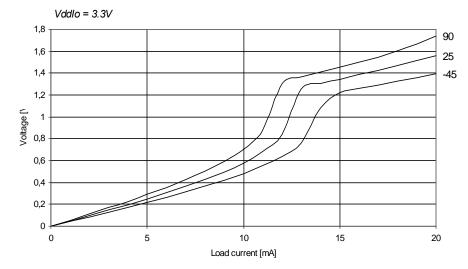

Figure 7-1.I/O Pin drive x2 Output Low Level Voltage (VOL) vs. Source Current

# 7.3 I/O pin Characteristics

These parameters are given in the following conditions:

- V<sub>DDCORE</sub> = 1.8V

- V<sub>DDIO</sub> = 3.3V

- Ambient Temperature = 25°C

# Table 7-9.BOD Timing

| Symbol           | Parameter                                                | Conditions                        | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------------------------|-----------------------------------|------|------|------|------|

| T <sub>BOD</sub> | Minimum time with VDDCORE < VBOD to detect power failure | Falling VDDCORE from 1.8V to 1.1V |      | 300  | 800  | ns   |

# 7.5.3 Reset Sequence

## Table 7-10. Electrical Characteristics

| Symbol               | Parameter                                                                                                                                          | Conditions                                              | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|------|------|------|

| V <sub>DDRR</sub>    | VDDIN/VDDIO rise rate to ensure<br>power-on-reset                                                                                                  |                                                         | 0.8  |      |      | V/ms |

| V <sub>POR+</sub>    | Rising threshold voltage: voltage up<br>to which device is kept under reset by<br>POR on rising VDDIN                                              | Rising VDDIN: V <sub>RESTART</sub> -> V <sub>POR+</sub> |      | 2.7  |      | V    |

| V <sub>POR-</sub>    | Falling threshold voltage: voltage<br>when POR resets device on falling<br>VDDIN                                                                   | Falling VDDIN: 3.3V -> V <sub>POR-</sub>                |      | 2.7  |      | V    |

| V <sub>RESTART</sub> | On falling VDDIN, voltage must go<br>down to this value before supply can<br>rise again to ensure reset signal is<br>released at V <sub>POR+</sub> | Falling VDDIN: 3.3V -> V <sub>RESTART</sub>             |      |      | 0.2  | V    |

| T <sub>SSU1</sub>    | Time for Cold System Startup: Time<br>for CPU to fetch its first instruction<br>(RCosc not calibrated)                                             |                                                         | 480  |      | 960  | μs   |

| T <sub>SSU2</sub>    | Time for Hot System Startup: Time for<br>CPU to fetch its first instruction<br>(RCosc calibrated)                                                  |                                                         |      | 420  |      | μs   |

# 7.5.4 RESET\_N Characteristics

# Table 7-11. RESET\_N Waveform Parameters

| Symbol             | Parameter                   | Conditions | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------|------------|------|------|------|------|

| t <sub>RESET</sub> | RESET_N minimum pulse width |            | 10   |      |      | ns   |

# 7.7 System Clock Characteristics

These parameters are given in the following conditions:

• V<sub>DDCORE</sub> = 1.8V

## 7.7.1 CPU/HSB Clock Characteristics

Table 7-14.

Core Clock Waveform Parameters

| Symbol                  | Parameter           | Conditions                         | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------------------------------|------|------|------|------|

| 1/(t <sub>CPCPU</sub> ) | CPU Clock Frequency | -40°C < Ambient Temperature < 70°C |      |      | 84   | MHz  |

| 1/(t <sub>CPCPU</sub> ) | CPU Clock Frequency | -40°C < Ambient Temperature < 85°C |      |      | 66   | MHz  |

## 7.7.2 PBA Clock Characteristics

| TADIE 1-13. FDA CIUCK WAVEIUIIII FAIAIIIEIEIS | Table 7-15. | PBA Clock Waveform Parameters |

|-----------------------------------------------|-------------|-------------------------------|

|-----------------------------------------------|-------------|-------------------------------|

| Symbol                  | Parameter           | Conditions                         | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------------------------------|------|------|------|------|

| 1/(t <sub>CPPBA</sub> ) | PBA Clock Frequency | -40°C < Ambient Temperature < 70°C |      |      | 84   | MHz  |

| 1/(t <sub>CPPBA</sub> ) | PBA Clock Frequency | -40°C < Ambient Temperature < 85°C |      |      | 66   | MHz  |

## 7.7.3 PBB Clock Characteristics

## Table 7-16. PBB Clock Waveform Parameters

| Symbol                  | Parameter           | Conditions                         | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------------------------------|------|------|------|------|

| 1/(t <sub>CPPBB</sub> ) | PBB Clock Frequency | -40°C < Ambient Temperature < 70°C |      |      | 84   | MHz  |

| 1/(t <sub>CPPBB</sub> ) | PBB Clock Frequency | -40°C < Ambient Temperature < 85°C |      |      | 66   | MHz  |

## 7.8.3 Main Oscillators

| Table 7-19. Main Oscillators Characteristic | cs |

|---------------------------------------------|----|

|---------------------------------------------|----|

| Symbol                   | Parameter                                       | Conditions                                                                                                                                   | Min.                | Тур.                  | Max.                | Unit |

|--------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|---------------------|------|

|                          |                                                 | External clock on XIN                                                                                                                        |                     |                       | 50                  | MHz  |

| 1/(t <sub>CPMAIN</sub> ) | Oscillator Frequency                            | Crystal                                                                                                                                      | 0.4                 |                       | 20                  | MHz  |

| $C_{L1}, C_{L2}$         | Internal Load Capacitance ( $C_{L1} = C_{L2}$ ) |                                                                                                                                              |                     | 7                     |                     | pF   |

| ESR                      | Crystal Equivalent Series Resistance            |                                                                                                                                              |                     |                       | 75                  | Ω    |

|                          | Duty Cycle                                      |                                                                                                                                              | 40                  | 50                    | 60                  | %    |

| t <sub>ST</sub>          | Startup Time                                    | f = 400 KHz<br>f = 8 MHz<br>f = 16 MHz<br>f = 20 MHz                                                                                         |                     | 25<br>4<br>1.4<br>1   |                     | ms   |

| t <sub>CH</sub>          | XIN Clock High Half-period                      |                                                                                                                                              | 0.4 t <sub>CP</sub> |                       | 0.6 t <sub>CP</sub> |      |

| t <sub>CL</sub>          | XIN Clock Low Half-period                       |                                                                                                                                              | 0.4 t <sub>CP</sub> |                       | 0.6 t <sub>CP</sub> |      |

| C <sub>IN</sub>          | XIN Input Capacitance                           |                                                                                                                                              |                     | 7                     |                     | pF   |

| I <sub>osc</sub>         | Current Consumption                             | Active mode at 400 KHz. Gain = G0<br>Active mode at 8 MHz. Gain = G1<br>Active mode at 16 MHz. Gain = G2<br>Active mode at 20 MHz. Gain = G3 |                     | 30<br>45<br>95<br>205 |                     | μA   |

# 7.8.4 Phase Lock Loop (PLL0, PLL1)

## Table 7-20. PLL Characteristics

| Symbol                               | Parameter                             | Conditions                 | Min. | Тур. | Max. | Unit |

|--------------------------------------|---------------------------------------|----------------------------|------|------|------|------|

| F <sub>OUT</sub>                     | VCO Output Frequency                  |                            | 80   |      | 240  | MHz  |

| F <sub>IN</sub>                      | Input Frequency (after input divider) |                            | 4    |      | 16   | MHz  |

| I <sub>PLL</sub> Current Consumption | Active mode (Fout=80 MHz)             |                            | 250  |      | μA   |      |

|                                      | Current Consumption                   | Active mode (Fout=240 MHz) |      | 600  |      | μA   |

# 7.8.5 USB Hi-Speed Phase Lock Loop

## Table 7-21. PLL Characteristics

| Symbol                | Parameter                                                                                 | Conditions                | Min. | Тур. | Max. | Unit |

|-----------------------|-------------------------------------------------------------------------------------------|---------------------------|------|------|------|------|

| F <sub>OUT</sub>      | VCO Output Frequency                                                                      |                           |      | 480  |      | MHz  |

| F <sub>IN</sub>       | Input Frequency                                                                           |                           |      | 12   |      | MHz  |

| Delta F <sub>IN</sub> | Input Frequency Accuracy (applicable<br>to Clock signal on XIN or to Quartz<br>tolerance) |                           | -500 |      | +500 | ppm  |

| I <sub>PLL</sub>      | Current Consumption                                                                       | Active mode @480MHz @1.8V |      | 2.5  |      | mA   |

## Table 7-38. SPI Timings

| Symbol            | Parameter                                            | Conditions <sup>(1)</sup> | Min.                                           | Max. | Unit |

|-------------------|------------------------------------------------------|---------------------------|------------------------------------------------|------|------|

| SPI <sub>0</sub>  | MISO Setup time before SPCK rises (master)           | 3.3V domain               | 22 +<br>(t <sub>СРМСК</sub> )/2 <sup>(2)</sup> |      | ns   |

| SPI1              | MISO Hold time after SPCK rises (master)             | 3.3V domain               | 0                                              |      | ns   |

| SPI <sub>2</sub>  | SPCK rising to MOSI Delay (master)                   | 3.3V domain               |                                                | 7    | ns   |

| SPI <sub>3</sub>  | MISO Setup time before SPCK <u>falls</u><br>(master) | 3.3V domain               | 22 +<br>(t <sub>CPMCK</sub> )/2 <sup>(3)</sup> |      | ns   |

| SPI <sub>4</sub>  | MISO Hold time after SPCK falls (master)             | 3.3V domain               | 0                                              |      | ns   |

| SPI <sub>5</sub>  | SPCK falling to MOSI Delay master)                   | 3.3V domain               |                                                | 7    | ns   |

| SPI <sub>6</sub>  | SPCK falling to MISO Delay (slave)                   | 3.3V domain               |                                                | 26.5 | ns   |

| SPI7              | MOSI Setup time before SPCK rises (slave)            | 3.3V domain               | 0                                              |      | ns   |

| SPI <sub>8</sub>  | MOSI Hold time after SPCK rises (slave)              | 3.3V domain               | 1.5                                            |      | ns   |

| SPI <sub>9</sub>  | SPCK rising to MISO Delay (slave)                    | 3.3V domain               |                                                | 27   | ns   |

| SPI <sub>10</sub> | MOSI Setup time before SPCK falls (slave)            | 3.3V domain               | 0                                              |      | ns   |

| SPI <sub>11</sub> | MOSI Hold time after SPCK falls (slave)              | 3.3V domain               | 1                                              |      | ns   |

1. 3.3V domain:  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 40 pF

2. t<sub>CPMCK</sub>: Master Clock period in ns.

3. t<sub>CPMCK</sub>: Master Clock period in ns.

# 7.14 MCI

The High Speed MultiMedia Card Interface (MCI) sup<u>por</u>ts the MultiMedia Card (MMC) Specification V4.2, the SD Memory Card Specification V2.0, the SDIO V1.1 specification and CE-ATA V1.1.

# 8.3 Soldering Profile

Table 8-5 gives the recommended soldering profile from J-STD-20.

| Table 8-5. | Soldering Profile |

|------------|-------------------|

|------------|-------------------|

| Profile Feature                            | Green Package   |

|--------------------------------------------|-----------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/Second max  |

| Preheat Temperature 175°C ±25°C            | 150-200°C       |

| Time Maintained Above 217°C                | 60-150 seconds  |

| Time within 5°C of Actual Peak Temperature | 30 seconds      |

| Peak Temperature Range                     | 260 (+0/-5°C)   |

| Ramp-down Rate                             | 6°C/Second max. |

| Time 25°C to Peak Temperature              | 8 minutes max   |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

#### Fix/Workaround

Set to 1b bit CORRS4 of the ECCHRS mode register (MD). In C-code: \*((volatile int\*) (0xFFFE2404))= 0x400.

DMACA data transfer fails when CTLx.SRC\_TR\_WIDTH is not equal to CTLx.DST\_TR\_WIDTH Fix/Workaround For any DMACA transfer make sure CTLx.SRC\_TR\_WIDTH = CTLx.DST\_TR\_WIDTH.

#### 3.3V supply monitor is not available

FGPFRLO[30:29] are reserved and should not be used by the application. **Fix/Workaround** None.

Service access bus (SAB) can not access DMACA registers Fix/Workaround None.

## 10.2.2 Processor and Architecture

#### LDM instruction with PC in the register list and without ++ increments Rp

For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12. **Fix/Workaround**

None.

#### Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

#### Fix/Workaround

Place breakpoints on earlier or later instructions.

#### When the main clock is RCSYS, TIMER\_CLOCK5 is equal to PBA clock

When the main clock is generated from RCSYS, TIMER\_CLOCK5 is equal to PBA Clock and not PBA Clock / 128.

#### Fix/Workaround None.

10.2.3 MPU

# Privilege violation when using interrupts in application mode with protected system stack

If the system stack is protected by the MPU and an interrupt occurs in application mode, an MPU DTLB exception will occur.

#### Fix/Workaround

Make a DTLB Protection (Write) exception handler which permits the interrupt request to be handled in privileged mode.

#### 10.2.4 USB

#### UPCFGn.INTFRQ is irrelevant for isochronous pipe

As a consequence, isochronous IN and OUT tokens are sent every 1ms (Full Speed), or every 125uS (High Speed).