Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | AVR                                                                          |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 66MHz                                                                        |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                        |

| Number of I/O              | 110                                                                          |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.75V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 144-TFBGA                                                                    |

| Supplier Device Package    | 144-FFBGA (11x11)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a3128s-ctut |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

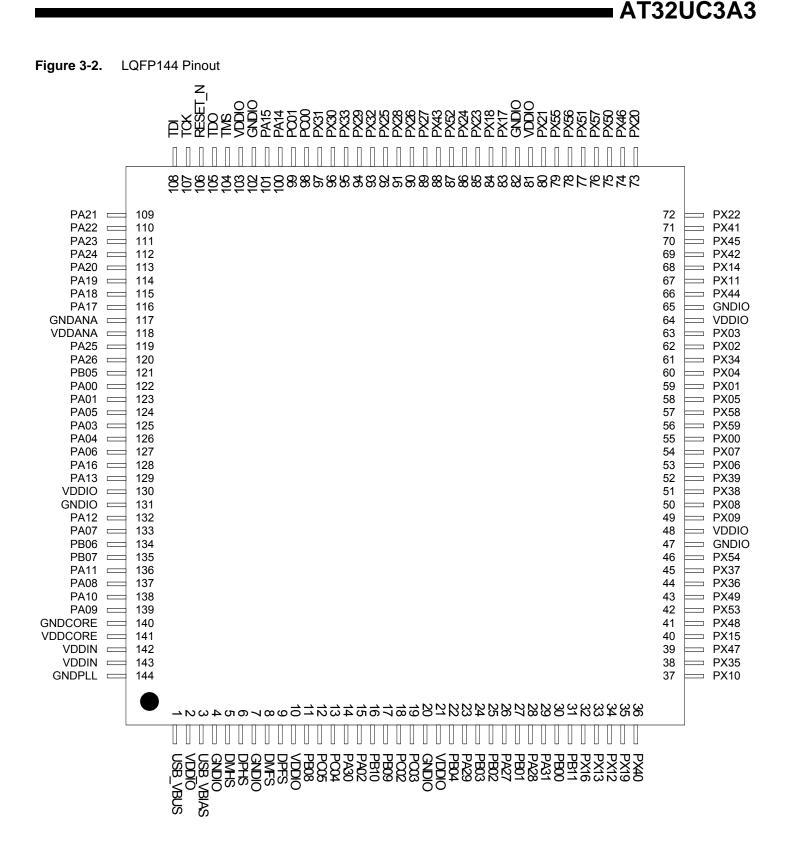

# 3.2 Peripheral Multiplexing on I/O lines

# 3.2.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following table describes the peripheral signals multiplexed to the GPIO lines.

Note that GPIO 44 is physically implemented in silicon but it must be kept unused and configured in input mode.

|            |            |                     |      | G       |        |             | GPIO function  |                     |                  |               |  |

|------------|------------|---------------------|------|---------|--------|-------------|----------------|---------------------|------------------|---------------|--|

|            |            |                     |      | P       |        | PIN         |                |                     |                  |               |  |

| BGA<br>144 | QFP<br>144 | BGA<br>100          | PIN  | <br>  0 | Supply | Type<br>(2) | А              | В                   | С                | D             |  |

|            |            |                     |      | -       |        |             |                |                     | -                | 0             |  |

| G11        | 122        | G8 <sup>(1)</sup>   | PA00 | 0       | VDDIO  | x3          | USART0 - RTS   | TC0 - CLK1          | SPI1 - NPCS[3]   |               |  |

| G12        | 123        | G10 <sup>(1)</sup>  | PA01 | 1       | VDDIO  | x1          | USART0 - CTS   | TC0 - A1            | USART2 - RTS     |               |  |

| D8         | 15         | E1 <sup>(1)</sup>   | PA02 | 2       | VDDIO  | x1          | USART0 - CLK   | TC0 - B1            | SPI0 - NPCS[0]   |               |  |

| G10        | 125        | F9                  | PA03 | 3       | VDDIO  | x1          | USART0 - RXD   | EIC - EXTINT[4]     | ABDAC - DATA[0]  |               |  |

| F9         | 126        | E9                  | PA04 | 4       | VDDIO  | x1          | USART0 - TXD   | EIC - EXTINT[5]     | ABDAC - DATAN[0] |               |  |

| F10        | 124        | G9                  | PA05 | 5       | VDDIO  | x1          | USART1 - RXD   | TC1 - CLK0          | USB - ID         |               |  |

| F8         | 127        | E8 <sup>(1)</sup>   | PA06 | 6       | VDDIO  | x1          | USART1 - TXD   | TC1 - CLK1          | USB - VBOF       |               |  |

| E10        | 133        | H10 <sup>(1)</sup>  | PA07 | 7       | VDDIO  | x1          | SPI0 - NPCS[3] | ABDAC - DATAN[0]    | USART1 - CLK     |               |  |

| C11        | 137        | F8                  | PA08 | 8       | VDDIO  | x3          | SPI0 - SPCK    | ABDAC - DATA[0]     | TC1 - B1         |               |  |

| B12        | 139        | D8                  | PA09 | 9       | VDDIO  | x2          | SPI0 - NPCS[0] | EIC - EXTINT[6]     | TC1 - A1         |               |  |

| C12        | 138        | C10                 | PA10 | 10      | VDDIO  | x2          | SPI0 - MOSI    | USB - VBOF          | TC1 - B0         |               |  |

| D10        | 136        | C9                  | PA11 | 11      | VDDIO  | x2          | SPI0 - MISO    | USB - ID            | TC1 - A2         |               |  |

| E12        | 132        | G7 <sup>(1)</sup>   | PA12 | 12      | VDDIO  | x1          | USART1 - CTS   | SPIO - NPCS[2]      | TC1 - A0         |               |  |

| F11        | 129        | E8 <sup>(1)</sup>   | PA13 | 13      | VDDIO  | x1          | USART1 - RTS   | SPIO - NPCS[1]      | EIC - EXTINT[7]  |               |  |

| J6         | 100        | K7 <sup>(1)</sup>   | PA14 | 14      | VDDIO  | x1          | SPI0 - NPCS[1] | TWIMS0 - TWALM      | TWIMS1 - TWCK    |               |  |

| J7         | 101        | J7 <sup>(1)</sup>   | PA15 | 15      | VDDIO  | x1          | MCI - CMD[1]   | SPI1 - SPCK         | TWIMS1 - TWD     |               |  |

| F12        | 128        | E7                  | PA16 | 16      | VDDIO  | x1          | MCI - DATA[11] | SPI1 - MOSI         | TC1 - CLK2       |               |  |

| H7         | 116        | G10 <sup>(1)</sup>  | PA17 | 17      | VDDANA | x1          | MCI - DATA[10] | SPI1 - NPCS[1]      | ADC - AD[7]      |               |  |

| K8         | 115        | G8 <sup>(1)</sup>   | PA18 | 18      | VDDANA | x1          | MCI - DATA[9]  | SPI1 - NPCS[2]      | ADC - AD[6]      |               |  |

| J8         | 114        | H10 <sup>(1)</sup>  | PA19 | 19      | VDDANA | x1          | MCI - DATA[8]  | SPI1 - MISO         | ADC - AD[5]      |               |  |

| J9         | 113        | H9 <sup>(1)</sup>   | PA20 | 20      | VDDANA | x1          | EIC - NMI      | SSC - RX_FRAME_SYNC | ADC - AD[4]      |               |  |

| H9         | 109        | K10 <sup>(1)</sup>  | PA21 | 21      | VDDANA | x1          | ADC - AD[0]    | EIC - EXTINT[0]     | USB - ID         |               |  |

| H10        | 110        | H6 <sup>(1)</sup>   | PA22 | 22      | VDDANA | x1          | ADC - AD[1]    | EIC - EXTINT[1]     | USB - VBOF       |               |  |

| G8         | 111        | G6 <sup>(1)</sup>   | PA23 | 23      | VDDANA | x1          | ADC - AD[2]    | EIC - EXTINT[2]     | ABDAC - DATA[1]  |               |  |

| G9         | 112        | J10 <sup>(1)</sup>  | PA24 | 24      | VDDANA | x1          | ADC - AD[3]    | EIC - EXTINT[3]     | ABDAC - DATAN[1] |               |  |

| E9         | 119        | G7 <sup>(1)</sup>   | PA25 | 25      | VDDIO  | x1          | TWIMS0 - TWD   | TWIMS1 - TWALM      | USART1 - DCD     |               |  |

| D9         | 120        | F7 <sup>(1)</sup> ) | PA26 | 26      | VDDIO  | x1          | TWIMS0 - TWCK  | USART2 - CTS        | USART1 - DSR     |               |  |

| A4         | 26         | A2                  | PA27 | 27      | VDDIO  | x2          | MCI - CLK      | SSC - RX_DATA       | USART3 - RTS     | MSI - SCLK    |  |

| A3         | 28         | A1                  | PA28 | 28      | VDDIO  | x1          | MCI - CMD[0]   | SSC - RX_CLOCK      | USART3 - CTS     | MSI - BS      |  |

| A6         | 23         | B4                  | PA29 | 29      | VDDIO  | x1          | MCI - DATA[0]  | USART3 - TXD        | TC0 - CLK0       | MSI - DATA[0] |  |

Table 3-1.

GPIO Controller Function Multiplexing

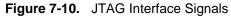

#### 3.2.4 JTAG port connections

| TFBGA144 | QFP144 | VFBGA100 | Pin name | JTAG pin |

|----------|--------|----------|----------|----------|

| K12      | 107    | K9       | тск      | ТСК      |

| L12      | 108    | K8       | TDI      | TDI      |

| J11      | 105    | J8       | TDO      | TDO      |

| J10      | 104    | H7       | TMS      | TMS      |

#### 3.2.5 Nexus OCD AUX port connections

If the OCD trace system is enabled, the trace system will take control over a number of pins, irrespective of the GPIO configuration. Three differents OCD trace pin mappings are possible, depending on the configuration of the OCD AXS register. For details, see the AVR32 UC Technical Reference Manual.

Table 3-5.

Nexus OCD AUX port connections

| Pin     | AXS=0 | AXS=1 | AXS=2 |

|---------|-------|-------|-------|

| EVTI_N  | PB05  | PA08  | PX00  |

| MDO[5]  | PA00  | PX56  | PX06  |

| MDO[4]  | PA01  | PX57  | PX05  |

| MDO[3]  | PA03  | PX58  | PX04  |

| MDO[2]  | PA16  | PA24  | PX03  |

| MDO[1]  | PA13  | PA23  | PX02  |

| MDO[0]  | PA12  | PA22  | PX01  |

| MSEO[1] | PA10  | PA07  | PX08  |

| MSEO[0] | PA11  | PX55  | PX07  |

| МСКО    | PB07  | PX00  | PB09  |

| EVTO_N  | PB06  | PB06  | PB06  |

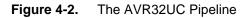

#### 4.3.2 AVR32A Microarchitecture Compliance

AVR32UC implements an AVR32A microarchitecture. The AVR32A microarchitecture is targeted at cost-sensitive, lower-end applications like smaller microcontrollers. This microarchitecture does not provide dedicated hardware registers for shadowing of register file registers in interrupt contexts. Additionally, it does not provide hardware registers for the return address registers and return status registers. Instead, all this information is stored on the system stack. This saves chip area at the expense of slower interrupt handling.

Upon interrupt initiation, registers R8-R12 are automatically pushed to the system stack. These registers are pushed regardless of the priority level of the pending interrupt. The return address and status register are also automatically pushed to stack. The interrupt handler can therefore use R8-R12 freely. Upon interrupt completion, the old R8-R12 registers and status register are restored, and execution continues at the return address stored popped from stack.

The stack is also used to store the status register and return address for exceptions and *scall*. Executing the *rete* or *rets* instruction at the completion of an exception or system call will pop this status register and continue execution at the popped return address.

#### 4.3.3 Java Support

AVR32UC does not provide Java hardware acceleration.

#### 4.3.4 Memory Protection

The MPU allows the user to check all memory accesses for privilege violations. If an access is attempted to an illegal memory address, the access is aborted and an exception is taken. The MPU in AVR32UC is specified in the AVR32UC Technical Reference manual.

#### 4.3.5 Unaligned Reference Handling

AVR32UC does not support unaligned accesses, except for doubleword accesses. AVR32UC is able to perform word-aligned *st.d* and *ld.d*. Any other unaligned memory access will cause an address exception. Doubleword-sized accesses with word-aligned pointers will automatically be performed as two word-sized accesses.

The following table shows the instructions with support for unaligned addresses. All other instructions require aligned addresses.

**Table 4-1.** Instructions with Unaligned Reference Support

| Instruction | Supported alignment |

|-------------|---------------------|

| ld.d        | Word                |

| st.d        | Word                |

#### 4.3.6 Unimplemented Instructions

The following instructions are unimplemented in AVR32UC, and will cause an Unimplemented Instruction Exception if executed:

- All SIMD instructions

- All coprocessor instructions if no coprocessors are present

- retj, incjosp, popjc, pushjc

- tlbr, tlbs, tlbw

- cache

#### 4.3.7 CPU and Architecture Revision

Three major revisions of the AVR32UC CPU currently exist.

The Architecture Revision field in the CONFIG0 system register identifies which architecture revision is implemented in a specific device.

AVR32UC CPU revision 3 is fully backward-compatible with revisions 1 and 2, ie. code compiled for revision 1 or 2 is binary-compatible with revision 3 CPUs.

# 4.4 Programming Model

#### 4.4.1 Register File Configuration

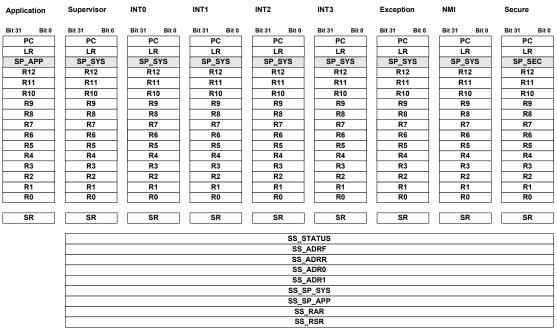

The AVR32UC register file is shown below.

#### Figure 4-3. The AVR32UC Register File

#### 4.4.2 Status Register Configuration

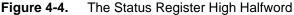

The Status Register (SR) is split into two halfwords, one upper and one lower, see Figure 4-4 on page 26 and Figure 4-5 on page 27. The lower word contains the C, Z, N, V, and Q condition code flags and the R, T, and L bits, while the upper halfword contains information about the mode and state the processor executes in. Refer to the *AVR32 Architecture Manual* for details.

All interrupt levels are by default disabled when debug state is entered, but they can individually be switched on by the monitor routine by clearing the respective mask bit in the status register.

Debug state can be entered as described in the AVR32UC Technical Reference Manual.

Debug state is exited by the retd instruction.

#### 4.4.4 System Registers

The system registers are placed outside of the virtual memory space, and are only accessible using the privileged *mfsr* and *mtsr* instructions. The table below lists the system registers specified in the AVR32 architecture, some of which are unused in AVR32UC. The programmer is responsible for maintaining correct sequencing of any instructions following a *mtsr* instruction. For detail on the system registers, refer to the *AVR32UC Technical Reference Manual*.

| Table 4-3. | System R | egisters |                                        |

|------------|----------|----------|----------------------------------------|

| Reg #      | Address  | Name     | Function                               |

| 0          | 0        | SR       | Status Register                        |

| 1          | 4        | EVBA     | Exception Vector Base Address          |

| 2          | 8        | ACBA     | Application Call Base Address          |

| 3          | 12       | CPUCR    | CPU Control Register                   |

| 4          | 16       | ECR      | Exception Cause Register               |

| 5          | 20       | RSR_SUP  | Unused in AVR32UC                      |

| 6          | 24       | RSR_INT0 | Unused in AVR32UC                      |

| 7          | 28       | RSR_INT1 | Unused in AVR32UC                      |

| 8          | 32       | RSR_INT2 | Unused in AVR32UC                      |

| 9          | 36       | RSR_INT3 | Unused in AVR32UC                      |

| 10         | 40       | RSR_EX   | Unused in AVR32UC                      |

| 11         | 44       | RSR_NMI  | Unused in AVR32UC                      |

| 12         | 48       | RSR_DBG  | Return Status Register for Debug mode  |

| 13         | 52       | RAR_SUP  | Unused in AVR32UC                      |

| 14         | 56       | RAR_INT0 | Unused in AVR32UC                      |

| 15         | 60       | RAR_INT1 | Unused in AVR32UC                      |

| 16         | 64       | RAR_INT2 | Unused in AVR32UC                      |

| 17         | 68       | RAR_INT3 | Unused in AVR32UC                      |

| 18         | 72       | RAR_EX   | Unused in AVR32UC                      |

| 19         | 76       | RAR_NMI  | Unused in AVR32UC                      |

| 20         | 80       | RAR_DBG  | Return Address Register for Debug mode |

| 21         | 84       | JECR     | Unused in AVR32UC                      |

| 22         | 88       | JOSP     | Unused in AVR32UC                      |

| 23         | 92       | JAVA_LV0 | Unused in AVR32UC                      |

| 24         | 96       | JAVA_LV1 | Unused in AVR32UC                      |

| 25         | 100      | JAVA_LV2 | Unused in AVR32UC                      |

Table 4-3.System Registers

The user must also make sure that the system stack is large enough so that any event is able to push the required registers to stack. If the system stack is full, and an event occurs, the system will enter an UNDEFINED state.

#### 4.5.2 Exceptions and Interrupt Requests

When an event other than *scall* or debug request is received by the core, the following actions are performed atomically:

- 1. The pending event will not be accepted if it is masked. The I3M, I2M, I1M, I0M, EM, and GM bits in the Status Register are used to mask different events. Not all events can be masked. A few critical events (NMI, Unrecoverable Exception, TLB Multiple Hit, and Bus Error) can not be masked. When an event is accepted, hardware automatically sets the mask bits corresponding to all sources with equal or lower priority. This inhibits acceptance of other events of the same or lower priority, except for the critical events listed above. Software may choose to clear some or all of these bits after saving the necessary state if other priority schemes are desired. It is the event source's responsability to ensure that their events are left pending until accepted by the CPU.

- 2. When a request is accepted, the Status Register and Program Counter of the current context is stored to the system stack. If the event is an INTO, INT1, INT2, or INT3, registers R8-R12 and LR are also automatically stored to stack. Storing the Status Register ensures that the core is returned to the previous execution mode when the current event handling is completed. When exceptions occur, both the EM and GM bits are set, and the application may manually enable nested exceptions if desired by clearing the appropriate bit. Each exception handler has a dedicated handler address, and this address uniquely identifies the exception source.

- 3. The Mode bits are set to reflect the priority of the accepted event, and the correct register file bank is selected. The address of the event handler, as shown in Table 4-4, is loaded into the Program Counter.

The execution of the event handler routine then continues from the effective address calculated.

The *rete* instruction signals the end of the event. When encountered, the Return Status Register and Return Address Register are popped from the system stack and restored to the Status Register and Program Counter. If the *rete* instruction returns from INT0, INT1, INT2, or INT3, registers R8-R12 and LR are also popped from the system stack. The restored Status Register contains information allowing the core to resume operation in the previous execution mode. This concludes the event handling.

#### 4.5.3 Supervisor Calls

The AVR32 instruction set provides a supervisor mode call instruction. The *scall* instruction is designed so that privileged routines can be called from any context. This facilitates sharing of code between different execution modes. The *scall* mechanism is designed so that a minimal execution cycle overhead is experienced when performing supervisor routine calls from time-critical event handlers.

The *scall* instruction behaves differently depending on which mode it is called from. The behaviour is detailed in the instruction set reference. In order to allow the *scall* routine to return to the correct context, a return from supervisor call instruction, *rets*, is implemented. In the AVR32UC CPU, *scall* and *rets* uses the system stack to store the return address and the status register.

#### 4.5.4 Debug Requests

The AVR32 architecture defines a dedicated Debug mode. When a debug request is received by the core, Debug mode is entered. Entry into Debug mode can be masked by the DM bit in the

# 7.5 Analog characteristics

# 7.5.1 ADC

## Table 7-5. Electrical Characteristics

| Symbol              | Parameter               | Conditions | Min. | Тур.  | Max.  | Unit |

|---------------------|-------------------------|------------|------|-------|-------|------|

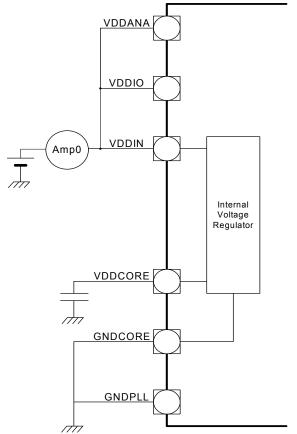

| V <sub>VDDANA</sub> | Analog Power Supply     |            | 3.0  |       | 3.6   | V    |

|                     |                         |            |      |       |       |      |

| Table 7-6.          | Decoupling Requirements |            |      | 1     |       | 1    |

| able 7-6.<br>Symbol | Parameter               | Conditions | Тур. | Techn | ology | Unit |

# 7.5.2 BOD

#### Table 7-7.1.8V BOD Level Values

| Symbol   | Parameter Value | Conditions | Min. | Тур. | Max. | Unit |

|----------|-----------------|------------|------|------|------|------|

|          | 00 1111b        |            |      | 1.79 |      | V    |

|          | 01 0111b        |            |      | 1.70 |      | V    |

| BODLEVEL | 01 1111b        |            |      | 1.61 |      | V    |

|          | 10 0111b        |            |      | 1.52 |      | V    |

Table 7-7 describes the values of the BODLEVEL field in the flash FGPFR register.

#### Table 7-8.3.3V BOD Level Values

| Symbol     | Parameter Value | Conditions | Min. | Тур. | Max. | Unit |

|------------|-----------------|------------|------|------|------|------|

|            | Reset value     |            |      | 2.71 |      | V    |

|            | 1011            |            |      | 2.27 |      | V    |

|            | 1010            |            |      | 2.37 |      | V    |

|            | 1001            |            |      | 2.46 |      | V    |

|            | 1000            |            |      | 2.56 |      | V    |

|            | 0111            |            |      | 2.66 |      | V    |

| BOD33LEVEL | 0110            |            |      | 2.76 |      | V    |

|            | 0101            |            |      | 2.86 |      | V    |

|            | 0100            |            |      | 2.96 |      | V    |

|            | 0011            |            |      | 3.06 |      | V    |

|            | 0010            |            |      | 3.15 |      | V    |

|            | 0001            |            |      | 3.25 |      | V    |

|            | 0000            |            |      | 3.35 |      | V    |

Table 7-8 describes the values of the BOD33.LEVEL field in the PM module

AT32UC3A3

# 7.6 Power Consumption

The values in Table 7-12 and Table 7-13 on page 50 are measured values of power consumption with operating conditions as follows:

$\bullet V_{DDIO} = 3.3V$

•TA =  $25^{\circ}C$

•I/Os are configured in input, pull-up enabled.

These figures represent the power consumption measured on the power supplies

| Peripheral | Тур. | Unit   |

|------------|------|--------|

| ADC        | 7    |        |

| AES        | 80   | _      |

| ABDAC      | 10   |        |

| DMACA      | 70   | _      |

| EBI        | 23   |        |

| EIC        | 0.5  |        |

| GPIO       | 37   |        |

| INTC       | 3    |        |

| MCI        | 40   |        |

| MSI        | 10   |        |

| PDCA       | 20   |        |

| SDRAM      | 5    | μA/MHz |

| SMC        | 9    |        |

| SPI        | 6    |        |

| SSC        | 10   |        |

| RTC        | 5    | _      |

| тс         | 8    | _      |

| TWIM       | 2    |        |

| TWIS       | 2    |        |

| USART      | 10   |        |

| USBB       | 90   |        |

| WDT        | 2    |        |

Table 7-13.

Typical Cuurent Consumption by Peripheral

#### 7.8.3 Main Oscillators

| Table 7-19. Main Oscillators Characteristic | cs |

|---------------------------------------------|----|

|---------------------------------------------|----|

| Symbol                   | Parameter                                       | Conditions                                                                                                                                   | Min.                | Тур.                  | Max.                | Unit |

|--------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|---------------------|------|

|                          |                                                 | External clock on XIN                                                                                                                        |                     |                       | 50                  | MHz  |

| 1/(t <sub>CPMAIN</sub> ) | Oscillator Frequency                            | Crystal                                                                                                                                      | 0.4                 |                       | 20                  | MHz  |

| $C_{L1}, C_{L2}$         | Internal Load Capacitance ( $C_{L1} = C_{L2}$ ) |                                                                                                                                              |                     | 7                     |                     | pF   |

| ESR                      | Crystal Equivalent Series Resistance            |                                                                                                                                              |                     |                       | 75                  | Ω    |

|                          | Duty Cycle                                      |                                                                                                                                              | 40                  | 50                    | 60                  | %    |

| t <sub>ST</sub>          | Startup Time                                    | f = 400 KHz<br>f = 8 MHz<br>f = 16 MHz<br>f = 20 MHz                                                                                         |                     | 25<br>4<br>1.4<br>1   |                     | ms   |

| t <sub>CH</sub>          | XIN Clock High Half-period                      |                                                                                                                                              | 0.4 t <sub>CP</sub> |                       | 0.6 t <sub>CP</sub> |      |

| t <sub>CL</sub>          | XIN Clock Low Half-period                       |                                                                                                                                              | 0.4 t <sub>CP</sub> |                       | 0.6 t <sub>CP</sub> |      |

| C <sub>IN</sub>          | XIN Input Capacitance                           |                                                                                                                                              |                     | 7                     |                     | pF   |

| I <sub>osc</sub>         | Current Consumption                             | Active mode at 400 KHz. Gain = G0<br>Active mode at 8 MHz. Gain = G1<br>Active mode at 16 MHz. Gain = G2<br>Active mode at 20 MHz. Gain = G3 |                     | 30<br>45<br>95<br>205 |                     | μA   |

# 7.8.4 Phase Lock Loop (PLL0, PLL1)

## Table 7-20. PLL Characteristics

| Symbol           | Parameter                             | Conditions                 | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------------|----------------------------|------|------|------|------|

| F <sub>OUT</sub> | VCO Output Frequency                  |                            | 80   |      | 240  | MHz  |

| F <sub>IN</sub>  | Input Frequency (after input divider) |                            | 4    |      | 16   | MHz  |

|                  | Current Consumption                   | Active mode (Fout=80 MHz)  |      | 250  |      | μA   |

| IPLL             | Current Consumption                   | Active mode (Fout=240 MHz) |      | 600  |      | μA   |

# 7.8.5 USB Hi-Speed Phase Lock Loop

#### Table 7-21. PLL Characteristics

| Symbol                | Parameter                                                                                 | Conditions                | Min. | Тур. | Max. | Unit |

|-----------------------|-------------------------------------------------------------------------------------------|---------------------------|------|------|------|------|

| F <sub>OUT</sub>      | VCO Output Frequency                                                                      |                           |      | 480  |      | MHz  |

| F <sub>IN</sub>       | Input Frequency                                                                           |                           |      | 12   |      | MHz  |

| Delta F <sub>IN</sub> | Input Frequency Accuracy (applicable<br>to Clock signal on XIN or to Quartz<br>tolerance) |                           | -500 |      | +500 | ppm  |

| I <sub>PLL</sub>      | Current Consumption                                                                       | Active mode @480MHz @1.8V |      | 2.5  |      | mA   |

# AT32UC3A3

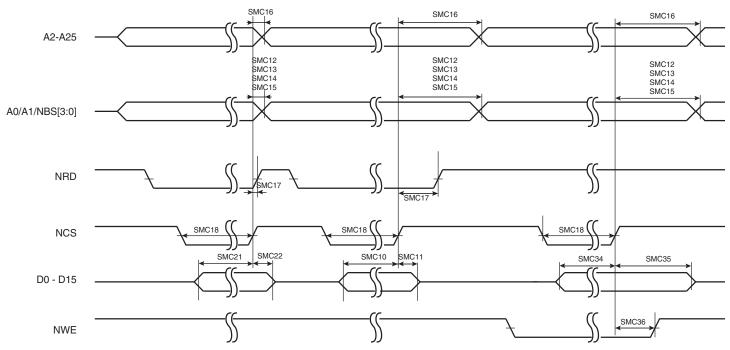

## Table 7-34. SMC Write Signals with No Hold Settings (NWE Controlled only)

| Symbol            | Parameter                        | Min.                                              | Unit |

|-------------------|----------------------------------|---------------------------------------------------|------|

| SMC <sub>43</sub> | Data Out Valid before NWE Rising | (nwe pulse length - 1) * t <sub>CPSMC</sub> - 1.2 | ns   |

| SMC <sub>44</sub> | Data Out Valid after NWE Rising  | 5                                                 | ns   |

| SMC <sub>45</sub> | NWE Pulse Width                  | nwe pulse length * t <sub>CPSMC</sub> - 0.9       | ns   |

# Figure 7-7. SMC Signals for NCS Controlled Accesses.

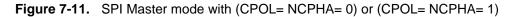

# 7.13 SPI Characteristics

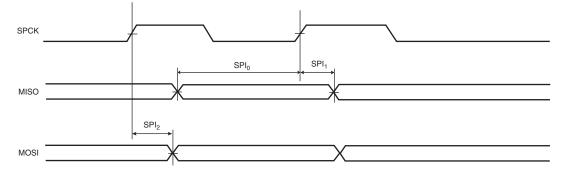

|     | Min       | MM<br>Nom | Max    | Min        | INCH<br>Nom | Max   |

|-----|-----------|-----------|--------|------------|-------------|-------|

| Α   | -         | -         | 1.60   | -          | -           | . 063 |

| С   | 0, 09     | -         | 0. 20  | . 004      | -           | , 008 |

| A3  | 1. 35     | 1.40      | 1.45   | . 053      | . 055       | . 057 |

| D   | 21.90     | 22. 00    | 22, 10 | . 862      | . 866       | . 870 |

| D 1 | 19.90     | 20. 00    | 20.10  | . 783      | . 787       | . 791 |

| E   | 21.90     | 22. 00    | 22. 10 | . 862      | . 866       | . 870 |

| E 1 | 19.90     | 20. 00    | 20. 10 | . 783      | . 787       | . 791 |

| J   | 0, 05     | -         | 0.15   | . 002      | -           | . 006 |

| L   | 0, 45     | 0, 60     | 0, 75  | . 018      | . 024       | . 030 |

| e   | 0, 50 BSC |           |        | . 0197 BSC |             |       |

| f   |           | 0.22 BSC  |        |            | ,009 BSC    |       |

## Table 8-2. Device and Package Maximum Weight

| 1300       |                         | mg |

|------------|-------------------------|----|

| Table 8-3. | Package Characteristics |    |

| Moisture Sensitivity Level MSL3 |

|---------------------------------|

|---------------------------------|

# Table 8-4. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

#### SPI data transfer hangs with CSR0.CSAAT==1 and MR.MODFDIS==0

When CSR0.CSAAT==1 and mode fault detection is enabled (MR.MODFDIS==0), the SPI module will not start a data transfer.

Fix/Workaround

Disable mode fault detection by writing a one to MR.MODFDIS.

#### Disabling SPI has no effect on the SR.TDRE bit

Disabling SPI has no effect on the SR.TDRE bit whereas the write data command is filtered when SPI is disabled. Writing to TDR when SPI is disabled will not clear SR.TDRE. If SPI is disabled during a PDCA transfer, the PDCA will continue to write data to TDR until its buffer is empty, and this data will be lost.

#### Fix/Workaround

Disable the PDCA, add two NOPs, and disable the SPI. To continue the transfer, enable the SPI and PDCA.

#### 10.1.8 Power Manager

# OSC32 not functionnal in Crystal Modes (OSC32CTRL.MODE=1 or OSC32CTRL.MODE=2)

OSC32 clock output is not active even if the oscillation signal is present on XIN32/XOUT32 pins.

OSC32RDY bit may still set even if the CLK32 is not active.

External clock mode (OSC32CTRL.MODE=0) is not affected.

#### Fix/Workaround

None.

# Clock sources will not be stopped in STATIC sleep mode if the difference between CPU and PBx division factor is too high

If the division factor between the CPU/HSB and PBx frequencies is more than 4 when going to a sleep mode where the system RC oscillator is turned off, then high speed clock sources will not be turned off. This will result in a significantly higher power consumption during the sleep mode.

#### Fix/Workaround

Before going to sleep modes where the system RC oscillator is stopped, make sure that the factor between the CPU/HSB and PBx frequencies is less than or equal to 4.

#### 10.1.9 PDCA

#### PCONTROL.CHxRES is non-functional

PCONTROL.CHxRES is non-functional. Counters are reset at power-on, and cannot be reset by software.

#### Fix/Workaround

Software needs to keep history of performance counters.

#### Transfer error will stall a transmit peripheral handshake interface

If a transfer error is encountered on a channel transmitting to a peripheral, the peripheral handshake of the active channel will stall and the PDCA will not do any more transfers on the affected peripheral handshake interface.

#### Fix/Workaround

Disable and then enable the peripheral after the transfer error.

#### Fix/Workaround

For higher polling time, the software must freeze the pipe for the desired period in order to prevent any "extra" token.

| 10.2.5 | ADC |

|--------|-----|

|--------|-----|

#### Sleep Mode activation needs additional A to D conversion

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.

#### Fix/Workaround

Activate the sleep mode in the mode register and then perform an AD conversion.

#### 10.2.6 USART

ISO7816 info register US\_NER cannot be read The NER register always returns zero. Fix/Workaround None.

#### The LIN ID is not transmitted in mode PDCM='0' Fix/Workaround

Using USART in mode LIN master with the PDCM bit = '0', the LINID written at the first address of the transmit buffer is not used. The LINID must be written in the LINIR register, after the configuration and start of the PDCA transfer. Writing the LINID in the LINIR register will start the transfer whenever the PDCA transfer is ready.

# The LINID interrupt is only available for the header reception and not available for the header transmission Fix/Workaround

None.

# USART LIN mode is not functional with the PDCA if PDCM bit in LINMR register is set to 1

If a PDCA transfer is initiated in USART LIN mode with PDCM bit set to 1, the transfer never starts.

#### Fix/Workaround

Only use PDCM=0 configuration with the PDCA transfer.

#### The RTS output does not function correctly in hardware handshaking mode

The RTS signal is not generated properly when the USART receives data in hardware handshaking mode. When the Peripheral DMA receive buffer becomes full, the RTS output should go high, but it will stay low.

#### **Fix/Workaround**

Do not use the hardware handshaking mode of the USART. If it is necessary to drive the RTS output high when the Peripheral DMA receive buffer becomes full, use the normal mode of the USART. Configure the Peripheral DMA Controller to signal an interrupt when the receive buffer is full. In the interrupt handler code, write a one to the RTSDIS bit in the USART Control Register (CR). This will drive the RTS output high. After the next DMA transfer is started and a receive buffer is available, write a one to the RTSEN bit in the USART CR so that RTS will be driven low.

#### ISO7816 Mode T1: RX impossible after any TX

RX impossible after any TX.

#### 10.3.5 ADC

#### Sleep Mode activation needs additional A to D conversion

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.

#### **Fix/Workaround**

Activate the sleep mode in the mode register and then perform an AD conversion.

#### 10.3.6 USART

#### **ISO7816 info register US\_NER cannot be read** The NER register always returns zero.

Fix/Workaround None.

#### The LIN ID is not transmitted in mode PDCM='0' Fix/Workaround

Using USART in mode LIN master with the PDCM bit = '0', the LINID written at the first address of the transmit buffer is not used. The LINID must be written in the LINIR register, after the configuration and start of the PDCA transfer. Writing the LINID in the LINIR register will start the transfer whenever the PDCA transfer is ready.

# The LINID interrupt is only available for the header reception and not available for the header transmission Fix/Workaround None.

USART LIN mode is not functional with the PDCA if PDCM bit in LINMR register is set to 1

If a PDCA transfer is initiated in USART LIN mode with PDCM bit set to 1, the transfer never starts.

#### Fix/Workaround

Only use PDCM=0 configuration with the PDCA transfer.

#### The RTS output does not function correctly in hardware handshaking mode

The RTS signal is not generated properly when the USART receives data in hardware handshaking mode. When the Peripheral DMA receive buffer becomes full, the RTS output should go high, but it will stay low.

#### Fix/Workaround

Do not use the hardware handshaking mode of the USART. If it is necessary to drive the RTS output high when the Peripheral DMA receive buffer becomes full, use the normal mode of the USART. Configure the Peripheral DMA Controller to signal an interrupt when the receive buffer is full. In the interrupt handler code, write a one to the RTSDIS bit in the USART Control Register (CR). This will drive the RTS output high. After the next DMA transfer is started and a receive buffer is available, write a one to the RTSEN bit in the USART CR so that RTS will be driven low.

#### ISO7816 Mode T1: RX impossible after any TX

RX impossible after any TX. **Fix/Workaround** SOFT\_RESET on RX+ Config US\_MR + Config\_US\_CR.

# 11.7 Rev. B - 08/09

1. Updated the datasheet with new device AT32UC3A4.

# 11.8 Rev. A - 03/09

1. Initial revision.

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1)(408) 441-0311 Fax: (+1)(408) 487-2600 www.atmel.com Atmel Asia Limited Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369 Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

#### Atmel Japan

16F, Shin Osaki Kangyo Bldg. 1-6-4 Osaka Shinagawa-ku Tokyo 104-0032 JAPAN Tel: (+81) 3-6417-0300 Fax: (+81) 3-6417-0370

#### © 2012 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof AVR<sup>®</sup>, Qtouch<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIFCT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROF-ITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.