Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                       |

| Number of I/O              | 110                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.75V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 144-TFBGA                                                                   |

| Supplier Device Package    | 144-FFBGA (11x11)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a364-ctur  |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. Description

The AT32UC3A3/A4 is a complete System-On-Chip microcontroller based on the AVR32 UC RISC processor running at frequencies up to 84MHz. AVR32 UC is a high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption, high code density and high performance.

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern operating systems and real-time operating systems. Higher computation capabilities are achievable using a rich set of DSP instructions.

The AT32UC3A3/A4 incorporates on-chip Flash and SRAM memories for secure and fast access. 64 KBytes of SRAM are directly coupled to the AVR32 UC for performances optimization. Two blocks of 32 Kbytes SRAM are independently attached to the High Speed Bus Matrix, allowing real ping-pong management.

The Peripheral Direct Memory Access Controller (PDCA) enables data transfers between peripherals and memories without processor involvement. The PDCA drastically reduces processing overhead when transferring continuous and large data streams.

The Power Manager improves design flexibility and security: the on-chip Brown-Out Detector monitors the power supply, the CPU runs from the on-chip RC oscillator or from one of external oscillator sources, a Real-Time Clock and its associated timer keeps track of the time.

The device includes two sets of three identical 16-bit Timer/Counter (TC) channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing and pulse width modulation. 16-bit channels are combined to operate as 32-bit channels.

The AT32UC3A3/A4 also features many communication interfaces for communication intensive applications like UART, SPI or TWI. The USART supports different communication modes, like SPI Mode and LIN Mode. Additionally, a flexible Synchronous Serial Controller (SSC) is available. The SSC provides easy access to serial communication protocols and audio standards like I2S.

The AT32UC3A3/A4 includes a powerfull External Bus Interface to interface all standard memory device like SRAM, SDRAM, NAND Flash or parallel interfaces like LCD Module.

The peripheral set includes a High Speed MCI for SDIO/SD/MMC and a hardware encryption module based on AES algorithm.

The device embeds a 10-bit ADC and a Digital Audio bistream DAC.

The Direct Memory Access controller (DMACA) allows high bandwidth data flows between high speed peripherals (USB, External Memories, MMC, SDIO, ...) and through high speed internal features (AES, internal memories).

The High-Speed (480MBit/s) USB 2.0 Device and Host interface supports several USB Classes at the same time thanks to the rich Endpoint configuration. The Embedded Host interface allows device like a USB Flash disk or a USB printer to be directly connected to the processor. This periphal has its own dedicated DMA and is perfect for Mass Storage application.

AT32UC3A3/A4 integrates a class 2+ Nexus 2.0 On-Chip Debug (OCD) System, with non-intrusive real-time trace, full-speed read/write memory access in addition to basic runtime control.

# 2.2 Configuration Summary

The table below lists all AT32UC3A3/A4 memory and package configurations:

| Feature                          | AT32UC3A3256/128/64                            | AT32UC3A4256/128/64                                                       |  |

|----------------------------------|------------------------------------------------|---------------------------------------------------------------------------|--|

| Flash                            |                                                | 8/64 KB                                                                   |  |

| SRAM                             | 64                                             | КВ                                                                        |  |

| HSB RAM                          | 64                                             | КВ                                                                        |  |

| EBI                              | Full                                           | Nand flash only                                                           |  |

| GPIO                             | 110                                            | 70                                                                        |  |

| External Interrupts              | 8                                              | 8                                                                         |  |

| TWI                              | 2                                              | 2                                                                         |  |

| USART                            |                                                | 4                                                                         |  |

| Peripheral DMA Channels          | 8                                              | 8                                                                         |  |

| Generic DMA Channels             |                                                | 4                                                                         |  |

| SPI                              | 2                                              | 2                                                                         |  |

| MCI slots                        | 2 MMC/SD slots                                 | 1 MMC/SD slot<br>+ 1 SD slot                                              |  |

| High Speed USB                   |                                                | 1                                                                         |  |

| AES (S option)                   |                                                | 1                                                                         |  |

| SSC                              |                                                | 1                                                                         |  |

| Audio Bitstream DAC              |                                                | 1                                                                         |  |

| Timer/Counter Channels           | (                                              | 6                                                                         |  |

| Watchdog Timer                   |                                                | 1                                                                         |  |

| Real-Time Clock Timer            |                                                | 1                                                                         |  |

| Power Manager                    |                                                | 1                                                                         |  |

| Oscillators                      | Crystal Oscillators 0.4-<br>Crystal Oscillator | Hz (PLL0/PLL1)<br>20 MHz (OSC0/OSC1)<br>32 KHz (OSC32K)<br>15 kHz (RCSYS) |  |

| 10-bit ADC<br>number of channels | 1<br>8                                         |                                                                           |  |

| JTAG                             | 1                                              |                                                                           |  |

| Max Frequency                    | 84 1                                           | MHz                                                                       |  |

| Package                          | LQFP144, TFBGA144                              | VFBGA100                                                                  |  |

**Table 2-1.**Configuration Summary

## 3.4 I/O Line Considerations

#### 3.4.1 JTAG Pins

TMS and TDI pins have pull-up resistors. TDO pin is an output, driven at up to VDDIO, and has no pull-up resistor.

#### 3.4.2 RESET\_N Pin

The RESET\_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIO. As the product integrates a power-on reset cell, the RESET\_N pin can be left unconnected in case no reset from the system needs to be applied to the product.

#### 3.4.3 TWI Pins

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation and inputs with inputs with spike filtering. When used as GPIO pins or used for other peripherals, the pins have the same characteristics as other GPIO pins.

### 3.4.4 GPIO Pins

All the I/O lines integrate a programmable pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the I/O Controller. After reset, I/O lines default as inputs with pull-up resistors disabled, except when indicated otherwise in the column "Reset State" of the I/O Controller multiplexing tables.

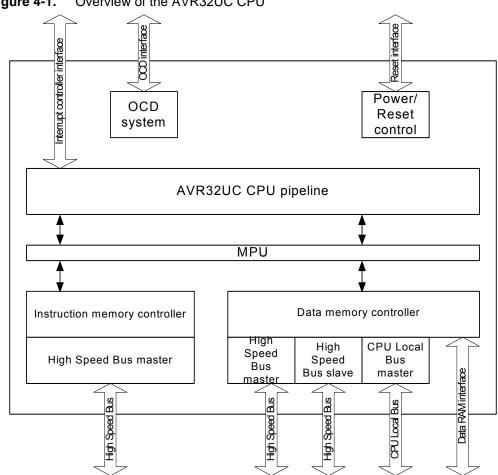

Figure 4-1. Overview of the AVR32UC CPU

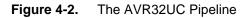

#### 4.3.1 Pipeline Overview

AVR32UC has three pipeline stages, Instruction Fetch (IF), Instruction Decode (ID), and Instruction Execute (EX). The EX stage is split into three parallel subsections, one arithmetic/logic (ALU) section, one multiply (MUL) section, and one load/store (LS) section.

Instructions are issued and complete in order. Certain operations require several clock cycles to complete, and in this case, the instruction resides in the ID and EX stages for the required number of clock cycles. Since there is only three pipeline stages, no internal data forwarding is required, and no data dependencies can arise in the pipeline.

Figure 4-2 on page 24 shows an overview of the AVR32UC pipeline stages.

### 4.3.2 AVR32A Microarchitecture Compliance

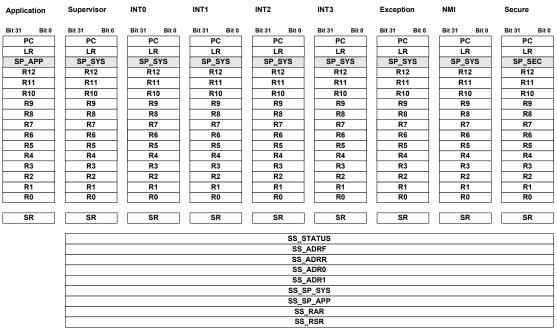

AVR32UC implements an AVR32A microarchitecture. The AVR32A microarchitecture is targeted at cost-sensitive, lower-end applications like smaller microcontrollers. This microarchitecture does not provide dedicated hardware registers for shadowing of register file registers in interrupt contexts. Additionally, it does not provide hardware registers for the return address registers and return status registers. Instead, all this information is stored on the system stack. This saves chip area at the expense of slower interrupt handling.

Upon interrupt initiation, registers R8-R12 are automatically pushed to the system stack. These registers are pushed regardless of the priority level of the pending interrupt. The return address and status register are also automatically pushed to stack. The interrupt handler can therefore use R8-R12 freely. Upon interrupt completion, the old R8-R12 registers and status register are restored, and execution continues at the return address stored popped from stack.

The stack is also used to store the status register and return address for exceptions and *scall*. Executing the *rete* or *rets* instruction at the completion of an exception or system call will pop this status register and continue execution at the popped return address.

#### 4.3.3 Java Support

AVR32UC does not provide Java hardware acceleration.

## 4.3.4 Memory Protection

The MPU allows the user to check all memory accesses for privilege violations. If an access is attempted to an illegal memory address, the access is aborted and an exception is taken. The MPU in AVR32UC is specified in the AVR32UC Technical Reference manual.

#### 4.3.5 Unaligned Reference Handling

AVR32UC does not support unaligned accesses, except for doubleword accesses. AVR32UC is able to perform word-aligned *st.d* and *ld.d*. Any other unaligned memory access will cause an address exception. Doubleword-sized accesses with word-aligned pointers will automatically be performed as two word-sized accesses.

## 4.4 Programming Model

## 4.4.1 Register File Configuration

The AVR32UC register file is shown below.

#### Figure 4-3. The AVR32UC Register File

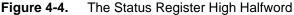

#### 4.4.2 Status Register Configuration

The Status Register (SR) is split into two halfwords, one upper and one lower, see Figure 4-4 on page 26 and Figure 4-5 on page 27. The lower word contains the C, Z, N, V, and Q condition code flags and the R, T, and L bits, while the upper halfword contains information about the mode and state the processor executes in. Refer to the *AVR32 Architecture Manual* for details.

status register. Upon entry into Debug mode, hardware sets the SR[D] bit and jumps to the Debug Exception handler. By default, Debug mode executes in the exception context, but with dedicated Return Address Register and Return Status Register. These dedicated registers remove the need for storing this data to the system stack, thereby improving debuggability. The mode bits in the status register can freely be manipulated in Debug mode, to observe registers in all contexts, while retaining full privileges.

Debug mode is exited by executing the *retd* instruction. This returns to the previous context.

#### 4.5.5 Entry Points for Events

Several different event handler entry points exists. In AVR32UC, the reset address is 0x8000\_0000. This places the reset address in the boot flash memory area.

TLB miss exceptions and *scall* have a dedicated space relative to EVBA where their event handler can be placed. This speeds up execution by removing the need for a jump instruction placed at the program address jumped to by the event hardware. All other exceptions have a dedicated event routine entry point located relative to EVBA. The handler routine address identifies the exception source directly.

AVR32UC uses the ITLB and DTLB protection exceptions to signal a MPU protection violation. ITLB and DTLB miss exceptions are used to signal that an access address did not map to any of the entries in the MPU. TLB multiple hit exception indicates that an access address did map to multiple TLB entries, signalling an error.

All external interrupt requests have entry points located at an offset relative to EVBA. This autovector offset is specified by an external Interrupt Controller. The programmer must make sure that none of the autovector offsets interfere with the placement of other code. The autovector offset has 14 address bits, giving an offset of maximum 16384 bytes.

Special considerations should be made when loading EVBA with a pointer. Due to security considerations, the event handlers should be located in non-writeable flash memory, or optionally in a privileged memory protection region if an MPU is present.

If several events occur on the same instruction, they are handled in a prioritized way. The priority ordering is presented in Table 4-4. If events occur on several instructions at different locations in the pipeline, the events on the oldest instruction are always handled before any events on any younger instruction, even if the younger instruction has events of higher priority than the oldest instruction. An instruction B is younger than an instruction A if it was sent down the pipeline later than A.

The addresses and priority of simultaneous events are shown in Table 4-4. Some of the exceptions are unused in AVR32UC since it has no MMU, coprocessor interface, or floating-point unit.

|                 |                  | Size                                                            | Size                                                            | Size                                                       |

|-----------------|------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------|

| Device          | Start<br>Address | AT32UC3A3256S<br>AT32UC3A3256<br>AT32UC3A4256S<br>AT32UC3A4256S | AT32UC3A3128S<br>AT32UC3A3128<br>AT32UC3A4128S<br>AT32UC3A4128S | AT32UC3A364S<br>AT32UC3A364<br>AT32UC3A464S<br>AT32UC3A464 |

| HRAMC0          | 0xFF000000       | 32KByte                                                         | 32KByte                                                         | 32KByte                                                    |

| HRAMC1          | 0xFF008000       | 32KByte                                                         | 32KByte                                                         | 32KByte                                                    |

| HSB-PB Bridge A | 0xFFFF0000       | 64KByte                                                         | 64KByte                                                         | 64KByte                                                    |

| HSB-PB Bridge B | 0xFFFE0000       | 64KByte                                                         | 64KByte                                                         | 64KByte                                                    |

Table 5-1.

AT32UC3A3A4 Physical Memory Map

# 5.3 Peripheral Address Map

## Table 5-2. Peripheral Address Mapping

| Address    |         | Peripheral Name                                           |

|------------|---------|-----------------------------------------------------------|

| 0xFF100000 | DMACA   | DMA Controller - DMACA                                    |

| 0xFFFD0000 | AES     | Advanced Encryption Standard - AES                        |

| 0xFFFE0000 | USB     | USB 2.0 Device and Host Interface - USB                   |

| 0xFFFE1000 | HMATRIX | HSB Matrix - HMATRIX                                      |

| 0xFFFE1400 | FLASHC  | Flash Controller - FLASHC                                 |

| 0xFFFE1C00 | SMC     | Static Memory Controller - SMC                            |

| 0xFFFE2000 | SDRAMC  | SDRAM Controller - SDRAMC                                 |

| 0xFFFE2400 | ECCHRS  | Error code corrector Hamming and Reed Solomon -<br>ECCHRS |

| 0xFFFE2800 | BUSMON  | Bus Monitor module - BUSMON                               |

| 0xFFFE4000 | MCI     | Mulitmedia Card Interface - MCI                           |

| 0xFFFE8000 | MSI     | Memory Stick Interface - MSI                              |

| 0xFFFF0000 | PDCA    | Peripheral DMA Controller - PDCA                          |

| 0xFFFF0800 | INTC    | Interrupt controller - INTC                               |

Table 5-2.

Peripheral Address Mapping

| 0xFFFF5000 | TWIS0 | Two-wire Slave Interface - TWIS0 |

|------------|-------|----------------------------------|

| 0xFFFF5400 | TWIS1 | Two-wire Slave Interface - TWIS1 |

## 5.4 CPU Local Bus Mapping

Some of the registers in the GPIO module are mapped onto the CPU local bus, in addition to being mapped on the Peripheral Bus. These registers can therefore be reached both by accesses on the Peripheral Bus, and by accesses on the local bus.

Mapping these registers on the local bus allows cycle-deterministic toggling of GPIO pins since the CPU and GPIO are the only modules connected to this bus. Also, since the local bus runs at CPU speed, one write or read operation can be performed per clock cycle to the local busmapped GPIO registers.

The following GPIO registers are mapped on the local bus:

Table 5-3.

Local Bus Mapped GPIO Registers

| Port | Register                             | Mode   | Local Bus<br>Address | Access     |

|------|--------------------------------------|--------|----------------------|------------|

| 0    | Output Driver Enable Register (ODER) | WRITE  | 0x40000040           | Write-only |

|      |                                      | SET    | 0x40000044           | Write-only |

|      |                                      | CLEAR  | 0x40000048           | Write-only |

|      |                                      | TOGGLE | 0x4000004C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000050           | Write-only |

|      |                                      | SET    | 0x40000054           | Write-only |

|      |                                      | CLEAR  | 0x40000058           | Write-only |

|      |                                      | TOGGLE | 0x4000005C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000060           | Read-only  |

| 1    | Output Driver Enable Register (ODER) | WRITE  | 0x40000140           | Write-only |

|      |                                      | SET    | 0x40000144           | Write-only |

|      |                                      | CLEAR  | 0x40000148           | Write-only |

|      |                                      | TOGGLE | 0x4000014C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000150           | Write-only |

|      |                                      | SET    | 0x40000154           | Write-only |

|      |                                      | CLEAR  | 0x40000158           | Write-only |

|      |                                      | TOGGLE | 0x4000015C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000160           | Read-only  |

## Table 7-9. BOD Timing

| Symbol           | Parameter                                                | Conditions                        | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------------------------|-----------------------------------|------|------|------|------|

| T <sub>BOD</sub> | Minimum time with VDDCORE < VBOD to detect power failure | Falling VDDCORE from 1.8V to 1.1V |      | 300  | 800  | ns   |

## 7.5.3 Reset Sequence

## Table 7-10. Electrical Characteristics

| Symbol               | Parameter                                                                                                                                          | Conditions                                              | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|------|------|------|

| V <sub>DDRR</sub>    | VDDIN/VDDIO rise rate to ensure<br>power-on-reset                                                                                                  |                                                         | 0.8  |      |      | V/ms |

| V <sub>POR+</sub>    | Rising threshold voltage: voltage up<br>to which device is kept under reset by<br>POR on rising VDDIN                                              | Rising VDDIN: V <sub>RESTART</sub> -> V <sub>POR+</sub> |      | 2.7  |      | V    |

| V <sub>POR-</sub>    | Falling threshold voltage: voltage<br>when POR resets device on falling<br>VDDIN                                                                   | Falling VDDIN: 3.3V -> V <sub>POR-</sub>                |      | 2.7  |      | V    |

| V <sub>RESTART</sub> | On falling VDDIN, voltage must go<br>down to this value before supply can<br>rise again to ensure reset signal is<br>released at V <sub>POR+</sub> | Falling VDDIN: 3.3V -> V <sub>RESTART</sub>             |      |      | 0.2  | V    |

| T <sub>SSU1</sub>    | Time for Cold System Startup: Time<br>for CPU to fetch its first instruction<br>(RCosc not calibrated)                                             |                                                         | 480  |      | 960  | μs   |

| T <sub>SSU2</sub>    | Time for Hot System Startup: Time for<br>CPU to fetch its first instruction<br>(RCosc calibrated)                                                  |                                                         |      | 420  |      | μs   |

## 7.6 Power Consumption

The values in Table 7-12 and Table 7-13 on page 50 are measured values of power consumption with operating conditions as follows:

$\bullet V_{DDIO} = 3.3V$

•TA =  $25^{\circ}C$

•I/Os are configured in input, pull-up enabled.

These figures represent the power consumption measured on the power supplies

## 7.8.3 Main Oscillators

| Table 7-19. Main Oscillators Characteristic | cs |

|---------------------------------------------|----|

|---------------------------------------------|----|

| Symbol                   | Parameter                                       | Conditions                                                                                                                                   | Min.                | Тур.                  | Max.                | Unit |

|--------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|---------------------|------|

|                          |                                                 | External clock on XIN                                                                                                                        |                     |                       | 50                  | MHz  |

| 1/(t <sub>CPMAIN</sub> ) | Oscillator Frequency                            | Crystal                                                                                                                                      | 0.4                 |                       | 20                  | MHz  |

| $C_{L1}, C_{L2}$         | Internal Load Capacitance ( $C_{L1} = C_{L2}$ ) |                                                                                                                                              |                     | 7                     |                     | pF   |

| ESR                      | Crystal Equivalent Series Resistance            |                                                                                                                                              |                     |                       | 75                  | Ω    |

|                          | Duty Cycle                                      |                                                                                                                                              | 40                  | 50                    | 60                  | %    |

| t <sub>ST</sub>          | Startup Time                                    | f = 400 KHz<br>f = 8 MHz<br>f = 16 MHz<br>f = 20 MHz                                                                                         |                     | 25<br>4<br>1.4<br>1   |                     | ms   |

| t <sub>CH</sub>          | XIN Clock High Half-period                      |                                                                                                                                              | 0.4 t <sub>CP</sub> |                       | 0.6 t <sub>CP</sub> |      |

| t <sub>CL</sub>          | XIN Clock Low Half-period                       |                                                                                                                                              | 0.4 t <sub>CP</sub> |                       | 0.6 t <sub>CP</sub> |      |

| C <sub>IN</sub>          | XIN Input Capacitance                           |                                                                                                                                              |                     | 7                     |                     | pF   |

| I <sub>osc</sub>         | Current Consumption                             | Active mode at 400 KHz. Gain = G0<br>Active mode at 8 MHz. Gain = G1<br>Active mode at 16 MHz. Gain = G2<br>Active mode at 20 MHz. Gain = G3 |                     | 30<br>45<br>95<br>205 |                     | μA   |

## 7.8.4 Phase Lock Loop (PLL0, PLL1)

## Table 7-20. PLL Characteristics

| Symbol           | Parameter                             | Conditions                 | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------------|----------------------------|------|------|------|------|

| F <sub>OUT</sub> | VCO Output Frequency                  |                            | 80   |      | 240  | MHz  |

| F <sub>IN</sub>  | Input Frequency (after input divider) |                            | 4    |      | 16   | MHz  |

|                  | Current Consumption                   | Active mode (Fout=80 MHz)  |      | 250  |      | μA   |

| IPLL             | Current Consumption                   | Active mode (Fout=240 MHz) |      | 600  |      | μA   |

## 7.8.5 USB Hi-Speed Phase Lock Loop

## Table 7-21. PLL Characteristics

| Symbol                | Parameter                                                                                 | Conditions                | Min. | Тур. | Max. | Unit |

|-----------------------|-------------------------------------------------------------------------------------------|---------------------------|------|------|------|------|

| F <sub>OUT</sub>      | VCO Output Frequency                                                                      |                           |      | 480  |      | MHz  |

| F <sub>IN</sub>       | Input Frequency                                                                           |                           |      | 12   |      | MHz  |

| Delta F <sub>IN</sub> | Input Frequency Accuracy (applicable<br>to Clock signal on XIN or to Quartz<br>tolerance) |                           | -500 |      | +500 | ppm  |

| I <sub>PLL</sub>      | Current Consumption                                                                       | Active mode @480MHz @1.8V |      | 2.5  |      | mA   |

| Parameter                  | Conditions          | Min. | Тур. | Max. | Unit |

|----------------------------|---------------------|------|------|------|------|

| Resolution                 |                     |      | 10   |      | Bit  |

| Absolute Accuracy          | ADC Clock = 5 MHz   |      |      | 3    | LSB  |

| Integral Non-linearity     | ADC Clock = 5 MHz   |      | 1.5  | 2    | LSB  |

|                            | ADC Clock = 5 MHz   |      | 1    | 2    | LSB  |

| Differential Non-linearity | ADC Clock = 2.5 MHz |      | 0.6  | 1    | LSB  |

| Offset Error               | ADC Clock = 5 MHz   | -2   |      | 2    | LSB  |

| Gain Error                 | ADC Clock = 5 MHz   | -2   |      | 2    | LSB  |

## **Table 7-26.**Transfer Characteristics in 10-bit mode

## 7.10 USB Transceiver Characteristics

## 7.10.1 Electrical Characteristics

## Table 7-27. Electrical Parameters

| Symbol            | Parameter                                   | Conditions                           | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------------------|--------------------------------------|------|------|------|------|

| R <sub>EXT</sub>  | Recommended External USB Series<br>Resistor | In series with each USB pin with ±5% |      | 39   |      | Ω    |

| R <sub>BIAS</sub> | VBIAS External Resistor <sup>(1)</sup>      | ±1%                                  |      | 6810 |      | Ω    |

| C <sub>BIAS</sub> | VBIAS External Capcitor                     |                                      |      | 10   |      | pF   |

1. The USB on-chip buffers comply with the Universal Serial Bus (USB) v2.0 standard. All AC parameters related to these buffers can be found within the USB 2.0 electrical specifications.

## 7.10.2 Static Power Consumption

#### Table 7-28. Static Power Consumption

| Symbol               | Parameter                                     | Conditions                                                                                    | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>BIAS</sub>    | Bias current consumption on VBG               |                                                                                               |      |      | 1    | μA   |

|                      | HS Transceiver and I/O current consumption    |                                                                                               |      |      | 8    | μA   |

| I <sub>VDDUTMI</sub> | FS/HS Transceiver and I/O current consumption | If cable is connected, add 200µA<br>(typical) due to Pull-up/Pull-down<br>current consumption |      |      | 3    | μA   |

## 7.10.3 Dynamic Power Consumption

#### **Table 7-29.**Dynamic Power Consumption

| Symbol            | Parameter                       | Conditions | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------|------------|------|------|------|------|

| I <sub>BIAS</sub> | Bias current consumption on VBG |            |      | 0.7  | 0.8  | mA   |

## **Table 7-29.**Dynamic Power Consumption

| Symbol   | Parameter                             | Conditions                              | Min. | Тур. | Max. | Unit |

|----------|---------------------------------------|-----------------------------------------|------|------|------|------|

|          | HS Transceiver current consumption    | HS transmission                         |      | 47   | 60   | mA   |

|          | HS Transceiver current consumption    | HS reception                            |      | 18   | 27   | mA   |

| Luppurtu | FS/HS Transceiver current consumption | FS transmission 0m cable <sup>(1)</sup> |      | 4    | 6    | mA   |

| IVDDUTMI | FS/HS Transceiver current consumption | FS transmission 5m cable                |      | 26   | 30   | mA   |

|          | FS/HS Transceiver current consumption | FS reception                            |      | 3    | 4.5  | mA   |

1. Including 1 mA due to Pull-up/Pull-down current consumption.

## 34.5.5 USB High Speed Design Guidelines

In order to facilitate hardware design, Atmel provides an application note on www.atmel.com.

# 7.11 EBI Timings

## 7.11.1 SMC Signals

These timings are given for worst case process, T =  $85 \cdot C$ , VDDIO = 3V and 40 pF load capacitance.

### Table 7-30. SMC Clock Signal

| Symbol                  | Parameter                      | Max. <sup>(1)</sup>     | Unit |

|-------------------------|--------------------------------|-------------------------|------|

| 1/(t <sub>CPSMC</sub> ) | SMC Controller Clock Frequency | 1/(t <sub>cpcpu</sub> ) | MHz  |

Note: 1. The maximum frequency of the SMC interface is the same as the max frequency for the HSB.

## Table 7-31. SMC Read Signals with Hold Settings

| Symbol            | Parameter                                  | Min.                                                              | Unit |

|-------------------|--------------------------------------------|-------------------------------------------------------------------|------|

|                   | NRD Control                                | led (READ_MODE = 1)                                               |      |

| SMC <sub>1</sub>  | Data Setup before NRD High                 | 12                                                                | ns   |

| SMC <sub>2</sub>  | Data Hold after NRD High                   | 0                                                                 | ns   |

| SMC <sub>3</sub>  | NRD High to NBS0/A0 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                        | ns   |

| SMC <sub>4</sub>  | NRD High to NBS1 Change <sup>(1)</sup>     | nrd hold length * t <sub>CPSMC</sub> - 1.3                        | ns   |

| SMC <sub>5</sub>  | NRD High to NBS2/A1 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                        | ns   |

| SMC <sub>7</sub>  | NRD High to A2 - A23 Change <sup>(1)</sup> | nrd hold length * t <sub>CPSMC</sub> - 1.3                        | ns   |

| SMC <sub>8</sub>  | NRD High to NCS Inactive <sup>(1)</sup>    | (nrd hold length - ncs rd hold length) * t <sub>CPSMC</sub> - 2.3 | ns   |

| SMC <sub>9</sub>  | NRD Pulse Width                            | nrd pulse length * t <sub>CPSMC</sub> - 1.4                       | ns   |

|                   | NRD Control                                | led (READ_MODE = 0)                                               |      |

| SMC <sub>10</sub> | Data Setup before NCS High                 | 11.5                                                              | ns   |

| SMC <sub>11</sub> | Data Hold after NCS High                   | 0                                                                 | ns   |

| SMC <sub>12</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                     | ns   |

| SMC <sub>13</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                     | ns   |

| SMC <sub>14</sub> | NCS High to NBS2/A1 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                     | ns   |

| SMC <sub>16</sub> | NCS High to A2 - A23 Change <sup>(1)</sup> | ncs rd hold length * t <sub>CPSMC</sub> - 4                       | ns   |

| SMC <sub>17</sub> | NCS High to NRD Inactive <sup>(1)</sup>    | ncs rd hold length - nrd hold length)* t <sub>CPSMC</sub> - 1.3   | ns   |

| SMC <sub>18</sub> | NCS Pulse Width                            | ncs rd pulse length * t <sub>CPSMC</sub> - 3.6                    | ns   |

Note: 1. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs rd hold length" or "nrd hold length".

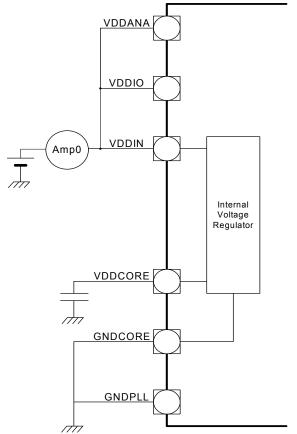

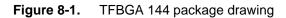

## 8.2 Package Drawings

ddd

bbb

copla: 0.120

copla: 0.200

|         |        | Fix/Workaround<br>None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.3.14 | MCI    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |        | <ul> <li>The busy signal of the responses R1b is not taken in account for CMD12 STOP_TRANSFER</li> <li>It is not possible to know the busy status of the card during the response (R1b) for the commands CMD12.</li> <li>Fix/Workaround</li> <li>The card busy line should be polled through the GPIO Input Value register (IVR) for commands CMD12.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10.3.15 | SSC    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |        | <ul> <li>Frame Synchro and Frame Synchro Data are delayed by one clock cycle</li> <li>The frame synchro and the frame synchro data are delayed from 1 SSC_CLOCK when:</li> <li>Clock is CKDIV</li> <li>The START is selected on either a frame synchro edge or a level</li> <li>Frame synchro data is enabled</li> <li>Transmit clock is gated on output (through CKO field)</li> <li>Fix/Workaround</li> <li>Transmit or receive CLOCK must not be gated (by the mean of CKO field) when START condition is performed on a generated frame synchro.</li> </ul>                                                                                                                                                                                                                                      |

| 10.3.16 | FLASHC |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |        | <ul> <li>Corrupted read in flash may happen after fuses write or erase operations (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands)</li> <li>After a flash fuse write or erase operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands), reading (data read or code fetch) in flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.</li> <li>Fix/Workaround</li> <li>Before the flash fuse write or erase operation, enable the flash high speed mode (FLASHC HSEN command). The flash fuse write or erase operations (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands) must be issued from RAM or through the EBI. After these commands, read 3 times one flash page initialized to 00h. Disable the flash high</li> </ul> |

speed mode (FLASHC HSDIS command). It is then possible to safely read or code fetch the

flash.

## 11.7 Rev. B - 08/09

1. Updated the datasheet with new device AT32UC3A4.

# 11.8 Rev. A - 03/09

1. Initial revision.

| 1 | Descr  | iption                               | 3  |

|---|--------|--------------------------------------|----|

| 2 | Overv  | <i>r</i> iew                         | 4  |

|   | 2.1    | Block Diagram                        | 4  |

|   | 2.2    | Configuration Summary                | 5  |

| 3 | Packa  | nge and Pinout                       | 6  |

|   | 3.1    | Package                              | 6  |

|   | 3.2    | Peripheral Multiplexing on I/O lines | 9  |

|   | 3.3    | Signal Descriptions                  | 14 |

|   | 3.4    | I/O Line Considerations              | 19 |

|   | 3.5    | Power Considerations                 | 20 |

| 4 | Proce  | essor and Architecture               | 21 |

|   | 4.1    | Features                             | 21 |

|   | 4.2    | AVR32 Architecture                   | 21 |

|   | 4.3    | The AVR32UC CPU                      | 22 |

|   | 4.4    | Programming Model                    | 26 |

|   | 4.5    | Exceptions and Interrupts            |    |

| 5 | Мето   | ories                                | 34 |

|   | 5.1    | Embedded Memories                    | 34 |

|   | 5.2    | Physical Memory Map                  | 34 |

|   | 5.3    | Peripheral Address Map               | 35 |

|   | 5.4    | CPU Local Bus Mapping                | 37 |

| 6 | Boot S | Sequence                             | 39 |

|   | 6.1    | Starting of Clocks                   |    |

|   | 6.2    | Fetching of Initial Instructions     |    |

| 7 | Electr | ical Characteristics                 | 40 |

|   | 7.1    | Absolute Maximum Ratings*            | 40 |

|   | 7.2    | DC Characteristics                   | 41 |

|   | 7.3    | I/O pin Characteristics              | 42 |

|   | 7.4    | Regulator characteristics            | 43 |

|   | 7.5    | Analog characteristics               | 44 |

|   | 7.6    | Power Consumption                    | 48 |

|   | 7.7    | System Clock Characteristics         | 51 |

|   | 7.8    | Oscillator Characteristics           | 52 |

|   | 7.9    | ADC Characteristics                  | 54 |

|    | 7.10    | USB Transceiver Characteristics | 55 |

|----|---------|---------------------------------|----|

|    | 7.11    | EBI Timings                     | 57 |

|    | 7.12    | JTAG Characteristics            | 63 |

|    | 7.13    | SPI Characteristics             | 64 |

|    | 7.14    | MCI                             | 66 |

|    | 7.15    | Flash Memory Characteristics    | 67 |

| 8  | Mecha   | nical Characteristics           | 68 |

|    | 8.1     | Thermal Considerations          | 68 |

|    | 8.2     | Package Drawings                | 69 |

|    | 8.3     | Soldering Profile               | 72 |

| 9  | Orderii | ng Information                  | 73 |

| 10 | Errata  |                                 | 74 |

|    | 10.1    | Rev. H                          | 74 |

|    | 10.2    | Rev. E                          | 78 |

|    | 10.3    | Rev. D                          | 84 |

| 11 | Datash  | neet Revision History           | 90 |

|    | 11.1    | Rev. H– 10/12                   | 90 |

|    | 11.2    | Rev. G– 11/11                   | 90 |

|    | 11.3    | Rev. F – 08/11                  | 90 |

|    | 11.4    | Rev. E – 06/11                  | 90 |

|    | 11.5    | Rev. D – 04/11                  | 90 |

|    | 11.6    | Rev. C – 03/10                  | 90 |

|    | 11.7    | Rev. B – 08/09                  | 91 |

|    | 11.8    | Rev. A – 03/09                  | 91 |

|    |         |                                 |    |