Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                       |

| Number of I/O              | 110                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.75V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 144-TFBGA                                                                   |

| Supplier Device Package    | 144-FFBGA (11x11)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a364-ctut  |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

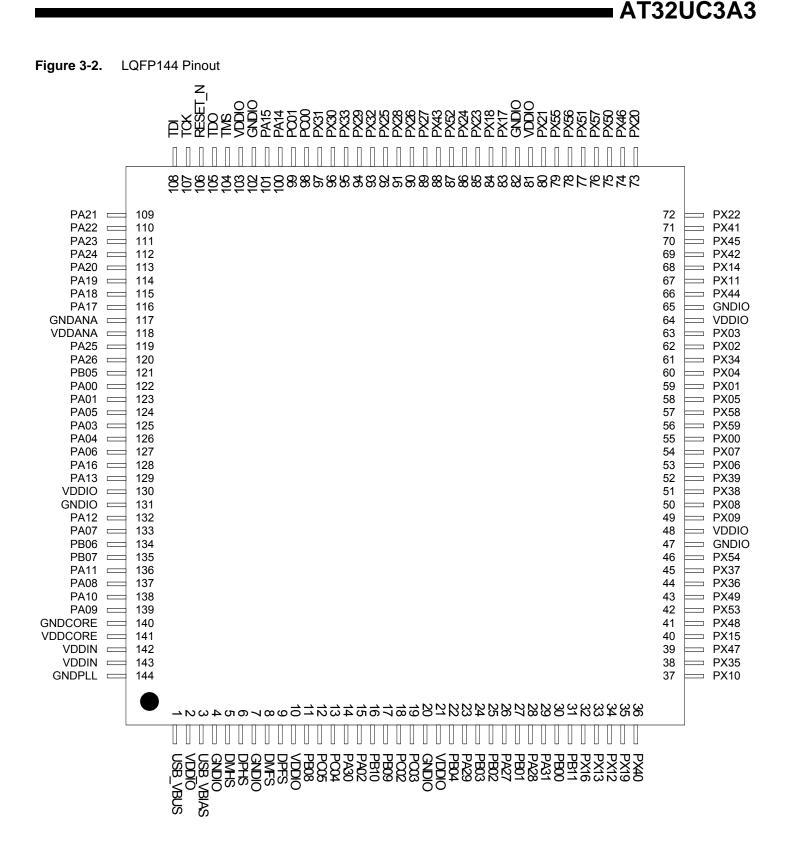

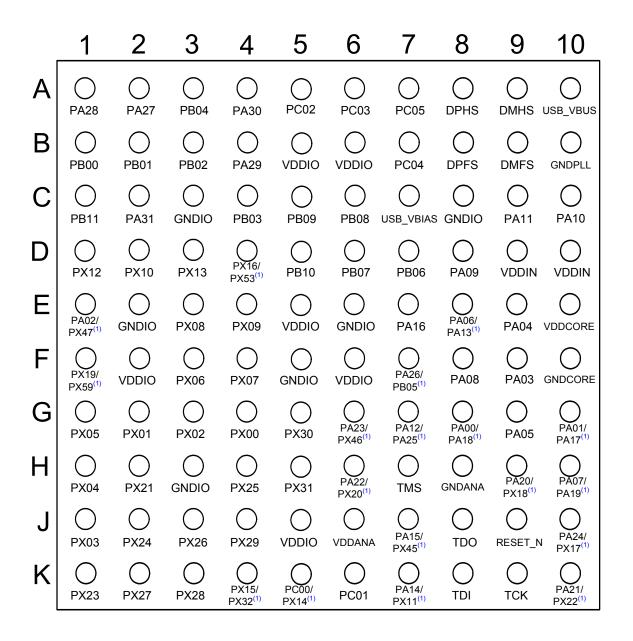

Note: 1. Those balls are physically connected to 2 GPIOs. Software must managed carrefully the GPIO configuration to avoid electrical conflict

# 3.2 Peripheral Multiplexing on I/O lines

# 3.2.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following table describes the peripheral signals multiplexed to the GPIO lines.

Note that GPIO 44 is physically implemented in silicon but it must be kept unused and configured in input mode.

|            |            |                     |      | G       |        |             |                | GPIO fur            | oction           |               |

|------------|------------|---------------------|------|---------|--------|-------------|----------------|---------------------|------------------|---------------|

|            |            |                     |      | P       |        | PIN         |                |                     |                  |               |

| BGA<br>144 | QFP<br>144 | BGA<br>100          | PIN  | <br>  0 | Supply | Type<br>(2) | А              | В                   | С                | D             |

|            |            |                     |      | -       |        |             |                |                     | -                | 0             |

| G11        | 122        | G8 <sup>(1)</sup>   | PA00 | 0       | VDDIO  | x3          | USART0 - RTS   | TC0 - CLK1          | SPI1 - NPCS[3]   |               |

| G12        | 123        | G10 <sup>(1)</sup>  | PA01 | 1       | VDDIO  | x1          | USART0 - CTS   | TC0 - A1            | USART2 - RTS     |               |

| D8         | 15         | E1 <sup>(1)</sup>   | PA02 | 2       | VDDIO  | x1          | USART0 - CLK   | TC0 - B1            | SPI0 - NPCS[0]   |               |

| G10        | 125        | F9                  | PA03 | 3       | VDDIO  | x1          | USART0 - RXD   | EIC - EXTINT[4]     | ABDAC - DATA[0]  |               |

| F9         | 126        | E9                  | PA04 | 4       | VDDIO  | x1          | USART0 - TXD   | EIC - EXTINT[5]     | ABDAC - DATAN[0] |               |

| F10        | 124        | G9                  | PA05 | 5       | VDDIO  | x1          | USART1 - RXD   | TC1 - CLK0          | USB - ID         |               |

| F8         | 127        | E8 <sup>(1)</sup>   | PA06 | 6       | VDDIO  | x1          | USART1 - TXD   | TC1 - CLK1          | USB - VBOF       |               |

| E10        | 133        | H10 <sup>(1)</sup>  | PA07 | 7       | VDDIO  | x1          | SPI0 - NPCS[3] | ABDAC - DATAN[0]    | USART1 - CLK     |               |

| C11        | 137        | F8                  | PA08 | 8       | VDDIO  | x3          | SPI0 - SPCK    | ABDAC - DATA[0]     | TC1 - B1         |               |

| B12        | 139        | D8                  | PA09 | 9       | VDDIO  | x2          | SPI0 - NPCS[0] | EIC - EXTINT[6]     | TC1 - A1         |               |

| C12        | 138        | C10                 | PA10 | 10      | VDDIO  | x2          | SPI0 - MOSI    | USB - VBOF          | TC1 - B0         |               |

| D10        | 136        | C9                  | PA11 | 11      | VDDIO  | x2          | SPI0 - MISO    | USB - ID            | TC1 - A2         |               |

| E12        | 132        | G7 <sup>(1)</sup>   | PA12 | 12      | VDDIO  | x1          | USART1 - CTS   | SPIO - NPCS[2]      | TC1 - A0         |               |

| F11        | 129        | E8 <sup>(1)</sup>   | PA13 | 13      | VDDIO  | x1          | USART1 - RTS   | SPIO - NPCS[1]      | EIC - EXTINT[7]  |               |

| J6         | 100        | K7 <sup>(1)</sup>   | PA14 | 14      | VDDIO  | x1          | SPI0 - NPCS[1] | TWIMS0 - TWALM      | TWIMS1 - TWCK    |               |

| J7         | 101        | J7 <sup>(1)</sup>   | PA15 | 15      | VDDIO  | x1          | MCI - CMD[1]   | SPI1 - SPCK         | TWIMS1 - TWD     |               |

| F12        | 128        | E7                  | PA16 | 16      | VDDIO  | x1          | MCI - DATA[11] | SPI1 - MOSI         | TC1 - CLK2       |               |

| H7         | 116        | G10 <sup>(1)</sup>  | PA17 | 17      | VDDANA | x1          | MCI - DATA[10] | SPI1 - NPCS[1]      | ADC - AD[7]      |               |

| K8         | 115        | G8 <sup>(1)</sup>   | PA18 | 18      | VDDANA | x1          | MCI - DATA[9]  | SPI1 - NPCS[2]      | ADC - AD[6]      |               |

| J8         | 114        | H10 <sup>(1)</sup>  | PA19 | 19      | VDDANA | x1          | MCI - DATA[8]  | SPI1 - MISO         | ADC - AD[5]      |               |

| J9         | 113        | H9 <sup>(1)</sup>   | PA20 | 20      | VDDANA | x1          | EIC - NMI      | SSC - RX_FRAME_SYNC | ADC - AD[4]      |               |

| H9         | 109        | K10 <sup>(1)</sup>  | PA21 | 21      | VDDANA | x1          | ADC - AD[0]    | EIC - EXTINT[0]     | USB - ID         |               |

| H10        | 110        | H6 <sup>(1)</sup>   | PA22 | 22      | VDDANA | x1          | ADC - AD[1]    | EIC - EXTINT[1]     | USB - VBOF       |               |

| G8         | 111        | G6 <sup>(1)</sup>   | PA23 | 23      | VDDANA | x1          | ADC - AD[2]    | EIC - EXTINT[2]     | ABDAC - DATA[1]  |               |

| G9         | 112        | J10 <sup>(1)</sup>  | PA24 | 24      | VDDANA | x1          | ADC - AD[3]    | EIC - EXTINT[3]     | ABDAC - DATAN[1] |               |

| E9         | 119        | G7 <sup>(1)</sup>   | PA25 | 25      | VDDIO  | x1          | TWIMS0 - TWD   | TWIMS1 - TWALM      | USART1 - DCD     |               |

| D9         | 120        | F7 <sup>(1)</sup> ) | PA26 | 26      | VDDIO  | x1          | TWIMS0 - TWCK  | USART2 - CTS        | USART1 - DSR     |               |

| A4         | 26         | A2                  | PA27 | 27      | VDDIO  | x2          | MCI - CLK      | SSC - RX_DATA       | USART3 - RTS     | MSI - SCLK    |

| A3         | 28         | A1                  | PA28 | 28      | VDDIO  | x1          | MCI - CMD[0]   | SSC - RX_CLOCK      | USART3 - CTS     | MSI - BS      |

| A6         | 23         | B4                  | PA29 | 29      | VDDIO  | x1          | MCI - DATA[0]  | USART3 - TXD        | TC0 - CLK0       | MSI - DATA[0] |

Table 3-1.

GPIO Controller Function Multiplexing

Table 3-1.

GPIO Controller Function Multiplexing

|     |     |                    |      | G<br>P |        | PIN  | -              | GPIO fur          | nction              |   |

|-----|-----|--------------------|------|--------|--------|------|----------------|-------------------|---------------------|---|

| BGA | QFP | BGA                |      |        |        | Туре |                |                   |                     |   |

| 144 | 144 | 100                | PIN  | 0      | Supply | (2)  | Α              | В                 | С                   | D |

| L6  | 84  | H9 <sup>(1)</sup>  | PX18 | 69     | VDDIO  | x2   | EBI - ADDR[16] | DMACA - DMAACK[1] | TC0 - A2            |   |

| D5  | 35  | F1 <sup>(1)</sup>  | PX19 | 70     | VDDIO  | x2   | EBI - ADDR[15] | EIC - SCAN[0]     | TC0 - B2            |   |

| L4  | 73  | H6 <sup>(1)</sup>  | PX20 | 71     | VDDIO  | x2   | EBI - ADDR[14] | EIC - SCAN[1]     | TC0 - CLK0          |   |

| М5  | 80  | H2                 | PX21 | 72     | VDDIO  | x2   | EBI - ADDR[13] | EIC - SCAN[2]     | TC0 - CLK1          |   |

| M1  | 72  | K10 <sup>(1)</sup> | PX22 | 73     | VDDIO  | x2   | EBI - ADDR[12] | EIC - SCAN[3]     | TC0 - CLK2          |   |

| M6  | 85  | K1                 | PX23 | 74     | VDDIO  | x2   | EBI - ADDR[11] | EIC - SCAN[4]     | SSC - TX_CLOCK      |   |

| M7  | 86  | J2                 | PX24 | 75     | VDDIO  | x2   | EBI - ADDR[10] | EIC - SCAN[5]     | SSC - TX_DATA       |   |

| M8  | 92  | H4                 | PX25 | 76     | VDDIO  | x2   | EBI - ADDR[9]  | EIC - SCAN[6]     | SSC - RX_DATA       |   |

| L9  | 90  | J3                 | PX26 | 77     | VDDIO  | x2   | EBI - ADDR[8]  | EIC - SCAN[7]     | SSC - RX_FRAME_SYNC |   |

| К9  | 89  | K2                 | PX27 | 78     | VDDIO  | x2   | EBI - ADDR[7]  | SPI0 - MISO       | SSC - TX_FRAME_SYNC |   |

| L10 | 91  | K3                 | PX28 | 79     | VDDIO  | x2   | EBI - ADDR[6]  | SPIO - MOSI       | SSC - RX_CLOCK      |   |

| K11 | 94  | J4                 | PX29 | 80     | VDDIO  | x2   | EBI - ADDR[5]  | SPI0 - SPCK       |                     |   |

| M11 | 96  | G5                 | PX30 | 81     | VDDIO  | x2   | EBI - ADDR[4]  | SPI0 - NPCS[0]    |                     |   |

| M10 | 97  | H5                 | PX31 | 82     | VDDIO  | x2   | EBI - ADDR[3]  | SPI0 - NPCS[1]    |                     |   |

| М9  | 93  | K4 <sup>(1)</sup>  | PX32 | 83     | VDDIO  | x2   | EBI - ADDR[2]  | SPI0 - NPCS[2]    |                     |   |

| M12 | 95  |                    | PX33 | 84     | VDDIO  | x2   | EBI - ADDR[1]  | SPI0 - NPCS[3]    |                     |   |

| J3  | 61  |                    | PX34 | 85     | VDDIO  | x2   | EBI - ADDR[0]  | SPI1 - MISO       | PM - GCLK[0]        |   |

| C2  | 38  |                    | PX35 | 86     | VDDIO  | x2   | EBI - DATA[15] | SPI1 - MOSI       | PM - GCLK[1]        |   |

| D3  | 44  |                    | PX36 | 87     | VDDIO  | x2   | EBI - DATA[14] | SPI1 - SPCK       | PM - GCLK[2]        |   |

| D2  | 45  |                    | PX37 | 88     | VDDIO  | x2   | EBI - DATA[13] | SPI1 - NPCS[0]    | PM - GCLK[3]        |   |

| E1  | 51  |                    | PX38 | 89     | VDDIO  | x2   | EBI - DATA[12] | SPI1 - NPCS[1]    | USART1 - DCD        |   |

| F1  | 52  |                    | PX39 | 90     | VDDIO  | x2   | EBI - DATA[11] | SPI1 - NPCS[2]    | USART1 - DSR        |   |

| A1  | 36  |                    | PX40 | 91     | VDDIO  | x2   |                | MCI - CLK         |                     |   |

| M2  | 71  |                    | PX41 | 92     | VDDIO  | x2   | EBI - CAS      |                   |                     |   |

| М3  | 69  |                    | PX42 | 93     | VDDIO  | x2   | EBI - RAS      |                   |                     |   |

| L7  | 88  |                    | PX43 | 94     | VDDIO  | x2   | EBI - SDA10    | USART1 - RI       |                     |   |

| К2  | 66  |                    | PX44 | 95     | VDDIO  | x2   | EBI - SDWE     | USART1 - DTR      |                     |   |

| L3  | 70  | J7 <sup>(1)</sup>  | PX45 | 96     | VDDIO  | x3   | EBI - SDCK     |                   |                     |   |

| K4  | 74  | G6 <sup>(1)</sup>  | PX46 | 97     | VDDIO  | x2   | EBI - SDCKE    |                   |                     |   |

| D4  | 39  | E1 <sup>(1)</sup>  | PX47 | 98     | VDDIO  | x2   | EBI - NANDOE   | ADC - TRIGGER     | MCI - DATA[11]      |   |

| F5  | 41  |                    | PX48 | 99     | VDDIO  | x2   | EBI - ADDR[23] | USB - VBOF        | MCI - DATA[10]      |   |

| F4  | 43  |                    | PX49 | 100    | VDDIO  | x2   | EBI - CFRNW    | USB - ID          | MCI - DATA[9]       |   |

| G4  | 75  |                    | PX50 | 101    | VDDIO  | x2   | EBI - CFCE2    | TC1 - B2          | MCI - DATA[8]       |   |

| G5  | 77  |                    | PX51 | 102    | VDDIO  | x2   | EBI - CFCE1    | DMACA - DMAACK[0] | MCI - DATA[15]      |   |

| K7  | 87  |                    | PX52 | 103    | VDDIO  | x2   | EBI - NCS[3]   | DMACA - DMARQ[0]  | MCI - DATA[14]      |   |

| E4  | 42  | D4 <sup>(1)</sup>  | PX53 | 104    | VDDIO  | x2   | EBI - NCS[2]   |                   | MCI - DATA[13]      |   |

| E3  | 46  |                    | PX54 | 105    | VDDIO  | x2   | EBI - NWAIT    | USART3 - TXD      | MCI - DATA[12]      |   |

| J5  | 79  |                    | PX55 | 106    | VDDIO  | x2   | EBI - ADDR[22] | EIC - SCAN[3]     | USART2 - RXD        |   |

# Table 3-6.Signal Description List

| Signal Name | Function                               | Туре   | Active<br>Level | Comments                                                                                                                                                                                        |

|-------------|----------------------------------------|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMHS        | USB High Speed Data -                  | Analog |                 |                                                                                                                                                                                                 |

| DPHS        | USB High Speed Data +                  | Analog |                 |                                                                                                                                                                                                 |

| USB_VBIAS   | USB VBIAS reference                    | Analog |                 | Connect to the ground through a<br>6810 ohms (+/- 1%) resistor in<br>parallel with a 10pf capacitor.<br>If USB hi-speed feature is not<br>required, leave this pin<br>unconnected to save power |

| USB_VBUS    | USB VBUS signal                        | Output |                 |                                                                                                                                                                                                 |

| VBOF        | USB VBUS on/off bus power control port | Output |                 |                                                                                                                                                                                                 |

| ID          | ID Pin fo the USB bus                  | Input  |                 |                                                                                                                                                                                                 |

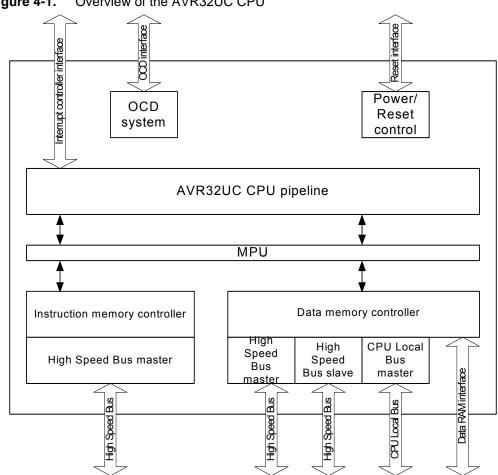

# 4. Processor and Architecture

Rev: 1.4.2.0

This chapter gives an overview of the AVR32UC CPU. AVR32UC is an implementation of the AVR32 architecture. A summary of the programming model, instruction set, and MPU is presented. For further details, see the AVR32 Architecture Manual and the AVR32UC Technical Reference Manual.

## 4.1 Features

- 32-bit load/store AVR32A RISC architecture

- 15 general-purpose 32-bit registers

- 32-bit Stack Pointer, Program Counter and Link Register reside in register file

- Fully orthogonal instruction set

- Privileged and unprivileged modes enabling efficient and secure Operating Systems

- Innovative instruction set together with variable instruction length ensuring industry leading code density

- DSP extention with saturating arithmetic, and a wide variety of multiply instructions

- 3-stage pipeline allows one instruction per clock cycle for most instructions

- Byte, halfword, word and double word memory access

- Multiple interrupt priority levels

- MPU allows for operating systems with memory protection

## 4.2 AVR32 Architecture

AVR32 is a high-performance 32-bit RISC microprocessor architecture, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption and high code density. In addition, the instruction set architecture has been tuned to allow a variety of microarchitectures, enabling the AVR32 to be implemented as low-, mid-, or high-performance processors. AVR32 extends the AVR family into the world of 32- and 64-bit applications.

Through a quantitative approach, a large set of industry recognized benchmarks has been compiled and analyzed to achieve the best code density in its class. In addition to lowering the memory requirements, a compact code size also contributes to the core's low power characteristics. The processor supports byte and halfword data types without penalty in code size and performance.

Memory load and store operations are provided for byte, halfword, word, and double word data with automatic sign- or zero extension of halfword and byte data. The C-compiler is closely linked to the architecture and is able to exploit code optimization features, both for size and speed.

In order to reduce code size to a minimum, some instructions have multiple addressing modes. As an example, instructions with immediates often have a compact format with a smaller immediate, and an extended format with a larger immediate. In this way, the compiler is able to use the format giving the smallest code size.

Another feature of the instruction set is that frequently used instructions, like add, have a compact format with two operands as well as an extended format with three operands. The larger format increases performance, allowing an addition and a data move in the same instruction in a single cycle. Load and store instructions have several different formats in order to reduce code size and speed up execution.

Figure 4-1. Overview of the AVR32UC CPU

### 4.3.1 Pipeline Overview

AVR32UC has three pipeline stages, Instruction Fetch (IF), Instruction Decode (ID), and Instruction Execute (EX). The EX stage is split into three parallel subsections, one arithmetic/logic (ALU) section, one multiply (MUL) section, and one load/store (LS) section.

Instructions are issued and complete in order. Certain operations require several clock cycles to complete, and in this case, the instruction resides in the ID and EX stages for the required number of clock cycles. Since there is only three pipeline stages, no internal data forwarding is required, and no data dependencies can arise in the pipeline.

Figure 4-2 on page 24 shows an overview of the AVR32UC pipeline stages.

| Table 4-3. | System Re | egisters (Continu | ied)                                   |

|------------|-----------|-------------------|----------------------------------------|

| Reg #      | Address   | Name              | Function                               |

| 26         | 104       | JAVA_LV3          | Unused in AVR32UC                      |

| 27         | 108       | JAVA_LV4          | Unused in AVR32UC                      |

| 28         | 112       | JAVA_LV5          | Unused in AVR32UC                      |

| 29         | 116       | JAVA_LV6          | Unused in AVR32UC                      |

| 30         | 120       | JAVA_LV7          | Unused in AVR32UC                      |

| 31         | 124       | JTBA              | Unused in AVR32UC                      |

| 32         | 128       | JBCR              | Unused in AVR32UC                      |

| 33-63      | 132-252   | Reserved          | Reserved for future use                |

| 64         | 256       | CONFIG0           | Configuration register 0               |

| 65         | 260       | CONFIG1           | Configuration register 1               |

| 66         | 264       | COUNT             | Cycle Counter register                 |

| 67         | 268       | COMPARE           | Compare register                       |

| 68         | 272       | TLBEHI            | Unused in AVR32UC                      |

| 69         | 276       | TLBELO            | Unused in AVR32UC                      |

| 70         | 280       | PTBR              | Unused in AVR32UC                      |

| 71         | 284       | TLBEAR            | Unused in AVR32UC                      |

| 72         | 288       | MMUCR             | Unused in AVR32UC                      |

| 73         | 292       | TLBARLO           | Unused in AVR32UC                      |

| 74         | 296       | TLBARHI           | Unused in AVR32UC                      |

| 75         | 300       | PCCNT             | Unused in AVR32UC                      |

| 76         | 304       | PCNT0             | Unused in AVR32UC                      |

| 77         | 308       | PCNT1             | Unused in AVR32UC                      |

| 78         | 312       | PCCR              | Unused in AVR32UC                      |

| 79         | 316       | BEAR              | Bus Error Address Register             |

| 80         | 320       | MPUAR0            | MPU Address Register region 0          |

| 81         | 324       | MPUAR1            | MPU Address Register region 1          |

| 82         | 328       | MPUAR2            | MPU Address Register region 2          |

| 83         | 332       | MPUAR3            | MPU Address Register region 3          |

| 84         | 336       | MPUAR4            | MPU Address Register region 4          |

| 85         | 340       | MPUAR5            | MPU Address Register region 5          |

| 86         | 344       | MPUAR6            | MPU Address Register region 6          |

| 87         | 348       | MPUAR7            | MPU Address Register region 7          |

| 88         | 352       | MPUPSR0           | MPU Privilege Select Register region 0 |

| 89         | 356       | MPUPSR1           | MPU Privilege Select Register region 1 |

| 90         | 360       | MPUPSR2           | MPU Privilege Select Register region 2 |

| 91         | 364       | MPUPSR3           | MPU Privilege Select Register region 3 |

Table 4-3.

System Registers (Continued)

# AT32UC3A3

| Priority | Handler Address        | Name                        | Event source   | Stored Return Address           |

|----------|------------------------|-----------------------------|----------------|---------------------------------|

| 1        | 0x8000_0000            | Reset                       | External input | Undefined                       |

| 2        | Provided by OCD system | OCD Stop CPU                | OCD system     | First non-completed instruction |

| 3        | EVBA+0x00              | Unrecoverable exception     | Internal       | PC of offending instruction     |

| 4        | EVBA+0x04              | TLB multiple hit            | MPU            |                                 |

| 5        | EVBA+0x08              | Bus error data fetch        | Data bus       | First non-completed instruction |

| 6        | EVBA+0x0C              | Bus error instruction fetch | Data bus       | First non-completed instruction |

| 7        | EVBA+0x10              | NMI                         | External input | First non-completed instruction |

| 8        | Autovectored           | Interrupt 3 request         | External input | First non-completed instruction |

| 9        | Autovectored           | Interrupt 2 request         | External input | First non-completed instruction |

| 10       | Autovectored           | Interrupt 1 request         | External input | First non-completed instruction |

| 11       | Autovectored           | Interrupt 0 request         | External input | First non-completed instruction |

| 12       | EVBA+0x14              | Instruction Address         | CPU            | PC of offending instruction     |

| 13       | EVBA+0x50              | ITLB Miss                   | MPU            |                                 |

| 14       | EVBA+0x18              | ITLB Protection             | MPU            | PC of offending instruction     |

| 15       | EVBA+0x1C              | Breakpoint                  | OCD system     | First non-completed instruction |

| 16       | EVBA+0x20              | Illegal Opcode              | Instruction    | PC of offending instruction     |

| 17       | EVBA+0x24              | Unimplemented instruction   | Instruction    | PC of offending instruction     |

| 18       | EVBA+0x28              | Privilege violation         | Instruction    | PC of offending instruction     |

| 19       | EVBA+0x2C              | Floating-point              | UNUSED         |                                 |

| 20       | EVBA+0x30              | Coprocessor absent          | Instruction    | PC of offending instruction     |

| 21       | EVBA+0x100             | Supervisor call             | Instruction    | PC(Supervisor Call) +2          |

| 22       | EVBA+0x34              | Data Address (Read)         | CPU            | PC of offending instruction     |

| 23       | EVBA+0x38              | Data Address (Write)        | CPU            | PC of offending instruction     |

| 24       | EVBA+0x60              | DTLB Miss (Read)            | MPU            |                                 |

| 25       | EVBA+0x70              | DTLB Miss (Write)           | MPU            |                                 |

| 26       | EVBA+0x3C              | DTLB Protection (Read)      | MPU            | PC of offending instruction     |

| 27       | EVBA+0x40              | DTLB Protection (Write)     | MPU            | PC of offending instruction     |

| 28       | EVBA+0x44              | DTLB Modified               | UNUSED         |                                 |

# Table 4-4. Priority and Handler Addresses for Events

### **Table 5-2.**Peripheral Address Mapping

| pheral Addres | s mapping |                                                                     |

|---------------|-----------|---------------------------------------------------------------------|

| 0xFFFF0C00    | РМ        | Power Manager - PM                                                  |

| 0xFFFF0D00    | RTC       | Real Time Counter - RTC                                             |

| 0xFFFF0D30    | WDT       | Watchdog Timer - WDT                                                |

| 0xFFFF0D80    | EIC       | External Interrupt Controller - EIC                                 |

| 0xFFFF1000    | GPIO      | General Purpose Input/Output Controller - GPIO                      |

| 0xFFFF1400    | USART0    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART0 |

| 0xFFFF1800    | USART1    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART1 |

| 0xFFFF1C00    | USART2    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART2 |

| 0xFFFF2000    | USART3    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART3 |

| 0xFFFF2400    | SPI0      | Serial Peripheral Interface - SPI0                                  |

| 0xFFFF2800    | SPI1      | Serial Peripheral Interface - SPI1                                  |

| 0xFFFF2C00    | TWIMO     | Two-wire Master Interface - TWIM0                                   |

| 0xFFFF3000    | TWIM1     | Two-wire Master Interface - TWIM1                                   |

| 0xFFFF3400    | SSC       | Synchronous Serial Controller - SSC                                 |

| 0xFFFF3800    | TC0       | Timer/Counter - TC0                                                 |

| 0xFFFF3C00    | ADC       | Analog to Digital Converter - ADC                                   |

| 0xFFFF4000    | ABDAC     | Audio Bitstream DAC - ABDAC                                         |

| 0xFFFF4400    | TC1       | Timer/Counter - TC1                                                 |

|               |           |                                                                     |

| Port | Register                             | Mode   | Local Bus<br>Address | Access     |

|------|--------------------------------------|--------|----------------------|------------|

| 2    | Output Driver Enable Register (ODER) | WRITE  | 0x40000240           | Write-only |

|      |                                      | SET    | 0x40000244           | Write-only |

|      |                                      | CLEAR  | 0x40000248           | Write-only |

|      |                                      | TOGGLE | 0x4000024C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000250           | Write-only |

|      |                                      | SET    | 0x40000254           | Write-only |

|      |                                      | CLEAR  | 0x40000258           | Write-only |

|      |                                      | TOGGLE | 0x4000025C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000260           | Read-only  |

| 3    | Output Driver Enable Register (ODER) | WRITE  | 0x40000340           | Write-only |

|      |                                      | SET    | 0x40000344           | Write-only |

|      |                                      | CLEAR  | 0x40000348           | Write-only |

|      |                                      | TOGGLE | 0x4000034C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000350           | Write-only |

|      |                                      | SET    | 0x40000354           | Write-only |

|      |                                      | CLEAR  | 0x40000358           | Write-only |

|      |                                      | TOGGLE | 0x4000035C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000360           | Read-only  |

Table 5-3.

Local Bus Mapped GPIO Registers

# 7.7 System Clock Characteristics

These parameters are given in the following conditions:

• V<sub>DDCORE</sub> = 1.8V

### 7.7.1 CPU/HSB Clock Characteristics

Table 7-14.

Core Clock Waveform Parameters

| Symbol                  | Parameter           | Conditions                         | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------------------------------|------|------|------|------|

| 1/(t <sub>CPCPU</sub> ) | CPU Clock Frequency | -40°C < Ambient Temperature < 70°C |      |      | 84   | MHz  |

| 1/(t <sub>CPCPU</sub> ) | CPU Clock Frequency | -40°C < Ambient Temperature < 85°C |      |      | 66   | MHz  |

### 7.7.2 PBA Clock Characteristics

| TADIE 1-13. FDA CIUCK WAVEIUIIII FAIAIIIEIEIS | Table 7-15. | PBA Clock Waveform Parameters |

|-----------------------------------------------|-------------|-------------------------------|

|-----------------------------------------------|-------------|-------------------------------|

| Symbol                  | Parameter           | Conditions                         | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------------------------------|------|------|------|------|

| 1/(t <sub>CPPBA</sub> ) | PBA Clock Frequency | -40°C < Ambient Temperature < 70°C |      |      | 84   | MHz  |

| 1/(t <sub>CPPBA</sub> ) | PBA Clock Frequency | -40°C < Ambient Temperature < 85°C |      |      | 66   | MHz  |

### 7.7.3 PBB Clock Characteristics

### Table 7-16. PBB Clock Waveform Parameters

| Symbol                  | Parameter           | Conditions                         | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|------------------------------------|------|------|------|------|

| 1/(t <sub>CPPBB</sub> ) | PBB Clock Frequency | -40°C < Ambient Temperature < 70°C |      |      | 84   | MHz  |

| 1/(t <sub>CPPBB</sub> ) | PBB Clock Frequency | -40°C < Ambient Temperature < 85°C |      |      | 66   | MHz  |

### 7.8.3 Main Oscillators

| Table 7-19. Main Oscillators | Characteristics |

|------------------------------|-----------------|

|------------------------------|-----------------|

| Symbol                   | Parameter                                       | Conditions                                                                                                                                   | Min.                | Тур.                  | Max.                | Unit |

|--------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|---------------------|------|

|                          |                                                 | External clock on XIN                                                                                                                        |                     |                       | 50                  | MHz  |

| 1/(t <sub>CPMAIN</sub> ) | Oscillator Frequency                            | Crystal                                                                                                                                      | 0.4                 |                       | 20                  | MHz  |

| $C_{L1}, C_{L2}$         | Internal Load Capacitance ( $C_{L1} = C_{L2}$ ) |                                                                                                                                              |                     | 7                     |                     | pF   |

| ESR                      | Crystal Equivalent Series Resistance            |                                                                                                                                              |                     |                       | 75                  | Ω    |

|                          | Duty Cycle                                      |                                                                                                                                              | 40                  | 50                    | 60                  | %    |

| t <sub>ST</sub>          | Startup Time                                    | f = 400 KHz<br>f = 8 MHz<br>f = 16 MHz<br>f = 20 MHz                                                                                         |                     | 25<br>4<br>1.4<br>1   |                     | ms   |

| t <sub>CH</sub>          | XIN Clock High Half-period                      |                                                                                                                                              | 0.4 t <sub>CP</sub> |                       | 0.6 t <sub>CP</sub> |      |

| t <sub>CL</sub>          | XIN Clock Low Half-period                       |                                                                                                                                              | 0.4 t <sub>CP</sub> |                       | 0.6 t <sub>CP</sub> |      |

| C <sub>IN</sub>          | XIN Input Capacitance                           |                                                                                                                                              |                     | 7                     |                     | pF   |

| I <sub>osc</sub>         | Current Consumption                             | Active mode at 400 KHz. Gain = G0<br>Active mode at 8 MHz. Gain = G1<br>Active mode at 16 MHz. Gain = G2<br>Active mode at 20 MHz. Gain = G3 |                     | 30<br>45<br>95<br>205 |                     | μA   |

# 7.8.4 Phase Lock Loop (PLL0, PLL1)

### Table 7-20. PLL Characteristics

| Symbol              | Parameter                             | Conditions                 | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------|----------------------------|------|------|------|------|

| F <sub>OUT</sub>    | VCO Output Frequency                  |                            | 80   |      | 240  | MHz  |

| F <sub>IN</sub>     | Input Frequency (after input divider) |                            | 4    |      | 16   | MHz  |

| I <sub>PLL</sub> Cu | Current Consumption                   | Active mode (Fout=80 MHz)  |      | 250  |      | μA   |

|                     |                                       | Active mode (Fout=240 MHz) |      | 600  |      | μA   |

# 7.8.5 USB Hi-Speed Phase Lock Loop

### Table 7-21. PLL Characteristics

| Symbol                | Parameter                                                                                 | Conditions                | Min. | Тур. | Max. | Unit |

|-----------------------|-------------------------------------------------------------------------------------------|---------------------------|------|------|------|------|

| F <sub>OUT</sub>      | VCO Output Frequency                                                                      |                           |      | 480  |      | MHz  |

| F <sub>IN</sub>       | Input Frequency                                                                           |                           |      | 12   |      | MHz  |

| Delta F <sub>IN</sub> | Input Frequency Accuracy (applicable<br>to Clock signal on XIN or to Quartz<br>tolerance) |                           | -500 |      | +500 | ppm  |

| I <sub>PLL</sub>      | Current Consumption                                                                       | Active mode @480MHz @1.8V |      | 2.5  |      | mA   |

### Table 7-29.Dynamic Power Consumption

| Symbol               | Parameter                             | Conditions                              | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------------------|-----------------------------------------|------|------|------|------|

|                      | HS Transceiver current consumption    | HS transmission                         |      | 47   | 60   | mA   |

|                      | HS Transceiver current consumption    | HS reception                            |      | 18   | 27   | mA   |

| I <sub>vddutmi</sub> | FS/HS Transceiver current consumption | FS transmission 0m cable <sup>(1)</sup> |      | 4    | 6    | mA   |

|                      | FS/HS Transceiver current consumption | FS transmission 5m cable                |      | 26   | 30   | mA   |

|                      | FS/HS Transceiver current consumption | FS reception                            |      | 3    | 4.5  | mA   |

1. Including 1 mA due to Pull-up/Pull-down current consumption.

### 34.5.5 USB High Speed Design Guidelines

In order to facilitate hardware design, Atmel provides an application note on www.atmel.com.

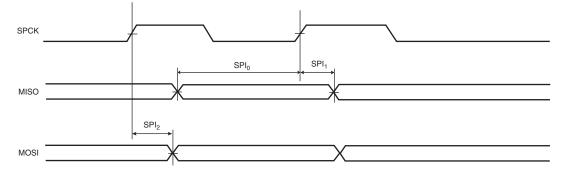

# 7.13 SPI Characteristics

# 8.3 Soldering Profile

Table 8-5 gives the recommended soldering profile from J-STD-20.

| Table 8-5. | Soldering Profile |

|------------|-------------------|

|------------|-------------------|

| Profile Feature                            | Green Package   |

|--------------------------------------------|-----------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/Second max  |

| Preheat Temperature 175°C ±25°C            | 150-200°C       |

| Time Maintained Above 217°C                | 60-150 seconds  |

| Time within 5°C of Actual Peak Temperature | 30 seconds      |

| Peak Temperature Range                     | 260 (+0/-5°C)   |

| Ramp-down Rate                             | 6°C/Second max. |

| Time 25°C to Peak Temperature              | 8 minutes max   |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

|         |         | <b>Fix/Workaround</b><br>Before going to sleep modes where the system RC oscillator is stopped, make sure that the factor between the CPU/HSB and PBx frequencies is less than or equal to 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.2.9  | PDCA    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | <b>PCONTROL.CHxRES is non-functional</b><br>PCONTROL.CHxRES is non-functional. Counters are reset at power-on, and cannot be<br>reset by software.<br><b>Fix/Workaround</b><br>Software needs to keep history of performance counters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |         | <b>Transfer error will stall a transmit peripheral handshake interface</b><br>If a transfer error is encountered on a channel transmitting to a peripheral, the peripheral<br>handshake of the active channel will stall and the PDCA will not do any more transfers on<br>the affected peripheral handshake interface.<br><b>Fix/Workaround</b><br>Disable and then enable the peripheral after the transfer error.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10.2.10 | AES     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | URAD (Unspecified Register Access Detection Status) does not detect read accesses<br>to the write-only KEYW[58]R registers<br>Fix/Workaround<br>None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10.2.11 | HMATRIX |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | In the PRAS and PRBS registers, the MxPR fields are only two bits<br>In the PRAS and PRBS registers, the MxPR fields are only two bits wide, instead of four bits.<br>The unused bits are undefined when reading the registers.<br>Fix/Workaround<br>Mask undefined bits when reading PRAS and PRBS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10.2.12 | тwiм    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | <ul> <li>TWIM SR.IDLE goes high immediately when NAK is received</li> <li>When a NAK is received and there is a non-zero number of bytes to be transmitted, SR.IDLE goes high immediately and does not wait for the STOP condition to be sent. This does not cause any problem just by itself, but can cause a problem if software waits for SR.IDLE to go high and then immediately disables the TWIM by writing a one to CR.MDIS. Disabling the TWIM causes the TWCK and TWD pins to go high immediately, so the STOP condition will not be transmitted correctly.</li> <li>Fix/Workaround</li> <li>If possible, do not disable the TWIM. If it is absolutely necessary to disable the TWIM, there must be a software delay of at least two TWCK periods between the detection of SR.IDLE==1 and the disabling of the TWIM.</li> </ul> |

|         |         | <b>TWIM TWALM polarity is wrong</b><br>The TWALM signal in the TWIM is active high instead of active low.<br><b>Fix/Workaround</b><br>Use an external inverter to invert the signal going into the TWIM. When using both TWIM<br>and TWIS on the same pins, the TWALM cannot be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# AT32UC3A3

|         |      | SMBALERT bit may be set after reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |      | The SMBus Alert (SMBALERT) bit in the Status Register (SR) might be erroneously set after                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |      | system reset. Fix/Workaround                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |      | After system reset, clear the SR.SMBALERT bit before commencing any TWI transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.2.13 | TWIS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |      | Clearing the NAK bit before the BTF bit is set locks up the TWI bus<br>When the TWIS is in transmit mode, clearing the NAK Received (NAK) bit of the Status Reg-<br>ister (SR) before the end of the Acknowledge/Not Acknowledge cycle will cause the TWIS to<br>attempt to continue transmitting data, thus locking up the bus.<br>Fix/Workaround<br>Clear SR.NAK only after the Byte Transfer Finished (BTF) bit of the same register has been<br>set.                                                                                                        |

|         |      | <b>TWIS stretch on Address match error</b><br>When the TWIS stretches TWCK due to a slave address match, it also holds TWD low for<br>the same duration if it is to be receiving data. When TWIS releases TWCK, it releases TWD<br>at the same time. This can cause a TWI timing violation.<br><b>Fix/Workaround</b><br>None.                                                                                                                                                                                                                                   |

| 10.2.14 | MCI  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |      | MCI_CLK features is not available on PX12, PX13 and PX40<br>Fix/Workaround<br>MCI_CLK feature is available on PA27 only.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |      | The busy signal of the responses R1b is not taken in account for CMD12 STOP TRANSFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |      | It is not possible to know the busy status of the card during the response (R1b) for the com-<br>mands CMD12.<br>Fix/Workaround                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |      | The card busy line should be polled through the GPIO Input Value register (IVR) for com-<br>mands CMD12.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10.2.15 | SSC  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |      | <ul> <li>Frame Synchro and Frame Synchro Data are delayed by one clock cycle</li> <li>The frame synchro and the frame synchro data are delayed from 1 SSC_CLOCK when:</li> <li>Clock is CKDIV</li> <li>The START is selected on either a frame synchro edge or a level</li> <li>Frame synchro data is enabled</li> <li>Transmit clock is gated on output (through CKO field)</li> <li>Fix/Workaround</li> <li>Transmit or receive CLOCK must not be gated (by the mean of CKO field) when START condition is performed on a generated frame synchro.</li> </ul> |

### 10.3.5 ADC

#### Sleep Mode activation needs additional A to D conversion

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.

#### **Fix/Workaround**

Activate the sleep mode in the mode register and then perform an AD conversion.

#### 10.3.6 USART

#### **ISO7816 info register US\_NER cannot be read** The NER register always returns zero.

Fix/Workaround None.

### The LIN ID is not transmitted in mode PDCM='0' Fix/Workaround

Using USART in mode LIN master with the PDCM bit = '0', the LINID written at the first address of the transmit buffer is not used. The LINID must be written in the LINIR register, after the configuration and start of the PDCA transfer. Writing the LINID in the LINIR register will start the transfer whenever the PDCA transfer is ready.

# The LINID interrupt is only available for the header reception and not available for the header transmission Fix/Workaround None.

USART LIN mode is not functional with the PDCA if PDCM bit in LINMR register is set to 1

If a PDCA transfer is initiated in USART LIN mode with PDCM bit set to 1, the transfer never starts.

#### Fix/Workaround

Only use PDCM=0 configuration with the PDCA transfer.

#### The RTS output does not function correctly in hardware handshaking mode

The RTS signal is not generated properly when the USART receives data in hardware handshaking mode. When the Peripheral DMA receive buffer becomes full, the RTS output should go high, but it will stay low.

#### Fix/Workaround

Do not use the hardware handshaking mode of the USART. If it is necessary to drive the RTS output high when the Peripheral DMA receive buffer becomes full, use the normal mode of the USART. Configure the Peripheral DMA Controller to signal an interrupt when the receive buffer is full. In the interrupt handler code, write a one to the RTSDIS bit in the USART Control Register (CR). This will drive the RTS output high. After the next DMA transfer is started and a receive buffer is available, write a one to the RTSEN bit in the USART CR so that RTS will be driven low.

#### ISO7816 Mode T1: RX impossible after any TX

RX impossible after any TX. **Fix/Workaround** SOFT\_RESET on RX+ Config US\_MR + Config\_US\_CR.

|         |        | Fix/Workaround<br>None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.3.14 | MCI    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |        | <ul> <li>The busy signal of the responses R1b is not taken in account for CMD12 STOP_TRANSFER</li> <li>It is not possible to know the busy status of the card during the response (R1b) for the commands CMD12.</li> <li>Fix/Workaround</li> <li>The card busy line should be polled through the GPIO Input Value register (IVR) for commands CMD12.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10.3.15 | SSC    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |        | <ul> <li>Frame Synchro and Frame Synchro Data are delayed by one clock cycle</li> <li>The frame synchro and the frame synchro data are delayed from 1 SSC_CLOCK when:</li> <li>Clock is CKDIV</li> <li>The START is selected on either a frame synchro edge or a level</li> <li>Frame synchro data is enabled</li> <li>Transmit clock is gated on output (through CKO field)</li> <li>Fix/Workaround</li> <li>Transmit or receive CLOCK must not be gated (by the mean of CKO field) when START condition is performed on a generated frame synchro.</li> </ul>                                                                                                                                                                                                                                      |

| 10.3.16 | FLASHC |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |        | <ul> <li>Corrupted read in flash may happen after fuses write or erase operations (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands)</li> <li>After a flash fuse write or erase operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands), reading (data read or code fetch) in flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.</li> <li>Fix/Workaround</li> <li>Before the flash fuse write or erase operation, enable the flash high speed mode (FLASHC HSEN command). The flash fuse write or erase operations (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands) must be issued from RAM or through the EBI. After these commands, read 3 times one flash page initialized to 00h. Disable the flash high</li> </ul> |

speed mode (FLASHC HSDIS command). It is then possible to safely read or code fetch the

flash.