Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                       |

| Number of I/O              | 110                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.75V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 144-LQFP                                                                    |

| Supplier Device Package    | 144-LQFP (20x20)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a364s-alur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. Description

The AT32UC3A3/A4 is a complete System-On-Chip microcontroller based on the AVR32 UC RISC processor running at frequencies up to 84MHz. AVR32 UC is a high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption, high code density and high performance.

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern operating systems and real-time operating systems. Higher computation capabilities are achievable using a rich set of DSP instructions.

The AT32UC3A3/A4 incorporates on-chip Flash and SRAM memories for secure and fast access. 64 KBytes of SRAM are directly coupled to the AVR32 UC for performances optimization. Two blocks of 32 Kbytes SRAM are independently attached to the High Speed Bus Matrix, allowing real ping-pong management.

The Peripheral Direct Memory Access Controller (PDCA) enables data transfers between peripherals and memories without processor involvement. The PDCA drastically reduces processing overhead when transferring continuous and large data streams.

The Power Manager improves design flexibility and security: the on-chip Brown-Out Detector monitors the power supply, the CPU runs from the on-chip RC oscillator or from one of external oscillator sources, a Real-Time Clock and its associated timer keeps track of the time.

The device includes two sets of three identical 16-bit Timer/Counter (TC) channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing and pulse width modulation. 16-bit channels are combined to operate as 32-bit channels.

The AT32UC3A3/A4 also features many communication interfaces for communication intensive applications like UART, SPI or TWI. The USART supports different communication modes, like SPI Mode and LIN Mode. Additionally, a flexible Synchronous Serial Controller (SSC) is available. The SSC provides easy access to serial communication protocols and audio standards like I2S.

The AT32UC3A3/A4 includes a powerfull External Bus Interface to interface all standard memory device like SRAM, SDRAM, NAND Flash or parallel interfaces like LCD Module.

The peripheral set includes a High Speed MCI for SDIO/SD/MMC and a hardware encryption module based on AES algorithm.

The device embeds a 10-bit ADC and a Digital Audio bistream DAC.

The Direct Memory Access controller (DMACA) allows high bandwidth data flows between high speed peripherals (USB, External Memories, MMC, SDIO, ...) and through high speed internal features (AES, internal memories).

The High-Speed (480MBit/s) USB 2.0 Device and Host interface supports several USB Classes at the same time thanks to the rich Endpoint configuration. The Embedded Host interface allows device like a USB Flash disk or a USB printer to be directly connected to the processor. This periphal has its own dedicated DMA and is perfect for Mass Storage application.

AT32UC3A3/A4 integrates a class 2+ Nexus 2.0 On-Chip Debug (OCD) System, with non-intrusive real-time trace, full-speed read/write memory access in addition to basic runtime control.

### 3.4 I/O Line Considerations

#### 3.4.1 JTAG Pins

TMS and TDI pins have pull-up resistors. TDO pin is an output, driven at up to VDDIO, and has no pull-up resistor.

#### 3.4.2 RESET\_N Pin

The RESET\_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIO. As the product integrates a power-on reset cell, the RESET\_N pin can be left unconnected in case no reset from the system needs to be applied to the product.

#### 3.4.3 TWI Pins

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation and inputs with inputs with spike filtering. When used as GPIO pins or used for other peripherals, the pins have the same characteristics as other GPIO pins.

#### 3.4.4 GPIO Pins

All the I/O lines integrate a programmable pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the I/O Controller. After reset, I/O lines default as inputs with pull-up resistors disabled, except when indicated otherwise in the column "Reset State" of the I/O Controller multiplexing tables.

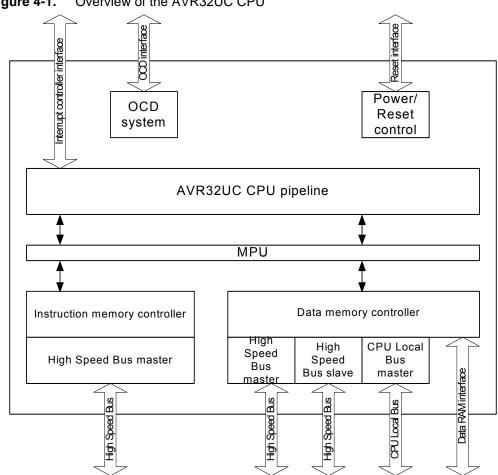

Figure 4-1. Overview of the AVR32UC CPU

#### 4.3.1 Pipeline Overview

AVR32UC has three pipeline stages, Instruction Fetch (IF), Instruction Decode (ID), and Instruction Execute (EX). The EX stage is split into three parallel subsections, one arithmetic/logic (ALU) section, one multiply (MUL) section, and one load/store (LS) section.

Instructions are issued and complete in order. Certain operations require several clock cycles to complete, and in this case, the instruction resides in the ID and EX stages for the required number of clock cycles. Since there is only three pipeline stages, no internal data forwarding is required, and no data dependencies can arise in the pipeline.

Figure 4-2 on page 24 shows an overview of the AVR32UC pipeline stages.

All interrupt levels are by default disabled when debug state is entered, but they can individually be switched on by the monitor routine by clearing the respective mask bit in the status register.

Debug state can be entered as described in the AVR32UC Technical Reference Manual.

Debug state is exited by the retd instruction.

#### 4.4.4 System Registers

The system registers are placed outside of the virtual memory space, and are only accessible using the privileged *mfsr* and *mtsr* instructions. The table below lists the system registers specified in the AVR32 architecture, some of which are unused in AVR32UC. The programmer is responsible for maintaining correct sequencing of any instructions following a *mtsr* instruction. For detail on the system registers, refer to the *AVR32UC Technical Reference Manual*.

| Table 4-3. | System R | egisters |                                        |

|------------|----------|----------|----------------------------------------|

| Reg #      | Address  | Name     | Function                               |

| 0          | 0        | SR       | Status Register                        |

| 1          | 4        | EVBA     | Exception Vector Base Address          |

| 2          | 8        | ACBA     | Application Call Base Address          |

| 3          | 12       | CPUCR    | CPU Control Register                   |

| 4          | 16       | ECR      | Exception Cause Register               |

| 5          | 20       | RSR_SUP  | Unused in AVR32UC                      |

| 6          | 24       | RSR_INT0 | Unused in AVR32UC                      |

| 7          | 28       | RSR_INT1 | Unused in AVR32UC                      |

| 8          | 32       | RSR_INT2 | Unused in AVR32UC                      |

| 9          | 36       | RSR_INT3 | Unused in AVR32UC                      |

| 10         | 40       | RSR_EX   | Unused in AVR32UC                      |

| 11         | 44       | RSR_NMI  | Unused in AVR32UC                      |

| 12         | 48       | RSR_DBG  | Return Status Register for Debug mode  |

| 13         | 52       | RAR_SUP  | Unused in AVR32UC                      |

| 14         | 56       | RAR_INT0 | Unused in AVR32UC                      |

| 15         | 60       | RAR_INT1 | Unused in AVR32UC                      |

| 16         | 64       | RAR_INT2 | Unused in AVR32UC                      |

| 17         | 68       | RAR_INT3 | Unused in AVR32UC                      |

| 18         | 72       | RAR_EX   | Unused in AVR32UC                      |

| 19         | 76       | RAR_NMI  | Unused in AVR32UC                      |

| 20         | 80       | RAR_DBG  | Return Address Register for Debug mode |

| 21         | 84       | JECR     | Unused in AVR32UC                      |

| 22         | 88       | JOSP     | Unused in AVR32UC                      |

| 23         | 92       | JAVA_LV0 | Unused in AVR32UC                      |

| 24         | 96       | JAVA_LV1 | Unused in AVR32UC                      |

| 25         | 100      | JAVA_LV2 | Unused in AVR32UC                      |

Table 4-3.System Registers

| Table 4-3. | able 4-3. System Registers (Continued) |          |                                        |

|------------|----------------------------------------|----------|----------------------------------------|

| Reg #      | Address                                | Name     | Function                               |

| 26         | 104                                    | JAVA_LV3 | Unused in AVR32UC                      |

| 27         | 108                                    | JAVA_LV4 | Unused in AVR32UC                      |

| 28         | 112                                    | JAVA_LV5 | Unused in AVR32UC                      |

| 29         | 116                                    | JAVA_LV6 | Unused in AVR32UC                      |

| 30         | 120                                    | JAVA_LV7 | Unused in AVR32UC                      |

| 31         | 124                                    | JTBA     | Unused in AVR32UC                      |

| 32         | 128                                    | JBCR     | Unused in AVR32UC                      |

| 33-63      | 132-252                                | Reserved | Reserved for future use                |

| 64         | 256                                    | CONFIG0  | Configuration register 0               |

| 65         | 260                                    | CONFIG1  | Configuration register 1               |

| 66         | 264                                    | COUNT    | Cycle Counter register                 |

| 67         | 268                                    | COMPARE  | Compare register                       |

| 68         | 272                                    | TLBEHI   | Unused in AVR32UC                      |

| 69         | 276                                    | TLBELO   | Unused in AVR32UC                      |

| 70         | 280                                    | PTBR     | Unused in AVR32UC                      |

| 71         | 284                                    | TLBEAR   | Unused in AVR32UC                      |

| 72         | 288                                    | MMUCR    | Unused in AVR32UC                      |

| 73         | 292                                    | TLBARLO  | Unused in AVR32UC                      |

| 74         | 296                                    | TLBARHI  | Unused in AVR32UC                      |

| 75         | 300                                    | PCCNT    | Unused in AVR32UC                      |

| 76         | 304                                    | PCNT0    | Unused in AVR32UC                      |

| 77         | 308                                    | PCNT1    | Unused in AVR32UC                      |

| 78         | 312                                    | PCCR     | Unused in AVR32UC                      |

| 79         | 316                                    | BEAR     | Bus Error Address Register             |

| 80         | 320                                    | MPUAR0   | MPU Address Register region 0          |

| 81         | 324                                    | MPUAR1   | MPU Address Register region 1          |

| 82         | 328                                    | MPUAR2   | MPU Address Register region 2          |

| 83         | 332                                    | MPUAR3   | MPU Address Register region 3          |

| 84         | 336                                    | MPUAR4   | MPU Address Register region 4          |

| 85         | 340                                    | MPUAR5   | MPU Address Register region 5          |

| 86         | 344                                    | MPUAR6   | MPU Address Register region 6          |

| 87         | 348                                    | MPUAR7   | MPU Address Register region 7          |

| 88         | 352                                    | MPUPSR0  | MPU Privilege Select Register region 0 |

| 89         | 356                                    | MPUPSR1  | MPU Privilege Select Register region 1 |

| 90         | 360                                    | MPUPSR2  | MPU Privilege Select Register region 2 |

| 91         | 364                                    | MPUPSR3  | MPU Privilege Select Register region 3 |

Table 4-3.

System Registers (Continued)

## AT32UC3A3

|                 |                  | Size                                                            | Size                                                            | Size                                                       |

|-----------------|------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------|

| Device          | Start<br>Address | AT32UC3A3256S<br>AT32UC3A3256<br>AT32UC3A4256S<br>AT32UC3A4256S | AT32UC3A3128S<br>AT32UC3A3128<br>AT32UC3A4128S<br>AT32UC3A4128S | AT32UC3A364S<br>AT32UC3A364<br>AT32UC3A464S<br>AT32UC3A464 |

| HRAMC0          | 0xFF000000       | 32KByte                                                         | 32KByte                                                         | 32KByte                                                    |

| HRAMC1          | 0xFF008000       | 32KByte                                                         | 32KByte                                                         | 32KByte                                                    |

| HSB-PB Bridge A | 0xFFFF0000       | 64KByte                                                         | 64KByte                                                         | 64KByte                                                    |

| HSB-PB Bridge B | 0xFFFE0000       | 64KByte                                                         | 64KByte                                                         | 64KByte                                                    |

Table 5-1.

AT32UC3A3A4 Physical Memory Map

## 5.3 Peripheral Address Map

## Table 5-2. Peripheral Address Mapping

| Address    |         | Peripheral Name                                           |

|------------|---------|-----------------------------------------------------------|

| 0xFF100000 | DMACA   | DMA Controller - DMACA                                    |

| 0xFFFD0000 | AES     | Advanced Encryption Standard - AES                        |

| 0xFFFE0000 | USB     | USB 2.0 Device and Host Interface - USB                   |

| 0xFFFE1000 | HMATRIX | HSB Matrix - HMATRIX                                      |

| 0xFFFE1400 | FLASHC  | Flash Controller - FLASHC                                 |

| 0xFFFE1C00 | SMC     | Static Memory Controller - SMC                            |

| 0xFFFE2000 | SDRAMC  | SDRAM Controller - SDRAMC                                 |

| 0xFFFE2400 | ECCHRS  | Error code corrector Hamming and Reed Solomon -<br>ECCHRS |

| 0xFFFE2800 | BUSMON  | Bus Monitor module - BUSMON                               |

| 0xFFFE4000 | MCI     | Mulitmedia Card Interface - MCI                           |

| 0xFFFE8000 | MSI     | Memory Stick Interface - MSI                              |

| 0xFFFF0000 | PDCA    | Peripheral DMA Controller - PDCA                          |

| 0xFFFF0800 | INTC    | Interrupt controller - INTC                               |

| Port | Register                             | Mode   | Local Bus<br>Address | Access     |

|------|--------------------------------------|--------|----------------------|------------|

| 2    | Output Driver Enable Register (ODER) | WRITE  | 0x40000240           | Write-only |

|      |                                      | SET    | 0x40000244           | Write-only |

|      |                                      | CLEAR  | 0x40000248           | Write-only |

|      |                                      | TOGGLE | 0x4000024C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000250           | Write-only |

|      |                                      | SET    | 0x40000254           | Write-only |

|      |                                      | CLEAR  | 0x40000258           | Write-only |

|      |                                      | TOGGLE | 0x4000025C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000260           | Read-only  |

| 3    | Output Driver Enable Register (ODER) | WRITE  | 0x40000340           | Write-only |

|      |                                      | SET    | 0x40000344           | Write-only |

|      |                                      | CLEAR  | 0x40000348           | Write-only |

|      |                                      | TOGGLE | 0x4000034C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000350           | Write-only |

|      |                                      | SET    | 0x40000354           | Write-only |

|      |                                      | CLEAR  | 0x40000358           | Write-only |

|      |                                      | TOGGLE | 0x4000035C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000360           | Read-only  |

Table 5-3.

Local Bus Mapped GPIO Registers

## 6. Boot Sequence

This chapter summarizes the boot sequence of the AT32UC3A3/A4. The behavior after powerup is controlled by the Power Manager. For specific details, refer to Section 7. "Power Manager (PM)" on page 86.

### 6.1 Starting of Clocks

After power-up, the device will be held in a reset state by the Power-On Reset circuitry, until the power has stabilized throughout the device. Once the power has stabilized, the device will use the internal RC Oscillator as clock source.

On system start-up, the PLLs are disabled. All clocks to all modules are running. No clocks have a divided frequency, all parts of the system receives a clock with the same frequency as the internal RC Oscillator.

### 6.2 Fetching of Initial Instructions

After reset has been released, the AVR32 UC CPU starts fetching instructions from the reset address, which is 0x8000\_0000. This address points to the first address in the internal Flash.

The internal Flash uses VDDIO voltage during read and write operations. BOD33 monitors this voltage and maintains the device under reset until VDDIO reaches the minimum voltage, preventing any spurious execution from flash.

The code read from the internal Flash is free to configure the system to use for example the PLLs, to divide the frequency of the clock routed to some of the peripherals, and to gate the clocks to unused peripherals.

When powering up the device, there may be a delay before the voltage has stabilized, depending on the rise time of the supply used. The CPU can start executing code as soon as the supply is above the POR threshold, and before the supply is stable. Before switching to a high-speed clock source, the user should use the BOD to make sure the VDDCORE is above the minimumlevel (1.62V).

## 7. Electrical Characteristics

## 7.1 Absolute Maximum Ratings\*

| Operating Temperature40°C to +85°C                            |

|---------------------------------------------------------------|

| Storage Temperature60°C to +150°C                             |

| Voltage on Input Pin<br>with respect to Ground0.3V to 3.6V    |

| Maximum Operating Voltage (VDDCORE) 1.95V                     |

| Maximum Operating Voltage (VDDIO)                             |

| Total DC Output Current on all I/O Pin<br>for TQFP144 package |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 7.5.4 RESET\_N Characteristics

## Table 7-11. RESET\_N Waveform Parameters

| Symbol             | Parameter                   | Conditions | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------|------------|------|------|------|------|

| t <sub>RESET</sub> | RESET_N minimum pulse width |            | 10   |      |      | ns   |

### Table 7-32. SMC Read Signals with no Hold Settings

| Symbol            | Parameter                      | Min.        | Unit |  |  |

|-------------------|--------------------------------|-------------|------|--|--|

|                   | NRD Controlled (REA            | D_MODE = 1) |      |  |  |

| SMC <sub>19</sub> | Data Setup before NRD High     | 13.7        | ns   |  |  |

| SMC <sub>20</sub> | Data Hold after NRD High       | 1           | ns   |  |  |

|                   | NRD Controlled (READ_MODE = 0) |             |      |  |  |

| SMC <sub>21</sub> | Data Setup before NCS High     | 13.3        | ns   |  |  |

| SMC <sub>22</sub> | Data Hold after NCS High       | 0           | ns   |  |  |

Table 7-33.

SMC Write Signals with Hold Settings

| Symbol            | Parameter                                    | Min.                                                             | Unit |

|-------------------|----------------------------------------------|------------------------------------------------------------------|------|

|                   | NRD Controlled (RE                           | AD_MODE = 1)                                                     |      |

| SMC <sub>23</sub> | Data Out Valid before NWE High               | (nwe pulse length - 1) * t <sub>CPSMC</sub> - 0.9                | ns   |

| SMC <sub>24</sub> | Data Out Valid after NWE High <sup>(1)</sup> | nwe hold length * t <sub>CPSMC</sub> - 6                         | ns   |

| SMC <sub>25</sub> | NWE High to NBS0/A0 Change <sup>(1)</sup>    | nwe hold length * t <sub>CPSMC</sub> - 1.9                       | ns   |

| SMC <sub>26</sub> | NWE High to NBS1 Change <sup>(1)</sup>       | nwe hold length * t <sub>CPSMC</sub> - 1.9                       | ns   |

| SMC <sub>29</sub> | NWE High to A1 Change <sup>(1)</sup>         | nwe hold length * t <sub>CPSMC</sub> - 1.9                       | ns   |

| SMC <sub>31</sub> | NWE High to A2 - A23 Change <sup>(1)</sup>   | nwe hold length * t <sub>CPSMC</sub> - 1.7                       | ns   |

| SMC <sub>32</sub> | NWE High to NCS Inactive <sup>(1)</sup>      | (nwe hold length - ncs wr hold length)* t <sub>CPSMC</sub> - 2.9 | ns   |

| SMC <sub>33</sub> | NWE Pulse Width                              | nwe pulse length * t <sub>CPSMC</sub> - 0.9                      | ns   |

|                   | NRD Controlled (RE                           | AD_MODE = 0)                                                     |      |

| SMC <sub>34</sub> | Data Out Valid before NCS High               | (ncs wr pulse length - 1)* t <sub>CPSMC</sub> - 4.6              | ns   |

| SMC <sub>35</sub> | Data Out Valid after NCS High <sup>(1)</sup> | ncs wr hold length * t <sub>CPSMC</sub> - 5.8                    | ns   |

| SMC <sub>36</sub> | NCS High to NWE Inactive <sup>(1)</sup>      | (ncs wr hold length - nwe hold length)* t <sub>CPSMC</sub> - 0.6 | ns   |

Note: 1. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs wr hold length" or "nwe hold length"

| Table 7-34. | SMC Write Signals with No Hold Settings (NWE Controlled only) |

|-------------|---------------------------------------------------------------|

|             |                                                               |

| Symbol            | Parameter                    | Min. | Unit |

|-------------------|------------------------------|------|------|

| SMC <sub>37</sub> | NWE Rising to A2-A25 Valid   | 5.4  | ns   |

| SMC <sub>38</sub> | NWE Rising to NBS0/A0 Valid  | 5    | ns   |

| SMC <sub>39</sub> | NWE Rising to NBS1 Change    | 5    | ns   |

| SMC <sub>40</sub> | NWE Rising to A1/NBS2 Change | 5    | ns   |

| SMC <sub>41</sub> | NWE Rising to NBS3 Change    | 5    | ns   |

| SMC <sub>42</sub> | NWE Rising to NCS Rising     | 5.1  | ns   |

| Symbol               | Parameter                                | Conditions | Min. | Max. | Unit |

|----------------------|------------------------------------------|------------|------|------|------|

| SDRAMC <sub>13</sub> | Bank Change before SDCK Rising Edge      |            | 6.3  |      | ns   |

| SDRAMC <sub>14</sub> | Bank Change after SDCK Rising Edge       |            | 2.4  |      | ns   |

| SDRAMC <sub>15</sub> | CAS Low before SDCK Rising Edge          |            | 7.4  |      | ns   |

| SDRAMC <sub>16</sub> | CAS High after SDCK Rising Edge          |            | 1.9  |      | ns   |

| SDRAMC <sub>17</sub> | DQM Change before SDCK Rising Edge       |            | 6.4  |      | ns   |

| SDRAMC <sub>18</sub> | DQM Change after SDCK Rising Edge        |            | 2.2  |      | ns   |

| SDRAMC <sub>19</sub> | D0-D15 in Setup before SDCK Rising Edge  |            | 9    |      | ns   |

| SDRAMC <sub>20</sub> | D0-D15 in Hold after SDCK Rising Edge    |            | 0    |      | ns   |

| SDRAMC <sub>23</sub> | SDWE Low before SDCK Rising Edge         |            | 7.6  |      | ns   |

| SDRAMC <sub>24</sub> | SDWE High after SDCK Rising Edge         |            | 1.8  |      | ns   |

| SDRAMC <sub>25</sub> | D0-D15 Out Valid before SDCK Rising Edge |            | 7.1  |      | ns   |

| SDRAMC <sub>26</sub> | D0-D15 Out Valid after SDCK Rising Edge  |            | 1.5  |      | ns   |

### Table 7-36. SDRAM Clock Signal

Тур

40.3

9.5

28.5

6.9

31.1

6.9

TFBGA144

TFBGA144

VFBGA100

VFBGA100

Unit

°C/W

°C/W

°C/W

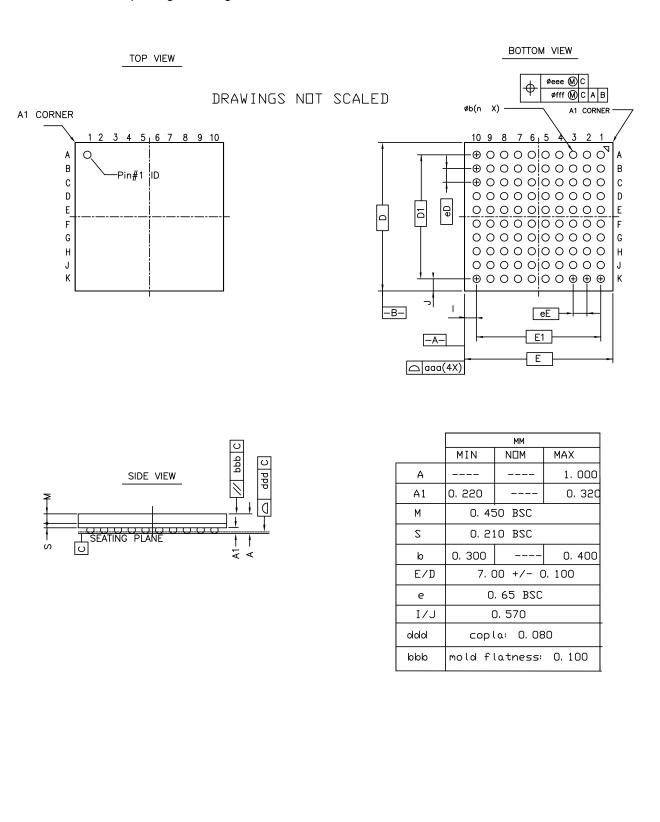

## 8. Mechanical Characteristics

## 8.1 Thermal Considerations

### 8.1.1 Thermal Data

Table 8-1 summarizes the thermal resistance data depending on the package.

| Symbol               | Parameter                              | Condition | Package |

|----------------------|----------------------------------------|-----------|---------|

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP144 |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP144 |

Junction-to-ambient thermal resistance

Junction-to-ambient thermal resistance

Junction-to-case thermal resistance

Junction-to-case thermal resistance

Table 8-1.Thermal Resistance Data

#### 8.1.2 Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

$$1. \quad T_J = T_A + (P_D \times \theta_{JA})$$

**2.**

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

where:

$\theta_{\mathsf{JA}}$

$\theta_{JC}$

$\theta_{\mathsf{JA}}$

$\theta_{\text{JC}}$

θ<sub>JA</sub> = package thermal resistance, Junction-to-ambient (°C/W), provided in Table 8-1 on page 68.

Still Air

Still Air

- $\theta_{JC}$  = package thermal resistance, Junction-to-case thermal resistance (°C/W), provided in Table 8-1 on page 68.

- $\theta_{HEAT SINK}$  = cooling device thermal resistance (°C/W), provided in the device datasheet.

- P<sub>D</sub> = device power consumption (W) estimated from data provided in the section "Regulator characteristics" on page 43.

- T<sub>A</sub> = ambient temperature (°C).

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

Figure 8-3. VFBGA-100 package drawing

## 9. Ordering Information

| Device        | Ordering Code      | Package        | Conditioning | Temperature Operating<br>Range |

|---------------|--------------------|----------------|--------------|--------------------------------|

| AT32UC3A3256S | AT32UC3A3256S-ALUT | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256S-ALUR | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256S-CTUT | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256S-CTUR | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A3256  | AT32UC3A3256-ALUT  | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256-ALUR  | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256-CTUT  | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256-CTUR  | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A3128S | AT32UC3A3128S-ALUT | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128S-ALUR | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128S-CTUT | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128S-CTUR | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A3128  | AT32UC3A3128-ALUT  | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128-ALUR  | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128-CTUT  | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128-CTUR  | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A364S  | AT32UC3A364S-ALUT  | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364S-ALUR  | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364S-CTUT  | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364S-CTUR  | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A364   | AT32UC3A364-ALUT   | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364-ALUR   | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364-CTUT   | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364-CTUR   | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4256S | AT32UC3A4256S-C1UT | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4256S-C1UR | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4256  | AT32UC3A4256-C1UT  | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4256-C1UR  | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4128S | AT32UC3A4128S-C1UT | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4128S-C1UR | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4128  | AT32UC3A4128-C1UT  | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4128-C1UR  | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A464S  | AT32UC3A464S-C1UT  | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A464S-C1UR  | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A464   | AT32UC3A464-C1UT   | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A464-C1UR   | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| 10.1.10 | AES     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |         | URAD (Unspecified Register Access Detection Status) does not detect read accesses<br>to the write-only KEYW[58]R registers<br>Fix/Workaround<br>None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10.1.11 | HMATRIX |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | In the PRAS and PRBS registers, the MxPR fields are only two bits<br>In the PRAS and PRBS registers, the MxPR fields are only two bits wide, instead of four bits.<br>The unused bits are undefined when reading the registers.<br>Fix/Workaround<br>Mask undefined bits when reading PRAS and PRBS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10.1.12 | тwim    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | <ul> <li>TWIM SR.IDLE goes high immediately when NAK is received</li> <li>When a NAK is received and there is a non-zero number of bytes to be transmitted, SR.IDLE goes high immediately and does not wait for the STOP condition to be sent. This does not cause any problem just by itself, but can cause a problem if software waits for SR.IDLE to go high and then immediately disables the TWIM by writing a one to CR.MDIS. Disabling the TWIM causes the TWCK and TWD pins to go high immediately, so the STOP condition will not be transmitted correctly.</li> <li>Fix/Workaround</li> <li>If possible, do not disable the TWIM. If it is absolutely necessary to disable the TWIM, there must be a software delay of at least two TWCK periods between the detection of SR.IDLE==1 and the disabling of the TWIM.</li> <li>TWIM TWALM polarity is wrong</li> <li>The TWALM signal in the TWIM is active high instead of active low.</li> <li>Fix/Workaround</li> <li>Use an external inverter to invert the signal going into the TWIM. When using both TWIM and TWIS on the same pins, the TWALM cannot be used.</li> </ul> |

|         |         | <ul> <li>SMBALERT bit may be set after reset</li> <li>The SMBus Alert (SMBALERT) bit in the Status Register (SR) might be erroneously set after system reset.</li> <li>Fix/Workaround</li> <li>After system reset, clear the SR.SMBALERT bit before commencing any TWI transfer.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.1.13 | TWIS    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | <b>Clearing the NAK bit before the BTF bit is set locks up the TWI bus</b><br>When the TWIS is in transmit mode, clearing the NAK Received (NAK) bit of the Status Reg-<br>ister (SR) before the end of the Acknowledge/Not Acknowledge cycle will cause the TWIS to<br>attempt to continue transmitting data, thus locking up the bus.<br><b>Fix/Workaround</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Clear SR.NAK only after the Byte Transfer Finished (BTF) bit of the same register has been set.

|         |         | <b>TWIS stretch on Address match error</b><br>When the TWIS stretches TWCK due to a slave address match, it also holds TWD low for<br>the same duration if it is to be receiving data. When TWIS releases TWCK, it releases TWD<br>at the same time. This can cause a TWI timing violation.<br><b>Fix/Workaround</b><br>None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.1.14 | SSC     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |         | <ul> <li>Frame Synchro and Frame Synchro Data are delayed by one clock cycle</li> <li>The frame synchro and the frame synchro data are delayed from 1 SSC_CLOCK when:</li> <li>Clock is CKDIV</li> <li>The START is selected on either a frame synchro edge or a level</li> <li>Frame synchro data is enabled</li> <li>Transmit clock is gated on output (through CKO field)</li> <li>Fix/Workaround</li> <li>Transmit or receive CLOCK must not be gated (by the mean of CKO field) when START condition is performed on a generated frame synchro.</li> </ul>                                                                                                                                                                                                                                                                                                                               |

| 10.1.15 | FLASHC  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |         | Corrupted read in flash may happen after fuses write or erase operations (FLASHC<br>LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands).<br>After a flash fuse write or erase operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB,<br>EAGPF commands), reading (data read or code fetch) in flash may fail. This may lead to an<br>exception or to other errors derived from this corrupted read access.<br><b>Fix/Workaround</b><br>Before the flash fuse write or erase operation, enable the flash high speed mode (FLASHC<br>HSEN command). The flash fuse write or erase operations (FLASHC LP, UP, WGPB,<br>EGPB, SSB, PGPFB, EAGPF commands) must be issued from RAM or through the EBI.<br>After these commands, read 3 times one flash page initialized to 00h. Disable the flash high<br>speed mode (FLASHC HSDIS command). It is then possible to safely read or code fetch the<br>flash. |

| 10.2 R  | lev. E  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10.2.1  | General | Devices cannot operate with CPU frequency higher than 66MHz in 1WS and 36MHz in<br>0WS<br>Fix/Workaround<br>None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |         | <ul> <li>Increased Power Consumption in VDDIO in sleep modes</li> <li>If the OSC0 is enabled in crystal mode when entering a sleep mode where the OSC0 is disabled, this will lead to an increased power consumption in VDDIO.</li> <li>Fix/Workaround</li> <li>Disable the OSC0 through the System Control Interface (SCIF) before going to any sleep mode where the OSC0 is disabled, or pull down or up XIN0 and XOUT0 with 1 Mohm resistor.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Power consumption in static mode The power consumption in static mode can be up to  $330\mu A$  on some parts (typical at  $25^{\circ}C$ )

#### Fix/Workaround

Set to 1b bit CORRS4 of the ECCHRS mode register (MD). In C-code: \*((volatile int\*) (0xFFFE2404))= 0x400.

DMACA data transfer fails when CTLx.SRC\_TR\_WIDTH is not equal to CTLx.DST\_TR\_WIDTH Fix/Workaround For any DMACA transfer make sure CTLx.SRC\_TR\_WIDTH = CTLx.DST\_TR\_WIDTH.

#### 3.3V supply monitor is not available

FGPFRLO[30:29] are reserved and should not be used by the application. **Fix/Workaround** None.

Service access bus (SAB) can not access DMACA registers Fix/Workaround None.

#### 10.2.2 Processor and Architecture

#### LDM instruction with PC in the register list and without ++ increments Rp

For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12. **Fix/Workaround**

None.

#### Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

#### Fix/Workaround

Place breakpoints on earlier or later instructions.

#### When the main clock is RCSYS, TIMER\_CLOCK5 is equal to PBA clock

When the main clock is generated from RCSYS, TIMER\_CLOCK5 is equal to PBA Clock and not PBA Clock / 128.

#### Fix/Workaround None.

10.2.3 MPU

## Privilege violation when using interrupts in application mode with protected system stack

If the system stack is protected by the MPU and an interrupt occurs in application mode, an MPU DTLB exception will occur.

#### Fix/Workaround

Make a DTLB Protection (Write) exception handler which permits the interrupt request to be handled in privileged mode.

#### 10.2.4 USB

#### UPCFGn.INTFRQ is irrelevant for isochronous pipe

As a consequence, isochronous IN and OUT tokens are sent every 1ms (Full Speed), or every 125uS (High Speed).

#### Fix/Workaround

SOFT\_RESET on RX+ Config US\_MR + Config\_US\_CR.

10.2.7 SPI

#### SPI disable does not work in SLAVE mode

SPI disable does not work in SLAVE mode.

#### Fix/Workaround

Read the last received data, then perform a software reset by writing a one to the Software Reset bit in the Control Register (CR.SWRST).

# SPI bad serial clock generation on 2nd chip\_select when SCBR=1, CPOL=1, and NCPHA=0

When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.

#### **Fix/Workaround**

When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.

#### SPI data transfer hangs with CSR0.CSAAT==1 and MR.MODFDIS==0

When CSR0.CSAAT==1 and mode fault detection is enabled (MR.MODFDIS==0), the SPI module will not start a data transfer.

#### Fix/Workaround

Disable mode fault detection by writing a one to MR.MODFDIS.

#### Disabling SPI has no effect on the SR.TDRE bit

Disabling SPI has no effect on the SR.TDRE bit whereas the write data command is filtered when SPI is disabled. Writing to TDR when SPI is disabled will not clear SR.TDRE. If SPI is disabled during a PDCA transfer, the PDCA will continue to write data to TDR until its buffer is empty, and this data will be lost.

#### **Fix/Workaround**

Disable the PDCA, add two NOPs, and disable the SPI. To continue the transfer, enable the SPI and PDCA.

#### 10.2.8 Power Manager

## OSC32 not functionnal in Crystal Modes (OSC32CTRL.MODE=1 or OSC32CTRL.MODE=2)

OSC32 clock output is not active even if the oscillation signal is present on XIN32/XOUT32 pins.

OSC32RDY bit may still set even if the CLK32 is not active.

External clock mode (OSC32CTRL.MODE=0) is not affected.

#### Fix/Workaround

None.

## Clock sources will not be stopped in STATIC sleep mode if the difference between CPU and PBx division factor is too high

If the division factor between the CPU/HSB and PBx frequencies is more than 4 when going to a sleep mode where the system RC oscillator is turned off, then high speed clock sources will not be turned off. This will result in a significantly higher power consumption during the sleep mode.

| 11. Datasheet Revision History |                |    |                                                                                                                                                       |

|--------------------------------|----------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                |    | te that the referring page numbers in this section are referred to this document. The evision in this section are referring to the document revision. |

| 11.1                           | Rev. H– 10/12  |    |                                                                                                                                                       |

|                                |                | 1. | Updated max frequency                                                                                                                                 |

|                                |                | 2. | Added Flash Read High Speed Mode description in FLASHC chapter                                                                                        |

|                                |                | 3. | Updated Electrical Characteristics accordingly to new max frequency                                                                                   |

|                                |                | 4. | Fixed wrong description of PLLOPT[0] in PM chapter                                                                                                    |

|                                |                | 5. | Updated Errata section according to new maximum frequency                                                                                             |

|                                |                | 6. | Added USB hi-speed PLL electrical characteristics                                                                                                     |

|                                |                | 7  | Added OSC32 Errata in Power Management sections for Rev D,E and H                                                                                     |

| 11.2                           | Rev. G– 11/11  |    |                                                                                                                                                       |

|                                |                | 1. | Add recommandation for MCI connection with more than 1 slot                                                                                           |

| 11.3                           | Rev. F – 08/11 |    |                                                                                                                                                       |

|                                |                | 1. | Final version                                                                                                                                         |

| 11.4                           | Rev. E – 06/11 |    |                                                                                                                                                       |

|                                |                | 1. | Updated Errata for E and D                                                                                                                            |

|                                |                | 2. | Updated FLASHC chapter with HSEN and HSDIS commands                                                                                                   |

| 11.5                           | Rev. D – 04/11 |    |                                                                                                                                                       |

|                                |                | 1. | Updated Errata for revision H and E                                                                                                                   |

|                                |                | 2. | Updated Reset Sequence                                                                                                                                |

|                                |                | 3. | Updated Peripherals' current consumption and others minor electrical charateristics                                                                   |

|                                |                | 4. | Updated Peripherals chapters                                                                                                                          |

| 11.6                           | Rev. C – 03/10 | )  |                                                                                                                                                       |

1. Updated the datasheet with new revision H features.