Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                       |

| Number of I/O              | 88                                                                          |

| Program Memory Size        | 128KB (128K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.75V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-VFBGA                                                                   |

| Supplier Device Package    | 100-VFBGA (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at32uc3a4128-c1ut                |

- Support for SPI and LIN

- Optionnal support for IrDA, ISO7816, Hardware Handshaking, RS485 interfaces and Modem Line

- Two Master/Slave Serial Peripheral Interfaces (SPI) with Chip Select Signals

- One Synchronous Serial Protocol Controller

- Supports I2S and Generic Frame-Based Protocols

- Two Master/Slave Two-Wire Interface (TWI), 400 kbit/s I2C-compatible

- 16-bit Stereo Audio Bitstream

- Sample Rate Up to 50 KHz

- QTouch® Library Support

- Capacitive Touch Buttons, Sliders, and Wheels

- QTouch and QMatrix Acquisition

- On-Chip Debug System (JTAG interface)

- Nexus Class 2+, Runtime Control, Non-Intrusive Data and Program Trace

- 110 General Purpose Input/Output (GPIOs)

- Standard or High Speed mode

- Toggle capability: up to 84MHz

- Packages

- 144-ball TFBGA, 11x11 mm, pitch 0.8 mm

- 144-pin LQFP, 22x22 mm, pitch 0.5 mm

- 100-ball VFBGA, 7x7 mm, pitch 0.65 mm

- Single 3.3V Power Supply

## 3. Package and Pinout

## 3.1 Package

The device pins are multiplexed with peripheral functions as described in the Peripheral Multiplexing on I/O Line section.

Figure 3-1. TFBGA144 Pinout (top view)

|   | 1         | 2         | 3         | 4         | 5         | 6         | 7         | 8         | 9         | 10        | 11        | 12        |

|---|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Α | O<br>PX40 | O<br>PB00 | O<br>PA28 | O<br>PA27 | O<br>PB03 | O<br>PA29 | O<br>PC02 | O<br>PC04 | O<br>PC05 | DPHS      | DMHS (    | JSB_VBUS  |

| В | O<br>PX10 | O<br>PB11 | O<br>PA31 | O<br>PB02 | VDDIO     | O<br>PB04 | O<br>PC03 | VDDIO     | USB_VBIAS | O<br>DMFS | GNDPLL    | PA09      |

| С | O<br>PX09 | O<br>PX35 | GNDIO     | O<br>PB01 | O<br>PX16 | O<br>PX13 | O<br>PA30 | O<br>PB08 | DPFS      | GNDCORE   | O<br>PA08 | O<br>PA10 |

| D | O<br>PX08 | O<br>PX37 | O<br>PX36 | O<br>PX47 | O<br>PX19 | O<br>PX12 | O<br>PB10 | O<br>PA02 | O<br>PA26 | O<br>PA11 | O<br>PB07 | O<br>PB06 |

| Е | O<br>PX38 | VDDIO     | O<br>PX54 | O<br>PX53 | VDDIO     | O<br>PX15 | O<br>PB09 | VDDIN     | O<br>PA25 | O<br>PA07 | VDDCORE   | O<br>PA12 |

| F | O<br>PX39 | O<br>PX07 | PX06      | O<br>PX49 | O<br>PX48 | GNDIO     | GNDIO     | O<br>PA06 | O<br>PA04 | O<br>PA05 | O<br>PA13 | O<br>PA16 |

| G | O<br>PX00 | O<br>PX05 | O<br>PX59 | O<br>PX50 | O<br>PX51 | GNDIO     | GNDIO     | O<br>PA23 | O<br>PA24 | O<br>PA03 | O<br>PA00 | O<br>PA01 |

| Н | O<br>PX01 | VDDIO     | O<br>PX58 | O<br>PX57 | VDDIO     | O<br>PC01 | O<br>PA17 | VDDIO     | O<br>PA21 | O<br>PA22 | VDDANA    | O<br>PB05 |

| J | O<br>PX04 | O<br>PX02 | O<br>PX34 | O<br>PX56 | O<br>PX55 | O<br>PA14 | O<br>PA15 | O<br>PA19 | O<br>PA20 | TMS       | TDO       | RESET_N   |

| K | O<br>PX03 | O<br>PX44 | GNDIO     | O<br>PX46 | PC00      | O<br>PX17 | O<br>PX52 | O<br>PA18 | O<br>PX27 | GNDIO     | O<br>PX29 | TCK       |

| L | O<br>PX11 | GNDIO     | O<br>PX45 | O<br>PX20 | VDDIO     | O<br>PX18 | O<br>PX43 | VDDIN     | O<br>PX26 | O<br>PX28 | GNDANA    | TDI       |

| M | O<br>PX22 | O<br>PX41 | O<br>PX42 | O<br>PX14 | O<br>PX21 | O<br>PX23 | O<br>PX24 | O<br>PX25 | O<br>PX32 | O<br>PX31 | PX30      | O<br>PX33 |

Figure 3-3. VFBGA100 Pinout (top view)

| _ | 1                            | 2         | 3         | 4                            | 5                            | 6                            | 7                            | 8                            | 9                            | 10                           |

|---|------------------------------|-----------|-----------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|

| Α | O<br>PA28                    | O<br>PA27 | O<br>PB04 | O<br>PA30                    | O<br>PC02                    | O<br>PC03                    | O<br>PC05                    | O<br>DPHS                    | DMHS                         | USB_VBUS                     |

| В | O<br>PB00                    | O<br>PB01 | O<br>PB02 | O<br>PA29                    | VDDIO                        | VDDIO                        | O<br>PC04                    | DPFS                         | DMFS                         | GNDPLL                       |

| С | O<br>PB11                    | O<br>PA31 | GNDIO     | PB03                         | PB09                         | PB08                         | USB_VBIAS                    | GNDIO                        | O<br>PA11                    | O<br>PA10                    |

| D | O<br>PX12                    | PX10      | O<br>PX13 | PX16/<br>PX53 <sup>(1)</sup> | O<br>PB10                    | O<br>PB07                    | O<br>PB06                    | PA09                         | VDDIN                        | VDDIN                        |

| Е | PA02/<br>PX47 <sup>(1)</sup> | GNDIO     | PX08      | PX09                         | VDDIO                        | GNDIO                        | O<br>PA16                    | PA06/<br>PA13 <sup>(1)</sup> | O<br>PA04                    | VDDCORE                      |

| F | PX19/<br>PX59 <sup>(1)</sup> | VDDIO     | PX06      | PX07                         | GNDIO                        | VDDIO                        | PA26/<br>PB05 <sup>(1)</sup> | O<br>PA08                    | PA03                         | GNDCORE                      |

| G | PX05                         | PX01      | O<br>PX02 | PX00                         | O<br>PX30                    | PA23/<br>PX46 <sup>(1)</sup> | PA12/<br>PA25 <sup>(1)</sup> | PA00/<br>PA18 <sup>(1)</sup> | PA05                         | PA01/<br>PA17 <sup>(1)</sup> |

| Н | PX04                         | O<br>PX21 | GNDIO     | O<br>PX25                    | O<br>PX31                    | PA22/<br>PX20 <sup>(1)</sup> | TMS                          | GNDANA                       | PA20/<br>PX18 <sup>(1)</sup> | PA07/<br>PA19 <sup>(1)</sup> |

| J | PX03                         | O<br>PX24 | PX26      | PX29                         | VDDIO                        | VDDANA                       | PA15/<br>PX45 <sup>(1)</sup> | TDO                          | RESET_N                      | PA24/<br>PX17 <sup>(1)</sup> |

| K | O<br>PX23                    | PX27      | PX28      | PX15/<br>PX32 <sup>(1)</sup> | PC00/<br>PX14 <sup>(1)</sup> | PC01                         | PA14/<br>PX11 <sup>(1)</sup> | TDI                          | TCK                          | PA21/<br>PX22 <sup>(1)</sup> |

Note: 1. Those balls are physically connected to 2 GPIOs. Software must managed carrefully the GPIO configuration to avoid electrical conflict

Table 3-6.Signal Description List

| Signal Name | Function                             | Туре            | Active<br>Level | Comments |

|-------------|--------------------------------------|-----------------|-----------------|----------|

| RESET_N     | Reset Pin                            | Input           | Low             |          |

|             | DMA Controller - DMA                 | ACA (optional   | )               |          |

| DMAACK[1:0] | DMA Acknowledge                      | Output          |                 |          |

| DMARQ[1:0]  | DMA Requests                         | Input           |                 |          |

|             | External Interrupt Co                | ontroller - EIC |                 |          |

| EXTINT[7:0] | External Interrupt Pins              | Input           |                 |          |

| SCAN[7:0]   | Keypad Scan Pins                     | Output          |                 |          |

| NMI         | Non-Maskable Interrupt Pin           | Input           | Low             |          |

|             | General Purpose Input/Output pin - C | PIOA, GPIOE     | , GPIOC, G      | PIOX     |

| PA[31:0]    | Parallel I/O Controller GPIO port A  | I/O             |                 |          |

| PB[11:0]    | Parallel I/O Controller GPIO port B  | I/O             |                 |          |

| PC[5:0]     | Parallel I/O Controller GPIO port C  | I/O             |                 |          |

| PX[59:0]    | Parallel I/O Controller GPIO port X  | I/O             |                 |          |

|             | External Bus Inte                    | rface - EBI     | 1               |          |

| ADDR[23:0]  | Address Bus                          | Output          |                 |          |

| CAS         | Column Signal                        | Output          | Low             |          |

| CFCE1       | Compact Flash 1 Chip Enable          | Output          | Low             |          |

| CFCE2       | Compact Flash 2 Chip Enable          | Output          | Low             |          |

| CFRNW       | Compact Flash Read Not Write         | Output          |                 |          |

| DATA[15:0]  | Data Bus                             | I/O             |                 |          |

| NANDOE      | NAND Flash Output Enable             | Output          | Low             |          |

| NANDWE      | NAND Flash Write Enable              | Output          | Low             |          |

| NCS[5:0]    | Chip Select                          | Output          | Low             |          |

| NRD         | Read Signal                          | Output          | Low             |          |

| NWAIT       | External Wait Signal                 | Input           | Low             |          |

| NWE0        | Write Enable 0                       | Output          | Low             |          |

| NWE1        | Write Enable 1                       | Output          | Low             |          |

| RAS         | Row Signal                           | Output          | Low             |          |

Table 5-1. AT32UC3A3A4 Physical Memory Map

|                 |                  | Size                                                           | Size                                                           | Size                                                       |

|-----------------|------------------|----------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------|

| Device          | Start<br>Address | AT32UC3A3256S<br>AT32UC3A3256<br>AT32UC3A4256S<br>AT32UC3A4256 | AT32UC3A3128S<br>AT32UC3A3128<br>AT32UC3A4128S<br>AT32UC3A4128 | AT32UC3A364S<br>AT32UC3A364<br>AT32UC3A464S<br>AT32UC3A464 |

| HRAMC0          | 0xFF000000       | 32KByte                                                        | 32KByte                                                        | 32KByte                                                    |

| HRAMC1          | 0xFF008000       | 32KByte                                                        | 32KByte                                                        | 32KByte                                                    |

| HSB-PB Bridge A | 0xFFFF0000       | 64KByte                                                        | 64KByte                                                        | 64KByte                                                    |

| HSB-PB Bridge B | 0xFFFE0000       | 64KByte                                                        | 64KByte                                                        | 64KByte                                                    |

## 5.3 Peripheral Address Map

Table 5-2.

Peripheral Address Mapping

| Address    |         | Peripheral Name                                        |

|------------|---------|--------------------------------------------------------|

| 0xFF100000 | DMACA   | DMA Controller - DMACA                                 |

| 0xFFFD0000 | AES     | Advanced Encryption Standard - AES                     |

| 0xFFFE0000 | USB     | USB 2.0 Device and Host Interface - USB                |

| 0xFFFE1000 | HMATRIX | HSB Matrix - HMATRIX                                   |

| 0xFFFE1400 | FLASHC  | Flash Controller - FLASHC                              |

| 0xFFFE1C00 | SMC     | Static Memory Controller - SMC                         |

| 0xFFFE2000 | SDRAMC  | SDRAM Controller - SDRAMC                              |

| 0xFFFE2400 | ECCHRS  | Error code corrector Hamming and Reed Solomon - ECCHRS |

| 0xFFFE2800 | BUSMON  | Bus Monitor module - BUSMON                            |

| 0xFFFE4000 | MCI     | Mulitmedia Card Interface - MCI                        |

| 0xFFFE8000 | MSI     | Memory Stick Interface - MSI                           |

| 0xFFFF0000 | PDCA    | Peripheral DMA Controller - PDCA                       |

| 0xFFFF0800 | INTC    | Interrupt controller - INTC                            |

Table 5-3.

Local Bus Mapped GPIO Registers

| Port | Register                             | Mode   | Local Bus<br>Address | Access     |

|------|--------------------------------------|--------|----------------------|------------|

| 2    | Output Driver Enable Register (ODER) | WRITE  | 0x40000240           | Write-only |

|      |                                      | SET    | 0x40000244           | Write-only |

|      |                                      | CLEAR  | 0x40000248           | Write-only |

|      |                                      | TOGGLE | 0x4000024C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000250           | Write-only |

|      |                                      | SET    | 0x40000254           | Write-only |

|      |                                      | CLEAR  | 0x40000258           | Write-only |

|      |                                      | TOGGLE | 0x4000025C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000260           | Read-only  |

| 3    | Output Driver Enable Register (ODER) | WRITE  | 0x40000340           | Write-only |

|      |                                      | SET    | 0x40000344           | Write-only |

|      |                                      | CLEAR  | 0x40000348           | Write-only |

|      |                                      | TOGGLE | 0x4000034C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000350           | Write-only |

|      |                                      | SET    | 0x40000354           | Write-only |

|      |                                      | CLEAR  | 0x40000358           | Write-only |

|      |                                      | TOGGLE | 0x4000035C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000360           | Read-only  |

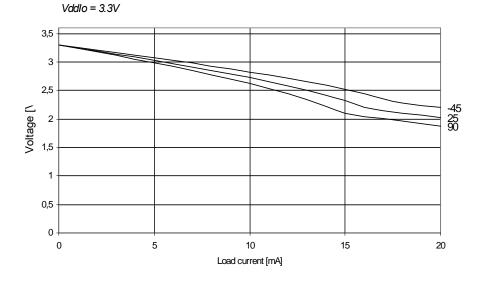

## 7.2.1 I/O Pin Output Level Typical Characteristics

VddIo = 3.3V1,8 90 1,6 25 1,4 1,2 Voltage [\ 0,8 0,6 0,4 0,2 0 5 10 15 20 Load current [mA]

Figure 7-1. I/O Pin drive x2 Output Low Level Voltage (VOL) vs. Source Current

Figure 7-2. I/O Pin drive x2 Output High Level Voltage (VOH) vs. Source Current

## 7.3 I/O pin Characteristics

These parameters are given in the following conditions:

- V<sub>DDCORE</sub> = 1.8V

- $V_{DDIO} = 3.3V$

- Ambient Temperature = 25°C

Table 7-9.BOD Timing

| Symbol           | Parameter                                                | Conditions                        | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------------------------|-----------------------------------|------|------|------|------|

| T <sub>BOD</sub> | Minimum time with VDDCORE < VBOD to detect power failure | Falling VDDCORE from 1.8V to 1.1V |      | 300  | 800  | ns   |

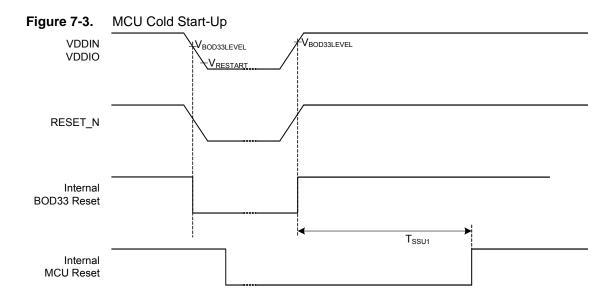

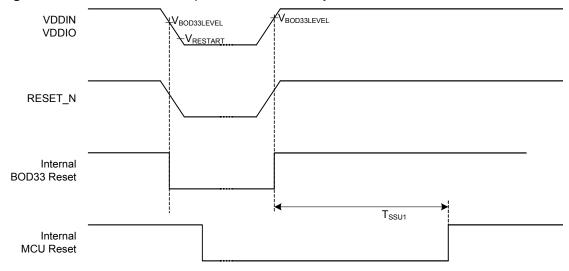

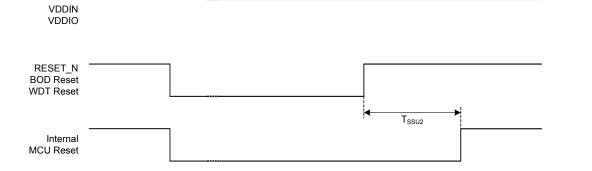

## 7.5.3 Reset Sequence

Table 7-10.

Electrical Characteristics

| Symbol               | Parameter                                                                                                                                 | Conditions                                              | Min. | Тур. | Max. | Unit |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|------|------|------|

| $V_{\rm DDRR}$       | VDDIN/VDDIO rise rate to ensure power-on-reset                                                                                            |                                                         | 0.8  |      |      | V/ms |

| V <sub>POR+</sub>    | Rising threshold voltage: voltage up to which device is kept under reset by POR on rising VDDIN                                           | Rising VDDIN: V <sub>RESTART</sub> -> V <sub>POR+</sub> |      | 2.7  |      | V    |

| V <sub>POR</sub> -   | Falling threshold voltage: voltage when POR resets device on falling VDDIN                                                                | Falling VDDIN: 3.3V -> V <sub>POR-</sub>                |      | 2.7  |      | V    |

| V <sub>RESTART</sub> | On falling VDDIN, voltage must go down to this value before supply can rise again to ensure reset signal is released at V <sub>POR+</sub> | Falling VDDIN: 3.3V -> V <sub>RESTART</sub>             |      |      | 0.2  | V    |

| T <sub>SSU1</sub>    | Time for Cold System Startup: Time for CPU to fetch its first instruction (RCosc not calibrated)                                          |                                                         | 480  |      | 960  | μs   |

| T <sub>SSU2</sub>    | Time for Hot System Startup: Time for CPU to fetch its first instruction (RCosc calibrated)                                               |                                                         |      | 420  |      | μs   |

Figure 7-4. MCU Cold Start-Up RESET\_N Externally Driven

Figure 7-5. MCU Hot Start-Up

Table 7-13.

Typical Cuurent Consumption by Peripheral

| Peripheral | Тур. | Unit     |

|------------|------|----------|

| ADC        | 7    |          |

| AES        | 80   |          |

| ABDAC      | 10   |          |

| DMACA      | 70   |          |

| EBI        | 23   |          |

| EIC        | 0.5  |          |

| GPIO       | 37   |          |

| INTC       | 3    |          |

| MCI        | 40   |          |

| MSI        | 10   |          |

| PDCA       | 20   | μΑ/MHz   |

| SDRAM      | 5    | μΑ/Ινίπ2 |

| SMC        | 9    |          |

| SPI        | 6    |          |

| SSC        | 10   |          |

| RTC        | 5    |          |

| TC         | 8    |          |

| TWIM       | 2    |          |

| TWIS       | 2    |          |

| USART      | 10   |          |

| USBB       | 90   |          |

| WDT        | 2    |          |

## 7.8 Oscillator Characteristics

The following characteristics are applicable to the operating temperature range:  $T_A = -40$ °C to 85°C and worst case of power supply, unless otherwise specified.

## 7.8.1 Slow Clock RC Oscillator

Table 7-17.

RC Oscillator Frequency

| Symbol          | Parameter                                | Conditions             | Min.  | Тур. | Max. | Unit |

|-----------------|------------------------------------------|------------------------|-------|------|------|------|

|                 | Calibration point: T <sub>A</sub> = 85°C |                        | 115.2 | 116  | KHz  |      |

| F <sub>RC</sub> |                                          | T <sub>A</sub> = 25°C  |       | 112  |      | KHz  |

|                 |                                          | T <sub>A</sub> = -40°C | 105   | 108  |      | KHz  |

## 7.8.2 32 KHz Oscillator

Table 7-18. 32 KHz Oscillator Characteristics

| Symbol                    | Parameter                            | Conditions                                | Min.                | Тур.   | Max.                | Unit |

|---------------------------|--------------------------------------|-------------------------------------------|---------------------|--------|---------------------|------|

| 4 //+                     | Ossillator Fraguenay                 | External clock on XIN32                   |                     |        | 30                  | MHz  |

| 1/(t <sub>CP32KHz</sub> ) | Oscillator Frequency                 | Crystal                                   |                     | 32 768 |                     | Hz   |

| C <sub>L</sub>            | Equivalent Load Capacitance          |                                           | 6                   |        | 12.5                | pF   |

| ESR                       | Crystal Equivalent Series Resistance |                                           |                     |        | 100                 | ΚΩ   |

| t <sub>ST</sub>           | Startup Time                         | $C_L = 6pF^{(1)}$<br>$C_L = 12.5pF^{(1)}$ |                     |        | 600<br>1200         | ms   |

| t <sub>CH</sub>           | XIN32 Clock High Half-period         |                                           | 0.4 t <sub>CP</sub> |        | 0.6 t <sub>CP</sub> |      |

| t <sub>CL</sub>           | XIN32 Clock Low Half-period          |                                           | 0.4 t <sub>CP</sub> |        | 0.6 t <sub>CP</sub> |      |

| C <sub>IN</sub>           | XIN32 Input Capacitance              |                                           |                     |        | 5                   | pF   |

|                           | 0                                    | Active mode                               |                     |        | 1.8                 | μA   |

| losc                      | Current Consumption                  | Standby mode                              |                     |        | 0.1                 | μA   |

Note: 1.  $C_L$  is the equivalent load capacitance.

## 7.9 ADC Characteristics

Table 7-22. Channel Conversion Time and ADC Clock

| Parameter                       | Conditions             | Min. | Тур. | Max.               | Unit |

|---------------------------------|------------------------|------|------|--------------------|------|

| ADC Clark Fraguency             | 10-bit resolution mode |      |      | 5                  | MHz  |

| ADC Clock Frequency             | 8-bit resolution mode  |      |      | 8                  | MHz  |

| Startup Time                    | Return from Idle Mode  |      |      | 20                 | μs   |

| Track and Hold Acquisition Time |                        | 600  |      |                    | ns   |

| Conversion Time                 | ADC Clock = 5 MHz      |      |      | 2                  | μs   |

| Conversion Time                 | ADC Clock = 8 MHz      |      |      | 1.25               | μs   |

| Throughput Data                 | ADC Clock = 5 MHz      |      |      | 384 <sup>(1)</sup> | kSPS |

| Throughput Rate                 | ADC Clock = 8 MHz      |      |      | 533 <sup>(2)</sup> | kSPS |

- 1. Corresponds to 13 clock cycles: 3 clock cycles for track and hold acquisition time and 10 clock cycles for conversion.

- 2. Corresponds to 15 clock cycles: 5 clock cycles for track and hold acquisition time and 10 clock cycles for conversion.

Table 7-23.

ADC Power Consumption

| Parameter                         | Conditions                           | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------------------------------------|------|------|------|------|

| Current Consumption on VDDANA (1) | On 13 samples with ADC clock = 5 MHz |      |      | 1.25 | mA   |

1. Including internal reference input current

Table 7-24. Analog Inputs

| Parameter             | Conditions | Min. | Тур. | Max.   | Unit |

|-----------------------|------------|------|------|--------|------|

| Input Voltage Range   |            | 0    |      | VDDANA | ٧    |

| Input Leakage Current |            |      |      | 1      | μΑ   |

| Input Capacitance     |            |      | 7    |        | pF   |

| Input Resistance      |            |      | 350  | 850    | Ohm  |

Table 7-25. Transfer Characteristics in 8-bit mode

| Parameter                  | Conditions        | Min. | Тур. | Max. | Unit |  |

|----------------------------|-------------------|------|------|------|------|--|

| Resolution                 |                   |      | 8    |      | Bit  |  |

| Abachuta Accuracy          | ADC Clock = 5 MHz |      |      | 0.8  | LSB  |  |

| Absolute Accuracy          | ADC Clock = 8 MHz |      |      | 1.5  | LSB  |  |

| Integral New linearity     | ADC Clock = 5 MHz |      | 0.35 | 0.5  | LSB  |  |

| Integral Non-linearity     | ADC Clock = 8 MHz |      | 0.5  | 1.5  | LSB  |  |

| D''' (C.11) (C. 12)        | ADC Clock = 5 MHz |      | 0.3  | 0.5  | LSB  |  |

| Differential Non-linearity | ADC Clock = 8 MHz |      | 0.5  | 1.5  | LSB  |  |

| Offset Error               | ADC Clock = 5 MHz | -1.5 |      | 1.5  | LSB  |  |

| Gain Error                 | ADC Clock = 5 MHz | -0.5 |      | 0.5  | LSB  |  |

Table 7-32.

SMC Read Signals with no Hold Settings

| Symbol            | Parameter                      | Min. | Unit |  |  |  |

|-------------------|--------------------------------|------|------|--|--|--|

|                   | NRD Controlled (READ_MODE = 1) |      |      |  |  |  |

| SMC <sub>19</sub> | Data Setup before NRD High     | 13.7 | ns   |  |  |  |

| SMC <sub>20</sub> | Data Hold after NRD High       | 1    | ns   |  |  |  |

|                   | NRD Controlled (READ_MODE = 0) |      |      |  |  |  |

| SMC <sub>21</sub> | Data Setup before NCS High     | 13.3 | ns   |  |  |  |

| SMC <sub>22</sub> | Data Hold after NCS High       | 0    | ns   |  |  |  |

Table 7-33.

SMC Write Signals with Hold Settings

| Symbol            | Parameter                                    | Min.                                                             | Unit |  |  |  |  |  |

|-------------------|----------------------------------------------|------------------------------------------------------------------|------|--|--|--|--|--|

|                   | NRD Controlled (READ_MODE = 1)               |                                                                  |      |  |  |  |  |  |

| SMC <sub>23</sub> | Data Out Valid before NWE High               | (nwe pulse length - 1) * t <sub>CPSMC</sub> - 0.9                | ns   |  |  |  |  |  |

| SMC <sub>24</sub> | Data Out Valid after NWE High <sup>(1)</sup> | nwe hold length * t <sub>CPSMC</sub> - 6                         | ns   |  |  |  |  |  |

| SMC <sub>25</sub> | NWE High to NBS0/A0 Change <sup>(1)</sup>    | nwe hold length * t <sub>CPSMC</sub> - 1.9                       | ns   |  |  |  |  |  |

| SMC <sub>26</sub> | NWE High to NBS1 Change <sup>(1)</sup>       | nwe hold length * t <sub>CPSMC</sub> - 1.9                       | ns   |  |  |  |  |  |

| SMC <sub>29</sub> | NWE High to A1 Change <sup>(1)</sup>         | nwe hold length * t <sub>CPSMC</sub> - 1.9                       | ns   |  |  |  |  |  |

| SMC <sub>31</sub> | NWE High to A2 - A23 Change <sup>(1)</sup>   | nwe hold length * t <sub>CPSMC</sub> - 1.7                       | ns   |  |  |  |  |  |

| SMC <sub>32</sub> | NWE High to NCS Inactive <sup>(1)</sup>      | (nwe hold length - ncs wr hold length)* t <sub>CPSMC</sub> - 2.9 | ns   |  |  |  |  |  |

| SMC <sub>33</sub> | NWE Pulse Width                              | nwe pulse length * t <sub>CPSMC</sub> - 0.9                      | ns   |  |  |  |  |  |

|                   | NRD Controlle                                | ed (READ_MODE = 0)                                               |      |  |  |  |  |  |

| SMC <sub>34</sub> | Data Out Valid before NCS High               | (ncs wr pulse length - 1)* t <sub>CPSMC</sub> - 4.6              | ns   |  |  |  |  |  |

| SMC <sub>35</sub> | Data Out Valid after NCS High <sup>(1)</sup> | ncs wr hold length * t <sub>CPSMC</sub> - 5.8                    | ns   |  |  |  |  |  |

| SMC <sub>36</sub> | NCS High to NWE Inactive <sup>(1)</sup>      | (ncs wr hold length - nwe hold length)* t <sub>CPSMC</sub> - 0.6 | ns   |  |  |  |  |  |

Note: 1. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs wr hold length" or "nwe hold length"

Table 7-34.

SMC Write Signals with No Hold Settings (NWE Controlled only)

| Symbol            | Parameter                    | Min. | Unit |

|-------------------|------------------------------|------|------|

| SMC <sub>37</sub> | NWE Rising to A2-A25 Valid   | 5.4  | ns   |

| SMC <sub>38</sub> | NWE Rising to NBS0/A0 Valid  | 5    | ns   |

| SMC <sub>39</sub> | NWE Rising to NBS1 Change    | 5    | ns   |

| SMC <sub>40</sub> | NWE Rising to A1/NBS2 Change | 5    | ns   |

| SMC <sub>41</sub> | NWE Rising to NBS3 Change    | 5    | ns   |

| SMC <sub>42</sub> | NWE Rising to NCS Rising     | 5.1  | ns   |

Table 7-36.

SDRAM Clock Signal

| Symbol               | Parameter                                | Conditions | Min. | Max. | Unit |

|----------------------|------------------------------------------|------------|------|------|------|

| SDRAMC <sub>13</sub> | Bank Change before SDCK Rising Edge      |            | 6.3  |      | ns   |

| SDRAMC <sub>14</sub> | Bank Change after SDCK Rising Edge       |            | 2.4  |      | ns   |

| SDRAMC <sub>15</sub> | CAS Low before SDCK Rising Edge          |            | 7.4  |      | ns   |

| SDRAMC <sub>16</sub> | CAS High after SDCK Rising Edge          |            | 1.9  |      | ns   |

| SDRAMC <sub>17</sub> | DQM Change before SDCK Rising Edge       |            | 6.4  |      | ns   |

| SDRAMC <sub>18</sub> | DQM Change after SDCK Rising Edge        |            | 2.2  |      | ns   |

| SDRAMC <sub>19</sub> | D0-D15 in Setup before SDCK Rising Edge  |            | 9    |      | ns   |

| SDRAMC <sub>20</sub> | D0-D15 in Hold after SDCK Rising Edge    |            | 0    |      | ns   |

| SDRAMC <sub>23</sub> | SDWE Low before SDCK Rising Edge         |            | 7.6  |      | ns   |

| SDRAMC <sub>24</sub> | SDWE High after SDCK Rising Edge         |            | 1.8  |      | ns   |

| SDRAMC <sub>25</sub> | D0-D15 Out Valid before SDCK Rising Edge |            | 7.1  |      | ns   |

| SDRAMC <sub>26</sub> | D0-D15 Out Valid after SDCK Rising Edge  |            | 1.5  |      | ns   |

# 9. Ordering Information

| Device        | Ordering Code      | Package        | Conditioning | Temperature Operating<br>Range |

|---------------|--------------------|----------------|--------------|--------------------------------|

| AT32UC3A3256S | AT32UC3A3256S-ALUT | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256S-ALUR | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256S-CTUT | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256S-CTUR | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A3256  | AT32UC3A3256-ALUT  | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256-ALUR  | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256-CTUT  | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256-CTUR  | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A3128S | AT32UC3A3128S-ALUT | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128S-ALUR | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128S-CTUT | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128S-CTUR | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A3128  | AT32UC3A3128-ALUT  | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128-ALUR  | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128-CTUT  | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128-CTUR  | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A364S  | AT32UC3A364S-ALUT  | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364S-ALUR  | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364S-CTUT  | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364S-CTUR  | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A364   | AT32UC3A364-ALUT   | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364-ALUR   | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364-CTUT   | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364-CTUR   | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4256S | AT32UC3A4256S-C1UT | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4256S-C1UR | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4256  | AT32UC3A4256-C1UT  | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4256-C1UR  | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4128S | AT32UC3A4128S-C1UT | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4128S-C1UR | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4128  | AT32UC3A4128-C1UT  | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4128-C1UR  | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A464S  | AT32UC3A464S-C1UT  | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A464S-C1UR  | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A464   | AT32UC3A464-C1UT   | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A464-C1UR   | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

#### Fix/Workaround

Set to 1b bit CORRS4 of the ECCHRS mode register (MD). In C-code: \*((volatile int\*) (0xFFFE2404))= 0x400.

# DMACA data transfer fails when CTLx.SRC\_TR\_WIDTH is not equal to CTLx.DST TR WIDTH

#### Fix/Workaround

For any DMACA transfer make sure CTLx.SRC\_TR\_WIDTH = CTLx.DST\_TR\_WIDTH.

#### 3.3V supply monitor is not available

FGPFRLO[30:29] are reserved and should not be used by the application.

#### Fix/Workaround

None.

## Service access bus (SAB) can not access DMACA registers

Fix/Workaround

None.

### 10.2.2 Processor and Architecture

### LDM instruction with PC in the register list and without ++ increments Rp

For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12.

#### Fix/Workaround

None.

#### Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

#### Fix/Workaround

Place breakpoints on earlier or later instructions.

#### When the main clock is RCSYS, TIMER CLOCK5 is equal to PBA clock

When the main clock is generated from RCSYS, TIMER\_CLOCK5 is equal to PBA Clock and not PBA Clock / 128.

#### Fix/Workaround

None.

#### 10.2.3 MPU

## Privilege violation when using interrupts in application mode with protected system stack

If the system stack is protected by the MPU and an interrupt occurs in application mode, an MPU DTLB exception will occur.

### Fix/Workaround

Make a DTLB Protection (Write) exception handler which permits the interrupt request to be handled in privileged mode.

#### 10.2.4 USB

### UPCFGn.INTFRQ is irrelevant for isochronous pipe

As a consequence, isochronous IN and OUT tokens are sent every 1ms (Full Speed), or every 125uS (High Speed).

#### Fix/Workaround

Before going to sleep modes where the system RC oscillator is stopped, make sure that the factor between the CPU/HSB and PBx frequencies is less than or equal to 4.

#### 10.2.9 PDCA

#### PCONTROL.CHxRES is non-functional

PCONTROL.CHxRES is non-functional. Counters are reset at power-on, and cannot be reset by software.

#### Fix/Workaround

Software needs to keep history of performance counters.

### Transfer error will stall a transmit peripheral handshake interface

If a transfer error is encountered on a channel transmitting to a peripheral, the peripheral handshake of the active channel will stall and the PDCA will not do any more transfers on the affected peripheral handshake interface.

### Fix/Workaround

Disable and then enable the peripheral after the transfer error.

#### 10.2.10 AES

# URAD (Unspecified Register Access Detection Status) does not detect read accesses to the write-only KEYW[5..8]R registers

#### Fix/Workaround

None.

#### 10.2.11 HMATRIX

#### In the PRAS and PRBS registers, the MxPR fields are only two bits

In the PRAS and PRBS registers, the MxPR fields are only two bits wide, instead of four bits. The unused bits are undefined when reading the registers.

#### Fix/Workaround

Mask undefined bits when reading PRAS and PRBS.

#### 10.2.12 TWIM

#### TWIM SR.IDLE goes high immediately when NAK is received

When a NAK is received and there is a non-zero number of bytes to be transmitted, SR.IDLE goes high immediately and does not wait for the STOP condition to be sent. This does not cause any problem just by itself, but can cause a problem if software waits for SR.IDLE to go high and then immediately disables the TWIM by writing a one to CR.MDIS. Disabling the TWIM causes the TWCK and TWD pins to go high immediately, so the STOP condition will not be transmitted correctly.

#### Fix/Workaround

If possible, do not disable the TWIM. If it is absolutely necessary to disable the TWIM, there must be a software delay of at least two TWCK periods between the detection of SR.IDLE==1 and the disabling of the TWIM.

### TWIM TWALM polarity is wrong

The TWALM signal in the TWIM is active high instead of active low.

#### Fix/Workaround

Use an external inverter to invert the signal going into the TWIM. When using both TWIM and TWIS on the same pins, the TWALM cannot be used.

### SMBALERT bit may be set after reset

The SMBus Alert (SMBALERT) bit in the Status Register (SR) might be erroneously set after system reset.

#### Fix/Workaround

After system reset, clear the SR.SMBALERT bit before commencing any TWI transfer.

#### 10.2.13 TWIS

#### Clearing the NAK bit before the BTF bit is set locks up the TWI bus

When the TWIS is in transmit mode, clearing the NAK Received (NAK) bit of the Status Register (SR) before the end of the Acknowledge/Not Acknowledge cycle will cause the TWIS to attempt to continue transmitting data, thus locking up the bus.

#### Fix/Workaround

Clear SR.NAK only after the Byte Transfer Finished (BTF) bit of the same register has been set.

#### TWIS stretch on Address match error

When the TWIS stretches TWCK due to a slave address match, it also holds TWD low for the same duration if it is to be receiving data. When TWIS releases TWCK, it releases TWD at the same time. This can cause a TWI timing violation.

#### Fix/Workaround

None.

#### 10.2.14 MCI

## MCI\_CLK features is not available on PX12, PX13 and PX40

Fix/Workaround

MCI CLK feature is available on PA27 only.

# The busy signal of the responses R1b is not taken in account for CMD12 STOP\_TRANSFER

It is not possible to know the busy status of the card during the response (R1b) for the commands CMD12.

#### Fix/Workaround

The card busy line should be polled through the GPIO Input Value register (IVR) for commands CMD12.

### 10.2.15 SSC

## Frame Synchro and Frame Synchro Data are delayed by one clock cycle

The frame synchro and the frame synchro data are delayed from 1 SSC\_CLOCK when:

- Clock is CKDIV

- The START is selected on either a frame synchro edge or a level

- Frame synchro data is enabled

- Transmit clock is gated on output (through CKO field)

### Fix/Workaround

Transmit or receive CLOCK must not be gated (by the mean of CKO field) when START condition is performed on a generated frame synchro.

#### 10.2.16 FLASHC

# Corrupted read in flash may happen after fuses write or erase operations (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands)

After a flash fuse write or erase operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands), reading (data read or code fetch) in flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

#### Fix/Workaround

Before the flash fuse write or erase operation, enable the flash high speed mode (FLASHC HSEN command). The flash fuse write or erase operations (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands) must be issued from RAM or through the EBI. After these commands, read 3 times one flash page initialized to 00h. Disable the flash high speed mode (FLASHC HSDIS command). It is then possible to safely read or code fetch the flash.

#### 10.3 Rev. D

#### 10.3.1 General

## Devices cannot operate with CPU frequency higher than 66MHz in 1WS and 36MHz in 0WS

#### Fix/Workaround

None

# DMACA data transfer fails when CTLx.SRC\_TR\_WIDTH is not equal to CTLx.DST TR WIDTH

#### Fix/Workaround

For any DMACA transfer make sure CTLx.SRC TR WIDTH = CTLx.DST TR WIDTH.

#### 3.3V supply monitor is not available

FGPFRLO[30:29] are reserved and should not be used by the application.

### Fix/Workaround

None.

## Service access bus (SAB) can not access DMACA registers

#### Fix/Workaround

None.

#### 10.3.2 Processor and Architecture

#### LDM instruction with PC in the register list and without ++ increments Rp

For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12.

#### Fix/Workaround

None.

#### Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

## Fix/Workaround

Place breakpoints on earlier or later instructions.

#### Fix/Workaround

None.

#### 10.3.14 MCI

# The busy signal of the responses R1b is not taken in account for CMD12 STOP TRANSFER

It is not possible to know the busy status of the card during the response (R1b) for the commands CMD12.

#### Fix/Workaround

The card busy line should be polled through the GPIO Input Value register (IVR) for commands CMD12.

#### 10.3.15 SSC

#### Frame Synchro and Frame Synchro Data are delayed by one clock cycle

The frame synchro and the frame synchro data are delayed from 1 SSC\_CLOCK when:

- Clock is CKDIV

- The START is selected on either a frame synchro edge or a level

- Frame synchro data is enabled

- Transmit clock is gated on output (through CKO field)

#### Fix/Workaround

Transmit or receive CLOCK must not be gated (by the mean of CKO field) when START condition is performed on a generated frame synchro.

#### 10.3.16 FLASHC

# Corrupted read in flash may happen after fuses write or erase operations (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands)

After a flash fuse write or erase operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands), reading (data read or code fetch) in flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

#### Fix/Workaround

Before the flash fuse write or erase operation, enable the flash high speed mode (FLASHC HSEN command). The flash fuse write or erase operations (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands) must be issued from RAM or through the EBI. After these commands, read 3 times one flash page initialized to 00h. Disable the flash high speed mode (FLASHC HSDIS command). It is then possible to safely read or code fetch the flash.