Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betuns                     |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | AVR                                                                          |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 66MHz                                                                        |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                        |

| Number of I/O              | 88                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.75V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-VFBGA                                                                    |

| Supplier Device Package    | 100-VFBGA (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a4128s-c1ut |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

AT32UC3A3

- Support for SPI and LIN

- Optionnal support for IrDA, ISO7816, Hardware Handshaking, RS485 interfaces and Modem Line

- Two Master/Slave Serial Peripheral Interfaces (SPI) with Chip Select Signals

- One Synchronous Serial Protocol Controller

- Supports I2S and Generic Frame-Based Protocols

- Two Master/Slave Two-Wire Interface (TWI), 400 kbit/s I2C-compatible

- 16-bit Stereo Audio Bitstream

- Sample Rate Up to 50 KHz

- QTouch<sup>®</sup> Library Support

- Capacitive Touch Buttons, Sliders, and Wheels

- QTouch and QMatrix Acquisition

- On-Chip Debug System (JTAG interface)

- Nexus Class 2+, Runtime Control, Non-Intrusive Data and Program Trace

- 110 General Purpose Input/Output (GPIOs)

- Standard or High Speed mode

- Toggle capability: up to 84MHz

- Packages

- 144-ball TFBGA, 11x11 mm, pitch 0.8 mm

- 144-pin LQFP, 22x22 mm, pitch 0.5 mm

- 100-ball VFBGA, 7x7 mm, pitch 0.65 mm

- Single 3.3V Power Supply

| Table 3-1. | GPIO Controller Function Multiplexing |

|------------|---------------------------------------|

|------------|---------------------------------------|

|     |     |                   |      | G   |        |      | GPIO function  |               |              |   |

|-----|-----|-------------------|------|-----|--------|------|----------------|---------------|--------------|---|

|     |     |                   |      | Р   |        | PIN  |                |               |              |   |

| BGA | QFP | BGA               |      | I   |        | Туре |                |               |              |   |

| 144 | 144 | 100               | PIN  | 0   | Supply | (2)  | Α              | В             | С            | D |

| J4  | 78  |                   | PX56 | 107 | VDDIO  | x2   | EBI - ADDR[21] | EIC - SCAN[2] | USART2 - TXD |   |

| H4  | 76  |                   | PX57 | 108 | VDDIO  | x2   | EBI - ADDR[20] | EIC - SCAN[1] | USART3 - RXD |   |

| H3  | 57  |                   | PX58 | 109 | VDDIO  | x2   | EBI - NCS[0]   | EIC - SCAN[0] | USART3 - TXD |   |

| G3  | 56  | F1 <sup>(1)</sup> | PX59 | 110 | VDDIO  | x2   | EBI - NANDWE   |               | MCI - CMD[1] |   |

Note: 1. Those balls are physically connected to 2 GPIOs. Software must managed carrefully the GPIO configuration to avoid electrical conflict.

2. Refer to "Electrical Characteristics" on page 40 for a description of the electrical properties of the pad types used..

## 3.2.2 Peripheral Functions

Each GPIO line can be assigned to one of several peripheral functions. The following table describes how the various peripheral functions are selected. The last listed function has priority in case multiple functions are enabled on the same pin.

| Table 3-2. Per | ipheral Functions |

|----------------|-------------------|

|----------------|-------------------|

| Function                              | Description                               |

|---------------------------------------|-------------------------------------------|

| GPIO Controller Function multiplexing | GPIO and GPIO peripheral selection A to D |

| Nexus OCD AUX port connections        | OCD trace system                          |

| JTAG port connections                 | JTAG debug port                           |

| Oscillators                           | OSC0, OSC1, OSC32                         |

## 3.2.3 Oscillator Pinout

The oscillators are not mapped to the normal GPIO functions and their muxings are controlled by registers in the Power Mananger (PM). Please refer to the PM chapter for more information about this.

| TFBGA144 | QFP144 | VFBGA100          | Pin name | Oscillator pin |

|----------|--------|-------------------|----------|----------------|

| A7       | 18     | A5                | PC02     | XIN0           |

| B7       | 19     | A6                | PC03     | XOUT0          |

| A8       | 13     | B7                | PC04     | XIN1           |

| A9       | 12     | A7                | PC05     | XOUT1          |

| K5       | 98     | K5 <sup>(1)</sup> | PC00     | XIN32          |

| H6       | 99     | K6                | PC01     | XOUT32         |

#### Table 3-3.Oscillator Pinout

Note: 1. This ball is physically connected to 2 GPIOs. Software must managed carrefully the GPIO configuration to avoid electrical conflict

## 3.2.4 JTAG port connections

| TFBGA144 | QFP144 | VFBGA100 | Pin name | JTAG pin |

|----------|--------|----------|----------|----------|

| K12      | 107    | K9       | тск      | ТСК      |

| L12      | 108    | K8       | TDI      | TDI      |

| J11      | 105    | J8       | TDO      | TDO      |

| J10      | 104    | H7       | TMS      | TMS      |

## 3.2.5 Nexus OCD AUX port connections

If the OCD trace system is enabled, the trace system will take control over a number of pins, irrespective of the GPIO configuration. Three differents OCD trace pin mappings are possible, depending on the configuration of the OCD AXS register. For details, see the AVR32 UC Technical Reference Manual.

Table 3-5.

Nexus OCD AUX port connections

| Pin     | AXS=0 | AXS=1 | AXS=2 |

|---------|-------|-------|-------|

| EVTI_N  | PB05  | PA08  | PX00  |

| MDO[5]  | PA00  | PX56  | PX06  |

| MDO[4]  | PA01  | PX57  | PX05  |

| MDO[3]  | PA03  | PX58  | PX04  |

| MDO[2]  | PA16  | PA24  | PX03  |

| MDO[1]  | PA13  | PA23  | PX02  |

| MDO[0]  | PA12  | PA22  | PX01  |

| MSEO[1] | PA10  | PA07  | PX08  |

| MSEO[0] | PA11  | PX55  | PX07  |

| МСКО    | PB07  | PX00  | PB09  |

| EVTO_N  | PB06  | PB06  | PB06  |

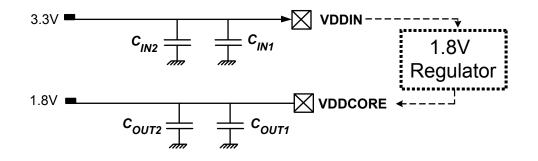

## 3.5 Power Considerations

## 3.5.1 Power Supplies

The AT32UC3A3 has several types of power supply pins:

- VDDIO: Powers I/O lines. Voltage is 3.3 V nominal

- VDDANA: Powers the ADC. Voltage is 3.3V nominal

- VDDIN: Input voltage for the voltage regulator. Voltage is 3.3V nominal

- VDDCORE: Output voltage from regulator for filtering purpose and provides the supply to the core, memories, and peripherals. Voltage is 1.8V nominal

The ground pin GNDCORE is common to VDDCORE and VDDIN. The ground pin for VDDANA is GNDANA. The ground pins for VDDIO are GNDIO.

Refer to Electrical Characteristics chapter for power consumption on the various supply pins.

## 3.5.2 Voltage Regulator

The AT32UC3A3 embeds a voltage regulator that converts from 3.3V to 1.8V with a load of up to 100 mA. The regulator takes its input voltage from VDDIN, and supplies the output voltage on VDDCORE and powers the core, memories and peripherals.

Adequate output supply decoupling is mandatory for VDDCORE to reduce ripple and avoid oscillations.

The best way to achieve this is to use two capacitors in parallel between VDDCORE and GNDCORE:

- One external 470pF (or 1nF) NPO capacitor (COUT1) should be connected as close to the chip as possible.

- One external 2.2µF (or 3.3µF) X7R capacitor (COUT2).

Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop.

The input decoupling capacitor should be placed close to the chip, e.g., two capacitors can be used in parallel (1nF NPO and  $4.7\mu$ F X7R).

For decoupling recommendations for VDDIO and VDDANA please refer to the Schematic checklist.

# 4. Processor and Architecture

Rev: 1.4.2.0

This chapter gives an overview of the AVR32UC CPU. AVR32UC is an implementation of the AVR32 architecture. A summary of the programming model, instruction set, and MPU is presented. For further details, see the AVR32 Architecture Manual and the AVR32UC Technical Reference Manual.

## 4.1 Features

- 32-bit load/store AVR32A RISC architecture

- 15 general-purpose 32-bit registers

- 32-bit Stack Pointer, Program Counter and Link Register reside in register file

- Fully orthogonal instruction set

- Privileged and unprivileged modes enabling efficient and secure Operating Systems

- Innovative instruction set together with variable instruction length ensuring industry leading code density

- DSP extention with saturating arithmetic, and a wide variety of multiply instructions

- 3-stage pipeline allows one instruction per clock cycle for most instructions

- Byte, halfword, word and double word memory access

- Multiple interrupt priority levels

- MPU allows for operating systems with memory protection

## 4.2 AVR32 Architecture

AVR32 is a high-performance 32-bit RISC microprocessor architecture, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption and high code density. In addition, the instruction set architecture has been tuned to allow a variety of microarchitectures, enabling the AVR32 to be implemented as low-, mid-, or high-performance processors. AVR32 extends the AVR family into the world of 32- and 64-bit applications.

Through a quantitative approach, a large set of industry recognized benchmarks has been compiled and analyzed to achieve the best code density in its class. In addition to lowering the memory requirements, a compact code size also contributes to the core's low power characteristics. The processor supports byte and halfword data types without penalty in code size and performance.

Memory load and store operations are provided for byte, halfword, word, and double word data with automatic sign- or zero extension of halfword and byte data. The C-compiler is closely linked to the architecture and is able to exploit code optimization features, both for size and speed.

In order to reduce code size to a minimum, some instructions have multiple addressing modes. As an example, instructions with immediates often have a compact format with a smaller immediate, and an extended format with a larger immediate. In this way, the compiler is able to use the format giving the smallest code size.

Another feature of the instruction set is that frequently used instructions, like add, have a compact format with two operands as well as an extended format with three operands. The larger format increases performance, allowing an addition and a data move in the same instruction in a single cycle. Load and store instructions have several different formats in order to reduce code size and speed up execution.

The following table shows the instructions with support for unaligned addresses. All other instructions require aligned addresses.

**Table 4-1.** Instructions with Unaligned Reference Support

| Instruction | Supported alignment |

|-------------|---------------------|

| ld.d        | Word                |

| st.d        | Word                |

## 4.3.6 Unimplemented Instructions

The following instructions are unimplemented in AVR32UC, and will cause an Unimplemented Instruction Exception if executed:

- All SIMD instructions

- All coprocessor instructions if no coprocessors are present

- retj, incjosp, popjc, pushjc

- tlbr, tlbs, tlbw

- cache

### 4.3.7 CPU and Architecture Revision

Three major revisions of the AVR32UC CPU currently exist.

The Architecture Revision field in the CONFIG0 system register identifies which architecture revision is implemented in a specific device.

AVR32UC CPU revision 3 is fully backward-compatible with revisions 1 and 2, ie. code compiled for revision 1 or 2 is binary-compatible with revision 3 CPUs.

# 4.4 Programming Model

## 4.4.1 Register File Configuration

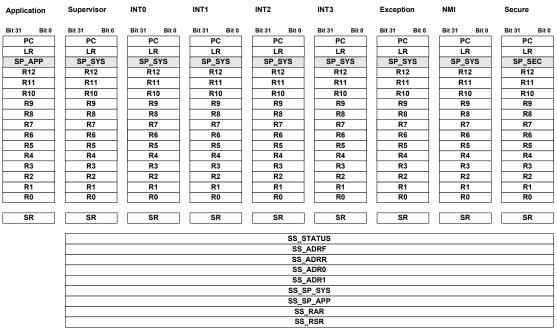

The AVR32UC register file is shown below.

## Figure 4-3. The AVR32UC Register File

## 4.4.2 Status Register Configuration

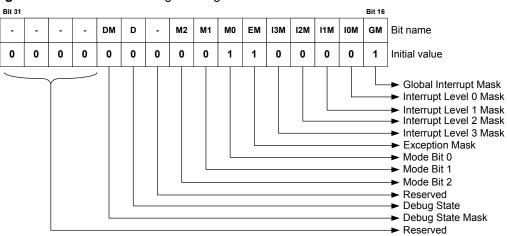

The Status Register (SR) is split into two halfwords, one upper and one lower, see Figure 4-4 on page 26 and Figure 4-5 on page 27. The lower word contains the C, Z, N, V, and Q condition code flags and the R, T, and L bits, while the upper halfword contains information about the mode and state the processor executes in. Refer to the *AVR32 Architecture Manual* for details.

## **Table 5-2.**Peripheral Address Mapping

| pheral Addres | s mapping |                                                                     |

|---------------|-----------|---------------------------------------------------------------------|

| 0xFFFF0C00    | РМ        | Power Manager - PM                                                  |

| 0xFFFF0D00    | RTC       | Real Time Counter - RTC                                             |

| 0xFFFF0D30    | WDT       | Watchdog Timer - WDT                                                |

| 0xFFFF0D80    | EIC       | External Interrupt Controller - EIC                                 |

| 0xFFFF1000    | GPIO      | General Purpose Input/Output Controller - GPIO                      |

| 0xFFFF1400    | USART0    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART0 |

| 0xFFFF1800    | USART1    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART1 |

| 0xFFFF1C00    | USART2    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART2 |

| 0xFFFF2000    | USART3    | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART3 |

| 0xFFFF2400    | SPI0      | Serial Peripheral Interface - SPI0                                  |

| 0xFFFF2800    | SPI1      | Serial Peripheral Interface - SPI1                                  |

| 0xFFFF2C00    | TWIMO     | Two-wire Master Interface - TWIM0                                   |

| 0xFFFF3000    | TWIM1     | Two-wire Master Interface - TWIM1                                   |

| 0xFFFF3400    | SSC       | Synchronous Serial Controller - SSC                                 |

| 0xFFFF3800    | TC0       | Timer/Counter - TC0                                                 |

| 0xFFFF3C00    | ADC       | Analog to Digital Converter - ADC                                   |

| 0xFFFF4000    | ABDAC     | Audio Bitstream DAC - ABDAC                                         |

| 0xFFFF4400    | TC1       | Timer/Counter - TC1                                                 |

|               |           |                                                                     |

| Port | Register                             | Mode   | Local Bus<br>Address | Access     |

|------|--------------------------------------|--------|----------------------|------------|

| 2    | Output Driver Enable Register (ODER) | WRITE  | 0x40000240           | Write-only |

|      |                                      | SET    | 0x40000244           | Write-only |

|      |                                      | CLEAR  | 0x40000248           | Write-only |

|      |                                      | TOGGLE | 0x4000024C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000250           | Write-only |

|      |                                      | SET    | 0x40000254           | Write-only |

|      |                                      | CLEAR  | 0x40000258           | Write-only |

|      |                                      | TOGGLE | 0x4000025C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000260           | Read-only  |

| 3    | Output Driver Enable Register (ODER) | WRITE  | 0x40000340           | Write-only |

|      |                                      | SET    | 0x40000344           | Write-only |

|      |                                      | CLEAR  | 0x40000348           | Write-only |

|      |                                      | TOGGLE | 0x4000034C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000350           | Write-only |

|      |                                      | SET    | 0x40000354           | Write-only |

|      |                                      | CLEAR  | 0x40000358           | Write-only |

|      |                                      | TOGGLE | 0x4000035C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000360           | Read-only  |

Table 5-3.

Local Bus Mapped GPIO Registers

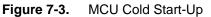

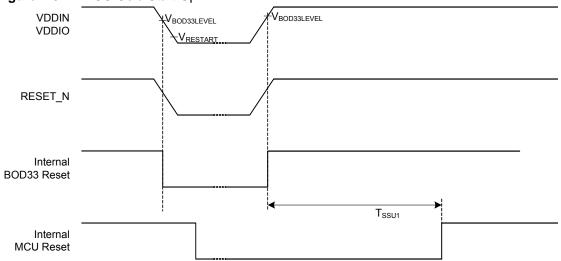

# Table 7-9.BOD Timing

| Symbol           | Parameter                                                | Conditions                        | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------------------------|-----------------------------------|------|------|------|------|

| T <sub>BOD</sub> | Minimum time with VDDCORE < VBOD to detect power failure | Falling VDDCORE from 1.8V to 1.1V |      | 300  | 800  | ns   |

# 7.5.3 Reset Sequence

## Table 7-10. Electrical Characteristics

| Symbol               | Parameter                                                                                                                                          | Conditions                                              | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|------|------|------|

| V <sub>DDRR</sub>    | VDDIN/VDDIO rise rate to ensure<br>power-on-reset                                                                                                  |                                                         | 0.8  |      |      | V/ms |

| V <sub>POR+</sub>    | Rising threshold voltage: voltage up<br>to which device is kept under reset by<br>POR on rising VDDIN                                              | Rising VDDIN: V <sub>RESTART</sub> -> V <sub>POR+</sub> |      | 2.7  |      | V    |

| V <sub>POR-</sub>    | Falling threshold voltage: voltage<br>when POR resets device on falling<br>VDDIN                                                                   | Falling VDDIN: 3.3V -> V <sub>POR-</sub>                |      | 2.7  |      | V    |

| V <sub>RESTART</sub> | On falling VDDIN, voltage must go<br>down to this value before supply can<br>rise again to ensure reset signal is<br>released at V <sub>POR+</sub> | Falling VDDIN: 3.3V -> V <sub>RESTART</sub>             |      |      | 0.2  | V    |

| T <sub>SSU1</sub>    | Time for Cold System Startup: Time<br>for CPU to fetch its first instruction<br>(RCosc not calibrated)                                             |                                                         | 480  |      | 960  | μs   |

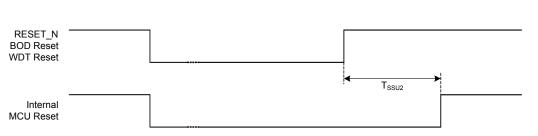

| T <sub>SSU2</sub>    | Time for Hot System Startup: Time for<br>CPU to fetch its first instruction<br>(RCosc calibrated)                                                  |                                                         |      | 420  |      | μs   |

# AT32UC3A3

VDDIN VDDIO

# 7.6.1 Power Consumtion for Different Sleep Modes

| Table 7-12. | Power Consumption for Different Sleep Modes |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| Mode     | Conditions <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                          |                    | Тур.               | Unit   |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------|--|

| Active   | <ul> <li>CPU running a recursive Fibonacci Algorithm from flash ar<br/>at f MHz.</li> <li>Flash High Speed mode disable (f &lt; 66 MHz)</li> <li>Voltage regulator is on.</li> <li>XIN0: external clock. Xin1 Stopped. XIN32 stopped.</li> <li>All peripheral clocks activated with a division by 8.</li> <li>GPIOs are inactive with internal pull-up, JTAG unconnected<br/>pullup and Input pins are connected to GND</li> </ul> | 0.626xf(MHz)+2.257 | mA/MHz             |        |  |

|          | Same conditions with Flash High Speed mode enable (66<                                                                                                                                                                                                                                                                                                                                                                             | f < 84 MHz)        | 0.670xf(MHz)+2.257 | mA/MHz |  |

|          | Same conditions with Flash High Speed mode disable at 60                                                                                                                                                                                                                                                                                                                                                                           | 40                 | mA                 |        |  |

| Idle     | See Active mode conditions                                                                                                                                                                                                                                                                                                                                                                                                         | 0.349xf(MHz)+0.968 | mA/MHz             |        |  |

|          | Same conditions at 60 MHz                                                                                                                                                                                                                                                                                                                                                                                                          |                    | 21.8               | mA     |  |

| Frozen   | See Active mode conditions                                                                                                                                                                                                                                                                                                                                                                                                         |                    | 0.098xf(MHz)+1.012 | mA/MHz |  |

|          | Same conditions at 60 MHz                                                                                                                                                                                                                                                                                                                                                                                                          |                    | 6.6                | mA     |  |

| Standby  | See Active mode conditions                                                                                                                                                                                                                                                                                                                                                                                                         | 0.066xf(MHz)+1.010 | mA/MHz             |        |  |

|          | Same conditions at 60 MHz                                                                                                                                                                                                                                                                                                                                                                                                          | 4.6                | mA                 |        |  |

| Stop     | <ul> <li>- CPU running in sleep mode</li> <li>- XIN0, Xin1 and XIN32 are stopped.</li> <li>- All peripheral clocks are desactived.</li> <li>- GPIOs are inactive with internal pull-up, JTAG unconnected with external pullup and Input pins are connected to GND.</li> </ul>                                                                                                                                                      |                    | 96                 | μA     |  |

| Deepstop | See Stop mode conditions                                                                                                                                                                                                                                                                                                                                                                                                           |                    | 54                 | μA     |  |

| Static   | $T_{A} = 25 \text{ °C}$ CPU is in static mode<br>GPIOs on internal pull-up<br>All peripheral clocks de-activated<br>DM and DP pins connected to ground<br>XIN0, Xin1 and XIN32 are stopped                                                                                                                                                                                                                                         | Amp0               | 31                 | μΑ     |  |

Notes: 1. Core frequency is generated from XIN0 using the PLL.

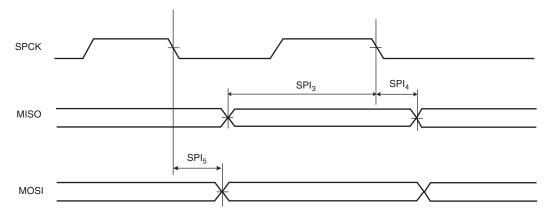

Figure 7-12. SPI Master mode with (CPOL= 0 and NCPHA= 1) or (CPOL= 1 and NCPHA= 0)

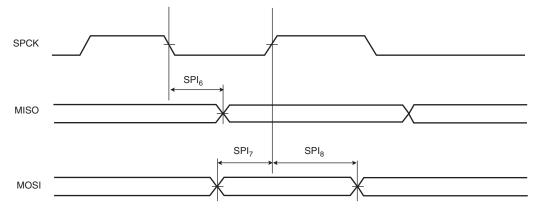

Figure 7-13. SPI Slave mode with (CPOL= 0 and NCPHA= 1) or (CPOL= 1 and NCPHA= 0)

# 8.3 Soldering Profile

Table 8-5 gives the recommended soldering profile from J-STD-20.

| Table 8-5. | Soldering Profile |

|------------|-------------------|

|------------|-------------------|

| Profile Feature                            | Green Package   |

|--------------------------------------------|-----------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/Second max  |

| Preheat Temperature 175°C ±25°C            | 150-200°C       |

| Time Maintained Above 217°C                | 60-150 seconds  |

| Time within 5°C of Actual Peak Temperature | 30 seconds      |

| Peak Temperature Range                     | 260 (+0/-5°C)   |

| Ramp-down Rate                             | 6°C/Second max. |

| Time 25°C to Peak Temperature              | 8 minutes max   |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

# 9. Ordering Information

| Device        | Ordering Code      | Package        | Conditioning | Temperature Operating<br>Range |

|---------------|--------------------|----------------|--------------|--------------------------------|

| AT32UC3A3256S | AT32UC3A3256S-ALUT | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256S-ALUR | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256S-CTUT | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256S-CTUR | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A3256  | AT32UC3A3256-ALUT  | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256-ALUR  | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256-CTUT  | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3256-CTUR  | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A3128S | AT32UC3A3128S-ALUT | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128S-ALUR | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128S-CTUT | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128S-CTUR | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A3128  | AT32UC3A3128-ALUT  | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128-ALUR  | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128-CTUT  | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A3128-CTUR  | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A364S  | AT32UC3A364S-ALUT  | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364S-ALUR  | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364S-CTUT  | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364S-CTUR  | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A364   | AT32UC3A364-ALUT   | 144-lead LQFP  | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364-ALUR   | 144-lead LQFP  | Reels        | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364-CTUT   | 144-ball TFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A364-CTUR   | 144-ball TFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4256S | AT32UC3A4256S-C1UT | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4256S-C1UR | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4256  | AT32UC3A4256-C1UT  | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4256-C1UR  | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4128S | AT32UC3A4128S-C1UT | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4128S-C1UR | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A4128  | AT32UC3A4128-C1UT  | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A4128-C1UR  | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A464S  | AT32UC3A464S-C1UT  | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A464S-C1UR  | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

| AT32UC3A464   | AT32UC3A464-C1UT   | 100-ball VFBGA | Tray         | Industrial (-40·C to 85·C)     |

|               | AT32UC3A464-C1UR   | 100-ball VFBGA | Reels        | Industrial (-40·C to 85·C)     |

# 10. Errata

## 10.1 Rev. H

## 10.1.1 General

Devices with Date Code lower than 1233 cannot operate with CPU frequency higher than 66MHz in 1WS and 36MHz in 0WS in the whole temperature range Fix/Workaround None

DMACA data transfer fails when CTLx.SRC\_TR\_WIDTH is not equal to CTLx.DST\_TR\_WIDTH Fix/Workaround For any DMACA transfer make sure CTLx.SRC\_TR\_WIDTH = CTLx.DST\_TR\_WIDTH.

#### 10.1.2 Processor and Architecture

#### LDM instruction with PC in the register list and without ++ increments Rp

For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12. **Fix/Workaround**

None.

#### Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

## Fix/Workaround

Place breakpoints on earlier or later instructions.

#### When the main clock is RCSYS, TIMER\_CLOCK5 is equal to PBA clock

When the main clock is generated from RCSYS, TIMER\_CLOCK5 is equal to PBA Clock and not PBA Clock / 128. Fix/Workaround

None.

#### 10.1.3 MPU

Privilege violation when using interrupts in application mode with protected system stack

If the system stack is protected by the MPU and an interrupt occurs in application mode, an MPU DTLB exception will occur.

## Fix/Workaround

Make a DTLB Protection (Write) exception handler which permits the interrupt request to be handled in privileged mode.

#### 10.1.4 USB

## UPCFGn.INTFRQ is irrelevant for isochronous pipe

As a consequence, isochronous IN and OUT tokens are sent every 1ms (Full Speed), or every 125uS (High Speed). **Fix/Workaround**

|         |         | <b>Fix/Workaround</b><br>Before going to sleep modes where the system RC oscillator is stopped, make sure that the factor between the CPU/HSB and PBx frequencies is less than or equal to 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.2.9  | PDCA    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | <b>PCONTROL.CHxRES is non-functional</b><br>PCONTROL.CHxRES is non-functional. Counters are reset at power-on, and cannot be<br>reset by software.<br><b>Fix/Workaround</b><br>Software needs to keep history of performance counters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |         | <b>Transfer error will stall a transmit peripheral handshake interface</b><br>If a transfer error is encountered on a channel transmitting to a peripheral, the peripheral<br>handshake of the active channel will stall and the PDCA will not do any more transfers on<br>the affected peripheral handshake interface.<br><b>Fix/Workaround</b><br>Disable and then enable the peripheral after the transfer error.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10.2.10 | AES     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | URAD (Unspecified Register Access Detection Status) does not detect read accesses<br>to the write-only KEYW[58]R registers<br>Fix/Workaround<br>None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10.2.11 | HMATRIX |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | In the PRAS and PRBS registers, the MxPR fields are only two bits<br>In the PRAS and PRBS registers, the MxPR fields are only two bits wide, instead of four bits.<br>The unused bits are undefined when reading the registers.<br>Fix/Workaround<br>Mask undefined bits when reading PRAS and PRBS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10.2.12 | тwiм    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |         | <ul> <li>TWIM SR.IDLE goes high immediately when NAK is received</li> <li>When a NAK is received and there is a non-zero number of bytes to be transmitted, SR.IDLE goes high immediately and does not wait for the STOP condition to be sent. This does not cause any problem just by itself, but can cause a problem if software waits for SR.IDLE to go high and then immediately disables the TWIM by writing a one to CR.MDIS. Disabling the TWIM causes the TWCK and TWD pins to go high immediately, so the STOP condition will not be transmitted correctly.</li> <li>Fix/Workaround</li> <li>If possible, do not disable the TWIM. If it is absolutely necessary to disable the TWIM, there must be a software delay of at least two TWCK periods between the detection of SR.IDLE==1 and the disabling of the TWIM.</li> </ul> |

|         |         | <b>TWIM TWALM polarity is wrong</b><br>The TWALM signal in the TWIM is active high instead of active low.<br><b>Fix/Workaround</b><br>Use an external inverter to invert the signal going into the TWIM. When using both TWIM<br>and TWIS on the same pins, the TWALM cannot be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |        | Fix/Workaround<br>None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.3.14 | MCI    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |        | <ul> <li>The busy signal of the responses R1b is not taken in account for CMD12 STOP_TRANSFER</li> <li>It is not possible to know the busy status of the card during the response (R1b) for the commands CMD12.</li> <li>Fix/Workaround</li> <li>The card busy line should be polled through the GPIO Input Value register (IVR) for commands CMD12.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10.3.15 | SSC    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |        | <ul> <li>Frame Synchro and Frame Synchro Data are delayed by one clock cycle</li> <li>The frame synchro and the frame synchro data are delayed from 1 SSC_CLOCK when:</li> <li>Clock is CKDIV</li> <li>The START is selected on either a frame synchro edge or a level</li> <li>Frame synchro data is enabled</li> <li>Transmit clock is gated on output (through CKO field)</li> <li>Fix/Workaround</li> <li>Transmit or receive CLOCK must not be gated (by the mean of CKO field) when START condition is performed on a generated frame synchro.</li> </ul>                                                                                                                                                                                                                                      |

| 10.3.16 | FLASHC |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |        | <ul> <li>Corrupted read in flash may happen after fuses write or erase operations (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands)</li> <li>After a flash fuse write or erase operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands), reading (data read or code fetch) in flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.</li> <li>Fix/Workaround</li> <li>Before the flash fuse write or erase operation, enable the flash high speed mode (FLASHC HSEN command). The flash fuse write or erase operations (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands) must be issued from RAM or through the EBI. After these commands, read 3 times one flash page initialized to 00h. Disable the flash high</li> </ul> |

speed mode (FLASHC HSDIS command). It is then possible to safely read or code fetch the

flash.

# AT32UC3A3

| 1 Description |        |                                      |    |  |  |

|---------------|--------|--------------------------------------|----|--|--|

| 2             | Overv  | <i>r</i> iew                         | 4  |  |  |

|               | 2.1    | Block Diagram                        | 4  |  |  |

|               | 2.2    | Configuration Summary                | 5  |  |  |

| 3             | Packa  | nge and Pinout                       | 6  |  |  |

|               | 3.1    | Package                              | 6  |  |  |

|               | 3.2    | Peripheral Multiplexing on I/O lines | 9  |  |  |

|               | 3.3    | Signal Descriptions                  | 14 |  |  |

|               | 3.4    | I/O Line Considerations              | 19 |  |  |

|               | 3.5    | Power Considerations                 | 20 |  |  |

| 4             | Proce  | essor and Architecture               | 21 |  |  |

|               | 4.1    | Features                             | 21 |  |  |

|               | 4.2    | AVR32 Architecture                   | 21 |  |  |

|               | 4.3    | The AVR32UC CPU                      | 22 |  |  |

|               | 4.4    | Programming Model                    | 26 |  |  |

|               | 4.5    | Exceptions and Interrupts            |    |  |  |

| 5             | Мето   | 34                                   |    |  |  |

|               | 5.1    | Embedded Memories                    | 34 |  |  |

|               | 5.2    | Physical Memory Map                  | 34 |  |  |

|               | 5.3    | Peripheral Address Map               | 35 |  |  |

|               | 5.4    | CPU Local Bus Mapping                | 37 |  |  |

| 6             | Boot S | Sequence                             | 39 |  |  |

|               | 6.1    | Starting of Clocks                   |    |  |  |

|               | 6.2    | Fetching of Initial Instructions     |    |  |  |

| 7             | Electr | ical Characteristics                 | 40 |  |  |

|               | 7.1    | Absolute Maximum Ratings*            | 40 |  |  |

|               | 7.2    | DC Characteristics                   | 41 |  |  |

|               | 7.3    | I/O pin Characteristics              | 42 |  |  |

|               | 7.4    | Regulator characteristics            | 43 |  |  |

|               | 7.5    | Analog characteristics               | 44 |  |  |

|               | 7.6    | Power Consumption                    | 48 |  |  |

|               | 7.7    | System Clock Characteristics         | 51 |  |  |

|               | 7.8    | Oscillator Characteristics           | 52 |  |  |

|               | 7.9    | ADC Characteristics                  | 54 |  |  |

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1)(408) 441-0311 Fax: (+1)(408) 487-2600 www.atmel.com Atmel Asia Limited Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369 Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

#### Atmel Japan

16F, Shin Osaki Kangyo Bldg. 1-6-4 Osaka Shinagawa-ku Tokyo 104-0032 JAPAN Tel: (+81) 3-6417-0300 Fax: (+81) 3-6417-0370

#### © 2012 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof AVR<sup>®</sup>, Qtouch<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIFCT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROF-ITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.