Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                       |

| Number of I/O              | 88                                                                          |

| Program Memory Size        | 256KB (256K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.75V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-VFBGA                                                                   |

| Supplier Device Package    | 100-VFBGA (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a4256-c1ut |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

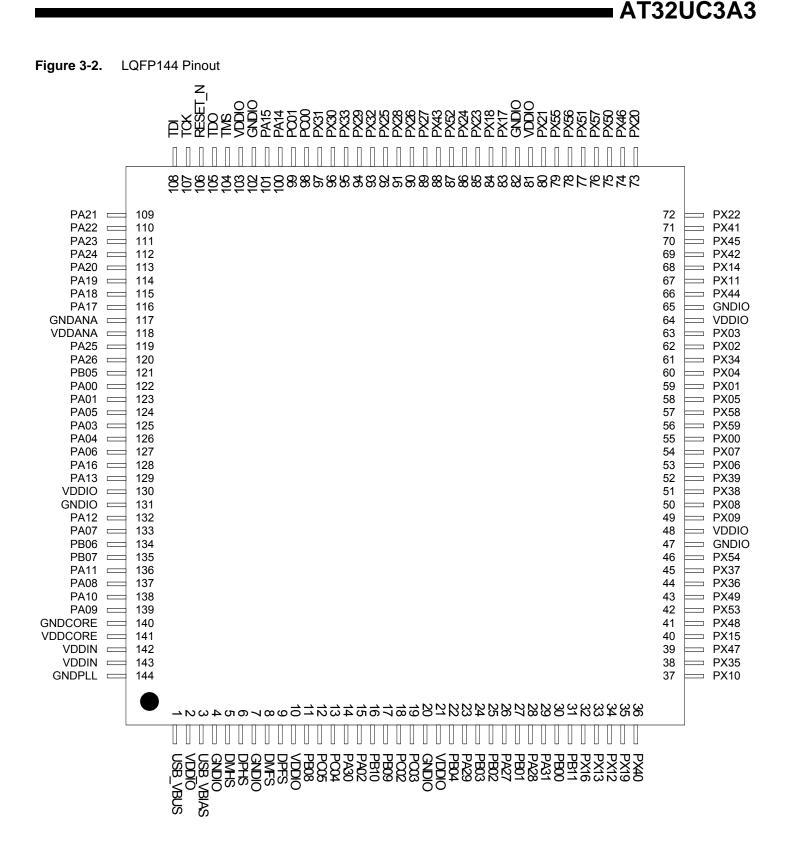

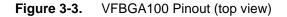

Note: 1. Those balls are physically connected to 2 GPIOs. Software must managed carrefully the GPIO configuration to avoid electrical conflict

# Table 3-6.Signal Description List

| Signal Name | Function                            | Туре             | Active<br>Level | Comments |

|-------------|-------------------------------------|------------------|-----------------|----------|

| RESET_N     | Reset Pin                           | Input            | Low             |          |

|             | DMA Controller - D                  | MACA (optional   | )               | ·        |

| DMAACK[1:0] | DMA Acknowledge                     | Output           |                 |          |

| DMARQ[1:0]  | DMA Requests                        | Input            |                 |          |

|             | External Interrupt                  | Controller - EIC |                 |          |

| EXTINT[7:0] | External Interrupt Pins             | Input            |                 |          |

| SCAN[7:0]   | Keypad Scan Pins                    | Output           |                 |          |

| NMI         | Non-Maskable Interrupt Pin          | Input            | Low             |          |

|             | General Purpose Input/Output pin    | - GPIOA, GPIOB   | , GPIOC, G      | PIOX     |

| PA[31:0]    | Parallel I/O Controller GPIO port A | I/O              |                 |          |

| PB[11:0]    | Parallel I/O Controller GPIO port B | I/O              |                 |          |

| PC[5:0]     | Parallel I/O Controller GPIO port C | I/O              |                 |          |

| PX[59:0]    | Parallel I/O Controller GPIO port X | I/O              |                 |          |

|             | External Bus Ir                     | nterface - EBI   |                 | 1        |

| ADDR[23:0]  | Address Bus                         | Output           |                 |          |

| CAS         | Column Signal                       | Output           | Low             |          |

| CFCE1       | Compact Flash 1 Chip Enable         | Output           | Low             |          |

| CFCE2       | Compact Flash 2 Chip Enable         | Output           | Low             |          |

| CFRNW       | Compact Flash Read Not Write        | Output           |                 |          |

| DATA[15:0]  | Data Bus                            | I/O              |                 |          |

| NANDOE      | NAND Flash Output Enable            | Output           | Low             |          |

| NANDWE      | NAND Flash Write Enable             | Output           | Low             |          |

| NCS[5:0]    | Chip Select                         | Output           | Low             |          |

| NRD         | Read Signal                         | Output           | Low             |          |

| NWAIT       | External Wait Signal                | Input            | Low             |          |

| NWE0        | Write Enable 0                      | Output           | Low             |          |

| NWE1        | Write Enable 1                      | Output           | Low             |          |

| RAS         | Row Signal                          | Output           | Low             |          |

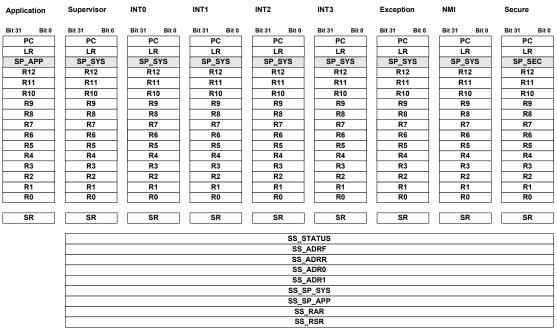

The register file is organized as sixteen 32-bit registers and includes the Program Counter, the Link Register, and the Stack Pointer. In addition, register R12 is designed to hold return values from function calls and is used implicitly by some instructions.

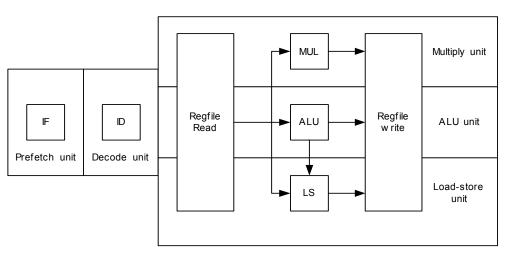

## 4.3 The AVR32UC CPU

The AVR32UC CPU targets low- and medium-performance applications, and provides an advanced OCD system, no caches, and a Memory Protection Unit (MPU). Java acceleration hardware is not implemented.

AVR32UC provides three memory interfaces, one High Speed Bus master for instruction fetch, one High Speed Bus master for data access, and one High Speed Bus slave interface allowing other bus masters to access data RAMs internal to the CPU. Keeping data RAMs internal to the CPU allows fast access to the RAMs, reduces latency, and guarantees deterministic timing. Also, power consumption is reduced by not needing a full High Speed Bus access for memory accesses. A dedicated data RAM interface is provided for communicating with the internal data RAMs.

A local bus interface is provided for connecting the CPU to device-specific high-speed systems, such as floating-point units and fast GPIO ports. This local bus has to be enabled by writing the LOCEN bit in the CPUCR system register. The local bus is able to transfer data between the CPU and the local bus slave in a single clock cycle. The local bus has a dedicated memory range allocated to it, and data transfers are performed using regular load and store instructions. Details on which devices that are mapped into the local bus space is given in the Memories chapter of this data sheet.

Figure 4-1 on page 23 displays the contents of AVR32UC.

## 4.3.2 AVR32A Microarchitecture Compliance

AVR32UC implements an AVR32A microarchitecture. The AVR32A microarchitecture is targeted at cost-sensitive, lower-end applications like smaller microcontrollers. This microarchitecture does not provide dedicated hardware registers for shadowing of register file registers in interrupt contexts. Additionally, it does not provide hardware registers for the return address registers and return status registers. Instead, all this information is stored on the system stack. This saves chip area at the expense of slower interrupt handling.

Upon interrupt initiation, registers R8-R12 are automatically pushed to the system stack. These registers are pushed regardless of the priority level of the pending interrupt. The return address and status register are also automatically pushed to stack. The interrupt handler can therefore use R8-R12 freely. Upon interrupt completion, the old R8-R12 registers and status register are restored, and execution continues at the return address stored popped from stack.

The stack is also used to store the status register and return address for exceptions and *scall*. Executing the *rete* or *rets* instruction at the completion of an exception or system call will pop this status register and continue execution at the popped return address.

### 4.3.3 Java Support

AVR32UC does not provide Java hardware acceleration.

## 4.3.4 Memory Protection

The MPU allows the user to check all memory accesses for privilege violations. If an access is attempted to an illegal memory address, the access is aborted and an exception is taken. The MPU in AVR32UC is specified in the AVR32UC Technical Reference manual.

### 4.3.5 Unaligned Reference Handling

AVR32UC does not support unaligned accesses, except for doubleword accesses. AVR32UC is able to perform word-aligned *st.d* and *ld.d*. Any other unaligned memory access will cause an address exception. Doubleword-sized accesses with word-aligned pointers will automatically be performed as two word-sized accesses.

# 4.4 Programming Model

## 4.4.1 Register File Configuration

The AVR32UC register file is shown below.

### Figure 4-3. The AVR32UC Register File

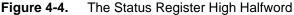

### 4.4.2 Status Register Configuration

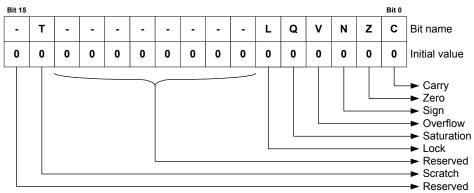

The Status Register (SR) is split into two halfwords, one upper and one lower, see Figure 4-4 on page 26 and Figure 4-5 on page 27. The lower word contains the C, Z, N, V, and Q condition code flags and the R, T, and L bits, while the upper halfword contains information about the mode and state the processor executes in. Refer to the *AVR32 Architecture Manual* for details.

Figure 4-5. The Status Register Low Halfword

### 4.4.3 Processor States

#### 4.4.3.1 Normal RISC State

The AVR32 processor supports several different execution contexts as shown in Table 4-2 on page 27.

| able 4-2. Overview of Execution modes, their Findhites and Findhege Levels. |                        |              |                                           |  |  |

|-----------------------------------------------------------------------------|------------------------|--------------|-------------------------------------------|--|--|

| Priority                                                                    | Mode                   | Security     | Description                               |  |  |

| 1                                                                           | Non Maskable Interrupt | Privileged   | Non Maskable high priority interrupt mode |  |  |

| 2                                                                           | Exception              | Privileged   | Execute exceptions                        |  |  |

| 3                                                                           | Interrupt 3            | Privileged   | General purpose interrupt mode            |  |  |

| 4                                                                           | Interrupt 2            | Privileged   | General purpose interrupt mode            |  |  |

| 5                                                                           | Interrupt 1            | Privileged   | General purpose interrupt mode            |  |  |

| 6                                                                           | Interrupt 0            | Privileged   | General purpose interrupt mode            |  |  |

| N/A                                                                         | Supervisor             | Privileged   | Runs supervisor calls                     |  |  |

| N/A                                                                         | Application            | Unprivileged | Normal program execution mode             |  |  |

Table 4-2. Overview of Execution Modes, their Priorities and Privilege Levels.

Mode changes can be made under software control, or can be caused by external interrupts or exception processing. A mode can be interrupted by a higher priority mode, but never by one with lower priority. Nested exceptions can be supported with a minimal software overhead.

When running an operating system on the AVR32, user processes will typically execute in the application mode. The programs executed in this mode are restricted from executing certain instructions. Furthermore, most system registers together with the upper halfword of the status register cannot be accessed. Protected memory areas are also not available. All other operating modes are privileged and are collectively called System Modes. They have full access to all privileged and unprivileged resources. After a reset, the processor will be in supervisor mode.

### 4.4.3.2 Debug State

The AVR32 can be set in a debug state, which allows implementation of software monitor routines that can read out and alter system information for use during application development. This implies that all system and application registers, including the status registers and program counters, are accessible in debug state. The privileged instructions are also available.

| Table 4-3. | System Re | egisters (Continu | ied)                                   |

|------------|-----------|-------------------|----------------------------------------|

| Reg #      | Address   | Name              | Function                               |

| 26         | 104       | JAVA_LV3          | Unused in AVR32UC                      |

| 27         | 108       | JAVA_LV4          | Unused in AVR32UC                      |

| 28         | 112       | JAVA_LV5          | Unused in AVR32UC                      |

| 29         | 116       | JAVA_LV6          | Unused in AVR32UC                      |

| 30         | 120       | JAVA_LV7          | Unused in AVR32UC                      |

| 31         | 124       | JTBA              | Unused in AVR32UC                      |

| 32         | 128       | JBCR              | Unused in AVR32UC                      |

| 33-63      | 132-252   | Reserved          | Reserved for future use                |

| 64         | 256       | CONFIG0           | Configuration register 0               |

| 65         | 260       | CONFIG1           | Configuration register 1               |

| 66         | 264       | COUNT             | Cycle Counter register                 |

| 67         | 268       | COMPARE           | Compare register                       |

| 68         | 272       | TLBEHI            | Unused in AVR32UC                      |

| 69         | 276       | TLBELO            | Unused in AVR32UC                      |

| 70         | 280       | PTBR              | Unused in AVR32UC                      |

| 71         | 284       | TLBEAR            | Unused in AVR32UC                      |

| 72         | 288       | MMUCR             | Unused in AVR32UC                      |

| 73         | 292       | TLBARLO           | Unused in AVR32UC                      |

| 74         | 296       | TLBARHI           | Unused in AVR32UC                      |

| 75         | 300       | PCCNT             | Unused in AVR32UC                      |

| 76         | 304       | PCNT0             | Unused in AVR32UC                      |

| 77         | 308       | PCNT1             | Unused in AVR32UC                      |

| 78         | 312       | PCCR              | Unused in AVR32UC                      |

| 79         | 316       | BEAR              | Bus Error Address Register             |

| 80         | 320       | MPUAR0            | MPU Address Register region 0          |

| 81         | 324       | MPUAR1            | MPU Address Register region 1          |

| 82         | 328       | MPUAR2            | MPU Address Register region 2          |

| 83         | 332       | MPUAR3            | MPU Address Register region 3          |

| 84         | 336       | MPUAR4            | MPU Address Register region 4          |

| 85         | 340       | MPUAR5            | MPU Address Register region 5          |

| 86         | 344       | MPUAR6            | MPU Address Register region 6          |

| 87         | 348       | MPUAR7            | MPU Address Register region 7          |

| 88         | 352       | MPUPSR0           | MPU Privilege Select Register region 0 |

| 89         | 356       | MPUPSR1           | MPU Privilege Select Register region 1 |

| 90         | 360       | MPUPSR2           | MPU Privilege Select Register region 2 |

| 91         | 364       | MPUPSR3           | MPU Privilege Select Register region 3 |

Table 4-3.

System Registers (Continued)

# 7. Electrical Characteristics

# 7.1 Absolute Maximum Ratings\*

| Operating Temperature40°C to +85°C                            |

|---------------------------------------------------------------|

| Storage Temperature60°C to +150°C                             |

| Voltage on Input Pin<br>with respect to Ground0.3V to 3.6V    |

| Maximum Operating Voltage (VDDCORE) 1.95V                     |

| Maximum Operating Voltage (VDDIO)                             |

| Total DC Output Current on all I/O Pin<br>for TQFP144 package |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Table 7-9. BOD Timing

| Symbol           | Parameter                                                | Conditions                        | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------------------------|-----------------------------------|------|------|------|------|

| T <sub>BOD</sub> | Minimum time with VDDCORE < VBOD to detect power failure | Falling VDDCORE from 1.8V to 1.1V |      | 300  | 800  | ns   |

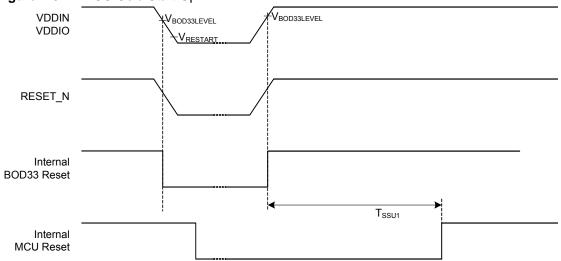

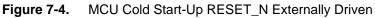

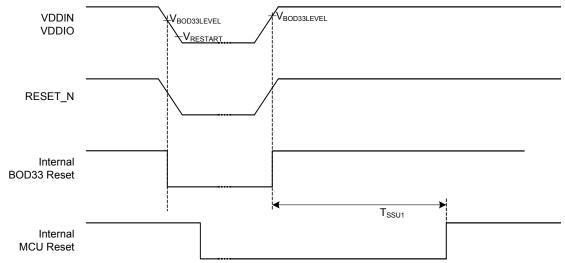

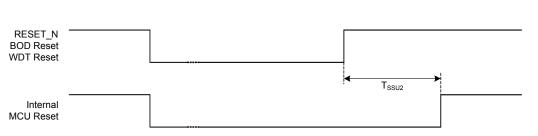

## 7.5.3 Reset Sequence

## Table 7-10. Electrical Characteristics

| Symbol               | Parameter                                                                                                                                          | Conditions                                              | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|------|------|------|

| V <sub>DDRR</sub>    | VDDIN/VDDIO rise rate to ensure<br>power-on-reset                                                                                                  |                                                         | 0.8  |      |      | V/ms |

| V <sub>POR+</sub>    | Rising threshold voltage: voltage up<br>to which device is kept under reset by<br>POR on rising VDDIN                                              | Rising VDDIN: V <sub>RESTART</sub> -> V <sub>POR+</sub> |      | 2.7  |      | V    |

| V <sub>POR-</sub>    | Falling threshold voltage: voltage<br>when POR resets device on falling<br>VDDIN                                                                   | Falling VDDIN: 3.3V -> V <sub>POR-</sub>                |      | 2.7  |      | V    |

| V <sub>RESTART</sub> | On falling VDDIN, voltage must go<br>down to this value before supply can<br>rise again to ensure reset signal is<br>released at V <sub>POR+</sub> | Falling VDDIN: 3.3V -> V <sub>RESTART</sub>             |      |      | 0.2  | V    |

| T <sub>SSU1</sub>    | Time for Cold System Startup: Time<br>for CPU to fetch its first instruction<br>(RCosc not calibrated)                                             |                                                         | 480  |      | 960  | μs   |

| T <sub>SSU2</sub>    | Time for Hot System Startup: Time for<br>CPU to fetch its first instruction<br>(RCosc calibrated)                                                  |                                                         |      | 420  |      | μs   |

# AT32UC3A3

VDDIN VDDIO

## 7.6.1 Power Consumtion for Different Sleep Modes

| Table 7-12. | Power Consumption for Different Sleep Modes |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| Mode     | Conditions <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                          |                          | Тур.               | Unit   |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------|--------|

| Active   | <ul> <li>CPU running a recursive Fibonacci Algorithm from flash ar<br/>at f MHz.</li> <li>Flash High Speed mode disable (f &lt; 66 MHz)</li> <li>Voltage regulator is on.</li> <li>XIN0: external clock. Xin1 Stopped. XIN32 stopped.</li> <li>All peripheral clocks activated with a division by 8.</li> <li>GPIOs are inactive with internal pull-up, JTAG unconnected<br/>pullup and Input pins are connected to GND</li> </ul> |                          | 0.626xf(MHz)+2.257 | mA/MHz |

|          | Same conditions with Flash High Speed mode enable (66<                                                                                                                                                                                                                                                                                                                                                                             | f < 84 MHz)              | 0.670xf(MHz)+2.257 | mA/MHz |

|          | Same conditions with Flash High Speed mode disable at 60                                                                                                                                                                                                                                                                                                                                                                           | ) MHz                    | 40                 | mA     |

| Idle     | See Active mode conditions                                                                                                                                                                                                                                                                                                                                                                                                         |                          | 0.349xf(MHz)+0.968 | mA/MHz |

|          | Same conditions at 60 MHz                                                                                                                                                                                                                                                                                                                                                                                                          |                          |                    | mA     |

| Frozen   | See Active mode conditions                                                                                                                                                                                                                                                                                                                                                                                                         | e Active mode conditions |                    | mA/MHz |

|          | Same conditions at 60 MHz                                                                                                                                                                                                                                                                                                                                                                                                          | nditions at 60 MHz       |                    | mA     |

| Standby  | See Active mode conditions                                                                                                                                                                                                                                                                                                                                                                                                         |                          | 0.066xf(MHz)+1.010 | mA/MHz |

|          | Same conditions at 60 MHz                                                                                                                                                                                                                                                                                                                                                                                                          |                          | 4.6                | mA     |

| Stop     | <ul> <li>CPU running in sleep mode</li> <li>XIN0, Xin1 and XIN32 are stopped.</li> <li>All peripheral clocks are desactived.</li> <li>GPIOs are inactive with internal pull-up, JTAG unconnected with external pullup and Input pins are connected to GND.</li> </ul>                                                                                                                                                              |                          | 96                 | μA     |

| Deepstop | See Stop mode conditions                                                                                                                                                                                                                                                                                                                                                                                                           |                          | 54                 | μA     |

| Static   | $ \begin{array}{l} T_A = 25 \ ^\circ C \\ CPU \ \text{is in static mode} \\ GPIOs \ \text{on internal pull-up} \\ All \ \text{peripheral clocks de-activated} \\ DM \ \text{and DP pins connected to ground} \\ XIN0, \ Xin1 \ \text{and XIN32 are stopped} \end{array} $                                                                                                                                                          | Amp0                     | 31                 | μΑ     |

Notes: 1. Core frequency is generated from XIN0 using the PLL.

# 7.8 Oscillator Characteristics

The following characteristics are applicable to the operating temperature range:  $T_A = -40^{\circ}C$  to 85°C and worst case of power supply, unless otherwise specified.

## 7.8.1 Slow Clock RC Oscillator

| Table 7-17. | RC Oscillator Frequency |

|-------------|-------------------------|

|-------------|-------------------------|

| Symbol          | Parameter               | Conditions                             | Min. | Тур.  | Max. | Unit |

|-----------------|-------------------------|----------------------------------------|------|-------|------|------|

| F <sub>RC</sub> | RC Oscillator Frequency | Calibration point: $T_A = 85^{\circ}C$ |      | 115.2 | 116  | KHz  |

|                 |                         | $T_A = 25^{\circ}C$                    |      | 112   |      | KHz  |

|                 |                         | $T_A = -40^{\circ}C$                   | 105  | 108   |      | KHz  |

## 7.8.2 32 KHz Oscillator

| Table 7-18. | 32 KHz Oscillator Characteristic | s |

|-------------|----------------------------------|---|

|             |                                  | - |

| Symbol                    | Parameter                            | Conditions                                | Min.                | Тур.   | Max.                | Unit |

|---------------------------|--------------------------------------|-------------------------------------------|---------------------|--------|---------------------|------|

| 4 //+                     | Ossillator Fraguency                 | External clock on XIN32                   |                     |        | 30                  | MHz  |

| 1/(t <sub>CP32KHz</sub> ) | Oscillator Frequency                 | Crystal                                   |                     | 32 768 |                     | Hz   |

| CL                        | Equivalent Load Capacitance          |                                           | 6                   |        | 12.5                | pF   |

| ESR                       | Crystal Equivalent Series Resistance |                                           |                     |        | 100                 | KΩ   |

| t <sub>ST</sub>           | Startup Time                         | $C_L = 6pF^{(1)}$<br>$C_L = 12.5pF^{(1)}$ |                     |        | 600<br>1200         | ms   |

| t <sub>CH</sub>           | XIN32 Clock High Half-period         |                                           | 0.4 t <sub>CP</sub> |        | 0.6 t <sub>CP</sub> |      |

| t <sub>CL</sub>           | XIN32 Clock Low Half-period          |                                           | 0.4 t <sub>CP</sub> |        | 0.6 t <sub>CP</sub> |      |

| C <sub>IN</sub>           | XIN32 Input Capacitance              |                                           |                     |        | 5                   | pF   |

|                           | Current Concurrentian                | Active mode                               |                     |        | 1.8                 | μA   |

| I <sub>OSC</sub>          | Current Consumption                  | Standby mode                              |                     |        | 0.1                 | μA   |

Note: 1.  $C_L$  is the equivalent load capacitance.

| Parameter                  | Conditions          | Min. | Тур. | Max. | Unit |

|----------------------------|---------------------|------|------|------|------|

| Resolution                 |                     |      | 10   |      | Bit  |

| Absolute Accuracy          | ADC Clock = 5 MHz   |      |      | 3    | LSB  |

| Integral Non-linearity     | ADC Clock = 5 MHz   |      | 1.5  | 2    | LSB  |

|                            | ADC Clock = 5 MHz   |      | 1    | 2    | LSB  |

| Differential Non-linearity | ADC Clock = 2.5 MHz |      | 0.6  | 1    | LSB  |

| Offset Error               | ADC Clock = 5 MHz   | -2   |      | 2    | LSB  |

| Gain Error                 | ADC Clock = 5 MHz   | -2   |      | 2    | LSB  |

## **Table 7-26.**Transfer Characteristics in 10-bit mode

## 7.10 USB Transceiver Characteristics

## 7.10.1 Electrical Characteristics

## Table 7-27. Electrical Parameters

| Symbol            | Parameter                                   | Conditions                           | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------------------|--------------------------------------|------|------|------|------|

| R <sub>EXT</sub>  | Recommended External USB Series<br>Resistor | In series with each USB pin with ±5% |      | 39   |      | Ω    |

| R <sub>BIAS</sub> | VBIAS External Resistor <sup>(1)</sup>      | ±1%                                  |      | 6810 |      | Ω    |

| C <sub>BIAS</sub> | VBIAS External Capcitor                     |                                      |      | 10   |      | pF   |

1. The USB on-chip buffers comply with the Universal Serial Bus (USB) v2.0 standard. All AC parameters related to these buffers can be found within the USB 2.0 electrical specifications.

## 7.10.2 Static Power Consumption

### Table 7-28. Static Power Consumption

| Symbol               | Parameter                                     | Conditions                                                                                    | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>BIAS</sub>    | Bias current consumption on VBG               |                                                                                               |      |      | 1    | μA   |

|                      | HS Transceiver and I/O current consumption    |                                                                                               |      |      | 8    | μA   |

| I <sub>VDDUTMI</sub> | FS/HS Transceiver and I/O current consumption | If cable is connected, add 200µA<br>(typical) due to Pull-up/Pull-down<br>current consumption |      |      | 3    | μA   |

## 7.10.3 Dynamic Power Consumption

### **Table 7-29.**Dynamic Power Consumption

| Symbol            | Parameter                       | Conditions | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------|------------|------|------|------|------|

| I <sub>BIAS</sub> | Bias current consumption on VBG |            |      | 0.7  | 0.8  | mA   |

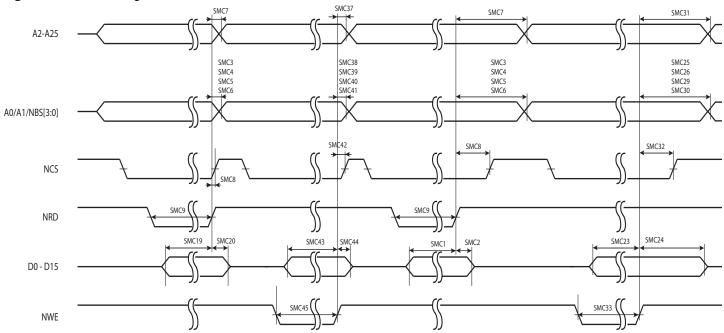

# 7.11 EBI Timings

## 7.11.1 SMC Signals

These timings are given for worst case process, T =  $85 \cdot C$ , VDDIO = 3V and 40 pF load capacitance.

## Table 7-30. SMC Clock Signal

| Symbol                  | Parameter                      | Max. <sup>(1)</sup>     | Unit |

|-------------------------|--------------------------------|-------------------------|------|

| 1/(t <sub>CPSMC</sub> ) | SMC Controller Clock Frequency | 1/(t <sub>cpcpu</sub> ) | MHz  |

Note: 1. The maximum frequency of the SMC interface is the same as the max frequency for the HSB.

## Table 7-31. SMC Read Signals with Hold Settings

| Symbol            | Parameter                                  | Min.                                                              |    |

|-------------------|--------------------------------------------|-------------------------------------------------------------------|----|

|                   | NRD Control                                | led (READ_MODE = 1)                                               |    |

| SMC <sub>1</sub>  | Data Setup before NRD High                 | 12                                                                | ns |

| SMC <sub>2</sub>  | Data Hold after NRD High                   | 0                                                                 | ns |

| SMC <sub>3</sub>  | NRD High to NBS0/A0 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                        | ns |

| SMC <sub>4</sub>  | NRD High to NBS1 Change <sup>(1)</sup>     | nrd hold length * t <sub>CPSMC</sub> - 1.3                        | ns |

| SMC <sub>5</sub>  | NRD High to NBS2/A1 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                        | ns |

| SMC <sub>7</sub>  | NRD High to A2 - A23 Change <sup>(1)</sup> | nrd hold length * t <sub>CPSMC</sub> - 1.3                        | ns |

| SMC <sub>8</sub>  | NRD High to NCS Inactive <sup>(1)</sup>    | (nrd hold length - ncs rd hold length) * t <sub>CPSMC</sub> - 2.3 | ns |

| SMC <sub>9</sub>  | NRD Pulse Width                            | nrd pulse length * t <sub>CPSMC</sub> - 1.4                       | ns |

|                   | NRD Control                                | led (READ_MODE = 0)                                               |    |

| SMC <sub>10</sub> | Data Setup before NCS High                 | 11.5                                                              | ns |

| SMC <sub>11</sub> | Data Hold after NCS High                   | 0                                                                 | ns |

| SMC <sub>12</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                     | ns |

| SMC <sub>13</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                     | ns |

| SMC <sub>14</sub> | NCS High to NBS2/A1 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                     | ns |

| SMC <sub>16</sub> | NCS High to A2 - A23 Change <sup>(1)</sup> | ncs rd hold length * t <sub>CPSMC</sub> - 4                       | ns |

| SMC <sub>17</sub> | NCS High to NRD Inactive <sup>(1)</sup>    | ncs rd hold length - nrd hold length)* t <sub>CPSMC</sub> - 1.3   | ns |

| SMC <sub>18</sub> | NCS Pulse Width                            | ncs rd pulse length * t <sub>CPSMC</sub> - 3.6                    | ns |

Note: 1. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs rd hold length" or "nrd hold length".

Figure 7-8. SMC Signals for NRD and NRW Controlled Accesses.

## 7.11.2 SDRAM Signals

## Table 7-35. SDRAM Clock Signal.

| Symbol                   | Parameter                        | Conditions | Min. | Max. <sup>(1)</sup>     | Unit |

|--------------------------|----------------------------------|------------|------|-------------------------|------|

| 1/(t <sub>CPSDCK</sub> ) | SDRAM Controller Clock Frequency |            |      | 1/(t <sub>cpcpu</sub> ) | MHz  |

Note: 1. The maximum frequency of the SDRAMC interface is the same as the max frequency for the HSB.

| Table 7-36. | SDRAM Clock Signal |

|-------------|--------------------|

|-------------|--------------------|

| Symbol               | Parameter                              | Conditions | Min. | Max. | Unit |

|----------------------|----------------------------------------|------------|------|------|------|

| SDRAMC <sub>1</sub>  | SDCKE High before SDCK Rising Edge     |            | 7.4  |      | ns   |

| SDRAMC <sub>2</sub>  | SDCKE Low after SDCK Rising Edge       |            | 3.2  |      | ns   |

| SDRAMC <sub>3</sub>  | SDCKE Low before SDCK Rising Edge      |            | 7    |      | ns   |

| SDRAMC <sub>4</sub>  | SDCKE High after SDCK Rising Edge      |            | 2.9  |      | ns   |

| SDRAMC <sub>5</sub>  | SDCS Low before SDCK Rising Edge       |            | 7.5  |      | ns   |

| SDRAMC <sub>6</sub>  | SDCS High after SDCK Rising Edge       |            | 1.6  |      | ns   |

| SDRAMC <sub>7</sub>  | RAS Low before SDCK Rising Edge        |            | 7.2  |      | ns   |

| SDRAMC <sub>8</sub>  | RAS High after SDCK Rising Edge        |            | 2.3  |      | ns   |

| SDRAMC <sub>9</sub>  | SDA10 Change before SDCK Rising Edge   |            | 7.6  |      | ns   |

| SDRAMC <sub>10</sub> | SDA10 Change after SDCK Rising Edge    |            | 1.9  |      | ns   |

| SDRAMC <sub>11</sub> | Address Change before SDCK Rising Edge |            | 6.2  |      | ns   |

| SDRAMC <sub>12</sub> | Address Change after SDCK Rising Edge  |            | 2.2  |      | ns   |

These timings are given for 10 pF load on SDCK and 40 pF on other signals.

# 8.3 Soldering Profile

Table 8-5 gives the recommended soldering profile from J-STD-20.

| Table 8-5. | Soldering Profile |

|------------|-------------------|

|------------|-------------------|

| Profile Feature                            | Green Package   |

|--------------------------------------------|-----------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/Second max  |

| Preheat Temperature 175°C ±25°C            | 150-200°C       |

| Time Maintained Above 217°C                | 60-150 seconds  |

| Time within 5°C of Actual Peak Temperature | 30 seconds      |

| Peak Temperature Range                     | 260 (+0/-5°C)   |

| Ramp-down Rate                             | 6°C/Second max. |

| Time 25°C to Peak Temperature              | 8 minutes max   |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

|        |       | For higher polling time, the software must freeze the pipe for the desired period in order to prevent any "extra" token.                                                                                                                                                                                                                                                                                                       |

|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.1.5 | ADC   |                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |       | <ul> <li>Sleep Mode activation needs additional A to D conversion</li> <li>If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.</li> <li>Fix/Workaround</li> <li>Activate the sleep mode in the mode register and then perform an AD conversion.</li> </ul>                                                                                          |

| 10.1.6 | USART |                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |       | ISO7816 info register US_NER cannot be read<br>The NER register always returns zero.<br>Fix/Workaround<br>None.                                                                                                                                                                                                                                                                                                                |

|        |       | The LIN ID is not transmitted in mode PDCM='0'                                                                                                                                                                                                                                                                                                                                                                                 |

|        |       | <b>Fix/Workaround</b><br>Using USART in mode LIN master with the PDCM bit = '0', the LINID written at the first<br>address of the transmit buffer is not used. The LINID must be written in the LINIR register,<br>after the configuration and start of the PDCA transfer. Writing the LINID in the LINIR register<br>will start the transfer whenever the PDCA transfer is ready.                                             |

|        |       | The LINID interrupt is only available for the header reception and not available for the header transmission<br>Fix/Workaround<br>None.                                                                                                                                                                                                                                                                                        |

|        |       | USART LIN mode is not functional with the PDCA if PDCM bit in LINMR register is set                                                                                                                                                                                                                                                                                                                                            |

|        |       | to 1<br>If a PDCA transfer is initiated in USART LIN mode with PDCM bit set to 1, the transfer never<br>starts.<br>Fix/Workaround                                                                                                                                                                                                                                                                                              |

|        |       | Only use PDCM=0 configuration with the PDCA transfer.                                                                                                                                                                                                                                                                                                                                                                          |

| 10.1.7 | SPI   |                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |       | <ul> <li>SPI disable does not work in SLAVE mode</li> <li>SPI disable does not work in SLAVE mode.</li> <li>Fix/Workaround</li> <li>Read the last received data, then perform a software reset by writing a one to the Software</li> <li>Reset bit in the Control Register (CR.SWRST).</li> </ul>                                                                                                                              |

|        |       | SPI bad serial clock generation on 2nd chip_select when SCBR=1, CPOL=1, and NCPHA=0<br>When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.<br>Fix/Workaround<br>When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 |

if CSRn.CPOL=1 and CSRn.NCPHA=0.

|         |         | <b>TWIS stretch on Address match error</b><br>When the TWIS stretches TWCK due to a slave address match, it also holds TWD low for<br>the same duration if it is to be receiving data. When TWIS releases TWCK, it releases TWD<br>at the same time. This can cause a TWI timing violation.<br><b>Fix/Workaround</b><br>None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.1.14 | SSC     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |         | <ul> <li>Frame Synchro and Frame Synchro Data are delayed by one clock cycle</li> <li>The frame synchro and the frame synchro data are delayed from 1 SSC_CLOCK when:</li> <li>Clock is CKDIV</li> <li>The START is selected on either a frame synchro edge or a level</li> <li>Frame synchro data is enabled</li> <li>Transmit clock is gated on output (through CKO field)</li> <li>Fix/Workaround</li> <li>Transmit or receive CLOCK must not be gated (by the mean of CKO field) when START condition is performed on a generated frame synchro.</li> </ul>                                                                                                                                                                                                                                                                                                                               |

| 10.1.15 | FLASHC  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |         | Corrupted read in flash may happen after fuses write or erase operations (FLASHC<br>LP, UP, WGPB, EGPB, SSB, PGPFB, EAGPF commands).<br>After a flash fuse write or erase operation (FLASHC LP, UP, WGPB, EGPB, SSB, PGPFB,<br>EAGPF commands), reading (data read or code fetch) in flash may fail. This may lead to an<br>exception or to other errors derived from this corrupted read access.<br><b>Fix/Workaround</b><br>Before the flash fuse write or erase operation, enable the flash high speed mode (FLASHC<br>HSEN command). The flash fuse write or erase operations (FLASHC LP, UP, WGPB,<br>EGPB, SSB, PGPFB, EAGPF commands) must be issued from RAM or through the EBI.<br>After these commands, read 3 times one flash page initialized to 00h. Disable the flash high<br>speed mode (FLASHC HSDIS command). It is then possible to safely read or code fetch the<br>flash. |

| 10.2 R  | lev. E  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10.2.1  | General | Devices cannot operate with CPU frequency higher than 66MHz in 1WS and 36MHz in<br>0WS<br>Fix/Workaround<br>None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |         | <ul> <li>Increased Power Consumption in VDDIO in sleep modes</li> <li>If the OSC0 is enabled in crystal mode when entering a sleep mode where the OSC0 is disabled, this will lead to an increased power consumption in VDDIO.</li> <li>Fix/Workaround</li> <li>Disable the OSC0 through the System Control Interface (SCIF) before going to any sleep mode where the OSC0 is disabled, or pull down or up XIN0 and XOUT0 with 1 Mohm resistor.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Power consumption in static mode The power consumption in static mode can be up to  $330\mu A$  on some parts (typical at  $25^{\circ}C$ )

#### Fix/Workaround

Set to 1b bit CORRS4 of the ECCHRS mode register (MD). In C-code: \*((volatile int\*) (0xFFFE2404))= 0x400.

DMACA data transfer fails when CTLx.SRC\_TR\_WIDTH is not equal to CTLx.DST\_TR\_WIDTH Fix/Workaround For any DMACA transfer make sure CTLx.SRC\_TR\_WIDTH = CTLx.DST\_TR\_WIDTH.

#### 3.3V supply monitor is not available

FGPFRLO[30:29] are reserved and should not be used by the application. **Fix/Workaround** None.

Service access bus (SAB) can not access DMACA registers Fix/Workaround None.

## 10.2.2 Processor and Architecture

#### LDM instruction with PC in the register list and without ++ increments Rp

For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12. **Fix/Workaround**

None.

#### Hardware breakpoints may corrupt MAC results

Hardware breakpoints on MAC instructions may corrupt the destination register of the MAC instruction.

#### Fix/Workaround

Place breakpoints on earlier or later instructions.

#### When the main clock is RCSYS, TIMER\_CLOCK5 is equal to PBA clock

When the main clock is generated from RCSYS, TIMER\_CLOCK5 is equal to PBA Clock and not PBA Clock / 128.

#### Fix/Workaround None.

10.2.3 MPU

# Privilege violation when using interrupts in application mode with protected system stack

If the system stack is protected by the MPU and an interrupt occurs in application mode, an MPU DTLB exception will occur.

#### Fix/Workaround

Make a DTLB Protection (Write) exception handler which permits the interrupt request to be handled in privileged mode.

#### 10.2.4 USB

#### UPCFGn.INTFRQ is irrelevant for isochronous pipe

As a consequence, isochronous IN and OUT tokens are sent every 1ms (Full Speed), or every 125uS (High Speed).