## Eatice Semiconductor Corporation - ICE40UL1K-SWG16ITR1K Datasheet

Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                 |

|--------------------------------|---------------------------------------------------------------------------------|

| Product Status                 | Active                                                                          |

| Number of LABs/CLBs            | 156                                                                             |

| Number of Logic Elements/Cells | 1248                                                                            |

| Total RAM Bits                 | 57344                                                                           |

| Number of I/O                  | 10                                                                              |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                   |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                              |

| Package / Case                 | 16-XFBGA, WLCSP                                                                 |

| Supplier Device Package        | 16-WLCSP (1.4x1.48)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/ice40ul1k-swg16itr1k |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Lattice provides many pre-engineered IP (Intellectual Property) modules, including a number of reference designs, licensed free of charge, optimized for the iCE40 UltraLite FPGA family. Lattice also can provide fully verified bitstream for some of the widely used target functions in mobile device applications, such as IR remote, barcode emulator, and RGB LED control functions. Users can use these functions as offered by Lattice, or they can use the design to create their own unique required functions. For more information regarding Lattice's reference designs or fully-verified bitstreams, please contact your local Lattice representative.

## iCE40 UltraLite Family Data Sheet Architecture

July 2016 Data Sheet DS1050

### **Architecture Overview**

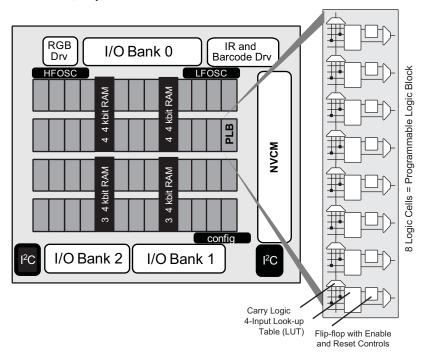

The iCE40 UltraLite family architecture contains an array of Programmable Logic Blocks (PLB), two Oscillator Generators, two user configurable I<sup>2</sup>C controllers, and blocks of sysMEM™ Embedded Block RAM (EBR) surrounded by Programmable I/O (PIO). Figure 2-1shows the block diagram of the iCE40UL-1K device.

Figure 2-1. iCE40UL-1K Device, Top View

The logic blocks, Programmable Logic Blocks (PLB) and sysMEM EBR blocks, are arranged in a two-dimensional grid with rows and columns. Each column has either PLB or EBR blocks. The PIO cells are located at the top and bottom of the device, arranged in banks. The PLB contains the building blocks for logic, arithmetic, and register functions. The PIOs utilize a flexible I/O buffer referred to as a sysIO buffer that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

In the iCE40 UltraLite family, there are three sysIO banks, one on top and two at the bottom. User can connect all  $V_{CCIO}$ s together, if all the I/Os are using the same voltage standard. Refer to the details in later sections of this document. The sysMEM EBRs are large 4 kbit, dedicated fast memory blocks. These blocks can be configured as RAM, ROM or FIFO with user logic using PLBs.

The iCE40 UltraLite also includes two user I<sup>2</sup>C ports, two Oscillators, and high current RGB and IR LED sinks, and a 100 mA Barcode emulation output.

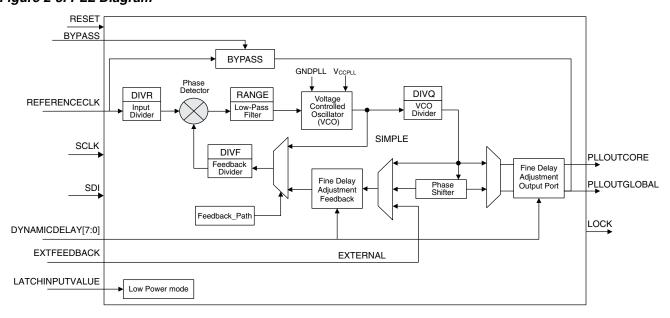

sysCLOCK Phase Locked Loops (PLLs) (sysCLOCK PLL is only supported in 36-ball ucBGA package)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The iCE40 UltraLite devices have one sysCLOCK PLL. REFERENCECLK is the reference frequency input to the PLL and its source can come from an external I/O pin, the internal Oscillator Generators from internal routing. EXTFEEDBACK is the feedback signal to the PLL which can come from internal routing or an external I/O pin. The feedback divider is used to multiply the reference frequency and thus synthesize a higher frequency clock output.

The PLLOUT output has an output divider, thus allowing the PLL to generate different frequencies for each output. The output divider can have a value from 1 to 64 (in increments of 2X). The PLLOUT outputs can all be used to drive the iCE40 UltraLite global clock network directly or general purpose routing resources can be used.

The LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected. A block diagram of the PLL is shown in Figure 2-3.

The timing of the device registers can be optimized by programming a phase shift into the PLLOUT output clock which will advance or delay the output clock with reference to the REFERENCECLK clock. This phase shift can be either programmed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after a phase adjustment on the output used as the feedback source and not relock until the tLOCK parameter has been satisfied.

There is an additional feature in the iCE40 UltraLite PLL. There are 2 FPGA controlled inputs, SCLK and SDI, that allows the user logic to serially shift in data thru SDI, clocked by SCLK clock. The data shifted in would change the configuration settings of the PLL. This feature allows the PLL to be time multiplexed for different functions, with different clock rates. After the data is shifted in, user would simply pulse the RESET input of the PLL block, and the PLL will re-lock with the new settings. For more details, please refer to TN1251, iCE40 sysCLOCK PLL Design and Usage Guide.

Figure 2-3. PLL Diagram

Table 2-3 provides signal descriptions of the PLL block.

## Table 2-3. PLL Signal Descriptions

| Signal Name       | Direction | Description                                                                                                                                                                                 |

|-------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCECLK      | Input     | Input reference clock                                                                                                                                                                       |

| BYPASS            | Input     | The BYPASS control selects which clock signal connects to the PLL-OUT output.  0 = PLL generated signal  1 = REFERENCECLK                                                                   |

| EXTFEEDBACK       | Input     | External feedback input to PLL. Enabled when the FEEDBACK_PATH attribute is set to EXTERNAL.                                                                                                |

| DYNAMICDELAY[7:0] | Input     | Fine delay adjustment control inputs. Enabled when DELAY_ADJUSTMENT_MODE is set to DYNAMIC.                                                                                                 |

| LATCHINPUTVALUE   | Input     | When enabled, puts the PLL into low-power mode; PLL output is held static at the last input clock value. Set ENABLE ICEGATE_PORTA and PORTB to '1' to enable.                               |

| PLLOUTGLOBAL      | Output    | Output from the Phase-Locked Loop (PLL). Drives a global clock network on the FPGA. The port has optimal connections to global clock buffers GBUF4 and GBUF5.                               |

| PLLOUTCORE        | Output    | Output clock generated by the PLL, drives regular FPGA routing. The frequency generated on this output is the same as the frequency of the clock signal generated on the PLLOUTLGOBAL port. |

| LOCK              | Output    | When High, indicates that the PLL output is phase aligned or locked to the input reference clock.                                                                                           |

| RESET             | Input     | Active low reset.                                                                                                                                                                           |

| SCLK              | Input     | Input, Serial Clock used for re-programming PLL settings.                                                                                                                                   |

| SDI               | Input     | Input, Serial Data used for re-programming PLL settings.                                                                                                                                    |

## sysMEM Embedded Block RAM Memory

Larger iCE40 UltraLite device includes multiple high-speed synchronous sysMEM Embedded Block RAMs (EBRs), each 4 kbit in size. This memory can be used for a wide variety of purposes including data buffering, and FIFO.

#### sysMEM Memory Block

The sysMEM block can implement single port, pseudo dual port, or FIFO memories with programmable logic resources. Each block can be used in a variety of depths and widths as shown in Table 2-4.

## Table 2-4. sysMEM Block Configurations<sup>1</sup>

| Block RAM<br>Configuration                                           | Block RAM<br>Configuration<br>and Size | WADDR Port<br>Size (Bits) | WDATA Port<br>Size (Bits) | RADDR Port<br>Size (Bits) | RDATA Port<br>Size (Bits) | MASK Port<br>Size (Bits) |

|----------------------------------------------------------------------|----------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------|

| SB_RAM256x16<br>SB_RAM256x16NR<br>SB_RAM256x16NW<br>SB_RAM256x16NRNW | 256x16 (4K)                            | 8 [7:0]                   | 16 [15:0]                 | 8 [7:0]                   | 16 [15:0]                 | 16 [15:0]                |

| SB_RAM512x8<br>SB_RAM512x8NR<br>SB_RAM512x8NW<br>SB_RAM512x8NRNW     | 512x8 (4K)                             | 9 [8:0]                   | 8 [7:0]                   | 9 [8:0]                   | 8 [7:0]                   | No Mask Port             |

| SB_RAM1024x4<br>SB_RAM1024x4NR<br>SB_RAM1024x4NW<br>SB_RAM1024x4NRNW | 1024x4 (4K)                            | 10 [9:0]                  | 4 [3:0]                   | 10 [9:0]                  | 4 [3:0]                   | No Mask Port             |

| SB_RAM2048x2<br>SB_RAM2048x2NR<br>SB_RAM2048x2NW<br>SB_RAM2048x2NRNW | 2048x2 (4K)                            | 11 [10:0]                 | 2 [1:0]                   | 11 [10:0]                 | 2 [1:0]                   | No Mask Port             |

<sup>1.</sup> For iCE40 Ultra, the primitive name without "Nxx" uses rising-edge Read and Write clocks. "NR" uses rising-edge Write clock and falling-edge Read clock. "NRW" uses falling-edge Urite clock and rising-edge Read clock. "NRNW" uses falling-edge clocks on both Read and Write.

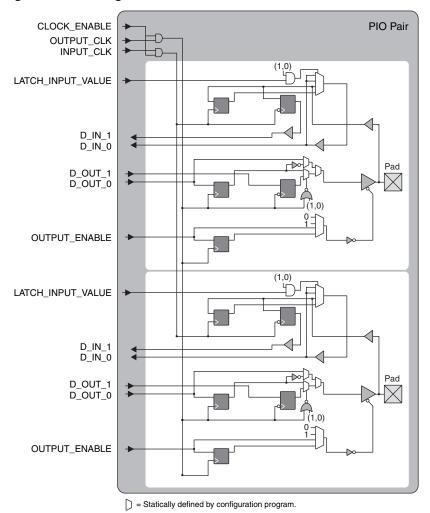

Figure 2-6. iCE I/O Register Block Diagram

Table 2-6. PIO Signal List

| Pin Name          | I/O Type | Description                   |

|-------------------|----------|-------------------------------|

| OUTPUT_CLK        | Input    | Output register clock         |

| CLOCK_ENABLE      | Input    | Clock enable                  |

| INPUT_CLK         | Input    | Input register clock          |

| OUTPUT_ENABLE     | Input    | Output enable                 |

| D_OUT_0/1         | Input    | Data from the core            |

| D_IN_0/1          | Output   | Data to the core              |

| LATCH_INPUT_VALUE | Input    | Latches/holds the Input Value |

## sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysIO buffers allow users to implement a wide variety of standards that are found in today's systems with LVCMOS interfaces.

#### Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$ ,  $SPI\_V_{CCIO}$ , and  $V_{PP\_2V5}$  reach the level defined in the Power-On-Reset Voltage table in the DC and Switching Characteristics chapter of this data sheet. After the POR signal is deactivated, the FPGA core logic becomes active. You must ensure that all  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. The default configuration of the I/O pins in a device prior to configuration is tri-stated with a weak pull-up to  $V_{CCIO}$ . The I/O pins maintain the pre-configuration state until  $V_{CC}$ ,  $SPI\_V_{CCIO}$ , and  $V_{PP\_2V5}$  reach the defined levels. The I/Os take on the software user-configured settings only after POR signal is deactivated and the device performs a proper download/configuration. Unused I/Os are automatically blocked and the pull-up termination is disabled.

#### **Supported Standards**

The iCE40 UltraLite sysIO buffer supports both single-ended input/output standards, and used as differential comparators. The buffer supports the LVCMOS 1.8, 2.5, and 3.3 V standards. The buffer has individually configurable options for bus maintenance (weak pull-up or none).

Table 2-7 and Table 2-8 show the I/O standards (together with their supply and reference voltages) supported by the iCE40 UltraLite devices.

#### **Programmable Pull Up Resistors**

The iCE40 UltraLite sysIO buffer can be configured with programmable pull up resistors on every I/O. The options are 3.3 kOhms, 6.8 kOhms, 10 kOhms or 100 kOhms (default). This feature is useful in supporting the I<sup>2</sup>C interface. The user can also use it for other purposes.

#### **Differential Comparators**

The iCE40 UltraLite devices provide differential comparator on pairs of I/O pins. These comparators are useful in some mobile applications. Please refer to the Pin Information Summary section to locate the corresponding paired I/Os with differential comparators.

Table 2-7. Supported Input Standards

| Input Standard          | V <sub>CCIO</sub> (Typical) |       |       |  |  |  |  |

|-------------------------|-----------------------------|-------|-------|--|--|--|--|

| input Standard          | 3.3 V                       | 2.5 V | 1.8 V |  |  |  |  |

| Single-Ended Interfaces |                             |       |       |  |  |  |  |

| LVCMOS33                | Yes                         |       |       |  |  |  |  |

| LVCMOS25                |                             | Yes   |       |  |  |  |  |

| LVCMOS18 <sup>1</sup>   |                             |       | Yes   |  |  |  |  |

<sup>1.</sup> Not supported in bank 0 for 16-WLCP package.

Table 2-8. Supported Output Standards

| Output Standard         | V <sub>CCIO</sub> (Typical) |

|-------------------------|-----------------------------|

| Single-Ended Interfaces |                             |

| LVCMOS33                | 3.3 V                       |

| LVCMOS25                | 2.5 V                       |

| LVCMOS18 <sup>1</sup>   | 1.8 V                       |

<sup>1.</sup> Not supported in bank 0 for 16-WLCP package.

### **On-Chip Oscillator**

The iCE40 UltraLite devices feature two different frequency Oscillator. One is tailored for low-power operation that runs at low frequency (LFOSC). Both Oscillators are controlled with internally generated current.

The LFOSC runs at nominal frequency of 10 kHz. The high frequency oscillator (HFOSC) runs at a nominal frequency of 48 MHz, divisible to 24 MHz, 12 MHz, or 6 MHz, by user option. The LFOSC can be used to perform all always-on functions, with the lowest power possible. The HFOSC can be enabled when the always-on functions detect a condition that would need to wake up the system to perform higher frequency functions.

#### User I<sup>2</sup>C IP

The iCE40 UltraLite devices have two I<sup>2</sup>C IP cores. Either of the two cores can be configured either as an I<sup>2</sup>C master or as an I<sup>2</sup>C slave. The pins for the I<sup>2</sup>C interface are not pre-assigned. User can use any General Purpose I/O pins.

In each of the two cores, there are options to delay the either the input or the output, or both, by 50 ns nominal, using dedicated on-chip delay elements. This provides an easier interface with any external I<sup>2</sup>C components.

In optional FIFO mode, FIFOs are used for storing multiple bytes of data for transmit and / or receive in order to efficiently support the I<sup>2</sup>C sensor applications

When the IP core is configured as master, it will be able to control other devices on the I<sup>2</sup>C bus through the preassigned pin interface. When the core is configured as the slave, the device will be able to provide I/O expansion to an I<sup>2</sup>C Master. The I<sup>2</sup>C cores support the following functionality:

- Master and Slave operation

- · 7-bit and 10-bit addressing

- Multi-master arbitration support

- Clock stretching

- Up to 1 MHz data transfer speed

- · General Call support

- · Optionally delaying input or output data, or both

- · Optional FIFO mode

- Transmit FIFO size is 10 bits x 16 bytes, receive FIFO size is 10 bits x 32 bytes

For further information on the User I<sup>2</sup>C, please refer to TN1274, iCE40 SPI/I2C Hardened IP Usage Guide.

### **High Current LED Drive I/O Pins**

The iCE40 UltraLite family devices offer multiple high current LED drive outputs in each device in the family to allow the iCE40 UltraLite product to drive LED signals directly on mobile applications.

There are three outputs on each device that can sink up to 24 mA current. These outputs are open-drain outputs, and provides sinking current to an LED connecting to the positive supply. These three outputs are designed to drive the RBG LEDs, such as the service LED found in a lot of mobile devices. An embedded RGB PWM IP is also offered in the family. This RGB drive current is user programmable from 4 mA to 24 mA, in increments of 4 mA in full current mode or from 2 mA to 12 mA, in increments of 2 mA in half current mode. This output functions as General Purpose I/O with open-drain when the high current drive is not needed.

There is one output on each device that can sink up to 100 mA current. This output is open-drain, and provides sinking current to drive an external Barcode LED connecting to the positive supply. This Barcode drive current is user programmable from 16.6 mA to 100 mA in increments of 16.6 mA in full current mode or 8.3 mA to 50 mA in

increments of 8.3 mA in half current mode. This output functions as General Purpose I/O with open drain when the high current drive is not needed.

There is one output on each device that can sink up to 400 mA current. This output is open-drain, and provides sinking current to drive an external IR LED connecting to the positive supply. This IR drive current is user programmable from 50 mA to 400 mA in increments of 50 mA in full current mode or from 25mA to 200mA in increments of 25mA in half current mode. This output functions as General Purpose I/O with open-drain when the high current drive is not needed. This output pin can also bond together with the Barcode output to drive higher current for IR LED.

The 400 mA IR LED drive output and the 100 mA Barcode LED drive output can be connected together to drive up to 500 mA IR LED, if higher than 400 mA driving capability is needed.

Table 2-9 shows the different LED driving current in the different selected Current Modes. IR500 LED applies with both IR LED and Barcode LED pins connected together.

Table 2-9. Current Drive

|             | Full Curr                                                | ent Mode                      | Half Curr                                           | ent Mode                                           |

|-------------|----------------------------------------------------------|-------------------------------|-----------------------------------------------------|----------------------------------------------------|

|             | mA (V <sub>CCIO</sub> = 3.3 V)                           | mA (V <sub>CCIO</sub> =2.5 V) | mA (V <sub>CCIO</sub> = 3.3 V)                      | mA (V <sub>CCIO</sub> =2.5 V)                      |

| RGB LED     | 0, 4, 8, 12, 16, 20, 24                                  | not allowed                   | 0, 2, 4, 6, 8, 10, 12                               | 0, 2, 4, 6, 8, 10, 12                              |

| BARCODE LED | 0, 16.6, 33.3, 50, 66.6,<br>83.3, 100                    | not allowed                   | 0, 8.3, 16.6, 25, 33.3,<br>41.6, 50                 | not allowed                                        |

| IR400 LED   | 0, 50, 100, 150, 200,<br>250, 300, 350, 400              | not allowed                   | 0, 25, 50, 75, 100, 125,<br>150, 175, 200           | 0, 25, 50, 75, 100, 125,<br>150, 175, 200          |

| IR500 LED   | 0, 50, 100, 150, 200,<br>250, 300, 350, 400, 450,<br>500 | not allowed                   | 0, 25, 50, 75, 100, 125,<br>150, 175, 200, 225, 250 | 0,25, 50, 75, 100, 125,<br>150, 175, 200, 225, 250 |

#### Hardened RGB PWM IP

To provide an easier usage of the RGB high current drivers to drive RGB LED, a Pulse-Width Modulator IP can be embedded into the user design. This PWM IP provides the flexibility for user to dynamically change the settings on the ON-time duration, OFF-time duration, and ability to turn the LED lights on and off gradually with user set breath-on and breath-off time.

For additional information on the PWM IP, please refer to TN1288, iCE40 LED Driver Usage Guide.

#### Hardened IR Transceiver IP

The IR Transceiver hard IP provides logic function to transmit and receive data through the Infrared LED data link. It takes the data residing inside the FPGA fabric to transmit with user specified frequency. In user enabled learning mode, it receives data from Infrared receiver and send the received data back to the FPGA fabric along with the measured receiving frequency.

For additional information on IR Transceiver IP, please see TN1288, iCE40 LED Driver Usage Guide.

#### **Non-Volatile Configuration Memory**

All iCE40 UltraLite devices provide a Non-Volatile Configuration Memory (NVCM) block which can be used to configure the device.

For more information on the NVCM, please refer to TN1248, iCE40 Programming and Configuration.

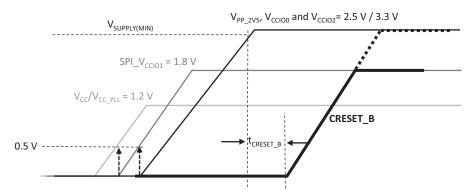

#### **Power On Reset**

iCE40 UltraLite devices have power-on reset circuitry to monitor  $V_{CC}$ ,  $SPI\_V_{CCIO1}$ , and  $V_{PP\_2V5}$  voltage levels during power-up and operation. At power-up, the POR circuitry monitors these voltage levels. It then triggers

download from either the internal NVCM or the external Flash memory after reaching the power-up levels specified in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. All power supplies should be powered up during configuration. Before and during configuration, the I/Os are held in tri-state. I/Os are released to user functionality once the device has finished configuration.

WLCSP package, VCCIO0 and VPP\_2V5 are connected to the same pin on the package, and should be powered as VPP 2V5 in the sequence.

There is no power down sequence required. However, when partial power supplies are powered down, it is required the above sequence to be followed when these supplies are repowered up again.

#### **External Reset**

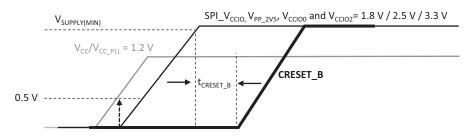

When all power supplies have reached to their minimum operating voltage defined in Minimum Operation Condition Table, it is required to either keep CRESET\_B LOW, or toggle CRESET\_B from HIGH to LOW, for a duration of  $t_{CRESET_B}$ , and release it to go HIGH, to start configuration download from either the internal NVCM or the external Flash memory.

Figure 3-1 shows Power-Up sequence when  $SPI_{CCIO1}$  and  $V_{PP_{2V5}}$  are connected separately, and the CRESET\_B signal triggers configuration download. Figure 3-2 shows when  $SPI_{CCIO1}$  and  $V_{PP_{2V5}}$  connected together. If the supply sequence is not followed, extra peak current may be observed on the supplies during power up.

All power supplies should be powered up during configuration. Before and during configuration, the I/Os are held in tri-state. I/Os are released to user functionality once the device has finished configuration.

Figure 3-1. Power Up Sequence with SPI\_V<sub>CCIO1</sub> and V<sub>PP 2V5</sub> Not Connected Together

Figure 3-2. Power Up Sequence with All Supplies Connected Together

## Supply Current 1, 2, 3, 4, 5

| Symbol                  | Parameter                                             | Typ. V <sub>CC</sub> = 1.2 V <sup>4</sup>                              | Units |

|-------------------------|-------------------------------------------------------|------------------------------------------------------------------------|-------|

| I <sub>CCSTDBY</sub>    | Core Power Supply Static Current                      | 35                                                                     | μΑ    |

| I <sub>PP2V5STDBY</sub> | V <sub>PP_2V5</sub> Power Supply Static Current       | 1                                                                      | μΑ    |

| I <sub>CCPLLSTDBY</sub> | PLL Power Supply Static Current                       | 1                                                                      | μΑ    |

| ICCIOSTDBY              | V <sub>CCIO</sub> Power Supply Static Current         | 1 at VCCIO equal or less<br>2.5 V; 5 at VCCIO equal<br>or less 3.465 V | μΑ    |

| I <sub>CCPEAK</sub>     | Core Power Supply Startup Peak Current                | 3.06                                                                   | mA    |

| I <sub>PP_2V5PEAK</sub> | V <sub>PP_2V5</sub> Power Supply Startup Peak Current | 2.15                                                                   | mA    |

| I <sub>CCPLLPEAK</sub>  | PLL Power Supply Startup Peak Current                 | 3.06 <sup>6</sup>                                                      | mA    |

| ICCIOPEAK               | V <sub>CCIO</sub> Power Supply Startup Peak Current   | 4.65 for config bank, 0.25<br>for regular IO bank                      | mA    |

Assumes programmed pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip PLL is off. For more detail with your specific design, use the Power Calculator tool. Power specified with master SPI configuration mode. Other modes may be up to 25% higher.

- 3. TJ = 25 °C, power supplies at nominal voltage.

- 4. Does not include pull-up.

- 5. Peak current is the in rush current highest current during power supply start up within the power supply ramp rate. See Power Supply Ramp Rates1, 2 section. These currents are measured with decoupling capacitance of 0.1 uF, 10 nF, and 1 nF to the power supply. Higher decoupling capacitance causes higher current.

- 6. PLL power supply shared with Core Power supply.

## **Internal Pull-Up Resistor Specifications**

| Parameter             | Condition             | Spec |     |      | Units |

|-----------------------|-----------------------|------|-----|------|-------|

|                       |                       | Min  | Тур | Max  |       |

| Resistor_3.3K         | 1.71 < Vccio < 3.47 V | 2.64 | 3.3 | 3.96 | kOhm  |

| Resistor_6.8K         | 1.71 < Vccio < 3.47 V | 5.44 | 6.8 | 8.16 | kOhm  |

| Resistor_10K          | 1.71 < Vccio < 3.47 V | 8    | 10  | 12   | kOhm  |

|                       | 1.71 < Vccio < 1.89 V | _    | 100 | _    | kOhm  |

| Weak pull-up resistor | 2.38 < Vccio < 2.63 V | _    | 55  | _    | kOhm  |

|                       | 3.13 < Vccio < 3.47 V | _    | 40  | _    | kOhm  |

## User I2C Specifications<sup>1</sup>

| SN | Symbol | Parameter           | STD Mode |     | FAST | Mode | FAS | T Mode I          | Plus  |

|----|--------|---------------------|----------|-----|------|------|-----|-------------------|-------|

|    |        |                     | Min      | Max | Min  | Max  | Min | Max               | Units |

| 1  | fSCL   | SCL clock frequency |          | 100 |      | 400  |     | 1000 <sup>2</sup> | kHz   |

<sup>1.</sup> Refer to the I2C specification for timing requirements.

<sup>2.</sup> Frequency = 0 MHz.

<sup>2.</sup> Fast Mode Plus maximum speed may be achieved by using external pull up resistor on I2C bus. Internal pull up may not be sufficient to support the maximum speed.

## High Current LED, IR LED and Barcode LED Drives<sup>1</sup>

| Symbol                 | Parameter                                                                                        | VC             | CIO = 3. | 3 V   | VC             | CIO = 2.5      | 5 V   |

|------------------------|--------------------------------------------------------------------------------------------------|----------------|----------|-------|----------------|----------------|-------|

|                        |                                                                                                  | Min.           | Max.     | Units | Min.           | Max.           | Units |

| IRGB_ACCURACY_FULL     | RGB LED0, LED1, LED2 Sink Current Accuracy to selected current @ V <sub>PAD</sub> = 0.5 ~ 2.5 V  | -12            | +12      | %     | not<br>allowed | not<br>allowed | %     |

| IRGB_ACCURACY_HALF     | RGB LED0, LED1, LED2 Sink Current Accuracy to selected current @ VPAD = 0.35 ~ 2.5 V             | -14            | +14      | %     | -14            | +14            | %     |

| I <sub>RGB_MATCH</sub> | RGB LED0, LED1, LED2 Sink Current Matching among the 3 outputs @ V <sub>PAD</sub> = 0.35 ~ 2.5 V | <del>-</del> 5 | +5       | %     | <b>-</b> 5     | +5             | %     |

| IIR_ACCURACY_FULL      | IR LED Sink Current Accuracy to selected current @ V <sub>PAD</sub> = 0.8 V ~ 2 V                | -12            | +12      | %     | not<br>allowed | not<br>allowed | %     |

| IR_ACCURACY_HALF       | IR LED Sink Current Accuracy to selected current @ V <sub>PAD</sub> = 0.55 V ~ 2 V               | -12            | +12      | %     | -12            | +12            | %     |

| BARCODE_ACCURACY_FULL  | BARCODE LED Sink Current<br>Accuracy to selected current @<br>V <sub>PAD</sub> =<br>0.8 V ~ 2 V  | -12            | +12      | %     | not<br>allowed | not<br>allowed | %     |

| BARCODE_ACCURACY_HALF  | BARCODE LED Sink Current<br>Accuracy to selected current @<br>V <sub>PAD</sub> =<br>0.55 V ~ 2 V | -12            | +12      | %     | not<br>allowed | not<br>allowed | %     |

<sup>1.</sup> Refer to Table 2-9 for valid current settings.

## **RGB LED Timing Specification**

| SN | Symbol                                          | Parameter                                                             | Min | TYP   | Max | Units |

|----|-------------------------------------------------|-----------------------------------------------------------------------|-----|-------|-----|-------|

| 1  | F <sub>PWM_OUT_X</sub><br>FR <sub>250</sub> = 0 | Frequency of the PWM output for color LED; When FR <sub>250</sub> = 0 |     | 125   |     | Hz    |

| 2  | F <sub>PWM_OUT_X</sub><br>FR <sub>250</sub> = 1 | Frequency of the PWM output for color LED; When FR <sub>250</sub> = 1 |     | 250   |     | Hz    |

| 3  | T <sub>HIGH_X</sub>                             | PWM High percentage for color LED.                                    | 0   |       | 99  | %     |

| 4  | T <sub>HIGH_STEP_X</sub>                        | PWM High percentage incremental step.                                 |     | 1/256 |     | %     |

## **IR Transceiver IP Timing Specification**

| SN | Symbol                          | Parameter                    | Min | TYP   | Max | Units |

|----|---------------------------------|------------------------------|-----|-------|-----|-------|

| 1  | F <sub>IR_OUT</sub>             | Frequency of the IR output   | 25  |       | 120 | kHz   |

| 2  | F <sub>IR_IN</sub>              | Frequency of the IR input    | 25  |       | 120 | kHz   |

| 3  | T <sub>HIGH</sub> (DUTY1/3 = 0) | Duty Cycle when DUTY1/3 = 0. |     | 50    |     | %     |

| 4  | T <sub>HIGH</sub> (DUTY1/3 = 1) | Duty Cycle when DUTY1/3 = 1. |     | 33.33 |     | %     |

## **Switching Test Conditions**

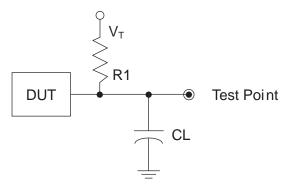

Figure 3-3 shows the output test load used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 3-1.

Figure 3-3. Output Test Load, LVCMOS Standards

Table 3-1. Test Fixture Required Components, Non-Terminated Interfaces

| Test Condition                   | R <sub>1</sub> | C <sub>L</sub> | Timing Reference                  | V <sub>T</sub>  |

|----------------------------------|----------------|----------------|-----------------------------------|-----------------|

|                                  | ∞              | 0 pF           | LVCMOS 3.3 = 1.5 V                | _               |

| LVCMOS settings (L -> H, H -> L) |                |                | LVCMOS 2.5 = V <sub>CCIO</sub> /2 | _               |

|                                  |                |                | LVCMOS 1.8 = V <sub>CCIO</sub> /2 | _               |

| LVCMOS 3.3 (Z -> H)              |                | 0 pF           | 1.5 V                             | V <sub>OL</sub> |

| LVCMOS 3.3 (Z -> L)              | 188            |                | 1.5 V                             | V <sub>OH</sub> |

| Other LVCMOS (Z -> H)            |                |                | V <sub>CCIO</sub> /2              | V <sub>OL</sub> |

| Other LVCMOS (Z -> L)            |                |                | V <sub>CCIO</sub> /2              | V <sub>OH</sub> |

| LVCMOS (H -> Z)                  |                |                | V <sub>OH</sub> - 0.15 V          | V <sub>OL</sub> |

| VCMOS (L -> Z)                   |                |                | V <sub>OL</sub> - 0.15 V          | V <sub>OH</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.

## iCE40 UltraLite Family Data Sheet Pinout Information

April 2016 Data Sheet DS1050

## **Signal Descriptions**

| Signal Name                                                        |                                                    | Function      | I/O                                                                                                                                                                                     | Description                                                                                                                                                                                                                       |  |  |

|--------------------------------------------------------------------|----------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Power Supplies                                                     | S                                                  | I             |                                                                                                                                                                                         | <u>'</u>                                                                                                                                                                                                                          |  |  |

| V <sub>CC</sub>                                                    |                                                    | Power         | _                                                                                                                                                                                       | Core Power Supply                                                                                                                                                                                                                 |  |  |

| V <sub>CCIO_0</sub> , SPI_V <sub>CCIO1</sub> , V <sub>CCIO_2</sub> |                                                    | Power         | _                                                                                                                                                                                       | Power for I/Os in Bank 0, 1, and 2. $V_{CCIO0}$ is tied with $V_{PP\_2V5}$ and $V_{CCIO2}$ is tied with $SPI\_V_{CCIO1}$ in 16 WLCS package.                                                                                      |  |  |

| V <sub>PP_2V5</sub>                                                |                                                    | Power         | _                                                                                                                                                                                       | Power for NVCM programming and operations                                                                                                                                                                                         |  |  |

| V <sub>CCPLL</sub>                                                 |                                                    | Power         | _                                                                                                                                                                                       | Power for PLL                                                                                                                                                                                                                     |  |  |

| GND                                                                |                                                    | GROUND        | _                                                                                                                                                                                       | Ground                                                                                                                                                                                                                            |  |  |

| GND_LED                                                            |                                                    | GROUND        | _                                                                                                                                                                                       | Ground for LED drivers. Should connect to GND on board                                                                                                                                                                            |  |  |

| Configuration                                                      |                                                    |               |                                                                                                                                                                                         |                                                                                                                                                                                                                                   |  |  |

| Primary                                                            | Secondary                                          |               |                                                                                                                                                                                         |                                                                                                                                                                                                                                   |  |  |

| CRESETB                                                            | internal pull-up resistor to V <sub>CCIO 2</sub> . |               | Configuration Reset, active LOW. Include a weak internal pull-up resistor to V <sub>CCIO_2</sub> . Or actively driven externally or connect an 10K-Ohm pull-up to V <sub>CCIO_2</sub> . |                                                                                                                                                                                                                                   |  |  |

| PIOB_8a                                                            | CDONE                                              | Configuration | I/O                                                                                                                                                                                     | Configuration Done. Includes a weak pull-up resistor to V <sub>CCIO_2</sub> . In 16 WLCS CDONE shared with PIOB_8a.                                                                                                               |  |  |

|                                                                    |                                                    | General I/O   | I/O                                                                                                                                                                                     | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                                    |  |  |

| PIOB_11b                                                           | CDONE                                              | Configuration | I/O                                                                                                                                                                                     | Configuration Done. Includes a weak pull-up resistor to V <sub>CCIO_2</sub> . In 36-ball ucBGA package CDONE shared with PIOB_11b.                                                                                                |  |  |

|                                                                    |                                                    | General I/O   | I/O                                                                                                                                                                                     | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                                    |  |  |

| Config SPI                                                         |                                                    | 1             |                                                                                                                                                                                         |                                                                                                                                                                                                                                   |  |  |

| Primary                                                            | Secondary                                          |               |                                                                                                                                                                                         |                                                                                                                                                                                                                                   |  |  |

| PIOB_16a                                                           | SPI_SCK                                            | Configuration | I/O                                                                                                                                                                                     | This pin is shared with device configuration. During configuration: In Master SPI mode, this pin outputs the clock to external SPI memory. In Slave SPI mode, this pin inputs the clock from external processor.                  |  |  |

|                                                                    |                                                    | General I/O   | I/O                                                                                                                                                                                     | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                                    |  |  |

| PIOB_14a                                                           | SPI_SO                                             | Configuration | Output                                                                                                                                                                                  | This pin is shared with device configuration. During configuration: In Master SPI mode, this pin outputs the command data to external SPI memory. In Slave SPI mode, this pin connects to the MISO pin of the external processor. |  |  |

|                                                                    |                                                    | General I/O   | I/O                                                                                                                                                                                     | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                                    |  |  |

## Pinout Information iCE40 UltraLite Family Data Sheet

| PIOB_15b       | SPI_SI    | Configuration | Input                | This pin is shared with device configuration. During configuration: In Master SPI mode, this pin receives data from external SPI memory. In Slave SPI mode, this pin connects to the MOSI pin of the external processor. |

|----------------|-----------|---------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |           | General I/O   | I/O                  | In user mode, after configuration, this pin can be programmed as general I/O in user function                                                                                                                            |

| PIOB_17b       | SPI_SS_B  | Configuration | I/O                  | This pin is shared with device configuration. During configuration: In Master SPI mode, this pin outputs to the external SPI memory. In Slave SPI mode, this pin inputs from the external processor.                     |

|                |           | General I/O   | I/O                  | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                           |

| Global Signals |           |               |                      |                                                                                                                                                                                                                          |

| Primary        | Secondary |               |                      |                                                                                                                                                                                                                          |

| PIOT_22b       | G0        | General I/O   | I/O                  | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                           |

|                |           | Global        | Input                | Global input used for high fanout, or clock/reset net.<br>The G0 pin drives the GBUF0 global buffer.                                                                                                                     |

| PIOT_21a       | G1        | General I/O   | I/O                  | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                           |

|                |           | Global        | Input                | Global input used for high fanout, or clock/reset net.<br>The G1 pin drives the GBUF1 global buffer.                                                                                                                     |

| PIOB_13b       | G3        | General I/O   | I/O                  | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                           |

|                |           | Global        | Input                | Global input used for high fanout, or clock/reset net.<br>The G3 pin drives the GBUF3 global buffer.                                                                                                                     |

| PIOB_8a        | G4        | General I/O   | I/O                  | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                           |

|                |           | Global        | Input                | Global input used for high fanout, or clock/reset net. The G4 pin drives the GBUF4 global buffer.                                                                                                                        |

| PIOB_7b        | G5        | General I/O   | I/O                  | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                           |

|                |           | Global        | Input                | Global input used for high fanout, or clock/reset net. The G5 pin drives the GBUF5 global buffer.                                                                                                                        |

| PIOB_3b        | G6        | General I/O   | I/O                  | In user mode, after configuration, this pin can be programmed as general I/O in user function.                                                                                                                           |

|                |           | Global        | Input                | Global input used for high fanout, or clock/reset net.<br>The G6 pin drives the GBUF6 global buffer.                                                                                                                     |

| LED Signals    |           |               |                      |                                                                                                                                                                                                                          |

| RGB0           |           | General I/O   | Open-Drain I/O       | In user mode, with user's choice, this pin can be programmed as open drain I/O in user function.                                                                                                                         |

|                |           | LED           | Open-Drain<br>Output | In user mode, with user's choice, this pin can be programmed as open drain 24mA output to drive external LED.                                                                                                            |

| RGB1           |           | General I/O   | Open-Drain I/O       | In user mode, with user's choice, this pin can be programmed as open drain I/O in user function.                                                                                                                         |

|                |           | LED           | Open-Drain<br>Output | In user mode, with user's choice, this pin can be programmed as open drain 24mA output to drive external LED.                                                                                                            |

## Pinout Information iCE40 UltraLite Family Data Sheet

| <b>-</b> | T           | T.                   |                                                                                                                             |

|----------|-------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| RGB2     | General I/O | Open-Drain I/O       | In user mode, with user's choice, this pin can be programmed as open drain I/O in user function.                            |

|          | LED         | Open-Drain<br>Output | In user mode, with user's choice, this pin can be programmed as open drain 24mA output to drive external LED.               |

| IRLED    | General I/O | Open-Drain I/O       | In user mode, with user's choice, this pin can be programmed as open drain I/O in user function.                            |

|          | LED         | Open-Drain<br>Output | In user mode, with user's choice, this pin can be programmed as open drain 400 mA output to drive external LED.             |

| BARCODE  | General I/O | Open-Drain I/O       | In user mode, with user's choice, this pin can be programmed as open drain I/O in user function.                            |

|          | LED         | Open-Drain<br>Output | In user mode, with user's choice, this pin can be programmed as open drain 100 mA output to drive external LED.             |

| PIOT_xx  | General I/O | I/O                  | In user mode, with user's choice, this pin can be programmed as I/O in user function in the top ( $xx = I/O$ location).     |

| PIOB_xx  | General I/O | I/O                  | In user mode, with user's choice, this pin can be programmed as $I/O$ in user function in the bottom (xx = $I/O$ location). |

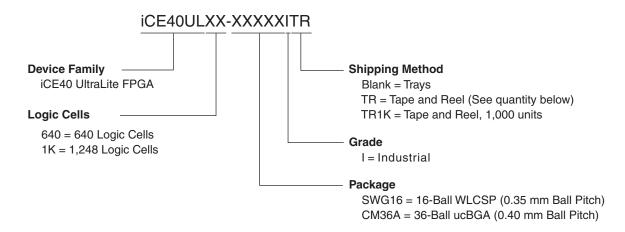

## iCE40 UltraLite Family Data Sheet Ordering Information

April 2016 Data Sheet DS1050

## iCE40 UltraLite Part Number Description

## **Tape and Reel Quantity**

| Package | TR Quantity |

|---------|-------------|

| CM36A   | 4,000       |

| SWG16   | 5,000       |

## **Ordering Part Numbers**

#### Industrial

| Part Number           | LUTs | Supply Voltage | Package            | Pins | Temp. |

|-----------------------|------|----------------|--------------------|------|-------|

| ICE40UL1K-SWG16ITR    | 1248 | 1.2            | Halogen-Free WLCSP | 16   | IND   |

| ICE40UL1K-CM36AITR    | 1248 | 1.2            | 36-Ball ucBGA      | 36   | IND   |

| ICE40UL1K-CM36AITR1K  | 1248 | 1.2            | 36-Ball ucBGA      | 36   | IND   |

| ICE40UL640-SWG16ITR   | 640  | 1.2            | Halogen-Free WLCSP | 16   | IND   |

| ICE40UL640-CM36AITR   | 640  | 1.2            | 36-Ball ucBGA      | 36   | IND   |

| ICE40UL640-CM36AITR1K | 640  | 1.2            | 36-Ball ucBGA      | 36   | IND   |

# iCE40 UltraLite Family Data Sheet Supplemental Information

July 2016 Data Sheet DS1050

#### For Further Information

A variety of technical notes for the iCE40 UltraLite family are available on the Lattice web site.

- TN1248, iCE40 Programming and Configuration

- TN1274, iCE40 I2C and SPI Hardened IP Usage Guide

- TN1276, Advanced iCE40 I2C and SPI Hardened IP Usage Guide

- TN1250, Memory Usage Guide for iCE40 Devices

- TN1251, iCE40 sysCLOCK PLL Design and Usage Guide

- TN1252, iCE40 Hardware Checklist

- TN1288, iCE40 LED Driver Usage Guide

- iCE40 UltraLite Pinout Files

- iCE40 UltraLite Pin Migration Files

- Thermal Management document

- Lattice design tools

- Schematic Symbols

# iCE40 UltraLite Family Data Sheet Revision History

November 2016 Data Sheet DS1050

| Date          | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|---------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2016 | 1.4     | DC and Switching<br>Characteristics | Updated External Reset section. Added information on following supply sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| June 2016     | 1.3     | Introduction                        | Updated General Description section.  — Changed "embedded RGB PWM IP" to "hardened RGB PWM IP".  — Changed "modulation logic" to "hardened TX/RX pulse logic".  — Updated information on the use of 500 mA IR driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|               |         |                                     | Updated Introduction section.  — Added "RGB LED and IR LED" to configurable Controllers.  — Added "LED" to RGB control functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |         | Architecture                        | Updated Architecture Overview section.  — Changed caption to Figure 2-1, iCE40UL1K iCE40UL-1K Device, Top View.  — Changed logic blocks to PLB.  — Changed "LED sink" to "RGB and IR LED sinks, and a 100 mA Barcode emulation output".  — Corrected headings in Table 2-2, Global Buffer (GBUF) Connections to Programmable Logic Blocks.  — Updated footnote in Table 2-4, sysMEM Block Configuration.  — Updated sysIO Buffer Banks section.  — Corrected V <sub>CCIO</sub> format in Figure 2-5, I/O Bank and Programmable I/O Cell.  — Updated Typical I/O Behavior During Power-up section.  — Updated Supported Standards section.  — Updated Programmable Pull Up Resistors section.  — Changed "more than one byte" to "multiple bytes" in User I <sup>2</sup> C IP section.  — Updated High Current LED Drive I/O Pins section.  Changed heading to High Current LED Drive I/O Pins. Added LED to "high current drive". Added information on use of 500 mA IR LED.  Added paragraph to reference Table 2-9.  — Changed heading to Hardened RGB PWM IP.  — Changed heading to Hardened IR Transceiver IP. |

|               |         |                                     | Updated iCE40 UltraLite Programming and Configuration section. Changed VCCIO_1 to SPI_V <sub>CCIO1</sub> in Device Programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               |         | DC and Switching<br>Characteristics | Updated Absolute Maximum Ratings section. Corrected $V_{\mbox{\footnotesize{PP\_2V5}}}$ and $V_{\mbox{\footnotesize{CCPLL}}}$ format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|               |         |                                     | Updated Recommended Operating Conditions section.  — Changed heading to Hardened RGB PWM IP.  — Updated footnote.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |         |                                     | Removed Power-up Sequence section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |         |                                     | Added the following sections:  — Power-On Reset — Power-Up Supply Sequencing — External Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|               |         |                                     | Updated DC Electrical Characteristics section. Revised footnote 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |         |                                     | Updated Supply Current section.  — Changed V <sub>PP_2V5</sub> format.  — Updated footnote 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|               |         |                                     | Updated Internal Oscillators (HFOSC, LFOSC) section. Added Commercial and Industrial Temp values for f <sub>CLKHF</sub> and DCH <sub>CLKHF</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               |         |                                     | Updated Differential Comparator Electrical Characteristics section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.