Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 54                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1946-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address                             | Name   | Bit 7        | Bit 6                                                    | Bit 5          | Bit 4        | Bit 3        | Bit 2       | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other |

|-------------------------------------|--------|--------------|----------------------------------------------------------|----------------|--------------|--------------|-------------|-----------|-----------|----------------------|-----------------------|

| Banks 1                             | 0-14   |              |                                                          |                |              |              |             |           |           |                      | Resets                |

| x00h/<br>x80h <sup>(2)</sup>        | INDF0  |              |                                                          |                |              |              |             |           | xxxx xxxx | xxxx xxxx            |                       |

| x00h/<br>x81h <b><sup>(2)</sup></b> | INDF1  |              | this location ical register)                             | uses contents  | s of FSR1H/F | SR1L to addr | ess data me | mory      |           | XXXX XXXX            | XXXX XXXX             |

| x02h/<br>x82h <sup>(2)</sup>        | PCL    | Program C    | ounter (PC) L                                            | east Significa | nt Byte      |              |             |           |           | 0000 0000            | 0000 0000             |

| x03h/<br>x83h <sup>(2)</sup>        | STATUS | -            | —                                                        | —              | TO           | PD           | Z           | DC        | С         | 1 1000               | q quuu                |

| x04h/<br>x84h <b><sup>(2)</sup></b> | FSR0L  | Indirect Dat | Indirect Data Memory Address 0 Low Pointer               |                |              |              |             |           | 0000 0000 | uuuu uuuu            |                       |

| x05h/<br>x85h <sup>(2)</sup>        | FSR0H  | Indirect Dat | Indirect Data Memory Address 0 High Pointer              |                |              |              |             |           | 0000 0000 | 0000 0000            |                       |

| x06h/<br>x86h <sup>(2)</sup>        | FSR1L  | Indirect Dat | Indirect Data Memory Address 1 Low Pointer               |                |              |              |             |           | 0000 0000 | uuuu uuuu            |                       |

| x07h/<br>x87h <sup>(2)</sup>        | FSR1H  | Indirect Dat | Indirect Data Memory Address 1 High Pointer              |                |              |              |             |           | 0000 0000 | 0000 0000            |                       |

| x08h/<br>x88h <sup>(2)</sup>        | BSR    | —            | — — BSR<4:0>                                             |                |              |              |             | 0 0000    | 0 0000    |                      |                       |

| x09h/<br>x89h <sup>(2)</sup>        | WREG   | Working Re   | Working Register                                         |                |              |              |             | 0000 0000 | uuuu uuuu |                      |                       |

| x0Ah/<br>x8Ah <b>(1),(2)</b>        | PCLATH | -            | Write Buffer for the upper 7 bits of the Program Counter |                |              |              |             | -000 0000 | -000 0000 |                      |                       |

| x0Bh/<br>x8Bh <b><sup>(2)</sup></b> | INTCON | GIE          | PEIE                                                     | TMR0IE         | INTE         | IOCIE        | TMR0IF      | INTF      | IOCIF     | 0000 000x            | 0000 000u             |

| x0Ch/<br>x8Ch                       | _      | Unimpleme    | nted                                                     |                |              |              |             |           |           | -                    | _                     |

| <br>x1Fh/<br>x9Fh                   |        |              |                                                          |                |              |              |             |           |           |                      |                       |

#### TABLE 3-10. SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are 1: transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: Unimplemented, read as '1'.

#### 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT, or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

#### TABLE 5-1: OSCILLATOR SWITCHING DELAYS

#### Switch To Switch From Frequency **Oscillator Delay** LFINTOSC<sup>(1)</sup> 31 kHz MFINTOSC<sup>(1)</sup> Sleep 31.25 kHz-500 kHz 2 cycles HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz EC, RC<sup>(1)</sup> Sleep/POR DC - 32 MHz 2 cycles EC. RC<sup>(1)</sup> **LFINTOSC** DC - 32 MHz 1 cycle of each Timer1 Oscillator Sleep/POR 32 kHz-20 MHz 1024 Clock Cycles (OST) LP, XT, HS<sup>(1)</sup> MFINTOSC<sup>(1)</sup> 31.25 kHz-500 kHz Any clock source 2 µs (approx.) HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz LFINTOSC<sup>(1)</sup> 31 kHz Any clock source 1 cvcle of each Timer1 Oscillator 32 kHz Any clock source 1024 Clock Cycles (OST) PLL inactive 16-32 MHz PLL active 2 ms (approx.)

**Note 1:** PLL inactive.

### 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

#### 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2, PIE3 and PIE4 registers)

The INTCON, PIR1, PIR2, PIR3 and PIR4 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

#### 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is 3 or 4 instruction cycles. For asynchronous interrupts, the latency is 3 to 5 instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

#### 12.7 PORTC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 12-11). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 12-10) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The TRISC register (Register 12-11) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 12.7.1 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-7.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority. Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the priority list.

| Pin Name | Function Priority <sup>(1)</sup>                                                           |

|----------|--------------------------------------------------------------------------------------------|

| RC0      | T1OSO (Timer1 Oscillator)<br>SEG40 (ICD)<br>RC0                                            |

| RC1      | T1OSI (Timer1 Oscillator)<br>CCP2 <sup>(2)</sup> /P2A <sup>(2)</sup><br>SEG32 (ICD)<br>RC1 |

| RC2      | SEG13 (LCD)<br>CCP1/P1A<br>RC2                                                             |

| RC3      | SEG17 (LCD)<br>SCL1 (MSSP1)<br>SCK1 (MSSP1)<br>RC3                                         |

| RC4      | SEG16 (LCD)<br>SDA1 (MSSP1)<br>RC4                                                         |

| RC5      | SEG12 (LCD)<br>SDO1 (MSSP1)<br>RC5                                                         |

| RC6      | SEG27 (LCD)<br>TX1 (EUSART1)<br>CK1 (EUSART1)<br>RC6                                       |

| RC7      | SEG28 (LCD)<br>DT1 (EUSART1)<br>RC7                                                        |

TABLE 12-7: PORTC OUTPUT PRIORITY

141

Note 1: Priority listed from highest to lowest.

**2:** Default pin (see APFCON register).

### 16.4 Register Definitions: ADC Control

| U-0                           | R/W-0/0                  | R/W-0/0                            | R/W-0/0        | R/W-0/0                      | R/W-0/0         | R/W-0/0           | R/W-0/0      |

|-------------------------------|--------------------------|------------------------------------|----------------|------------------------------|-----------------|-------------------|--------------|

| _                             |                          |                                    | CHS<4:0>       |                              |                 | GO/DONE           | ADON         |

| pit 7                         |                          |                                    |                |                              |                 |                   | bit          |

|                               |                          |                                    |                |                              |                 |                   |              |

| L <b>egend:</b><br>R = Readat | le hit                   | W = Writable                       | hit            | II – Unimpler                | nented bit, rea | ud as 'O'         |              |

| u = Bit is un                 |                          | x = Bit is unkl                    |                |                              |                 | OR/Value at all o | other Decete |

| "1' = Bit is s                | 0                        | '0' = Bit is cle                   |                |                              |                 |                   |              |

| 1 – Dit is s                  | ει                       |                                    | areu           |                              |                 |                   |              |

| bit 7                         | Unimpleme                | nted: Read as                      | 0'             |                              |                 |                   |              |

| oit 6-2                       | CHS<4:0>:                | Analog Channe                      | I Select bits  |                              |                 |                   |              |

|                               |                          | R (Fixed Voltage                   | e Reference) E | Buffer 1 Output <sup>(</sup> | 2)              |                   |              |

|                               | 11110 <b>= DA</b>        |                                    | (3)            |                              |                 |                   |              |

|                               |                          | nperature Indica<br>served. No cha |                | ч                            |                 |                   |              |

|                               | •                        |                                    |                | u.                           |                 |                   |              |

|                               | •                        |                                    |                |                              |                 |                   |              |

|                               | •                        |                                    |                |                              |                 |                   |              |

|                               |                          | served. No chai                    | nnel connected | d.                           |                 |                   |              |

|                               | 10000 = AN<br>01111 = AN |                                    |                |                              |                 |                   |              |

|                               | 01110 <b>= AN</b>        |                                    |                |                              |                 |                   |              |

|                               | 01101 = AN               |                                    |                |                              |                 |                   |              |

|                               | 01100 <b>= AN</b>        |                                    |                |                              |                 |                   |              |

|                               | 01011 = AN               |                                    |                |                              |                 |                   |              |

|                               | 01010 = AN<br>01001 = AN |                                    |                |                              |                 |                   |              |

|                               | 01000 = AN               |                                    |                |                              |                 |                   |              |

|                               | 00111 <b>= AN</b>        |                                    |                |                              |                 |                   |              |

|                               | 00110 <b>= AN</b>        | 6                                  |                |                              |                 |                   |              |

|                               | 00101 <b>= AN</b>        |                                    |                |                              |                 |                   |              |

|                               | 00100 = AN               |                                    |                |                              |                 |                   |              |

|                               | 00011 = AN<br>00010 = AN |                                    |                |                              |                 |                   |              |

|                               | 00001 = AN               |                                    |                |                              |                 |                   |              |

|                               | 00000 <b>=AN</b>         | )                                  |                |                              |                 |                   |              |

| bit 1                         | GO/DONE:                 | A/D Conversion                     | Status bit     |                              |                 |                   |              |

|                               |                          | version cycle in                   |                |                              |                 |                   | od           |

|                               |                          | version complet                    |                |                              |                 | ion has complet   |              |

| bit 0                         | ADON: ADC                | Enable bit                         |                |                              |                 |                   |              |

|                               | 1 = ADC is e             |                                    |                |                              |                 |                   |              |

|                               | 0 = ADC is c             | lisabled and co                    | nsumes no op   | erating current              |                 |                   |              |

| Note 1: S                     | See Section 17.0         | ) "Digital-to-Ar                   | nalog Conver   | ter (DAC) Mod                | ule" for more   | information.      |              |

| 2: 8                          | See Section 14.0         | ) "Fixed Voltag                    | e Reference    | (FVR)" for more              | e information.  |                   |              |

|                               |                          |                                    |                |                              |                 |                   |              |

#### REGISTER 16-1: ADCON0: A/D CONTROL REGISTER 0

#### 18.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 registers (see Register 18-1) contain Control and Status bits for the following:

- Enable

- · Output selection

- Output polarity

- · Speed/Power selection

- · Hysteresis enable

- · Output synchronization

The CMxCON1 registers (see Register 18-2) contain Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- · CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

| Note 1: | The CxOE bit of the CMxCON0 register   |

|---------|----------------------------------------|

|         | overrides the PORT data latch. Setting |

|         | the CxON bit of the CMxCON0 register   |

|         | has no impact on the port override.    |

The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 18.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a noninverted output.

Table 18-2 shows the output state versus input conditions, including polarity control.

# TABLE 18-2:COMPARATOR OUTPUT<br/>STATE VS. INPUT<br/>CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### 18.2.4 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the normal speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

#### 23.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

#### 23.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name    | Bit 7       | Bit 6                                                                      | Bit 5         | Bit 4        | Bit 3             | Bit 2    | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------|----------------------------------------------------------------------------|---------------|--------------|-------------------|----------|--------|--------|---------------------|

| APFCON  | P3CSEL      | P3BSEL                                                                     | P2DSEL        | P2CSEL       | P2BSEL            | CCP2SEL  | P1CSEL | P1BSEL | 123                 |

| CCPxCON | PxM<        | 1:0> <sup>(1)</sup>                                                        | DCxB          | <1:0>        |                   | CCPxM<   | :3:0>  |        | 227                 |

| CCPRxL  | Capture/Co  | mpare/PWM                                                                  | Register x L  | ow Byte (LSI | 3)                |          |        |        | 205*                |

| CCPRxH  | Capture/Co  | mpare/PWM                                                                  | Register x H  | igh Byte (MS | SB)               |          |        |        | 205*                |

| INTCON  | GIE         | PEIE                                                                       | TMR0IE        | INTE         | IOCIE             | TMR0IF   | INTF   | IOCIF  | 90                  |

| PIE1    | TMR1GIE     | ADIE                                                                       | RCIE          | TXIE         | SSPIE             | CCP1IE   | TMR2IE | TMR1IE | 91                  |

| PIE2    | OSFIE       | C2IE                                                                       | C1IE          | EEIE         | BCLIE             | LCDIE    | C3IE   | CCP2IE | 92                  |

| PIE3    | —           | CCP5IE                                                                     | CCP4IE        | CCP3IE       | TMR6IE            | _        | TMR4IE | —      | 93                  |

| PIR1    | TMR1GIF     | ADIF                                                                       | RCIF          | TXIF         | SSPIF             | CCP1IF   | TMR2IF | TMR1IF | 95                  |

| PIR2    | OSFIF       | C2IF                                                                       | C1IF          | EEIF         | BCLIF             | LCDIF    | C3IF   | CCP2IF | 96                  |

| PIR3    | —           | CCP5IF                                                                     | CCP4IF        | CCP3IF       | TMR6IF            | —        | TMR4IF | —      | 97                  |

| T1CON   | TMR1C       | S<1:0>                                                                     | T1CKP         | S<1:0>       | T1OSCEN           | T1SYNC   | —      | TMR10N | 197                 |

| T1GCON  | TMR1GE      | T1GPOL                                                                     | T1GTM         | T1GSPM       | T1GGO/DONE        | T1GVAL   | T1GSS  | S<1:0> | 198                 |

| TMR1L   | Holding Reg | gister for the                                                             | Least Signifi | cant Byte of | the 16-bit TMR1 I | Register |        |        | 193*                |

| TMR1H   | Holding Reg | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |               |              |                   |          | 193*   |        |                     |

| TRISB   | TRISB7      | TRISB6                                                                     | TRISB5        | TRISB4       | TRISB3            | TRISB2   | TRISB1 | TRISB0 | 128                 |

| TRISC   | TRISC7      | TRISC6                                                                     | TRISC5        | TRISC4       | TRISC3            | TRISC2   | TRISC1 | TRISC0 | 131                 |

| TRISE   | TRISE7      | TRISE6                                                                     | TRISE5        | TRISE4       | TRISE3            | TRISE2   | TRISE1 | TRISE0 | 137                 |

| TRISG   | TRISG7      | TRISG6                                                                     | TRISG5        | TRISG4       | TRISG3            | TRISG2   | TRISG1 | TRISG0 | 143                 |

#### TABLE 23-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Capture mode.

**Note 1:** Applies to ECCP modules only.

\* Page provides register information.

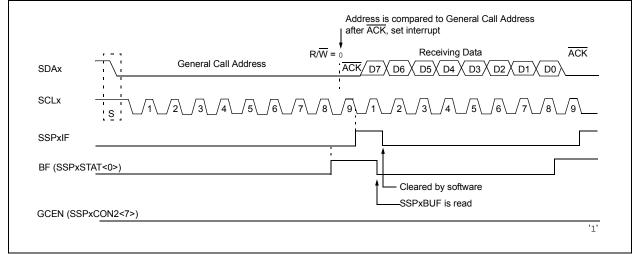

#### 24.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address, regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 24-23 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCLx. The slave must then set its ACKDT value and release the clock with communication, progressing as it would normally.

#### 24.5.9 SSPx MASK REGISTER

An SSPx Mask (SSPxMSK) register (Register 24-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSPx operation until written with a mask value.

The SSPx Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0>, only. The SSPx mask has no effect during the reception of the first (high) byte of the address.

#### 24.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN bit of the SSPxCON2 register.

| Note: | The MSSPx module must be in an Idle     |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The Baud Rate Generator begins counting and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSPx is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

#### 24.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 24.6.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

#### 24.6.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 24.6.7.4 Typical Receive Sequence

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDAx pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- User sets the RCEN bit of the SSPxCON2 register and the Master clocks in a byte from the slave.

- 9. After the eighth falling edge of SCLx, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPxUF, clears BF.

- 11. Master sets ACK value sent to slave in ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Masters ACK is clocked out to the Slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

#### 26.2.2 CURRENT RANGES

The capacitive sensing oscillator can operate in one of seven different power modes. The power modes are separated into two ranges: the low range and the high range.

When the oscillator's low range is selected, the fixed internal voltage references of the capacitive sensing oscillator are being used. When the oscillator's high range is selected, the variable voltage references supplied by the FVR and DAC modules are being used. Selection between the voltage references is controlled by the CPSRM bit of the CPSCON0 register. See **Section 26.2.1 "Voltage Reference Modes"** for more information.

Within each range there are three distinct power modes: low, medium and high. Current consumption is dependent upon the range and mode selected. Selecting Power modes within each range is accomplished by configuring the CPSRNG <1:0> bits in the CPSCON0 register. See Table for proper power mode selection. The remaining mode is a Noise Detection mode that resides within the high range. The Noise Detection mode is unique in that it disables the sinking and sourcing of current on the analog pin but leaves the rest of the oscillator circuitry active. This reduces the oscillation frequency on the analog pin to zero and also greatly reduces the current consumed by the oscillator module.

When noise is introduced onto the pin, the oscillator is driven at the frequency determined by the noise. This produces a detectable signal at the comparator output, indicating the presence of activity on the pin.

Figure 26-2 shows a more detailed drawing of the current sources and comparators associated with the oscillator.

| CPSRM | Range | CPSRNG<1:0> | Current Range <sup>(1)</sup> |

|-------|-------|-------------|------------------------------|

|       |       | 00          | Noise Detection              |

| 1     |       | 01          | Low                          |

| T     | High  | 10          | Medium                       |

|       |       | 11          | High                         |

|       |       | 00          | Off                          |

| 0     | Law   | 01          | Low                          |

| 0     | Low   | 10          | Medium                       |

|       |       | 11          | High                         |

Note 1: See Power-Down Currents (IPD) in Section 30.0 "Electrical Specifications" for more information.

#### 26.2.3 TIMER RESOURCES

To measure the change in frequency of the capacitive sensing oscillator, a fixed time base is required. For the period of the fixed time base, the capacitive sensing oscillator is used to clock either Timer0 or Timer1. The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed time base.

#### 26.2.4 FIXED TIME BASE

To measure the frequency of the capacitive sensing oscillator, a fixed time base is required. Any timer resource or software loop can be used to establish the fixed time base. It is up to the end user to determine the method in which the fixed time base is generated.

| Note: | The fixed time base can not be generated  |

|-------|-------------------------------------------|

|       | by the timer resource that the capacitive |

|       | sensing oscillator is clocking.           |

#### 26.2.4.1 Timer0

To select Timer0 as the timer resource for the CPS module:

- Set the T0XCS bit of the CPSCON0 register.

- Clear the TMR0CS bit of the OPTION\_REG register.

When Timer0 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer0. Refer to **Section 20.0** "**Timer0 Module**" for additional information.

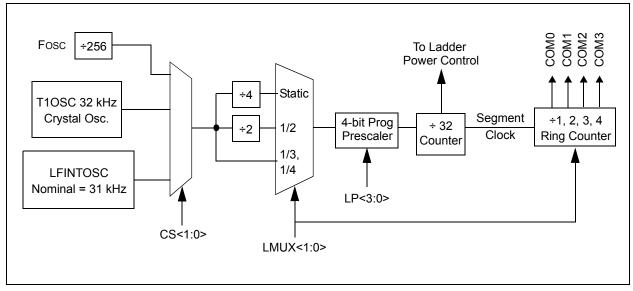

#### 27.3 LCD Clock Source Selection

The LCD module has three possible clock sources:

- Fosc/256

- T10SC

- LFINTOSC

The first clock source is the system clock divided by 256 (Fosc/256). This divider ratio is chosen to provide about 1 kHz output when the system clock is 8 MHz. The divider is not programmable. Instead, the LCD prescaler bits LP<3:0> of the LCDPS register are used to set the LCD frame clock rate.

The second clock source is the T1OSC. This also gives about 1 kHz when a 32.768 kHz crystal is used with the Timer1 oscillator. To use the Timer1 oscillator as a clock source, the T1OSCEN bit of the T1CON register should be set.

The third clock source is the 31 kHz LFINTOSC, which provides approximately 1 kHz output.

The second and third clock sources may be used to continue running the LCD while the processor is in Sleep.

Using bits CS<1:0> of the LCDCON register can select any of these clock sources.

#### 27.3.1 LCD PRESCALER

A 4-bit counter is available as a prescaler for the LCD clock. The prescaler is not directly readable or writable; its value is set by the LP<3:0> bits of the LCDPS register, which determine the prescaler assignment and prescale ratio.

The prescale values are selectable from 1:1 through 1:16.

#### FIGURE 27-2: LCD CLOCK GENERATION

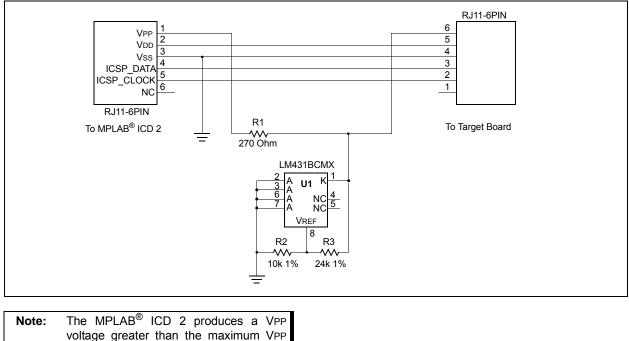

#### 28.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP™ refer to the *PIC16F193X/LF193X/PIC16F194X/LF194X/PIC16LF 190X Memory Programming Specification* (DS41397).

#### 28.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

Some programmers produce VPP greater than VIHH (9.0V), an external circuit is required to limit the VPP voltage. See Figure 28-1 for example circuit.

FIGURE 28-1: VPP LIMITER EXAMPLE CIRCUIT

specification of the PIC16(L)F1946/47.

© 2010-2016 Microchip Technology Inc.

### FIGURE 29-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                |               |

|---------------------------------------------------------------------------------------|---------------|

| OPCODE d                                                                              | f (FILE #)    |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |               |

| Bit-oriented file register operations13109760                                         |               |

| OPCODE b (BIT                                                                         |               |

| b = 3-bit bit address<br>f = 7-bit file register address                              |               |

| Literal and control operations                                                        |               |

| General                                                                               |               |

| 13 8                                                                                  | 7 0           |

| OPCODE                                                                                | k (literal)   |

| k = 8-bit immediate value                                                             |               |

| CALL and GOTO instructions of                                                         | only          |

| 13 11 10                                                                              | 0             |

| OPCODE                                                                                | k (literal)   |

| k = 11-bit immediate val                                                              | ue            |

| MOVLP instruction only                                                                |               |

| 13 7                                                                                  |               |

| OPCODE                                                                                | k (literal)   |

| k = 7-bit immediate valu                                                              |               |

| 13                                                                                    | 5 4 0         |

| OPCODE                                                                                | k (literal)   |

| k = 5-bit immediate value<br>BRA instruction only                                     |               |

| 13 9 8                                                                                | 0             |

| OPCODE                                                                                | k (literal)   |

| k = 9-bit immediate value                                                             |               |

| FSR Offset instructions                                                               |               |

| 13 7                                                                                  | 6 5 0         |

| OPCODE                                                                                | n k (literal) |

| n = appropriate FSR<br>k = 6-bit immediate value                                      |               |

| FSR Increment instructions 13                                                         | 3210          |

| OPCODE                                                                                | n m (mode)    |

| n = appropriate FSR<br>m = 2-bit mode value                                           |               |

| OPCODE only<br>13                                                                     | 0             |

| OPCOL                                                                                 |               |

|                                                                                       |               |

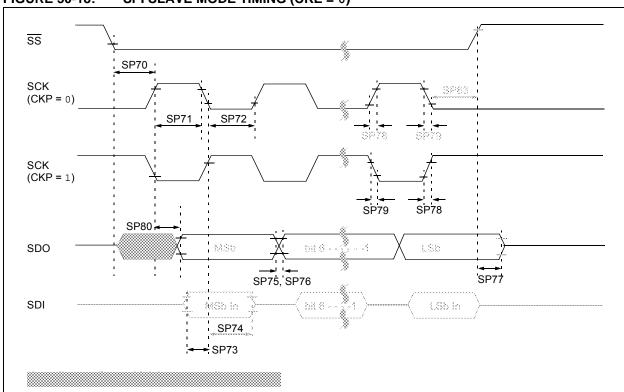

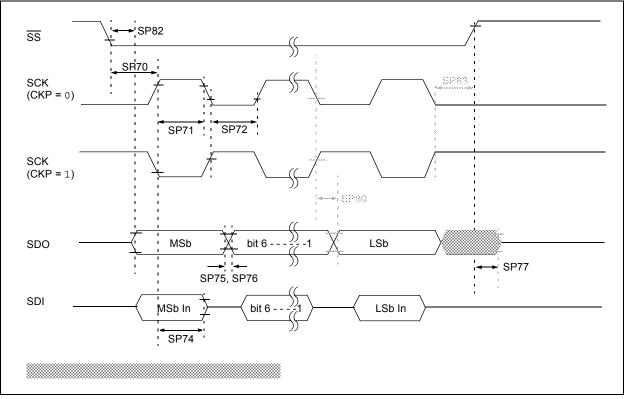

#### FIGURE 30-18: SPI SLAVE MODE TIMING (CKE = 0)

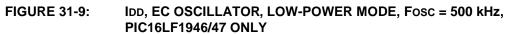

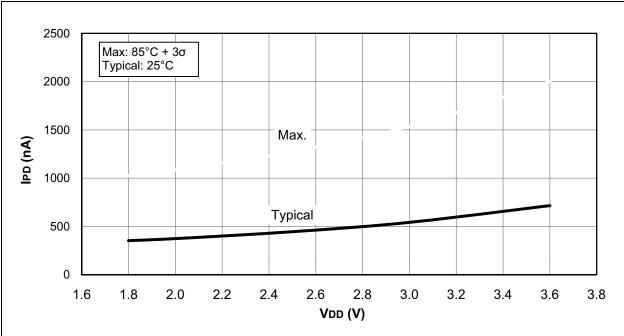

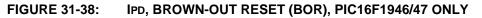

#### FIGURE 31-34: IPD, WATCHDOG TIMER (WDT), PIC16F1946/47 ONLY

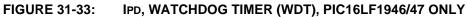

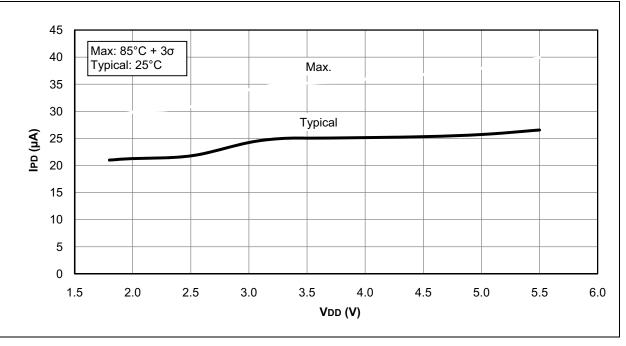

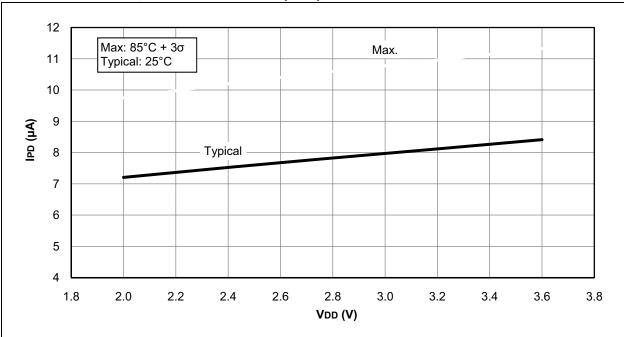

#### FIGURE 31-37: IPD, BROWN-OUT RESET (BOR), PIC16LF1946/47 ONLY

#### 32.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 32.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 32.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 32.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

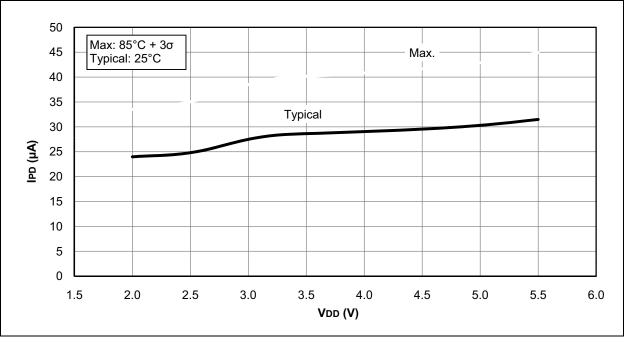

#### 33.2 Package Details

The following sections give the technical details of the packages.

### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

Fax: 852-2401-3431

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

France - Saint Cloud Tel: 33-1-30-60-70-00

**Germany - Garching** Tel: 49-8931-9700 **Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820