Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1946t-i-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

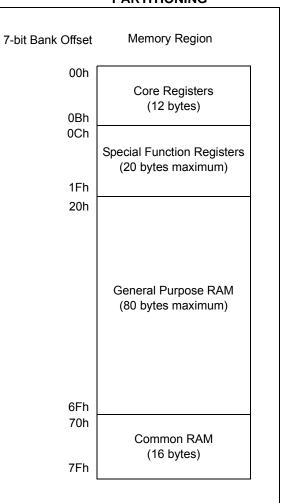

#### 3.3.1 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.3.2 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

#### 3.3.2.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2** "**Linear Data Memory**" for more information.

#### 3.3.3 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-3: BANKED MEMORY PARTITIONING

#### 3.3.4 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-3.

#### TABLE 3-3:MEMORY MAP TABLES

| Device           | Banks | Table No.            |

|------------------|-------|----------------------|

| PIC16(L)F1946/47 | 0-7   | Table 3-4            |

|                  | 8-15  | Table 3-5, Table 3-8 |

|                  | 16-23 | Table 3-6            |

|                  | 23-31 | Table 3-7, Table 3-9 |

#### REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2 (CONTINUED)

- bit 1-0 WRT<1:0>: Flash Memory Self-Write Protection bits

- 8 kW Flash memory (PIC16(L)F1946):

- 11 = Write protection off

- 10 = 000h to 1FFh write-protected, 200h to 1FFFh may be modified by EECON control

- 01 = 000h to FFFh write-protected, 1000h to 1FFFh may be modified by EECON control

- 00 = 000h to 1FFFh write-protected, no addresses may be modified by EECON control

- 16 kW Flash memory (PIC16(L)F1947):

- 11 = Write protection off

- 10 = 000h to 1FFh write-protected, 200h to 3FFFh may be modified by EECON control

- 01 = 000h to 1FFFh write-protected, 2000h to 3FFFh may be modified by EECON control

- 00 = 000h to 3FFFh write-protected, no addresses may be modified by EECON control

- Note 1: The LVP bit cannot be programmed to '0' when Programming mode is entered via LVP.

- 2: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

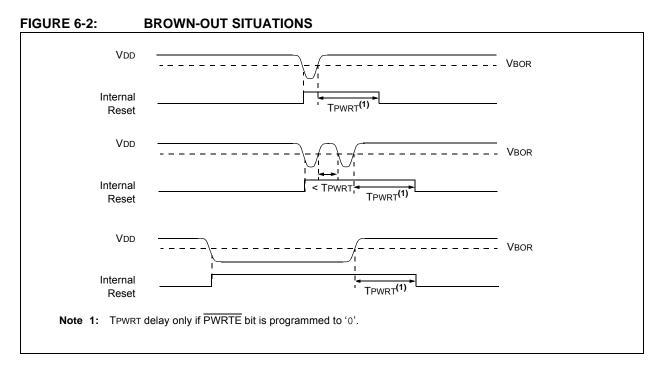

- **3:** See Vbor parameter for specific trip point voltages.

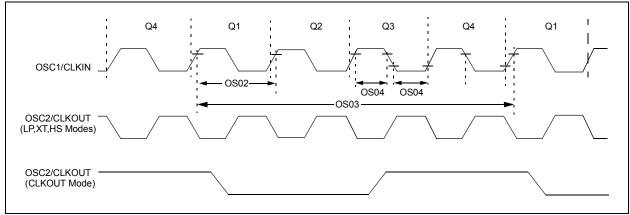

#### 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT, or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

#### TABLE 5-1: OSCILLATOR SWITCHING DELAYS

#### Switch To Switch From Frequency **Oscillator Delay** LFINTOSC<sup>(1)</sup> 31 kHz MFINTOSC<sup>(1)</sup> Sleep 31.25 kHz-500 kHz 2 cycles HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz EC, RC<sup>(1)</sup> Sleep/POR DC - 32 MHz 2 cycles EC. RC<sup>(1)</sup> **LFINTOSC** DC - 32 MHz 1 cycle of each Timer1 Oscillator Sleep/POR 32 kHz-20 MHz 1024 Clock Cycles (OST) LP, XT, HS<sup>(1)</sup> MFINTOSC<sup>(1)</sup> 31.25 kHz-500 kHz Any clock source 2 µs (approx.) HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz LFINTOSC<sup>(1)</sup> 31 kHz Any clock source 1 cvcle of each Timer1 Oscillator 32 kHz Any clock source 1024 Clock Cycles (OST) PLL inactive 16-32 MHz PLL active 2 ms (approx.)

**Note 1:** PLL inactive.

### 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

### 6.3 Register Definitions: BOR Control

#### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN  | —   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |     |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit         |

|---------|-----------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words ≠ 01:         |

|         | SBOREN is read/write, but has no effect on the BOR. |

|         | If BOREN <1:0> in Configuration Words = 01:         |

|         | 1 = BOR Enabled                                     |

|         | 0 = BOR Disabled                                    |

| bit 6-1 | Unimplemented: Read as '0'                          |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit    |

|         | 1 = The Brown-out Reset circuit is active           |

|         | 0 = The Brown-out Reset circuit is inactive         |

#### EXAMPLE 11-2: DATA EEPROM WRITE

|                      | BANKSEL<br>MOVLW<br>MOVWF<br>MOVLW<br>BCF<br>BCF<br>BSF     | DATA_EE_ADDR<br>EEADRL<br>DATA_EE_DATA<br>EEDATL<br>EECON1, CFGS<br>EECON1, EEPGD |                                                                                                                                                                     |

|----------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Required<br>Sequence | BCF<br>MOVLW<br>MOVWF<br>BSF<br>BSF<br>BCF<br>BTFSC<br>GOTO | 55h<br>EECON2<br>OAAh<br>EECON2<br>EECON1, WR<br>INTCON, GIE<br>EECON1, WREN      | ;Disable INTs.<br>;<br>;Write 55h<br>;<br>;Write AAh<br>;Set WR bit to begin write<br>;Enable Interrupts<br>;Disable writes<br>;Wait for write to complete<br>;Done |

| Q1 Q2 Q3 Q4                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC PC + 1 XEEADRH,EEADRL PC + 3 X PC + 4 X PC + 5                                                                                                                                                                    |

| INSTR (PC) INSTR (PC + 1) EEDATH,EEDATL INSTR (PC + 3) INSTR (PC + 4)                                                                                                                                                |

| INSTR(PC - 1)       BSF EECON1,RD       INSTR(PC + 1)       Forced NOP       INSTR(PC + 3)       INSTR(PC + 4)         executed here       executed here       executed here       executed here       executed here |

|                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                      |

#### REGISTER 11-3: EEADRL: EEPROM ADDRESS LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0  | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|----------|-------------------|---------|----------------|------------------|------------------|-------------|

| 10/070/0         | 1010 0/0 | 10,00 0,0         |         |                | 1000 0/0         | 10,00,0          | 10,00 0,0   |

|                  |          |                   | EEAD    | R<7:0>         |                  |                  |             |

| bit 7            |          |                   |         |                |                  |                  | bit 0       |

| <u> </u>         |          |                   |         |                |                  |                  |             |

| Legend:          |          |                   |         |                |                  |                  |             |

| R = Readable     | bit      | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is unch  | anged    | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |          | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0 EEADR<7:0>: Specifies the Least Significant bits for program memory address or EEPROM address

#### REGISTER 11-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|------------|---------|---------|---------|

| (1)   |         |         |         | EEADR<14:8 | >       |         |         |

| bit 7 |         |         |         |            |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 EEADR<14:8>: Specifies the Most Significant bits for program memory address or EEPROM address

Note 1: Unimplemented, read as '1'.

### 12.15 PORTG Registers

PORTG is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISG (Register 12-25). Setting a TRISG bit (= 1) will make the corresponding PORTG pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISG bit (= 0) will make the corresponding PORTG pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). The exception is RG5, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize an I/O port.

Reading the PORTG register (Register 12-24) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATG). RG5 reads '0' when MCLRE = 1.

The TRISG register (Register 12-25) controls the PORTG pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISG register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 12.15.1 ANSELG REGISTER

The ANSELG register (Register 12-27) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELG bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELG bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELG register must be initialized     |

|-------|---------------------------------------------|

|       | to configure an analog channel as a digital |

|       | input. Pins configured as analog inputs     |

|       | will read '0'.                              |

#### PORTG FUNCTIONS AND OUTPUT 12.15.2 PRIORITIES

Each PORTG pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-16.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the priority list.

| Pin Name | Function Priority <sup>(1)</sup>                                         |

|----------|--------------------------------------------------------------------------|

| RG0      | CCP3 (CCP)<br>P3A (CCP)<br>SEG42 (LCD)<br>RG0                            |

| RG1      | TX2 (EUSART)<br>CK2 (EUSART)<br>C3OUT (Comparator)<br>SEG43 (LCD)<br>RG1 |

| RG2      | DT2<br>SEG44 (LCD)<br>RG2                                                |

| RG3      | CCP4 (CCP)<br>P3D (CCP)<br>SEG45 (LCD)<br>RG3                            |

| RG4      | CCP5 (CCP)<br>P1D (CCP)<br>SEG26 (LCD)<br>RG4                            |

| RG5      | Input-only pin                                                           |

#### TABLE 12-16: PORTG OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

| R/W-0/0         | R/W-0/0                                                   | R/W-0/0                                     | R/W-0/0         |               | U-0                              | R/W-0/0          | R/W-0/0      |  |  |  |  |

|-----------------|-----------------------------------------------------------|---------------------------------------------|-----------------|---------------|----------------------------------|------------------|--------------|--|--|--|--|

| CxINTP          |                                                           | 1                                           | H<1:0>          |               |                                  |                  | H<1:0>       |  |  |  |  |

| bit 7           |                                                           |                                             |                 |               |                                  |                  | bit (        |  |  |  |  |

|                 |                                                           |                                             |                 |               |                                  |                  |              |  |  |  |  |

| Legend:         |                                                           |                                             |                 |               |                                  |                  |              |  |  |  |  |

| R = Readabl     | e bit                                                     | W = Writable                                | bit             | U = Unimpler  | mented bit, read                 | l as '0'         |              |  |  |  |  |

| u = Bit is und  | hanged                                                    | x = Bit is unk                              | nown            | -n/n = Value  | at POR and BO                    | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is se | t                                                         | '0' = Bit is cle                            | ared            |               |                                  |                  |              |  |  |  |  |

|                 |                                                           |                                             |                 |               |                                  |                  |              |  |  |  |  |

| bit 7           | CxINTP: Cor                                               | nparator Interru                            | upt on Positive | Going Edge E  | nable bits                       |                  |              |  |  |  |  |

|                 |                                                           | 1 0                                         |                 | 1 0           | ing edge of the                  |                  |              |  |  |  |  |

|                 | 0 = No interr                                             | upt flag will be                            | set on a positi | ve going edge | of the CxOUT b                   | bit              |              |  |  |  |  |

| bit 6           |                                                           | nparator Interr                             | 0               | 0 0           |                                  |                  |              |  |  |  |  |

|                 |                                                           |                                             |                 |               | oing edge of the<br>of the CxOUT |                  |              |  |  |  |  |

| bit 5-4         | CxPCH<1:0>: Comparator Positive Input Channel Select bits |                                             |                 |               |                                  |                  |              |  |  |  |  |

|                 | 11 = CxVP connects to Vss                                 |                                             |                 |               |                                  |                  |              |  |  |  |  |

|                 |                                                           | 10 = CxVP connects to FVR Voltage Reference |                 |               |                                  |                  |              |  |  |  |  |

|                 |                                                           | onnects to DA                               | 0               | rence         |                                  |                  |              |  |  |  |  |

| bit 3-2         |                                                           | onnects to CxI                              |                 |               |                                  |                  |              |  |  |  |  |

|                 | •                                                         | ted: Read as '                              |                 | Channel Cala  | at laite                         |                  |              |  |  |  |  |

| bit 1-0         |                                                           | Comparator                                  | 0 1             | Channel Sele  | UT DITS                          |                  |              |  |  |  |  |

|                 |                                                           | onnects to CxI<br>onnects to CxI            | •               |               |                                  |                  |              |  |  |  |  |

|                 |                                                           | onnects to CxI                              |                 |               |                                  |                  |              |  |  |  |  |

|                 | 00 = CxVN c                                               | 00 = CxVN connects to CxINO- pin            |                 |               |                                  |                  |              |  |  |  |  |

|                 |                                                           |                                             |                 |               |                                  |                  |              |  |  |  |  |

#### REGISTER 18-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

#### REGISTER 18-3: CMOUT: COMPARATOR OUTPUT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R-0/0    | R-0/0 | R-0/0  |

|-------|-----|-----|-----|-----|----------|-------|--------|

|       | —   | _   | _   | _   | — MC3OUT |       | MC1OUT |

| bit 7 |     |     |     |     |          |       | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

- bit 7-3 Unimplemented: Read as '0'

- bit 2 MC3OUT: Mirror Copy of C3OUT bit

- bit 1 MC2OUT: Mirror Copy of C2OUT bit

- bit 0 MC10UT: Mirror Copy of C10UT bit

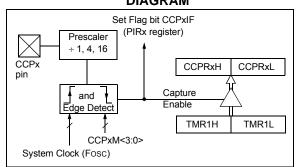

### 23.1 Capture Mode

The Capture mode function described in this section is available and identical for CCP modules ECCP1, ECCP2, ECCP3, CCP4 and CCP5.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- · Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, and the old captured value is overwritten by the new captured value.

Figure 23-1 shows a simplified diagram of the Capture operation.

#### 23.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Also, the CCPx pin function can be moved to alternative pins using the APFCON register. Refer to **Section 12.1 "Alternate Pin Function"** for more details.

Note: If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 23-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 23.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 21.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 23.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for the Capture mode to  |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

#### 23.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 23-1 demonstrates the code to perform this function.

#### EXAMPLE 23-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL CCPxCON | ;Set Bank bits to point |

|-----------------|-------------------------|

|                 | ;to CCPxCON             |

| CLRF CCPxCON    | ;Turn CCP module off    |

| MOVLW NEW_CAPT_ | PS;Load the W reg with  |

|                 | ;the new prescaler      |

|                 | ;move value and CCP ON  |

| MOVWF CCPxCON   | ;Load CCPxCON with this |

|                 | ;value                  |

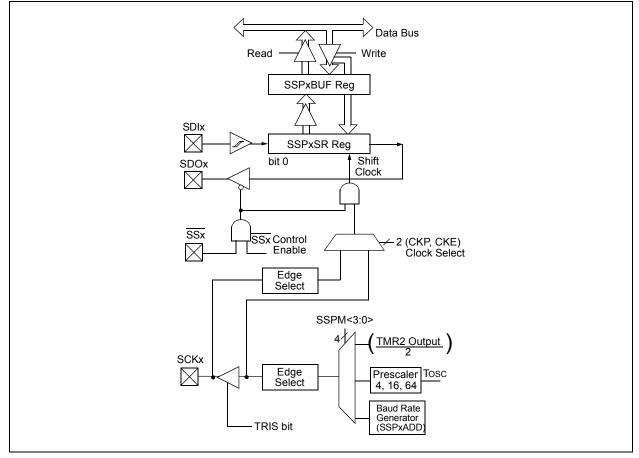

### 24.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP1 AND MSSP2) MODULE

#### 24.1 Master SSPx (MSSPx) Module Overview

The Master Synchronous Serial Port (MSSPx) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSPx module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 24-1 is a block diagram of the SPI interface module.

#### 24.4.4 SDAx HOLD TIME

The hold time of the SDAx pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDAx is held valid after the falling edge of SCLx. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

TABLE 24-2:I<sup>2</sup>C BUS TERMS

| TERM                | Description                                                                                                                                                                                      |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                   |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                    |

| Master              | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                                    |

| Slave               | The device addressed by the master.                                                                                                                                                              |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                              |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                           |

| Idle                | No master is controlling the bus,<br>and both SDAx and SCLx lines are<br>high.                                                                                                                   |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                     |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                     |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                              |

| Write Request       | Slave receives a matching<br>address with R/W bit clear, and is<br>ready to clock in data.                                                                                                       |

| Read Request        | Master sends an address byte with the $R/\overline{W}$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCLx low to stall communication.                                                                                                                                   |

| Bus Collision       | Any time the SDAx line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                      |

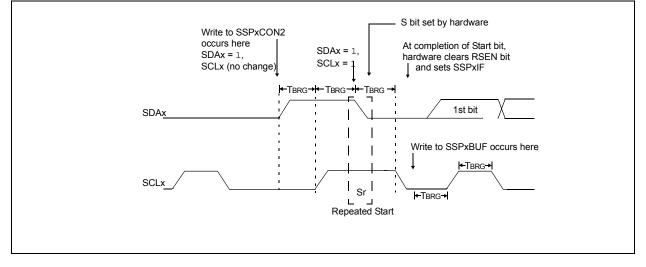

#### 24.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit of the SSPxCON2 register is programmed high and the Master state machine is no longer active. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. SCLx is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

### FIGURE 24-27: REPEAT START CONDITION WAVEFORM

| R/C/HS-0/0       | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0/0                                                                                                        | R/W-0/0                                                                                     | R/W-0/0                                                                               | R/W-0/0                                                     | R/W-0/0                                                                                                  | R/W-0/0                                 |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| WCOL             | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SSPEN                                                                                                          | CKP                                                                                         |                                                                                       | SSPN                                                        | VI<3:0>                                                                                                  |                                         |  |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                |                                                                                             |                                                                                       |                                                             |                                                                                                          | bit (                                   |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                |                                                                                             |                                                                                       |                                                             |                                                                                                          |                                         |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                |                                                                                             |                                                                                       |                                                             |                                                                                                          |                                         |  |

| R = Readable b   | vit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | W = Writable b                                                                                                 | it                                                                                          | U = Unimpleme                                                                         | ented bit, read as                                          | s 'O'                                                                                                    |                                         |  |

| u = Bit is uncha | nged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | x = Bit is unkno                                                                                               | own                                                                                         | -n/n = Value at                                                                       | POR and BOR/                                                | /alue at all other I                                                                                     | Resets                                  |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | '0' = Bit is clea                                                                                              | red                                                                                         | HS = Bit is set                                                                       | by hardware                                                 | C = User cleare                                                                                          | ed                                      |  |

| bit 7            | Master mode:<br>1 = A write to<br>be started<br>0 = No collision<br>Slave mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | l<br>on<br>BUF register is wi                                                                                  | egister was atte                                                                            |                                                                                       |                                                             | ere not valid for a<br>ust be cleared in se                                                              |                                         |  |

| bit 6            | $\frac{\text{In SPI mode:}}{1 = A \text{ new byte}}$ if only trantion (and the transmit of transmit of transmit of the transmit of tr | R is lost. Overflow<br>smitting data, to a<br>ransmission) is in<br>ow<br>received while th<br>mode (must be c | e the SSPxBUF<br>can only occur<br>avoid setting ove<br>itiated by writing<br>ne SSPxBUF re | in Slave mode. In S<br>rflow. In Master mo<br>to the SSPxBUF<br>egister is still hold | Slave mode, the u<br>ode, the overflow<br>register (must be | data. In case of or<br>ser must read the<br>bit is not set since<br>cleared in softwar<br>byte. SSPOV is | SSPxBUF, ever<br>each new recep<br>re). |  |

| bit 5            | <ul> <li>0 = No overflow</li> <li>SSPEN: Synchronous Serial Port Enable bit<br/>In both modes, when enabled, these pins must be properly configured as input or output<br/>In SPI mode:</li> <li>1 = Enables serial port and configures SCKx, SDOx, SDIx and SSx as the source of the serial port pins<sup>(2)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins<br/>In I<sup>2</sup>C mode:</li> <li>1 = Enables the serial port and configures the SDAx and SCLx pins as the source of the serial port pins<sup>(3)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |                                                                                             |                                                                                       |                                                             |                                                                                                          |                                         |  |

| bit 4            | In <u>SPI mode:</u><br>1 = Idle state for<br>0 = Idle state for<br><u>In I<sup>2</sup>C Slave model</u><br>SCLx release of<br>1 = Enable close                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | control<br>ck<br>< low (clock stret<br><u>node:</u>                                                            | level                                                                                       | nsure data setup                                                                      | time.)                                                      |                                                                                                          |                                         |  |

#### REGISTER 24-2: SSPxCON1: SSPx CONTROL REGISTER 1

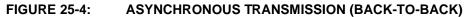

#### TABLE 25-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name     | Bit 7  | Bit 6 | Bit 5   | Bit 4       | Bit 3         | Bit 2     | Bit 1  | Bit 0  | Register<br>on page |

|----------|--------|-------|---------|-------------|---------------|-----------|--------|--------|---------------------|

| BAUD1CON | ABDOVF | RCIDL | _       | SCKP        | BRG16         | _         | WUE    | ABDEN  | 299                 |

| BAUD2CON | ABDOVF | RCIDL | _       | SCKP        | BRG16         | —         | WUE    | ABDEN  | 299                 |

| INTCON   | GIE    | PEIE  | TMR0IE  | INTE        | IOCIE         | TMR0IF    | INTF   | IOCIF  | 90                  |

| PIE1     | _      | ADIE  | RC1IE   | TX1IE       | SSP1IE        | CCP1IE    | TMR2IE | TMR1IE | 91                  |

| PIE4     | _      | _     | RC2IE   | TX2IE       | _             | —         | BCL2IE | SSP2IE | 94                  |

| PIR1     | _      | ADIF  | RC1IF   | TX1IF       | SSP1IF        | CCP1IF    | TMR2IF | TMR1IF | 95                  |

| PIR4     | _      | _     | RC2IF   | TX2IF       | _             | —         | BCL2IF | SSP2IF | 98                  |

| RC1STA   | SPEN   | RX9   | SREN    | CREN        | ADDEN         | FERR      | OERR   | RX9D   | 298                 |

| RC2STA   | SPEN   | RX9   | SREN    | CREN        | ADDEN         | FERR      | OERR   | RX9D   | 298                 |

| SP1BRGL  |        |       | EUSART  | Baud Rate   | Generator, I  | _ow Byte  |        |        | 300*                |

| SP1BRGH  |        |       | EUSART1 | Baud Rate   | Generator, H  | High Byte |        |        | 300*                |

| SP2BRGL  |        |       | EUSART2 | 2 Baud Rate | Generator, I  | _ow Byte  |        |        | 300*                |

| SP2BRGH  |        |       | EUSART2 | Baud Rate   | Generator, H  | High Byte |        |        | 300*                |

| TX1REG   |        |       | EL      | JSART1 Trar | nsmit Registe | er        |        |        | 292*                |

| TX1STA   | CSRC   | TX9   | TXEN    | SYNC        | SENDB         | BRGH      | TRMT   | TX9D   | 297                 |

| TX2REG   |        |       | EU      | JSART2 Trar | nsmit Registe | er        |        |        | 292*                |

| TX2STA   | CSRC   | TX9   | TXEN    | SYNC        | SENDB         | BRGH      | TRMT   | TX9D   | 297                 |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for asynchronous transmission.

\* Page provides register information.

# PIC16(L)F1946/47

### FIGURE 25-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

|                        | 04030304                   | 4040260303                      | 0.99030393  | ų a         | 25          | ХX              | 3030X03                               | 020090    | 40966903    |                                                                                                                                                                                                                                    | estozice).          | 28,03900 | 10.30%                                |

|------------------------|----------------------------|---------------------------------|-------------|-------------|-------------|-----------------|---------------------------------------|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|---------------------------------------|

| 1                      | . М.Л.Ч.М.Г<br>1945 545 55 | fununun.<br>Ssan                | fununu.     | 3<br>5<br>3 |             |                 |                                       | naun.     | .n.n.n.     |                                                                                                                                                                                                                                    | NINITUS<br>Viene da |          | · · · · · · · · · · · · · · · · · · · |

| VABE BRI               |                            | : ~~<br>/<br>:                  | 2<br>1<br>1 | ·<br>·      |             |                 | · · · · · · · · · · · · · · · · · · · | · · · · · |             |                                                                                                                                                                                                                                    |                     | :<br>;   | *<br>*                                |

| sou xH062738<br>Pavosa | ×                          | -<br>-<br>-                     |             | ,<br>,<br>, |             | is<br>Yaaaaaaaa | · · · · · · · · · · · · · · · · · · · |           |             | e de la construcción de la constru<br>Construcción de la construcción de l |                     |          | 2<br>2<br>2                           |

|                        | <b>8</b> 9                 | isee Courran                    | d Sixocoted | ž.          | execp Brods |                 | Classe                                | 9 699 KC  | : User Ree  | a otik                                                                                                                                                                                                                             | ROXREC -            | ?.       | ······                                |

|                        |                            | gi event regut<br>nie elegoence |             |             |             |                 |                                       | i ina Wil | VE DE COM A | 5,00,8                                                                                                                                                                                                                             | i walio tin         | acyosa   | signed is                             |

| 2:                     | The SHEAR                  | 8 coccaine le :                 | de wole the | 9498 b8 w s | 92.         |                 |                                       |           |             |                                                                                                                                                                                                                                    |                     |          |                                       |

#### 25.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 25.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXxSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART. If the RXx/DTx or TXx/CKx pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

The TRIS bits corresponding to the RXx/DTx and TXx/CKx pins should be set.

#### 25.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TXx/CKx line. The TXx/CKx pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 25.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDxCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock and is sampled on the rising edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock and is sampled on the falling edge of each clock.

#### 25.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RXx/DTx pin. The RXx/DTx and TXx/CKx pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.