Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1946t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

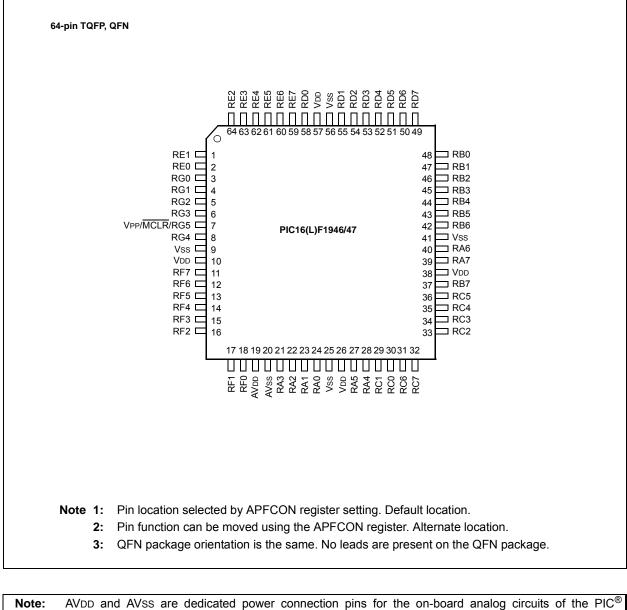

## Pin Diagram – 64-Pin TQFP/QFN (PIC16(L)F1946/47)

**Note:** AVDD and AVSS are dedicated power connection pins for the on-board analog circuits of the PIC<sup>®</sup> microcontroller. The separate power pins help eliminate digital switching noise interference with the analog circuitry inside the device, especially on larger devices with more I/O pins and larger switching currents on the VDD/VSS pins. Customers typically connect these to the appropriate VDD or VSS connections on the PCB, unless there is a lot of noise on the external power rails. In those situations, they will add additional noise filtering components (like capacitors) on the AVDD/AVSS pins to help ensure good solid supply to the analog modules inside the device.

| Name                                               | Function | Input<br>Type | Output<br>Type | Description                             |  |  |  |

|----------------------------------------------------|----------|---------------|----------------|-----------------------------------------|--|--|--|

| RE1/P2C <sup>(1)</sup> /VLCD2                      | RE1      | ST            | CMOS           | General purpose I/O.                    |  |  |  |

|                                                    | P2C      |               | CMOS           | PWM output.                             |  |  |  |

|                                                    | VLCD2    | AN            | —              | LCD analog input.                       |  |  |  |

| RE2/P2B <sup>(1)</sup> /VLCD3                      | RE2      | ST            | CMOS           | General purpose I/O.                    |  |  |  |

|                                                    | P2B      |               | CMOS           | PWM output.                             |  |  |  |

|                                                    | VLCD3    | AN            |                | LCD analog input.                       |  |  |  |

| RE3/P3C <sup>(1)</sup> /COM0                       | RE3      | ST            | CMOS           | General purpose I/O.                    |  |  |  |

|                                                    | P3C      | _             | CMOS           | PWM output.                             |  |  |  |

|                                                    | COM0     | _             | AN             | LCD Analog output.                      |  |  |  |

| RE4/P3B <sup>(1)</sup> /COM1                       | RE4      | ST            | CMOS           | General purpose I/O.                    |  |  |  |

|                                                    | P3B      | _             | CMOS           | PWM output.                             |  |  |  |

|                                                    | COM1     | _             | AN             | LCD Analog output.                      |  |  |  |

| RE5/P1C <sup>(1)</sup> /COM2                       | RE5      | ST            | CMOS           | General purpose I/O.                    |  |  |  |

|                                                    | P1C      | _             | CMOS           | PWM output.                             |  |  |  |

|                                                    | COM2     | _             | AN             | LCD Analog output.                      |  |  |  |

| RE6/P1B <sup>(1)</sup> /COM3                       | RE6      | ST            | _              | General purpose I/O.                    |  |  |  |

|                                                    | P1B      | _             | CMOS           | PWM output.                             |  |  |  |

|                                                    | COM3     | _             | AN             | LCD Analog output.                      |  |  |  |

| RE7/CCP2 <sup>(1)</sup> /P2A <sup>(1)</sup> /SEG31 | RE7      | ST            | CMOS           | General purpose I/O.                    |  |  |  |

|                                                    | CCP2     | ST            | CMOS           | Capture/Compare/PWM.                    |  |  |  |

|                                                    | P2A      | _             | CMOS           | PWM output.                             |  |  |  |

|                                                    | SEG31    | _             | AN             | LCD analog output.                      |  |  |  |

| RF0/AN16/CPS16/C1IN0-/C2IN0                        | RF0      | ST            | CMOS           | General purpose I/O.                    |  |  |  |

| /SEG41/VCAP                                        | AN16     | AN            | _              | A/D Channel input.                      |  |  |  |

|                                                    | CPS16    | AN            | —              | Capacitive sensing input.               |  |  |  |

|                                                    | C1IN0-   | AN            | _              | Comparator negative input.              |  |  |  |

|                                                    | C2IN0-   | AN            | _              | Comparator negative input.              |  |  |  |

|                                                    | SEG41    | _             | AN             | LCD Analog output.                      |  |  |  |

|                                                    | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator. |  |  |  |

| RF1/AN6/CPS6/C2OUT/SRNQ/                           | RF1      | ST            | CMOS           | General purpose I/O.                    |  |  |  |

| SEG19                                              | AN6      | AN            | —              | A/D Channel input.                      |  |  |  |

|                                                    | CPS6     | AN            | _              | Capacitive sensing input.               |  |  |  |

|                                                    | C2OUT    | _             | CMOS           | Comparator output.                      |  |  |  |

|                                                    | SRNQ     | _             | CMOS           | SR Latch inverting output.              |  |  |  |

|                                                    | SEG19    | _             | AN             | LCD Analog output.                      |  |  |  |

| RF2/AN7/CPS7/C1OUT/SRQ/                            | RF2      | ST            | CMOS           | General purpose I/O.                    |  |  |  |

| SEG20                                              | AN7      | AN            | —              | A/D Channel input.                      |  |  |  |

|                                                    | CPS7     | AN            | _              | Capacitive sensing input.               |  |  |  |

|                                                    | C10UT    |               | CMOS           | Comparator output.                      |  |  |  |

|                                                    | SRQ      | _             | CMOS           | SR Latch non-inverting output.          |  |  |  |

|                                                    | SEG20    |               | AN             | LCD Analog output.                      |  |  |  |

| TABLE 1-2: | PIC16(L)F1946/47 PINOUT DESCRIPTION (CONTINUED) |

|------------|-------------------------------------------------|

| IADLL I-2. |                                                 |

HV = High Voltage **Note 1:** Pin function is selectable via the APFCON register.

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit<7> if a label points to a location in program memory.

EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants   |                             |

|-------------|-----------------------------|

| DW          | DATAO ;First constant       |

| DW          | DATA1 ;Second constant      |

| DW          | DATA2                       |

| DW          | DATA3                       |

| my_function | 1                           |

| ; LOTS      | OF CODE                     |

| MOVLW       | DATA_INDEX                  |

| ADDLW       | LOW constants               |

| MOVWF       | FSR1L                       |

| MOVLW       | HIGH constant ;MSb is set   |

| automatical | ly                          |

| MOVWF       | FSR1H                       |

| BTFSC       | STATUS,C ; cary from ADDLW? |

| INCF        | FSR1H,f ;yes                |

| MOVIW       | 0[FSR1]                     |

| ;THE PROGRA | M MEMORY IS IN W            |

|             |                             |

## 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- · 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.6 "Indirect Addressing"** for more information.

Data Memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

#### 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-4.

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| x0Bh or x8Bh | INTCON |

# PIC16(L)F1946/1947

| Address                | Name   | Bit 7                     | Bit 6                                                                                                  | Bit 5          | Bit 4    | Bit 3   | Bit 2    | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |  |

|------------------------|--------|---------------------------|--------------------------------------------------------------------------------------------------------|----------------|----------|---------|----------|---------|---------|----------------------|---------------------------------|--|

| Bank 8                 | 1      |                           |                                                                                                        |                |          |         |          |         |         | •                    |                                 |  |

| 400h <sup>(2)</sup>    | INDF0  | Addressing<br>(not a phys | XXXX XXXX                                                                                              | XXXX XXXX      |          |         |          |         |         |                      |                                 |  |

| 401h <sup>(2)</sup>    | INDF1  |                           | Addressing this location uses contents of FSR1H/FSR1L to address data memory (not a physical register) |                |          |         |          |         |         |                      |                                 |  |

| 402h <sup>(2)</sup>    | PCL    | Program Co                | ounter (PC) L                                                                                          | east Significa | int Byte |         |          |         |         | 0000 0000            | 0000 0000                       |  |

| 403h <sup>(2)</sup>    | STATUS | _                         | _                                                                                                      | _              | то       | PD      | Z        | DC      | С       | 1 1000               | q quuu                          |  |

| 404h <sup>(2)</sup>    | FSR0L  | Indirect Dat              | ta Memory Ac                                                                                           | Idress 0 Low   | Pointer  |         |          |         |         | 0000 0000            | uuuu uuuu                       |  |

| 405h <sup>(2)</sup>    | FSR0H  | Indirect Dat              | ta Memory Ac                                                                                           | ldress 0 High  | Pointer  |         |          |         |         | 0000 0000            | 0000 0000                       |  |

| 406h <sup>(2)</sup>    | FSR1L  | Indirect Dat              | ta Memory Ac                                                                                           | ldress 1 Low   | Pointer  |         |          |         |         | 0000 0000            | uuuu uuuu                       |  |

| 407h <sup>(2)</sup>    | FSR1H  | Indirect Dat              | ta Memory Ac                                                                                           | ldress 1 High  | Pointer  |         |          |         |         | 0000 0000            | 0000 0000                       |  |

| 408h <sup>(2)</sup>    | BSR    | _                         | —                                                                                                      | —              |          | I       | BSR<4:0> |         |         | 0 0000               | 0 0000                          |  |

| 409h <sup>(2)</sup>    | WREG   | Working Re                | Working Register                                                                                       |                |          |         |          |         |         |                      | uuuu uuuu                       |  |

| 40Ah <sup>(1, 2)</sup> | PCLATH | _                         | Write Buffer for the upper 7 bits of the Program Counter                                               |                |          |         |          |         |         |                      | -000 0000                       |  |

| 40Bh <sup>(2)</sup>    | INTCON | GIE                       | PEIE                                                                                                   | TMR0IE         | INTE     | IOCIE   | TMR0IF   | INTF    | IOCIF   | 0000 000x            | 0000 000u                       |  |

| 40Ch                   | ANSELF | ANSELF7                   | ANSELF6                                                                                                | ANSELF5        | ANSELF4  | ANSELF3 | ANSELF2  | ANSELF1 | ANSELF0 | 1111 1111            | 1111 1111                       |  |

| 40Dh                   | ANSELG | _                         | _                                                                                                      | _              | ANSELG4  | ANSELG3 | ANSELG2  | ANSELG1 | _       | 1 111-               | 1 111-                          |  |

| 40Eh                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | _                               |  |

| 40Fh                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | _                               |  |

| 410h                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | —                               |  |

| 411h                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | —                               |  |

| 412h                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | _                               |  |

| 413h                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | —                               |  |

| 414h                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | _                               |  |

| 415h                   | TMR4   | Timer 4 Mo                | dule Register                                                                                          |                |          |         |          |         |         | 0000 0000            | 0000 0000                       |  |

| 416h                   | PR4    | Timer 4 Per               | riod Register                                                                                          |                |          |         |          |         |         | 1111 1111            | 1111 1111                       |  |

| 417h                   | T4CON  | _                         |                                                                                                        | T4OUT          | PS<3:0>  |         | TMR4ON   | T4CKF   | PS<1:0> | -000 0000            | -000 0000                       |  |

| 418h                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | _                               |  |

| 419h                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | _                               |  |

| 41Ah                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | _                               |  |

| 41Bh                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | _                               |  |

| 41Ch                   | TMR6   | Timer 6 Mo                | dule Register                                                                                          |                |          |         |          |         |         | 0000 0000            | 0000 0000                       |  |

| 41Dh                   | PR6    | Timer 6 Per               | riod Register                                                                                          |                |          |         |          |         |         | 1111 1111            | 1111 1111                       |  |

| 41Eh                   | T6CON  | _                         |                                                                                                        | T6OUT          | PS<3:0>  |         | TMR6ON   | T6CKF   | PS<1:0> | -000 0000            | -000 0000                       |  |

| 41Fh                   | _      | Unimpleme                 | ented                                                                                                  |                |          |         |          |         |         | _                    | _                               |  |

## TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

**2:** These registers can be addressed from any bank.

**3:** Unimplemented, read as '1'.

## 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2, PIE3 and PIE4 registers)

The INTCON, PIR1, PIR2, PIR3 and PIR4 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

## 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is 3 or 4 instruction cycles. For asynchronous interrupts, the latency is 3 to 5 instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

## 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the **Section 9.0 "Power-Down Mode (Sleep)"**for more details.

## 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

## 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the Shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding Shadow register should be modified and the value will be restored when exiting the ISR. The Shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

| R/W-0/       | 0 R/W-0/0          | R-0/0                                                     | R-0/0           | R/W-0/0      | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |

|--------------|--------------------|-----------------------------------------------------------|-----------------|--------------|------------------|------------------|--------------|--|--|

| TMR1G        | IF ADIF            | RCIF                                                      | TXIF            | SSPIF        | CCP1IF           | TMR2IF           | TMR1IF       |  |  |

| bit 7        |                    |                                                           |                 |              |                  |                  | bit          |  |  |

|              |                    |                                                           |                 |              |                  |                  |              |  |  |

| Legend:      |                    |                                                           |                 |              |                  |                  |              |  |  |

| R = Read     | able bit           | W = Writable                                              | bit             | U = Unimple  | mented bit, read | l as '0'         |              |  |  |

| u = Bit is   | unchanged          | x = Bit is unk                                            | nown            | -n/n = Value | at POR and BO    | R/Value at all c | other Resets |  |  |

| '1' = Bit is | set                | '0' = Bit is cle                                          | eared           |              |                  |                  |              |  |  |

| bit 7        | TMR1GIF:           | Timer1 Gate Inte                                          | errupt Flag bit |              |                  |                  |              |  |  |

|              |                    | pt is pending                                             |                 |              |                  |                  |              |  |  |

|              |                    | pt is not pending                                         |                 |              |                  |                  |              |  |  |

| bit 6        | ADIF: A/D          | Converter Interru                                         | upt Flag bit    |              |                  |                  |              |  |  |

|              | 1 = Interru        | pt is pending                                             |                 |              |                  |                  |              |  |  |

|              |                    | pt is not pending                                         |                 |              |                  |                  |              |  |  |

| bit 5        | RCIF: USA          | ART1 Receive Int                                          | errupt Flag bi  | t            |                  |                  |              |  |  |

|              |                    | pt is pending<br>pt is not pending                        |                 |              |                  |                  |              |  |  |

| bit 4        | TXIF: USA          | RT1 Transmit Inf                                          | errupt Flag bi  | t            |                  |                  |              |  |  |

|              | 1 = Interru        | 1 = Interrupt is pending                                  |                 |              |                  |                  |              |  |  |

|              | 0 = Interru        | 0 = Interrupt is not pending                              |                 |              |                  |                  |              |  |  |

| bit 3        | SSPIF: Sy          | SSPIF: Synchronous Serial Port (MSSP1) Interrupt Flag bit |                 |              |                  |                  |              |  |  |

|              |                    | pt is pending                                             |                 |              |                  |                  |              |  |  |

|              |                    | pt is not pending                                         |                 |              |                  |                  |              |  |  |

| bit 2        |                    | CP1 Interrupt Fla                                         | ag bit          |              |                  |                  |              |  |  |

|              |                    | pt is pending<br>pt is not pending                        |                 |              |                  |                  |              |  |  |

| bit 1        |                    |                                                           | orrunt Eloa bit |              |                  |                  |              |  |  |

|              |                    | imer2 to PR2 Int<br>pt is pending                         | enupt riag bit  |              |                  |                  |              |  |  |

|              |                    | pt is not pending                                         |                 |              |                  |                  |              |  |  |

| bit 0        |                    | imer1 Overflow I                                          | nterrupt Flag   | bit          |                  |                  |              |  |  |

|              |                    | pt is pending                                             | interrupt i lug |              |                  |                  |              |  |  |

|              |                    | pt is not pending                                         |                 |              |                  |                  |              |  |  |

| Note:        | Interrupt flag bit | s are set when ar                                         | n interrupt     |              |                  |                  |              |  |  |

|              |                    | s, regardless of th                                       |                 |              |                  |                  |              |  |  |

|              |                    | ig enable bit or t                                        |                 |              |                  |                  |              |  |  |

|              | Enable bit, GIE    | , of the INTCON<br>e should ens                           | •               |              |                  |                  |              |  |  |

|              |                    | rrupt flag bits are                                       |                 |              |                  |                  |              |  |  |

|              | to enabling an ir  |                                                           |                 |              |                  |                  |              |  |  |

## REGISTER 7-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

## 11.3 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash Program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum block size that can be erased by user software.

Flash program memory may only be written or erased if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT<1:0> of Configuration Words.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the EEDATH:EEDATL register pair.

| Note: | If the user wants to modify only a portion |

|-------|--------------------------------------------|

|       | of a previously programmed row, then the   |

|       | contents of the entire row must be read    |

|       | and saved in RAM prior to the erase.       |

The number of data write latches may not be equivalent to the number of row locations. During programming, user software may need to fill the set of write latches and initiate a programming operation multiple times in order to fully reprogram an erased row. For example, a device with a row size of 32 words and eight write latches will need to load the write latches with data and initiate a programming operation four times.

The size of a program memory row and the number of program memory write latches may vary by device. See Table 11-1 for details.

## 11.3.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the Least and Most Significant address bits to the EEADRH:EEADRL register pair.

- 2. Clear the CFGS bit of the EECON1 register.

- 3. Set the EEPGD control bit of the EECON1 register.

- 4. Then, set control bit RD of the EECON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle, in the EEDATH:EEDATL register pair; therefore, it can be read as two bytes in the following instructions.

EEDATH:EEDATL register pair will hold this value until another read or until it is written to by the user.

- Note 1: The two instructions following a program memory read are required to be NOPS. This prevents the user from executing a two-cycle instruction on the next instruction after the RD bit is set.

- 2: Flash program memory can be read regardless of the setting of the CP bit.

## TABLE 11-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device Erase Block (Row) Size/Boundary         |  | Number of Write Latches/Boundary |

|------------------------------------------------|--|----------------------------------|

| PIC16(L)F1946/47 32 words, EEADRL<4:0> = 00000 |  | 32 words, EEADRL<4:0> = 00000    |

## 11.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

#### EXAMPLE 11-6: EEPROM WRITE VERIFY

| BANKSEI | LEEDATL    | ;                    |

|---------|------------|----------------------|

| MOVF    | EEDATL, W  | ;EEDATL not changed  |

|         |            | ;from previous write |

| BSF     | EECON1, RD | ;YES, Read the       |

|         |            | ;value written       |

| XORWF   | EEDATL, W  | ;                    |

| BTFSS   | STATUS, Z  | ;Is data the same    |

| GOTO    | WRITE_ERR  | ;No, handle error    |

| :       |            | ;Yes, continue       |

| 1       |            |                      |

| W-0/0            | W-0/0       | W-0/0             | W-0/0     | W-0/0             | W-0/0            | W-0/0            | W-0/0       |  |  |  |

|------------------|-------------|-------------------|-----------|-------------------|------------------|------------------|-------------|--|--|--|

|                  |             |                   | EEPROM Co | ontrol Register 2 | 2                |                  |             |  |  |  |

| bit 7            | bit 7 bit 0 |                   |           |                   |                  |                  |             |  |  |  |

|                  |             |                   |           |                   |                  |                  |             |  |  |  |

| Legend:          |             |                   |           |                   |                  |                  |             |  |  |  |

| R = Readable     | bit         | W = Writable      | bit       | U = Unimpler      | nented bit, read | 1 as '0'         |             |  |  |  |

| S = Bit can onl  | y be set    | x = Bit is unkr   | nown      | -n/n = Value a    | at POR and BO    | R/Value at all c | ther Resets |  |  |  |

| '1' = Bit is set |             | '0' = Bit is clea | ared      |                   |                  |                  |             |  |  |  |

#### REGISTER 11-6: EECON2: EEPROM CONTROL 2 REGISTER

#### bit 7-0 Data EEPROM Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the EECON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes. Refer to **Section 11.2.2** "Writing to the Data EEPROM Memory" for more information.

#### TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name   | Bit 7                                               | Bit 6         | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on Page |

|--------|-----------------------------------------------------|---------------|--------|-------|-------|--------|-------|--------|---------------------|

| EECON1 | EEPGD                                               | CFGS          | LWLO   | FREE  | WRERR | WREN   | WR    | RD     | 119                 |

| EECON2 | EEPROM Control Register 2 (not a physical register) |               |        |       |       |        |       | 106*   |                     |

| EEADRL |                                                     | EEADRL<7:0>   |        |       |       |        |       |        | 118                 |

| EEADRH | (1)                                                 | EEADRH<6:0>   |        |       |       |        |       |        | 118                 |

| EEDATL |                                                     | EEDATL<7:0>   |        |       |       |        |       | 117    |                     |

| EEDATH | _                                                   | — EEDATH<5:0> |        |       |       |        |       | 117    |                     |

| INTCON | GIE                                                 | PEIE          | TMR0IE | INTE  | IOCIE | TMR0IF | INTF  | IOCIF  | 90                  |

| PIE2   | OSFIE                                               | C2IE          | C1IE   | EEIE  | BCLIE | LCDIE  | C3IE  | CCP2IE | 92                  |

| PIR2   | OSFIF                                               | C2IF          | C1IF   | EEIF  | BCLIF | LCDIF  | C3IF  | CCP2IF | 96                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by data EEPROM module.

\* Page provides register information.

Note 1: Unimplemented, read as '1'.

## 12.5 PORTB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 12-7). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 12-6) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

The TRISB register (Register 12-7) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

## 12.5.1 WEAK PULL-UPS

Each of the PORTB pins has an individually configurable internal weak pull-up. Control bits WPUB<7:0> enable or disable each pull-up (see Register 12-9). Each weak pull-up is automatically turned off when the port pin is configured as an output. All pull-ups are disabled on a Power-on Reset by the WPUEN bit of the OPTION\_REG register.

## 12.5.2 INTERRUPT-ON-CHANGE

All of the PORTB pins are individually configurable as an interrupt-on-change pin. Control bits IOCB<7:0> enable or disable the interrupt function for each pin. The interrupt-on-change feature is disabled on a Power-on Reset. Reference **Section 13.0 "Interrupt-On-Change"** for more information.

#### 12.5.3 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions, such as the EUSART RX signal, override other port functions and are included in the priority list.

| Pin<br>Name | Function Priority <sup>(1)</sup>                                                      |

|-------------|---------------------------------------------------------------------------------------|

| RB0         | SEG30 (LED)<br>SRI (SR Latch)<br>RB0                                                  |

| RB1         | SEG8 (LCD)<br>RB1                                                                     |

| RB2         | SEG9 (LCD)<br>RB2                                                                     |

| RB3         | SEG10 (LCD)<br>RB3                                                                    |

| RB4         | SEG11 (LCD)<br>RB4                                                                    |

| RB5         | SEG29 (LCD)<br>RB5                                                                    |

| RB6         | ICSPCLK (Programming)<br>ICDCLK (enabled by Configuration Word)<br>SEG38 (LCD)<br>RB6 |

| RB7         | ICSPDAT (Programming)<br>ICDDAT (enabled by Configuration Word)<br>SEG39 (LCD)<br>RB7 |

TABLE 12-5: PORTB OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

## 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- · ADC input channel

- DACOUT pin

- Capacitive Sensing module (CPS)

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

## EQUATION 17-1: DAC OUTPUT VOLTAGE

#### <u>IF DACEN = 1</u>

$VOUT = \left( (VSOURCE + -VSOURCE -) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE -$

#### <u>IF DACEN = 0 & DACLPS = 1 & DACR[4:0] = 11111</u>

VOUT = VSOURCE +

#### <u>IF DACEN = 0 & DACLPS = 0 & DACR[4:0] = 00000</u>

VOUT = VSOURCE -

VSOURCE+ = VDD, VREF, or FVR BUFFER 2

VSOURCE- = VSS

## 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 30.0** "**Electrical Specifications**".

## 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the following equations:

## 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17-2 shows an example buffering technique.

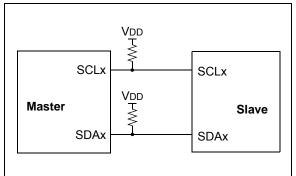

## 24.3 I<sup>2</sup>C MODE OVERVIEW

The Inter-Integrated Circuit Bus (I<sup>2</sup>C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- · Serial Clock (SCLx)

- · Serial Data (SDAx)

Figure 24-2 and Figure 24-3 show the block diagrams of the MSSPx module when operating in  $I^{2}C$  mode.

Both the SCLx and SDAx connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 24-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode

(master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDAx line while the SCLx line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

#### FIGURE 24-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDAx line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCLx line is held low. Transitions that occur while the SCLx line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an ACK bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDAx line while the SCLx line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols:

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

#### 25.1.2.3 Receive Interrupts

The RCxIF interrupt flag bit of the PIR1/PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCxIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCxIF interrupts are enabled by setting the following bits:

- RCxIE interrupt enable bit of the PIE1/PIE4 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCxIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 25.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCxSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCxREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCxSTA register which resets the EUSART. Clearing the CREN bit of the RCxSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive |

|-------|------------------------------------------|

|       | FIFO have framing errors, repeated reads |

|       | of the RCxREG will not clear the FERR    |

|       | bit.                                     |

#### 25.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated If a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCxSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCxSTA register or by resetting the EUSART by clearing the SPEN bit of the RCxSTA register.

## 25.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set, the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

#### 25.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCxSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCxIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

|        |                   |            |                               |                | SY         | NC = 0, BRGH                  | l = 1, BRG <sup>.</sup> | <b>16 =</b> 0 |                               |                |            |                               |

|--------|-------------------|------------|-------------------------------|----------------|------------|-------------------------------|-------------------------|---------------|-------------------------------|----------------|------------|-------------------------------|

| BAUD   | Fosc = 32.000 MHz |            | Fosc = 18.432 MHz             |                |            | Fosc = 16.000 MHz             |                         |               | Fosc = 11.0592 MHz            |                |            |                               |

| RATE   | Actual<br>Rate    | %<br>Error | SPxBRGL<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPxBRGL<br>value<br>(decimal) | Actual<br>Rate          | %<br>Error    | SPxBRGL<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPxBRGL<br>value<br>(decimal) |

| 300    | —                 | —          | _                             |                |            | _                             | -                       |               | —                             | _              |            | _                             |

| 1200   | —                 | _          | _                             | _              | _          | _                             | —                       | _             | _                             | —              | _          | _                             |

| 2400   | —                 | —          | —                             | —              | _          | —                             | _                       | _             | _                             | —              | _          | _                             |

| 9600   | 9615              | 0.16       | 207                           | 9600           | 0.00       | 119                           | 9615                    | 0.16          | 103                           | 9600           | 0.00       | 71                            |

| 10417  | 10417             | 0.00       | 191                           | 10378          | -0.37      | 110                           | 10417                   | 0.00          | 95                            | 10473          | 0.53       | 65                            |

| 19.2k  | 19.23k            | 0.16       | 103                           | 19.20k         | 0.00       | 59                            | 19.23k                  | 0.16          | 51                            | 19.20k         | 0.00       | 35                            |

| 57.6k  | 57.14k            | -0.79      | 34                            | 57.60k         | 0.00       | 19                            | 58.82k                  | 2.12          | 16                            | 57.60k         | 0.00       | 11                            |

| 115.2k | 117.64k           | 2.12       | 16                            | 115.2k         | 0.00       | 9                             | 111.1k                  | -3.55         | 8                             | 115.2k         | 0.00       | 5                             |

## TABLE 25-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                  |            |                               |                | SY         | NC = 0, BRGH                  | H = 1, BRG     | <b>16 =</b> 0 |                               |                |            |                               |

|--------|------------------|------------|-------------------------------|----------------|------------|-------------------------------|----------------|---------------|-------------------------------|----------------|------------|-------------------------------|

| BAUD   | Fosc = 8.000 MHz |            | Fosc = 4.000 MHz              |                |            | Fosc = 3.6864 MHz             |                |               | Fosc = 1.000 MHz              |                |            |                               |

| RATE   | Actual<br>Rate   | %<br>Error | SPxBRGL<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPxBRGL<br>value<br>(decimal) | Actual<br>Rate | %<br>Error    | SPxBRGL<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPxBRGL<br>value<br>(decimal) |

| 300    | _                | _          | _                             | _              | _          | _                             | _              | _             | _                             | 300            | 0.16       | 207                           |

| 1200   | —                | —          | —                             | 1202           | 0.16       | 207                           | 1200           | 0.00          | 191                           | 1202           | 0.16       | 51                            |

| 2400   | 2404             | 0.16       | 207                           | 2404           | 0.16       | 103                           | 2400           | 0.00          | 95                            | 2404           | 0.16       | 25                            |

| 9600   | 9615             | 0.16       | 51                            | 9615           | 0.16       | 25                            | 9600           | 0.00          | 23                            | _              | _          | _                             |

| 10417  | 10417            | 0.00       | 47                            | 10417          | 0.00       | 23                            | 10473          | 0.53          | 21                            | 10417          | 0.00       | 5                             |

| 19.2k  | 19231            | 0.16       | 25                            | 19.23k         | 0.16       | 12                            | 19.2k          | 0.00          | 11                            | _              | _          | _                             |

| 57.6k  | 55556            | -3.55      | 8                             | —              | _          | _                             | 57.60k         | 0.00          | 3                             | —              | _          | _                             |

| 115.2k | —                | _          | —                             | —              | _          | _                             | 115.2k         | 0.00          | 1                             | —              | _          | _                             |

|        |                |            |                                  |                | SY         | NC = 0, BRGH                     | I = 0, BRG1    | 16 = 1     |                                  |                |            |                                  |

|--------|----------------|------------|----------------------------------|----------------|------------|----------------------------------|----------------|------------|----------------------------------|----------------|------------|----------------------------------|

| BAUD   | Fos            | c = 32.00  | 0 MHz                            | Fos            | c = 18.43  | 2 MHz                            | Fos            | c = 16.00  | 0 MHz                            | Fos            | c = 11.059 | 92 MHz                           |

| RATE   | Actual<br>Rate | %<br>Error | SPxBRGH:<br>SPxBRGL<br>(decimal) |

| 300    | 300.0          | 0.00       | 6666                             | 300.0          | 0.00       | 3839                             | 300.03         | 0.01       | 3332                             | 300.0          | 0.00       | 2303                             |

| 1200   | 1200.1         | 0.02       | 3332                             | 1200           | 0.00       | 959                              | 1200.5         | 0.04       | 832                              | 1200           | 0.00       | 575                              |

| 2400   | 2401           | -0.04      | 832                              | 2400           | 0.00       | 479                              | 2398           | -0.08      | 416                              | 2400           | 0.00       | 287                              |

| 9600   | 9615           | 0.16       | 207                              | 9600           | 0.00       | 119                              | 9615           | 0.16       | 103                              | 9600           | 0.00       | 71                               |

| 10417  | 10417          | 0.00       | 191                              | 10378          | -0.37      | 110                              | 10417          | 0.00       | 95                               | 10473          | 0.53       | 65                               |

| 19.2k  | 19.23k         | 0.16       | 103                              | 19.20k         | 0.00       | 59                               | 19.23k         | 0.16       | 51                               | 19.20k         | 0.00       | 35                               |

| 57.6k  | 57.14k         | -0.79      | 34                               | 57.60k         | 0.00       | 19                               | 58.82k         | 2.12       | 16                               | 57.60k         | 0.00       | 11                               |

| 115.2k | 117.6k         | 2.12       | 16                               | 115.2k         | 0.00       | 9                                | 111.11k        | -3.55      | 8                                | 115.2k         | 0.00       | 5                                |

#### 25.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXxSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART. If the RXx/DTx or TXx/CKx pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

RXx/DTx and TXx/CKx pin output drivers must be disabled by setting the corresponding TRIS bits.

#### 25.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 25.5.1.3 "Synchronous Master Transmission"), except in the case of the Sleep mode. If two words are written to the TXxREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXxREG register.

- 3. The TXxIF bit will not be set.

- After the first character has been shifted out of TSR, the TXxREG register will transfer the second character to the TSR and the TXxIF bit will now be set.

- If the PEIE and TXxIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 25.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- 3. Clear the CREN and SREN bits.

- 4. If using interrupts, ensure that the GIE and PEIE bits of the INTCON register are set and set the TXxIE bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXxREG register.

#### 26.2.2 CURRENT RANGES

The capacitive sensing oscillator can operate in one of seven different power modes. The power modes are separated into two ranges: the low range and the high range.

When the oscillator's low range is selected, the fixed internal voltage references of the capacitive sensing oscillator are being used. When the oscillator's high range is selected, the variable voltage references supplied by the FVR and DAC modules are being used. Selection between the voltage references is controlled by the CPSRM bit of the CPSCON0 register. See **Section 26.2.1 "Voltage Reference Modes"** for more information.

Within each range there are three distinct power modes: low, medium and high. Current consumption is dependent upon the range and mode selected. Selecting Power modes within each range is accomplished by configuring the CPSRNG <1:0> bits in the CPSCON0 register. See Table for proper power mode selection. The remaining mode is a Noise Detection mode that resides within the high range. The Noise Detection mode is unique in that it disables the sinking and sourcing of current on the analog pin but leaves the rest of the oscillator circuitry active. This reduces the oscillation frequency on the analog pin to zero and also greatly reduces the current consumed by the oscillator module.

When noise is introduced onto the pin, the oscillator is driven at the frequency determined by the noise. This produces a detectable signal at the comparator output, indicating the presence of activity on the pin.

Figure 26-2 shows a more detailed drawing of the current sources and comparators associated with the oscillator.

| CPSRM | Range | CPSRNG<1:0> | Current Range <sup>(1)</sup> |  |  |

|-------|-------|-------------|------------------------------|--|--|

|       |       | 00          | Noise Detection              |  |  |

| 1     | Lliab | 01          | Low                          |  |  |

| 1     | High  | 10          | Medium                       |  |  |

|       |       | 11          | High                         |  |  |

|       |       | 00          | Off                          |  |  |

| 0     | Law   | 01          | Low                          |  |  |

| 0     | Low   | 10          | Medium                       |  |  |

|       |       | 11          | High                         |  |  |

Note 1: See Power-Down Currents (IPD) in Section 30.0 "Electrical Specifications" for more information.

## 26.2.3 TIMER RESOURCES

To measure the change in frequency of the capacitive sensing oscillator, a fixed time base is required. For the period of the fixed time base, the capacitive sensing oscillator is used to clock either Timer0 or Timer1. The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed time base.

## 26.2.4 FIXED TIME BASE

To measure the frequency of the capacitive sensing oscillator, a fixed time base is required. Any timer resource or software loop can be used to establish the fixed time base. It is up to the end user to determine the method in which the fixed time base is generated.

| Note: | The fixed time base can not be generated  |

|-------|-------------------------------------------|

|       | by the timer resource that the capacitive |

|       | sensing oscillator is clocking.           |

## 26.2.4.1 Timer0

To select Timer0 as the timer resource for the CPS module:

- Set the T0XCS bit of the CPSCON0 register.

- Clear the TMR0CS bit of the OPTION\_REG register.

When Timer0 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer0. Refer to **Section 20.0** "**Timer0 Module**" for additional information.

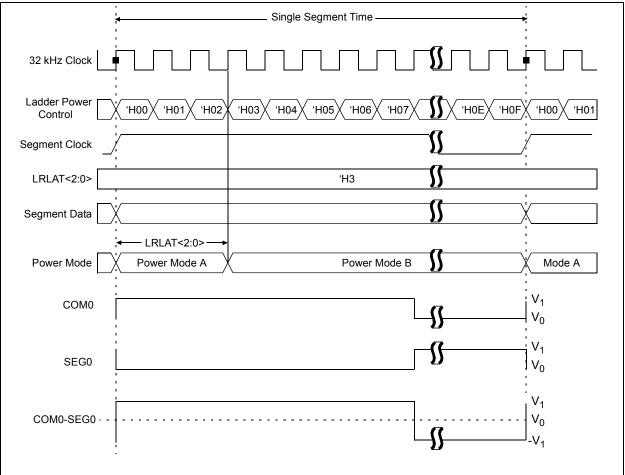

#### 27.5.3 AUTOMATIC POWER MODE SWITCHING

As an LCD segment is electrically only a capacitor, current is drawn only during the interval where the voltage is switching. To minimize total device current, the LCD internal reference ladder can be operated in a different power mode for the transition portion of the duration. This is controlled by the LCDRL Register (Register 27-7).

The LCDRL register allows switching between two power modes, designated 'A' and 'B'. 'A' Power mode is active for a programmable time, beginning at the time when the LCD segments transition. 'B' Power mode is the remaining time before the segments or commons change again. The LRLAT<2:0> bits select how long, if any, that the 'A' Power mode is active. Refer to Figure 27-4.

To implement this, the 5-bit prescaler used to divide the 32 kHz clock down to the LCD controller's 1 kHz base rate is used to select the power mode.

#### FIGURE 27-4: LCD INTERNAL REFERENCE LADDER POWER MODE SWITCHING DIAGRAM – TYPE A

## PIC16(L)F1946/47