Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 54                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1947-i-mr |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Peripheral Features (Continued)**

- Two Master Synchronous Serial Ports (MSSPs) with SPI and I<sup>2</sup>C with:

- 7-bit address masking

- SMBus/PMBus™ compatibility

- Auto-wake-up on start

- Two Enhanced Universal Synchronous:

- Asynchronous Receiver Transmitters (EUSARTs)

- RS-232, RS-485 and LIN compatible

- Auto-Baud Detect

- SR Latch (555 Timer):

- Multiple Set/Reset input options

- Emulates 555 Timer applications

- Three Comparators:

- Rail-to-rail inputs/outputs

- Power mode control

- Software enable hysteresis

- Voltage Reference Module:

- Fixed Voltage Reference (FVR) with 1.024V, 2.048V and 4.096V output levels

- 5-bit rail-to-rail resistive DAC with positive and negative reference selection

## PIC16(L)F193X/194X Family Types

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data EEPROM<br>(bytes) | Data SRAM<br>(bytes) | I/OS <sup>(2)</sup> | 10-bit ADC (ch) | CapSense (ch) | Comparators | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> C/SPI) | ECCP | ССР | LCD (Com/Seg/Total)    | Debug <sup>(1)</sup> | ХГР |

|---------------|------------------|---------------------------------|------------------------|----------------------|---------------------|-----------------|---------------|-------------|----------------------|--------|-----------------------------|------|-----|------------------------|----------------------|-----|

| PIC16(L)F1933 | (1)              | 4096                            | 256                    | 256                  | 25                  | 11              | 8             | 2           | 4/1                  | 1      | 1                           | 3    | 2   | 4/16/60 <sup>(3)</sup> | I/H                  | Y   |

| PIC16(L)F1934 | (2)              | 4096                            | 256                    | 256                  | 36                  | 14              | 16            | 2           | 4/1                  | 1      | 1                           | 3    | 2   | 4/24/96                | I/H                  | Y   |

| PIC16(L)F1936 | (2)              | 8192                            | 256                    | 512                  | 25                  | 11              | 8             | 2           | 4/1                  | 1      | 1                           | 3    | 2   | 4/16/60 <sup>(3)</sup> | I/H                  | Y   |

| PIC16(L)F1937 | (2)              | 8192                            | 256                    | 512                  | 36                  | 14              | 16            | 2           | 4/1                  | 1      | 1                           | 3    | 2   | 4/24/96                | I/H                  | Υ   |

| PIC16(L)F1938 | (3)              | 16384                           | 256                    | 1024                 | 25                  | 11              | 8             | 2           | 4/1                  | 1      | 1                           | 3    | 2   | 4/16/60 <sup>(3)</sup> | I/H                  | Y   |

| PIC16(L)F1939 | (3)              | 16384                           | 256                    | 1024                 | 36                  | 14              | 16            | 2           | 4/1                  | 1      | 1                           | 3    | 2   | 4/24/96                | I/H                  | Y   |

| PIC16(L)F1946 | (4)              | 8192                            | 256                    | 512                  | 54                  | 17              | 17            | 3           | 4/1                  | 2      | 2                           | 3    | 2   | 4/46/184               | I                    | Y   |

| PIC16(L)F1947 | (4)              | 16384                           | 256                    | 1024                 | 54                  | 17              | 17            | 3           | 4/1                  | 2      | 2                           | 3    | 2   | 4/46/184               | Ι                    | Y   |

Note 1: I – Debugging, Integrated on Chip; H – Debugging, Requires Debug Header.

- **2:** One pin is input-only.

- **3:** COM3 and SEG15 share the same physical pin, therefore SEG15 is not available when using 1/4 multiplex displays.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS41575 PIC16(L)F1933 Data Sheet, 28-Pin Flash, 8-bit Microcontrollers.

- 2: DS41364 PIC16(L)F1934/6/7 Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers.

- 3: DS40001574 PIC16(L)F1938/9 Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers.

- 4: DS41414 PIC16(L)F1946/1947 Data Sheet, 64-Pin Flash, 8-bit Microcontrollers.

| Address                | Name    | Bit 7        | Bit 6                                                    | Bit 5          | Bit 4        | Bit 3        | Bit 2        | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|---------|--------------|----------------------------------------------------------|----------------|--------------|--------------|--------------|--------|--------|----------------------|---------------------------------|

| Bank 2                 |         |              |                                                          |                |              |              |              |        |        |                      |                                 |

| 100h <sup>(2)</sup>    | INDF0   |              | this location ical register)                             | uses contents  | s of FSR0H/F | SR0L to addr | ess data mer | nory   |        | xxxx xxxx            | xxxx xxxx                       |

| 101h <sup>(2)</sup>    | INDF1   |              | this location ical register)                             | uses contents  | s of FSR1H/F | SR1L to addr | ess data mer | mory   |        | xxxx xxxx            | xxxx xxxx                       |

| 102h <sup>(2)</sup>    | PCL     | Program Co   | ounter (PC) L                                            | east Significa | nt Byte      |              |              |        |        | 0000 0000            | 0000 0000                       |

| 103h <sup>(2)</sup>    | STATUS  | _            |                                                          | _              | TO           | PD           | Z            | DC     | С      | 1 1000               | q quuu                          |

| 104h <sup>(2)</sup>    | FSR0L   | Indirect Dat | Indirect Data Memory Address 0 Low Pointer 0             |                |              |              |              |        |        |                      | uuuu uuuu                       |

| 105h <sup>(2)</sup>    | FSR0H   | Indirect Dat | a Memory Ad                                              | ldress 0 High  | Pointer      |              |              |        |        | 0000 0000            | 0000 0000                       |

| 106h <sup>(2)</sup>    | FSR1L   | Indirect Dat | a Memory Ad                                              |                | 0000 0000    | uuuu uuuu    |              |        |        |                      |                                 |

| 107h <sup>(2)</sup>    | FSR1H   | Indirect Dat | ndirect Data Memory Address 1 High Pointer               |                |              |              |              |        |        |                      | 0000 0000                       |

| 108h <sup>(2)</sup>    | BSR     |              | BSR<4:0>                                                 |                |              |              |              |        |        | 0 0000               | 0 0000                          |

| 109h <sup>(2)</sup>    | WREG    | Working Re   | Working Register                                         |                |              |              |              |        |        | 0000 0000            | uuuu uuuu                       |

| 10Ah <sup>(1, 2)</sup> | PCLATH  |              | Write Buffer for the upper 7 bits of the Program Counter |                |              |              |              |        |        | -000 0000            | -000 0000                       |

| 10Bh <sup>(2)</sup>    | INTCON  | GIE          | PEIE                                                     | TMR0IE         | INTE         | IOCIE        | TMR0IF       | INTF   | IOCIF  | 0000 000x            | 0000 000u                       |

| 10Ch                   | LATA    | PORTA Da     | PORTA Data Latch                                         |                |              |              |              |        |        | xxxx xxxx            | uuuu uuuu                       |

| 10Dh                   | LATB    | PORTB Da     | PORTB Data Latch                                         |                |              |              |              |        |        |                      | uuuu uuuu                       |

| 10Eh                   | LATC    | PORTC Da     | PORTC Data Latch                                         |                |              |              |              |        |        |                      | uuuu uuuu                       |

| 10Fh                   | LATD    | PORTD Da     | ta Latch                                                 |                |              |              |              |        |        | xxxx xxxx            | uuuu uuuu                       |

| 110h                   | LATE    | PORTE Da     | ta Latch                                                 |                |              |              |              |        |        | xxxx xxxx            | uuuu uuuu                       |

| 111h                   | CM1CON0 | C10N         | C10UT                                                    | C10E           | C1POL        | _            | C1SP         | C1HYS  | C1SYNC | 0000 -100            | 0000 -100                       |

| 112h                   | CM1CON1 | C1INTP       | C1INTN                                                   | C1PCH1         | C1PCH0       | _            | _            | C1NC   | H<1:0> | 000000               | 000000                          |

| 113h                   | CM2CON0 | C2ON         | C2OUT                                                    | C2OE           | C2POL        | _            | C2SP         | C2HYS  | C2SYNC | 0000 -100            | 0000 -100                       |

| 114h                   | CM2CON1 | C2INTP       | C2INTN                                                   | C2PCH1         | C2PCH0       | _            | _            | C2NC   | H<1:0> | 000000               | 000000                          |

| 115h                   | CMOUT   |              |                                                          | _              | _            | _            | MC3OUT       | MC2OUT | MC1OUT | 000                  | 000                             |

| 116h                   | BORCON  | SBOREN       |                                                          | _              | _            | _            | _            | _      | BORRDY | 1 q                  | uu                              |

| 117h                   | FVRCON  | FVREN        | FVRRDY                                                   | TSEN           | TSRNG        | CDAFVR1      | CDAFVR0      | ADFV   | R<1:0> | 0q00 0000            | 0q00 0000                       |

| 118h                   | DACCON0 | DACEN        | DACLPS                                                   | DACOE          | _            | DACPS        | S<1:0>       | _      | DACNSS | 000- 00-0            | 000- 00-0                       |

| 119h                   | DACCON1 | _            | _                                                        | _              |              | D            | )ACR<4:0>    |        |        | 0 0000               | 0 0000                          |

| 11Ah                   | SRCON0  | SRLEN        | SRCLK2                                                   | SRCLK1         | SRCLK0       | SRQEN        | SRNQEN       | SRPS   | SRPR   | 0000 0000            | 0000 0000                       |

| 11Bh                   | SRCON1  | SRSPE        | SRSCKE                                                   | SRSC2E         | SRSC1E       | SRRPE        | SRRCKE       | SRRC2E | SRRC1E | 0000 0000            | 0000 0000                       |

| 11Ch                   | —       | Unimpleme    | nted                                                     |                |              |              |              |        |        | —                    | —                               |

| 11Dh                   | APFCON  | P3CSEL       | P3BSEL                                                   | P2DSEL         | P2CSEL       | P2BSEL       | CCP2SEL      | P1CSEL | P1BSEL | 0000 0000            | 0000 0000                       |

| 11Eh                   | CM3CON0 | C3ON         | C3OUT                                                    | C3OE           | C3POL        | _            | C3SP         | C3HYS  | C3SYNC | 0000 -100            | 0000 -100                       |

| 11Fh                   | CM3CON1 | C3INTP       | C3INTN                                                   | C3PCH1         | C3PCH0       | _            | _            | C3NC   | H<1:0> | 000000               | 000000                          |

## TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

**3:** Unimplemented, read as '1'.

## FIGURE 3-9: INDIRECT ADDRESSING

## 8.0 LOW DROPOUT (LDO) VOLTAGE REGULATOR

The PIC16F1946/47 has an internal Low Dropout Regulator (LDO) which provides operation above 3.6V. The LDO regulates a voltage for the internal device logic while permitting the VDD and I/O pins to operate at a higher voltage. There is no user enable/disable control available for the LDO, it is always active. The PIC16LF1946/47 operates at a maximum VDD of 3.6V and does not incorporate an LDO.

A device I/O pin may be configured as the LDO voltage output, identified as the VCAP pin. Although not required, an external low-ESR capacitor may be connected to the VCAP pin for additional regulator stability.

The VCAPEN bit of Configuration Words enables or disables the VCAP pin. Refer to Table 8-1.

## TABLE 8-1: VCAPEN SELECT BIT

| VCAPEN | Pin     |

|--------|---------|

| 0      | RF0     |

| 1      | No VCAP |

On power-up, the external capacitor will load the LDO voltage regulator. To prevent erroneous operation, the device is held in Reset while a constant current source charges the external capacitor. After the cap is fully charged, the device is released from Reset. For more information on the constant current rate, refer to the LDO Regulator Characteristics Table in **Section 30.0** "**Electrical Specifications**".

## TABLE 8-2: SUMMARY OF CONFIGURATION WORD WITH LDO

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 13:8 |         |         | LVP      | DEBUG    |          | BORV     | STVREN  | PLLEN   | 56                  |

| CONFIGZ | 7:0  | _       |         | _        | VCAPEN   | _        |          | WRT1    | WRT0    | 50                  |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by LDO.

## 9.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

FIGURE 9-1:

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction is executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

|                          |                  |              |                       |         | •••••           |                   |             |             |

|--------------------------|------------------|--------------|-----------------------|---------|-----------------|-------------------|-------------|-------------|

| OSC1 <sup>(1)</sup>      | Q1 Q2 Q3 Q4      | Q1 Q2 Q3  Q4 | Q1                    |         | Q1 Q2 Q3 Q4     | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4 |             |

| CLKOUT <sup>(2)</sup>    |                  |              | ,<br>,<br>,           | Tost(3) |                 |                   |             |             |

| Interrupt flag           |                  |              | /                     |         | Interrupt Laten | <sub>CY</sub> (4) |             |             |

| GIE bit<br>(INTCON reg.) | · <u>·</u>       |              | Processor in<br>Sleep | ''      |                 |                   |             |             |

| nstruction Flow<br>PC    |                  | ( PC + 1     | X PC                  | + 2     | X PC + 2        | ( PC + 2          | X 0004h     | X 0005h     |

| Instruction {<br>Fetched | Inst(PC) = Sleep | Inst(PC + 1) | 1<br>1<br>1           | 1       | Inst(PC + 2)    |                   | Inst(0004h) | Inst(0005h) |

| Instruction J            | Inst(PC - 1)     | Sleep        | 1<br>1                | 1       | Inst(PC + 1)    | Forced NOP        | Forced NOP  | Inst(0004h) |

2: CLKOUT is not available in XT, HS, or LP Oscillator modes, but shown here for timing reference.

3: TOST = 1024 TOSC (drawing not to scale). This delay applies only to XT, HS or LP Oscillator modes.

WAKE-UP FROM SLEEP THROUGH INTERRUPT

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

## TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name   | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|--------|---------|--------|--------|--------|------------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE   | TMR0IE | INTE   | IOCIE      | TMR0IF | INTF   | IOCIF  | 90                  |

| IOCBF  | IOCBF7  | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3     | IOCBF2 | IOCBF1 | IOCBF0 | 148                 |

| IOCBN  | IOCBN7  | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3     | IOCBN2 | IOCBN1 | IOCBN0 | 148                 |

| IOCBP  | IOCBP7  | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3     | IOCBP2 | IOCBP1 | IOCBP0 | 148                 |

| PIE1   | TMR1GIE | ADIE   | RCIE   | TXIE   | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 91                  |

| PIE2   | OSFIE   | C2IE   | C1IE   | EEIE   | BCLIE      | LCDIE  | C3IE   | CCP2IE | 92                  |

| PIE3   | —       | CCP5IE | CCP4IE | CCP3IE | TMR6IE     | _      | TMR4IE | _      | 93                  |

| PIE4   | —       | _      | RC2IE  | TX2IE  | _          | _      | BCL2IE | SSP2IE | 94                  |

| PIR1   | TMR1GIF | ADIF   | RCIF   | TXIF   | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 95                  |

| PIR2   | OSFIF   | C2IF   | C1IF   | EEIF   | BCLIF      | LCDIF  | C3IF   | CCP2IF | 96                  |

| PIR3   | _       | CCP5IF | CCP4IF | CCP3IF | TMR6IF     | _      | TMR4IF | _      | 97                  |

| PIR4   | _       | —      | RC2IF  | TX2IF  | _          | _      | BCL2IF | SSP2IF | 98                  |

| STATUS | _       | _      | _      | TO     | PD         | Z      | DC     | С      | 22                  |

| WDTCON |         |        |        |        | WDTPS<4:0> |        |        | SWDTEN | 104                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

© 2010-2016 Microchip Technology Inc.

## **10.1** Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 30.0 "Electrical Specifications**" for the LFINTOSC tolerances.

## 10.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

| TABLE 10-1: WDI OPERATING MODES | TABLE 10-1: | WDT OPERATING MODES |

|---------------------------------|-------------|---------------------|

|---------------------------------|-------------|---------------------|

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 1.0       | 37     | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | ^              | Disabled    |

| 00        | Х      | Х              | Disabled    |

#### 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

## 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 10-2 for more information.

## 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 5.0** "Oscillator **Module (With Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. See **Section 3.0** "**Memory Organization**" and STATUS register (**Register 3-1**) for more information.

| TABLE 10-2: WDT CLEARING CONDITIONS |

|-------------------------------------|

|-------------------------------------|

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                           |                              |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |

| CLRWDT Command                                           | Cleared                      |

| Oscillator Fail Detected                                 |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |

## 12.2 Register Definitions: Alternate Pin Function Control

| R/W-0/0          | R/W-0/0      | R/W-0/0                            | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0      | R/W-0/0 |

|------------------|--------------|------------------------------------|----------------|----------------|------------------|--------------|---------|

| P3CSEL           | P3BSEL       | P2DSEL                             | P2CSEL         | P2BSEL         | CCP2SEL          | P1CSEL       | P1BSEL  |

| bit 7            | •            |                                    | •              | •              |                  |              | bit (   |

| Legend:          |              |                                    |                |                |                  |              |         |

| R = Readable     | bit          | W = Writable                       | bit            | U = Unimpler   | nented bit, read | as '0'       |         |

| u = bit is unch  | anged        | x = Bit is unki                    | -n/n = Value a | at POR and BOI | R/Value at all c | other Resets |         |

| '1' = Bit is set | 0            | '0' = Bit is cle                   | ared           |                |                  |              |         |

|                  |              |                                    |                |                |                  |              |         |

| bit 7            |              | P3 PWM C Ou                        | •              | tion bit       |                  |              |         |

|                  |              | ction is on RE3<br>ction is on RD3 |                |                |                  |              |         |

| bit 6            |              | P3 PWM B Ou                        |                | tion bit       |                  |              |         |

|                  |              | ction is on RE4                    | •              |                |                  |              |         |

|                  | 1 = P3B fund | ction is on RD4                    | /P3B/SEG4      |                |                  |              |         |

| bit 5            | P2DSEL: CC   | P2 PWM D Ou                        | tput Pin Selec | tion bit       |                  |              |         |

|                  |              | ction is on RE0                    |                |                |                  |              |         |

| hit 1            |              | ction is on RD0                    |                | tion hit       |                  |              |         |

| bit 4            |              | P2 PWM C Ou<br>ction is on RE1     | •              |                |                  |              |         |

|                  |              | ction is on RD1                    |                |                |                  |              |         |

| bit 3            |              | P2 PWM B Ou                        |                | tion bit       |                  |              |         |

|                  |              | tion is on RE2                     | •              |                |                  |              |         |

|                  | 1 = P2B fund | ction is on RD2                    | /P2B/SEG2      |                |                  |              |         |

| bit 2            | CCP2SEL: C   | CP2 Input/Out                      | put Pin Select | ion bit        |                  |              |         |

|                  |              | 2A function is o                   |                |                | G32              |              |         |

|                  |              | 2A function is o                   |                |                |                  |              |         |

| bit 1            |              | P1 PWM C Ou                        | •              | tion bit       |                  |              |         |

|                  |              | ction is on RE5<br>ction is on RD5 |                |                |                  |              |         |

| bit 0            |              |                                    |                | tion hit       |                  |              |         |

|                  |              | P1 PWM B Ou<br>tion is on RE6      | •              |                |                  |              |         |

|                  |              |                                    |                |                |                  |              |         |

## REGISTER 12-1: APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER

| Name    | Bit 7  | Bit 6           | Bit 5  | Bit 4    | Bit 3      | Bit 2             | Bit 1      | Bit 0  | Register on<br>Page |

|---------|--------|-----------------|--------|----------|------------|-------------------|------------|--------|---------------------|

| ADCON0  | _      |                 |        | CHS<4:0> |            |                   | GO/DONE    | ADON   | 161                 |

| ANSELG  | —      | -               | _      | ANSG4    | ANSG3      | ANSG2             | ANSG1      | _      | 144                 |

| CCPxCON | PxM<   | 1:0> <b>(1)</b> | DCxB   | <1:0>    |            | CCPx              | /<3:0>     |        | 227                 |

| CMOUT   | —      | _               | _      | _        | _          | MC3OUT            | MC2OUT     | MC1OUT | 179                 |

| CM1CON1 | C1INTP | C1INTN          | C1PCH1 | C1PCH0   |            | —                 | C1NCH<1:0> |        | 179                 |

| CM2CON1 | C2INTP | C2INTN          | C2PCH1 | C2PCH0   | _          | —                 | C2NCH<1:0> |        | 179                 |

| CPSCON0 | CPSON  | CPSRM           | _      | _        | CPSRN      | IG<1:0>           | CPSOUT     | TOXCS  | 322                 |

| CPSCON1 | —      | _               | _      | _        | CPSCH<3:0> |                   |            | 323    |                     |

| LATG    | —      | _               | —      | LATG4    | LATG3      | LATG2             | LATG1      | LATG0  | 143                 |

| LCDCON  | LCDEN  | SLPEN           | WERR   | —        | CS<        | CS<1:0> LMUX<1:0> |            | 326    |                     |

| LCDSE3  | SE31   | SE30            | SE29   | SE28     | SE27       | SE26              | SE25       | SE24   | 330                 |

| LCDSE5  | —      | _               | SE45   | SE44     | SE43       | SE42              | SE41       | SE40   | 330                 |

| PORTG   | —      | _               | RG5    | RG4      | RG3        | RG2               | RG1        | RG0    | 143                 |

| TRISG   | —      |                 | TRISG5 | TRISG4   | TRISG3     | TRISG2            | TRISG1     | TRISG0 | 143                 |

| WPUG    | —      | _               | WPUG5  | _        | _          | —                 | —          | —      | 144                 |

| TABLE 12-17: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTG |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTG. **Note 1:** Applies to ECCP modules only.

## 13.0 INTERRUPT-ON-CHANGE

The PORTB pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTB pin, or combination of PORTB pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- · Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

## 13.1 Enabling the Module

To allow individual PORTB pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 13.2 Individual Pin Configuration

For each PORTB pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCBPx bit of the IOCBP register is set. To enable a pin to detect a falling edge, the associated IOCBNx bit of the IOCBN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCBPx bit and the IOCBNx bit of the IOCBP and IOCBN registers, respectively.

## 13.3 Interrupt Flags

The IOCBFx bits located in the IOCBF register are status flags that correspond to the interrupt-on-change pins of PORTB. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCBFx bits.

## 13.4 Clearing Interrupt Flags

The individual status flags, (IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

## EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCBF register will be updated prior to the first instruction executed out of Sleep.

## 18.11 Register Definitions: Comparator Control

| R/W-0/0          | R-0/0                                                                                               | R/W-0/0                                                 | R/W-0/0    | U-0          | R/W-1/1          | R/W-0/0       | R/W-0/0      |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------|--------------|------------------|---------------|--------------|--|--|--|--|--|

| CxON             | CxOUT                                                                                               | CxOE                                                    | CxPOL      | —            | CxSP             | CxHYS         | CxSYNC       |  |  |  |  |  |

| bit 7            |                                                                                                     |                                                         |            | _            | •                |               | bit C        |  |  |  |  |  |

| Legend:          |                                                                                                     |                                                         |            |              |                  |               |              |  |  |  |  |  |

| R = Readable     | e bit                                                                                               | W = Writable                                            | bit        | U = Unimpler | mented bit, read | d as '0'      |              |  |  |  |  |  |

| u = Bit is uncl  | nanged                                                                                              | x = Bit is unki                                         | nown       | •            | at POR and BC    |               | other Resets |  |  |  |  |  |

| '1' = Bit is set | ·                                                                                                   | '0' = Bit is cle                                        | ared       |              |                  |               |              |  |  |  |  |  |

|                  |                                                                                                     |                                                         |            |              |                  |               |              |  |  |  |  |  |

| bit 7            | CxON: Comp                                                                                          | parator Enable                                          | bit        |              |                  |               |              |  |  |  |  |  |

|                  |                                                                                                     | 1 = Comparator is enabled                               |            |              |                  |               |              |  |  |  |  |  |

|                  |                                                                                                     | 0 = Comparator is disabled and consumes no active power |            |              |                  |               |              |  |  |  |  |  |

| bit 6            | CxOUT: Comparator Output bit                                                                        |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | If CxPOL = 1 (inverted polarity):<br>1 = CxVP < CxVN                                                |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | 0 = CxVP > CxVN                                                                                     |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | $\frac{ \text{f CxPOL} = 0 \text{ (non-inverted polarity)}:}{1 - C + 2}$                            |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | 1 = CxVP > CxVN $0 = CxVP < CxVN$                                                                   |                                                         |            |              |                  |               |              |  |  |  |  |  |

| bit 5            |                                                                                                     | barator Output                                          | Enable bit |              |                  |               |              |  |  |  |  |  |

|                  | 1 = CxOUT is present on the CxOUT pin. Requires that the associated TRIS bit be cleared to actually |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | drive the pin. Not affected by CxON.                                                                |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | 0 = CxOUT is internal only                                                                          |                                                         |            |              |                  |               |              |  |  |  |  |  |

| bit 4            | CxPOL: Comparator Output Polarity Select bit                                                        |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | <ol> <li>Comparator output is inverted</li> <li>Comparator output is not inverted</li> </ol>        |                                                         |            |              |                  |               |              |  |  |  |  |  |

| bit 3            | •                                                                                                   | •                                                       |            |              |                  |               |              |  |  |  |  |  |

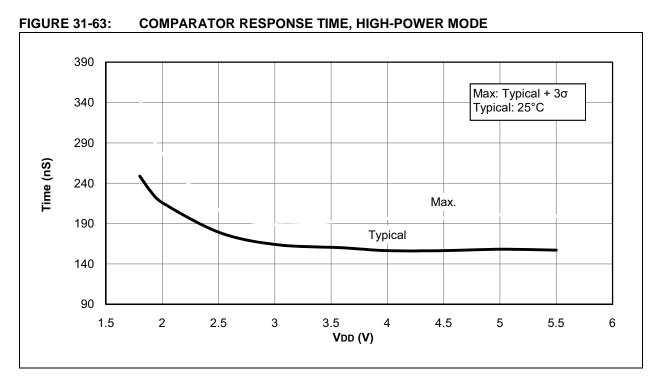

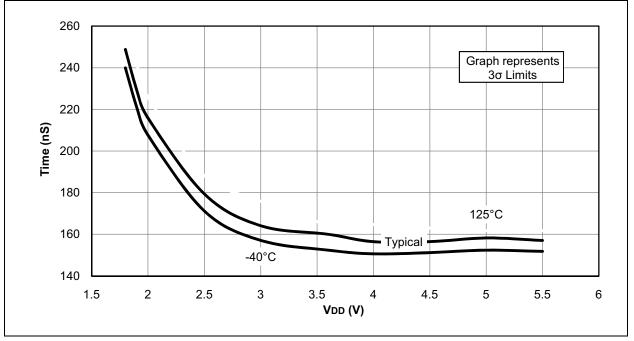

| bit 2            | Unimplemented: Read as '0'<br>CxSP: Comparator Speed/Power Select bit                               |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | 1 = Comparator operates in normal power, higher speed mode                                          |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | 0 = Comparator operates in low-power, low-speed mode                                                |                                                         |            |              |                  |               |              |  |  |  |  |  |

| bit 1            | CxHYS: Comparator Hysteresis Enable bit                                                             |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | 1 = Comparator hysteresis enabled                                                                   |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  | -                                                                                                   | ator hysteresis                                         |            |              |                  |               |              |  |  |  |  |  |

| bit 0            |                                                                                                     | CxSYNC: Comparator Output Synchronous Mode bit          |            |              |                  |               |              |  |  |  |  |  |

|                  | 1 = Comparator output to Timer1 and I/O pin is synchronous to changes on Timer1 clock source.       |                                                         |            |              |                  |               |              |  |  |  |  |  |

|                  |                                                                                                     | ator output to T<br>pdated on the                       |            |              |                  | ges on Timer1 | clock source |  |  |  |  |  |

## REGISTER 18-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| REGISTER         |                                                                                                                                                                | -                                                                       | CHCONIRO        |                 |                  |                |              |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|-----------------|------------------|----------------|--------------|--|--|--|--|

| R/W-0/0          | R/W-0/0                                                                                                                                                        | R/W-0/0                                                                 | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |  |  |

| SRSPE            | SRSCKE                                                                                                                                                         | SRSC2E                                                                  | SRSC1E          | SRRPE           | SRRCKE           | SRRC2E         | SRRC1E       |  |  |  |  |

| bit 7            |                                                                                                                                                                |                                                                         |                 |                 |                  |                | bit 0        |  |  |  |  |

| • • • • •        |                                                                                                                                                                |                                                                         |                 |                 |                  |                |              |  |  |  |  |

| Legend:          |                                                                                                                                                                |                                                                         |                 |                 |                  |                |              |  |  |  |  |

| R = Readable     |                                                                                                                                                                | W = Writable                                                            |                 | •               | mented bit, rea  |                |              |  |  |  |  |

| u = Bit is unc   | •                                                                                                                                                              | x = Bit is unki                                                         |                 | -n/n = Value    | at POR and BC    | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                                | '0' = Bit is cle                                                        | ared            |                 |                  |                |              |  |  |  |  |

| bit 7            | SRSPE: SR I                                                                                                                                                    | Latch Peripher                                                          | al Set Enable b | bit             |                  |                |              |  |  |  |  |

|                  |                                                                                                                                                                | n is set when th                                                        |                 |                 |                  |                |              |  |  |  |  |

|                  |                                                                                                                                                                | nas no effect or                                                        |                 |                 | h                |                |              |  |  |  |  |

| bit 6            | SRSCKE: SR Latch Set Clock Enable bit                                                                                                                          |                                                                         |                 |                 |                  |                |              |  |  |  |  |

|                  | 1 = Set input of SR Latch is pulsed with SRCLK                                                                                                                 |                                                                         |                 |                 |                  |                |              |  |  |  |  |

|                  | 0 = SRCLK                                                                                                                                                      | has no effect of                                                        | n the set input | of the SR Latc  | h                |                |              |  |  |  |  |

| bit 5            | SRSC2E: SR Latch C2 Set Enable bit                                                                                                                             |                                                                         |                 |                 |                  |                |              |  |  |  |  |

|                  | 1 = SR Latch is set when the C2 Comparator output is high                                                                                                      |                                                                         |                 |                 |                  |                |              |  |  |  |  |

|                  | •                                                                                                                                                              | 0 = C2 Comparator output has no effect on the set input of the SR Latch |                 |                 |                  |                |              |  |  |  |  |

| bit 4            | SRSC1E: SR Latch C1 Set Enable bit                                                                                                                             |                                                                         |                 |                 |                  |                |              |  |  |  |  |

|                  | <ul> <li>1 = SR Latch is set when the C1 Comparator output is high</li> <li>0 = C1 Comparator output has no effect on the set input of the SR Latch</li> </ul> |                                                                         |                 |                 |                  |                |              |  |  |  |  |

| bit 3            | •                                                                                                                                                              | SRRPE: SR Latch Peripheral Reset Enable bit                             |                 |                 |                  |                |              |  |  |  |  |

| bit 5            | 1 = SR Latch is reset when the SRI pin is high                                                                                                                 |                                                                         |                 |                 |                  |                |              |  |  |  |  |

|                  | 0 = SRI pin has no effect on the Reset input of the SR Latch                                                                                                   |                                                                         |                 |                 |                  |                |              |  |  |  |  |

| bit 2            | SRRCKE: SR Latch Reset Clock Enable bit                                                                                                                        |                                                                         |                 |                 |                  |                |              |  |  |  |  |

|                  | 1 = Reset in                                                                                                                                                   | 1 = Reset input of SR Latch is pulsed with SRCLK                        |                 |                 |                  |                |              |  |  |  |  |

|                  | 0 = SRCLK                                                                                                                                                      | 0 = SRCLK has no effect on the Reset input of the SR Latch              |                 |                 |                  |                |              |  |  |  |  |

| bit 1            | SRRC2E: SR                                                                                                                                                     | R Latch C2 Res                                                          | et Enable bit   |                 |                  |                |              |  |  |  |  |

|                  | 1 = SR Latch is reset when the C2 Comparator output is high                                                                                                    |                                                                         |                 |                 |                  |                |              |  |  |  |  |

|                  | •                                                                                                                                                              | •                                                                       |                 | n the Reset inp | out of the SR La | atch           |              |  |  |  |  |

| bit 0            |                                                                                                                                                                | R Latch C1 Res                                                          |                 |                 |                  |                |              |  |  |  |  |

|                  |                                                                                                                                                                | n is reset when                                                         |                 |                 |                  | atab           |              |  |  |  |  |

|                  | 0 = C1 Complexity                                                                                                                                              | parator output                                                          | nas no effect o | n the Reset inp | out of the SR La | atch           |              |  |  |  |  |

## REGISTER 19-3: SRCON1: SR LATCH CONTROL 1 REGISTER

## TABLE 19-2: SUMMARY OF REGISTERS ASSOCIATED WITH SR LATCH MODULE

| Name   | Bit 7   | Bit 6      | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|--------|---------|------------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELF | ANSELF7 | ANSELF6    | ANSELF5 | ANSELF4 | ANSELF3 | ANSELF2 | ANSELF1 | ANSELF0 | 126                 |

| SRCON0 | SRLEN   | SRCLK<2:0> |         |         | SRQEN   | SRNQEN  | SRPS    | SRPR    | 184                 |

| SRCON1 | SRSPE   | SRSCKE     | SRSC2E  | SRSC1E  | SRRPE   | SRRCKE  | SRRC2E  | SRRC1E  | 185                 |

| TRISB  | TRISB7  | TRISB6     | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  | 125                 |

| TRISF  | TRISF7  | TRISF6     | TRISF5  | TRISF4  | TRISF3  | TRISF2  | TRISF1  | TRISF0  | 125                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are unused by the SR Latch module.

| R/W-0/u         | R/W-0/u                                                                                                                                                                            | R/W-0/u                                                                                                                                                      | R/W-0/u        | R/W/HC-0/u      | R-x/x            | R/W-0/u        | R/W-0/u      |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|------------------|----------------|--------------|--|--|--|--|--|

| TMR1GE          | T1GPOL                                                                                                                                                                             | T1GTM                                                                                                                                                        | T1GSPM         | T1GGO/<br>DONE  | T1GVAL           | T1GS           | 6<1:0>       |  |  |  |  |  |

| bit 7           |                                                                                                                                                                                    |                                                                                                                                                              |                |                 |                  |                | bit (        |  |  |  |  |  |

|                 |                                                                                                                                                                                    |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

| Legend:         |                                                                                                                                                                                    |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

| R = Readable    | bit                                                                                                                                                                                | W = Writable                                                                                                                                                 | bit            | U = Unimplen    | nented bit, read | d as '0'       |              |  |  |  |  |  |

| u = Bit is unch | anged                                                                                                                                                                              | x = Bit is unkr                                                                                                                                              | nown           | -n/n = Value a  | at POR and BC    | R/Value at all | other Resets |  |  |  |  |  |

| 1' = Bit is set |                                                                                                                                                                                    | '0' = Bit is cle                                                                                                                                             | ared           | HC = Bit is cle | eared by hardw   | /are           |              |  |  |  |  |  |

|                 |                                                                                                                                                                                    |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

| bit 7           | TMR1GE: Timer1 Gate Enable bit                                                                                                                                                     |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

|                 |                                                                                                                                                                                    | $\frac{\text{If TMR1ON} = 0}{\text{This bit is imposed}}$                                                                                                    |                |                 |                  |                |              |  |  |  |  |  |

|                 | This bit is ignored<br>If TMR1ON = 1:                                                                                                                                              |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

|                 | 1 = Timer1 counting is controlled by the Timer1 gate function                                                                                                                      |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

|                 | 0 = Timer1 c                                                                                                                                                                       | = Timer1 counts regardless of Timer1 gate function                                                                                                           |                |                 |                  |                |              |  |  |  |  |  |

| bit 6           | T1GPOL: Timer1 Gate Polarity bit                                                                                                                                                   |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

|                 | •                                                                                                                                                                                  | <ul> <li>1 = Timer1 gate is active-high (Timer1 counts when gate is high)</li> <li>0 = Timer1 gate is active-low (Timer1 counts when gate is low)</li> </ul> |                |                 |                  |                |              |  |  |  |  |  |

| bit 5           | <b>T1GTM:</b> Timer1 Gate Toggle Mode bit                                                                                                                                          |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

|                 | 1 = Timer1 Gate Toggle mode is enabled                                                                                                                                             |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

|                 | <ul> <li>Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared</li> <li>Timer1 gate flip-flop toggles on every rising edge.</li> </ul>                               |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

| bit 4           | •                                                                                                                                                                                  |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

| UIL 4           | <b>T1GSPM:</b> Timer1 Gate Single-Pulse Mode bit<br>1 = Timer1 Gate Single-Pulse mode is enabled and is controlling Timer1 gate                                                    |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

|                 | <ul> <li>a Timer 1 Gate Single-Pulse mode is enabled and is controlling Timer 1 gate</li> <li>a Timer 1 Gate Single-Pulse mode is disabled</li> </ul>                              |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

| bit 3           | T1GGO/DONE: Timer1 Gate Single-Pulse Acquisition Status bit                                                                                                                        |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

|                 | <ul> <li>1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge</li> <li>0 = Timer1 gate single-pulse acquisition has completed or has not been started</li> </ul> |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

|                 | -                                                                                                                                                                                  | •                                                                                                                                                            |                | as completed o  | or has not beer  | started        |              |  |  |  |  |  |

| bit 2           | T1GVAL: Timer1 Gate Current State bit                                                                                                                                              |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

|                 | Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L.<br>Unaffected by Timer1 Gate Enable (TMR1GE).                                                |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

| bit 1-0         |                                                                                                                                                                                    | : Timer1 Gate                                                                                                                                                | •              | ,               |                  |                |              |  |  |  |  |  |

|                 | 11 = Compar                                                                                                                                                                        | ator 2 optional                                                                                                                                              | ly synchronize | d output (sync_ | C2OUT)           |                |              |  |  |  |  |  |

|                 |                                                                                                                                                                                    |                                                                                                                                                              |                | d output (sync  | C1OUT)           |                |              |  |  |  |  |  |

|                 | <ul> <li>10 = Comparator 1 optionally synchronized output (sync_C1OUT)</li> <li>01 = Timer0 overflow output</li> <li>00 = Timer1 gate pin</li> </ul>                               |                                                                                                                                                              |                |                 |                  |                |              |  |  |  |  |  |

## REGISTER 21-2: T1GCON: TIMER1 GATE CONTROL REGISTER

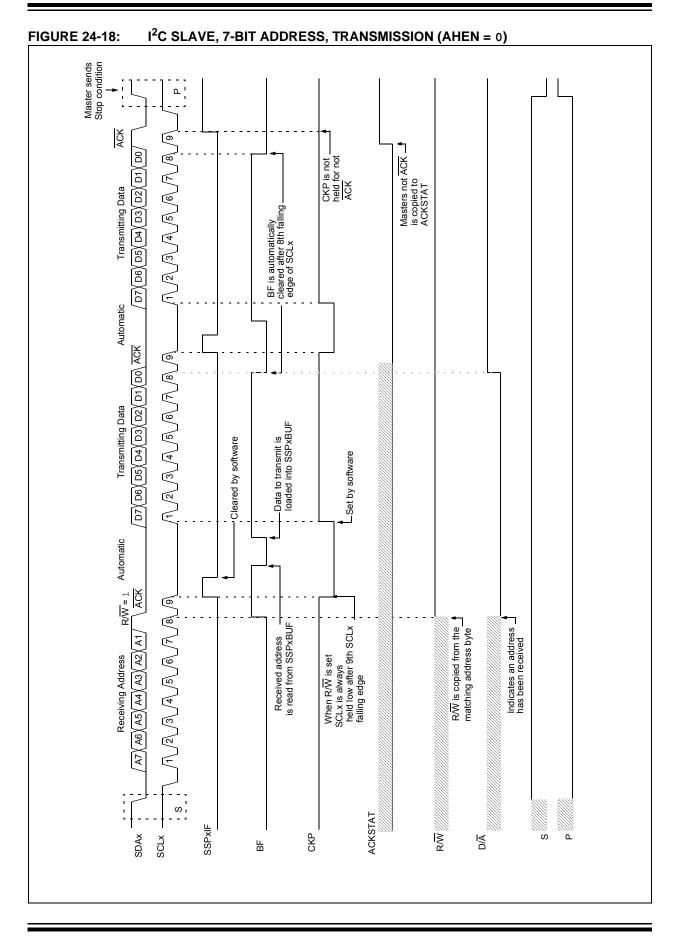

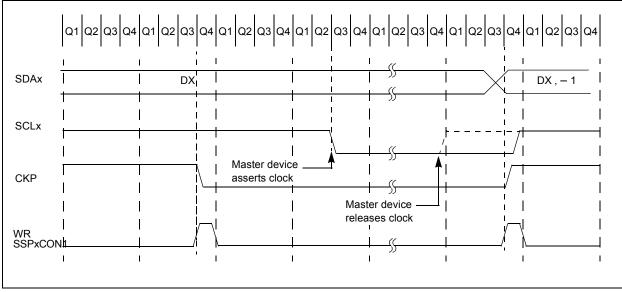

## 24.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCLx pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDAx line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDAx line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allows the user to set the  $\overrightarrow{ACK}$  value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

An ACK will not be sent by the slave when an overflow condition is detected. An overflow condition is defined by either the SSPxSTAT register bit BF being set, or by the SSPxCON1 register bit SSPOV being set.

When the module is addressed, after the eighth falling edge of SCLx on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

## 24.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSPx Slave mode operates in one of four modes selected in the SSPM bits of SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operated the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

## 24.5.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 24-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSPx Mask register (Register 24-5) affects the address matching process. See **Section 24.5.9 "SSPx Mask Register**" for more information.

## 24.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

## 24.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.