Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

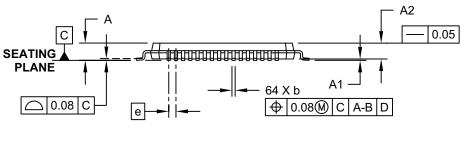

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1946-e-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

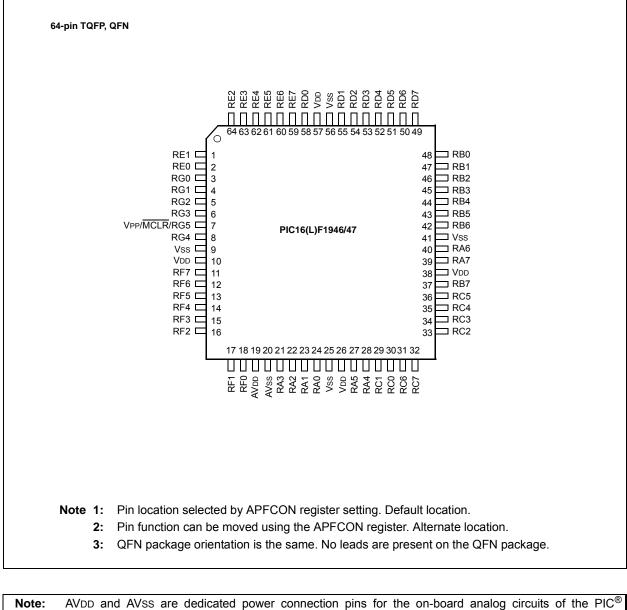

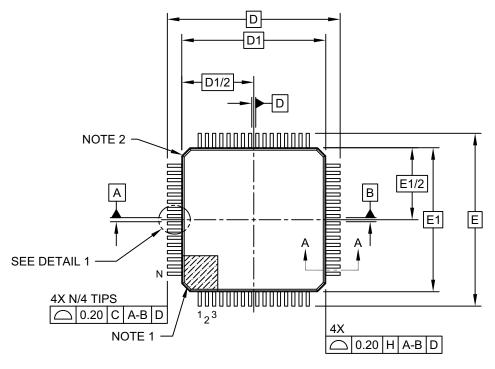

## Pin Diagram – 64-Pin TQFP/QFN (PIC16(L)F1946/47)

**Note:** AVDD and AVSS are dedicated power connection pins for the on-board analog circuits of the PIC<sup>®</sup> microcontroller. The separate power pins help eliminate digital switching noise interference with the analog circuitry inside the device, especially on larger devices with more I/O pins and larger switching currents on the VDD/VSS pins. Customers typically connect these to the appropriate VDD or VSS connections on the PCB, unless there is a lot of noise on the external power rails. In those situations, they will add additional noise filtering components (like capacitors) on the AVDD/AVSS pins to help ensure good solid supply to the analog modules inside the device.

| TABLE 1-2: | PIC16(L)F1946/47 PINOUT DESCRIPTION (CONTINUED) |

|------------|-------------------------------------------------|

|------------|-------------------------------------------------|

| TABLE 1-2. FIC TO(L)F 1940/47 FINOU                 |          |                  | -              | · · · · ·                                                                                          |  |  |  |

|-----------------------------------------------------|----------|------------------|----------------|----------------------------------------------------------------------------------------------------|--|--|--|

| Name                                                | Function | Input<br>Type    | Output<br>Type | Description                                                                                        |  |  |  |

| RB2/SEG9                                            | RB2      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |  |  |  |

|                                                     | SEG9     |                  | AN             | LCD Analog output.                                                                                 |  |  |  |

| RB3/SEG10                                           | RB3      | TTL              | CMOS           | 6 General purpose I/O. Individually controlled interrupt-on-cha<br>Individually enabled pull-up.   |  |  |  |

|                                                     | SEG10    |                  | AN             | LCD Analog output.                                                                                 |  |  |  |

| RB4/SEG11                                           | RB4      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |  |  |  |

|                                                     | SEG11    | _                | AN             | LCD Analog output.                                                                                 |  |  |  |

| RB5/T1G/SEG29                                       | RB5      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |  |  |  |

|                                                     | T1G      | ST               | —              | Timer1 Gate input.                                                                                 |  |  |  |

|                                                     | SEG29    | —                | AN             | LCD Analog output.                                                                                 |  |  |  |

| RB6/ICSPCLK/ICDCLK/SEG38                            | RB6      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |  |  |  |

|                                                     | ICSPCLK  | ST               | _              | Serial Programming Clock.                                                                          |  |  |  |

|                                                     | ICDCLK   | ST               | —              | In-Circuit Debug Clock.                                                                            |  |  |  |

|                                                     | SEG38    | _                | AN             | LCD Analog output.                                                                                 |  |  |  |

| RB7/ICSPDAT/ICDDAT/SEG39                            | RB7      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |  |  |  |

|                                                     | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                                                                                    |  |  |  |

|                                                     | ICDDAT   | ST               | CMOS           | In-Circuit Data I/O.                                                                               |  |  |  |

|                                                     | SEG39    |                  | AN             | LCD Analog output.                                                                                 |  |  |  |

| RC0/T1OSO/T1CKI/SEG40                               | RC0      | ST               | CMOS           | General purpose I/O.                                                                               |  |  |  |

|                                                     | T10S0    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                      |  |  |  |

|                                                     | T1CKI    | ST               | —              | Timer1 clock input.                                                                                |  |  |  |

|                                                     | SEG40    | —                | AN             | LCD Analog output.                                                                                 |  |  |  |

| RC1/T1OSI/P2A <sup>(1)</sup> /CCP2 <sup>(1)</sup> / | RC1      | ST               | CMOS           | General purpose I/O.                                                                               |  |  |  |

| SEG32                                               | T10SI    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                      |  |  |  |

|                                                     | P2A      | —                | CMOS           | PWM output.                                                                                        |  |  |  |

|                                                     | CCP2     | ST               | CMOS           | Capture/Compare/PWM.                                                                               |  |  |  |

|                                                     | SEG32    | —                | AN             | LCD Analog output.                                                                                 |  |  |  |

| RC2/CCP1/P1A/SEG13                                  | RC2      | ST               | CMOS           | General purpose I/O.                                                                               |  |  |  |

|                                                     | CCP1     | ST               | CMOS           | Capture/Compare/PWM.                                                                               |  |  |  |

|                                                     | P1A      | _                | CMOS           | PWM output.                                                                                        |  |  |  |

|                                                     | SEG13    | —                | AN             | LCD Analog output.                                                                                 |  |  |  |

| RC3/SCK1/SCL1/SEG17                                 | RC3      | ST               | CMOS           | General purpose I/O.                                                                               |  |  |  |

|                                                     | SCK1     | ST               | CMOS           | SPI clock.                                                                                         |  |  |  |

|                                                     | SCL1     | I <sup>2</sup> C | OD             | I <sup>2</sup> C clock.                                                                            |  |  |  |

|                                                     | SEG17    | —                | AN             | LCD Analog output.                                                                                 |  |  |  |

| RC4/SDI1/SDA1/SEG16                                 | RC4      | ST               | CMOS           | General purpose I/O.                                                                               |  |  |  |

|                                                     | SDI1     | ST               |                | SPI data input.                                                                                    |  |  |  |

|                                                     | SDA1     | I <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output.                                                                |  |  |  |

| legend: AN = Analog input or                        | SEG16    | —                | AN             | LCD Analog output.                                                                                 |  |  |  |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open-drain

= Schmitt Trigger input with  $I^2C$

Note 1: Pin function is selectable via the APFCON register.

| Name                                               | Function | Input<br>Type | Output<br>Type | Description                             |  |

|----------------------------------------------------|----------|---------------|----------------|-----------------------------------------|--|

| RE1/P2C <sup>(1)</sup> /VLCD2                      | RE1      | ST            | CMOS           | General purpose I/O.                    |  |

|                                                    | P2C      |               | CMOS           | PWM output.                             |  |

|                                                    | VLCD2    | AN            | —              | LCD analog input.                       |  |

| RE2/P2B <sup>(1)</sup> /VLCD3                      | RE2      | ST            | CMOS           | General purpose I/O.                    |  |

|                                                    | P2B      |               | CMOS           | PWM output.                             |  |

|                                                    | VLCD3    | AN            |                | LCD analog input.                       |  |

| RE3/P3C <sup>(1)</sup> /COM0                       | RE3      | ST            | CMOS           | General purpose I/O.                    |  |

|                                                    | P3C      | _             | CMOS           | PWM output.                             |  |

|                                                    | COM0     | _             | AN             | LCD Analog output.                      |  |

| RE4/P3B <sup>(1)</sup> /COM1                       | RE4      | ST            | CMOS           | General purpose I/O.                    |  |

|                                                    | P3B      | _             | CMOS           | PWM output.                             |  |

|                                                    | COM1     | _             | AN             | LCD Analog output.                      |  |

| RE5/P1C <sup>(1)</sup> /COM2                       | RE5      | ST            | CMOS           | General purpose I/O.                    |  |

|                                                    | P1C      | _             | CMOS           | PWM output.                             |  |

|                                                    | COM2     | _             | AN             | LCD Analog output.                      |  |

| RE6/P1B <sup>(1)</sup> /COM3                       | RE6      | ST            | _              | General purpose I/O.                    |  |

|                                                    | P1B      | _             | CMOS           | PWM output.                             |  |

|                                                    | COM3     | _             | AN             | LCD Analog output.                      |  |

| RE7/CCP2 <sup>(1)</sup> /P2A <sup>(1)</sup> /SEG31 | RE7      | ST            | CMOS           | General purpose I/O.                    |  |

|                                                    | CCP2     | ST            | CMOS           | Capture/Compare/PWM.                    |  |

|                                                    | P2A      | _             | CMOS           | PWM output.                             |  |

|                                                    | SEG31    | _             | AN             | LCD analog output.                      |  |

| RF0/AN16/CPS16/C1IN0-/C2IN0                        | RF0      | ST            | CMOS           | General purpose I/O.                    |  |

| /SEG41/VCAP                                        | AN16     | AN            | _              | A/D Channel input.                      |  |

|                                                    | CPS16    | AN            | —              | Capacitive sensing input.               |  |

|                                                    | C1IN0-   | AN            | —              | Comparator negative input.              |  |

|                                                    | C2IN0-   | AN            | _              | Comparator negative input.              |  |

|                                                    | SEG41    | _             | AN             | LCD Analog output.                      |  |

|                                                    | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator. |  |

| RF1/AN6/CPS6/C2OUT/SRNQ/                           | RF1      | ST            | CMOS           | General purpose I/O.                    |  |

| SEG19                                              | AN6      | AN            | —              | A/D Channel input.                      |  |

|                                                    | CPS6     | AN            | _              | Capacitive sensing input.               |  |

|                                                    | C2OUT    | _             | CMOS           | Comparator output.                      |  |

|                                                    | SRNQ     | _             | CMOS           | SR Latch inverting output.              |  |

|                                                    | SEG19    | _             | AN             | LCD Analog output.                      |  |

| RF2/AN7/CPS7/C1OUT/SRQ/                            | RF2      | ST            | CMOS           | General purpose I/O.                    |  |

| SEG20                                              | AN7      | AN            | —              | A/D Channel input.                      |  |

|                                                    | CPS7     | AN            | _              | Capacitive sensing input.               |  |

|                                                    | C10UT    |               | CMOS           | Comparator output.                      |  |

|                                                    | SRQ      | _             | CMOS           | SR Latch non-inverting output.          |  |

|                                                    | SEG20    |               | AN             | LCD Analog output.                      |  |

| TABLE 1-2: | PIC16(L)F1946/47 PINOUT DESCRIPTION (CONTINUED) |

|------------|-------------------------------------------------|

| IADLL I-2. |                                                 |

HV = High Voltage **Note 1:** Pin function is selectable via the APFCON register.

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

| Name                    | Function | Input<br>Type | Output<br>Type | Description                         |

|-------------------------|----------|---------------|----------------|-------------------------------------|

| RG2/AN14/CPS14/RX2/DT2/ | RG2      | ST            | CMOS           | General purpose I/O.                |

| C3IN+/SEG44             | AN14     | AN            | —              | A/D Channel input.                  |

|                         | CPS14    | AN            | _              | Capacitive sensing input.           |

|                         | RX2      | ST            | _              | USART2 asynchronous input.          |

|                         | DT2      | ST            | CMOS           | USART2 synchronous data.            |

|                         | C3IN+    | AN            | —              | Comparator positive input.          |

|                         | SEG44    |               | AN             | LCD Analog output.                  |

| RG3/AN13/CPS13/C3IN0-/  | RG3      | ST            | CMOS           | General purpose I/O.                |

| CCP4/P3D/SEG45          | AN13     | AN            | _              | A/D Channel input.                  |

|                         | CPS13    | AN            | —              | Capacitive sensing input.           |

|                         | C3IN0-   | AN            | —              | Comparator negative input.          |

|                         | CCP4     | ST            | CMOS           | Capture/Compare/PWM.                |

|                         | P3D      |               | CMOS           | PWM output.                         |

|                         | SEG45    |               | AN             | LCD Analog output.                  |

| RG4/AN12/CPS12/C3IN1-/  | RG4      | ST            | CMOS           | General purpose I/O.                |

| CCP5/P1D/SEG26          | AN12     | AN            | —              | A/D Channel input.                  |

|                         | CPS12    | AN            | —              | Capacitive sensing input.           |

|                         | C3IN1-   | AN            | —              | Comparator negative input.          |

|                         | CCP5     | ST            | CMOS           | Capture/Compare/PWM.                |

|                         | P1D      |               | CMOS           | PWM output.                         |

|                         | SEG26    |               | AN             | LCD Analog output.                  |

| RG5/MCLR/VPP            | RG5      | ST            | _              | General purpose input.              |

|                         | MCLR     | ST            | _              | Master Clear with internal pull-up. |

|                         | Vpp      | HV            | _              | Programming voltage.                |

| Vdd                     | Vdd      | Power         | _              | Positive supply.                    |

| Vss                     | Vss      | Power         | _              | Ground reference.                   |

|  | TABLE 1-2: | PIC16(L)F1946/47 PINOUT DESCRIPTION (CONTINUED) |

|--|------------|-------------------------------------------------|

|--|------------|-------------------------------------------------|

OD = Open-drain

Legend:

AN

= Analog input or output

CMOS =

CMOS compatible input or output

OD

TTL =

TTL compatible input

ST

=

Schmitt Trigger input with CMOS levels

I<sup>2</sup>C

= Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Pin function is selectable via the APFCON register.

# PIC16(L)F1946/1947

| Address                | Name                                                                                                      | Bit 7                                                    | Bit 6                        | Bit 5          | Bit 4        | Bit 3        | Bit 2        | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------|----------------|--------------|--------------|--------------|--------|-----------|----------------------|---------------------------------|

| Bank 2                 |                                                                                                           |                                                          |                              |                |              |              |              |        |           |                      |                                 |

| 100h <sup>(2)</sup>    | Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                                                          |                              |                |              |              |              |        |           |                      | xxxx xxxx                       |

| 101h <sup>(2)</sup>    | INDF1                                                                                                     |                                                          | this location ical register) | uses contents  | s of FSR1H/F | SR1L to addr | ess data mer | mory   |           | xxxx xxxx            | xxxx xxxx                       |

| 102h <sup>(2)</sup>    | PCL                                                                                                       | Program Co                                               | ounter (PC) L                | east Significa | nt Byte      |              |              |        |           | 0000 0000            | 0000 0000                       |

| 103h <sup>(2)</sup>    | STATUS                                                                                                    | _                                                        | – – – TO PD Z DC C           |                |              |              |              |        |           |                      | q quuu                          |

| 104h <sup>(2)</sup>    | FSR0L                                                                                                     | Indirect Data Memory Address 0 Low Pointer               |                              |                |              |              |              |        |           | 0000 0000            | uuuu uuuu                       |

| 105h <sup>(2)</sup>    | FSR0H                                                                                                     | Indirect Dat                                             | a Memory Ad                  | ldress 0 High  | Pointer      |              |              |        |           | 0000 0000            | 0000 0000                       |

| 106h <sup>(2)</sup>    | FSR1L                                                                                                     | Indirect Dat                                             | a Memory Ad                  | Idress 1 Low   | Pointer      |              |              |        |           | 0000 0000            | uuuu uuuu                       |

| 107h <sup>(2)</sup>    | FSR1H                                                                                                     | Indirect Dat                                             | a Memory Ad                  | ldress 1 High  | Pointer      |              |              |        |           | 0000 0000            | 0000 0000                       |

| 108h <sup>(2)</sup>    | BSR                                                                                                       |                                                          | — — — BSR<4:0>               |                |              |              |              |        | 0 0000    | 0 0000               |                                 |

| 109h <sup>(2)</sup>    | WREG                                                                                                      | Working Re                                               | Working Register             |                |              |              |              |        | 0000 0000 | uuuu uuuu            |                                 |

| 10Ah <sup>(1, 2)</sup> | PCLATH                                                                                                    | Write Buffer for the upper 7 bits of the Program Counter |                              |                |              |              |              |        | -000 0000 | -000 0000            |                                 |

| 10Bh <sup>(2)</sup>    | INTCON                                                                                                    | GIE                                                      | PEIE                         | TMR0IE         | INTE         | IOCIE        | TMR0IF       | INTF   | IOCIF     | 0000 000x            | 0000 000u                       |

| 10Ch                   | LATA                                                                                                      | PORTA Da                                                 | PORTA Data Latch             |                |              |              |              |        |           |                      | uuuu uuuu                       |

| 10Dh                   | LATB                                                                                                      | PORTB Da                                                 | PORTB Data Latch             |                |              |              |              |        |           |                      | uuuu uuuu                       |

| 10Eh                   | LATC                                                                                                      | PORTC Da                                                 | PORTC Data Latch             |                |              |              |              |        |           | xxxx xxxx            | uuuu uuuu                       |

| 10Fh                   | LATD                                                                                                      | PORTD Da                                                 | PORTD Data Latch             |                |              |              |              |        |           | xxxx xxxx            | uuuu uuuu                       |

| 110h                   | LATE                                                                                                      | PORTE Da                                                 | ta Latch                     |                |              |              |              |        |           | xxxx xxxx            | uuuu uuuu                       |

| 111h                   | CM1CON0                                                                                                   | C10N                                                     | C10UT                        | C10E           | C1POL        | _            | C1SP         | C1HYS  | C1SYNC    | 0000 -100            | 0000 -100                       |

| 112h                   | CM1CON1                                                                                                   | C1INTP                                                   | C1INTN                       | C1PCH1         | C1PCH0       | _            | _            | C1NC   | H<1:0>    | 000000               | 000000                          |

| 113h                   | CM2CON0                                                                                                   | C2ON                                                     | C2OUT                        | C2OE           | C2POL        | _            | C2SP         | C2HYS  | C2SYNC    | 0000 -100            | 0000 -100                       |

| 114h                   | CM2CON1                                                                                                   | C2INTP                                                   | C2INTN                       | C2PCH1         | C2PCH0       | _            | _            | C2NC   | H<1:0>    | 000000               | 000000                          |

| 115h                   | CMOUT                                                                                                     |                                                          |                              | _              | _            | _            | MC3OUT       | MC2OUT | MC1OUT    | 000                  | 000                             |

| 116h                   | BORCON                                                                                                    | SBOREN                                                   |                              | _              | _            | _            | _            | _      | BORRDY    | 1 q                  | uu                              |

| 117h                   | FVRCON                                                                                                    | FVREN                                                    | FVRRDY                       | TSEN           | TSRNG        | CDAFVR1      | CDAFVR0      | ADFV   | R<1:0>    | 0q00 0000            | 0q00 0000                       |

| 118h                   | DACCON0                                                                                                   | DACEN                                                    | DACLPS                       | DACOE          | _            | DACPS        | S<1:0>       | _      | DACNSS    | 000- 00-0            | 000- 00-0                       |

| 119h                   | DACCON1                                                                                                   | _                                                        | _                            | _              |              | D            | 0 0000       | 0 0000 |           |                      |                                 |

| 11Ah                   | SRCON0                                                                                                    | SRLEN                                                    | SRCLK2                       | SRCLK1         | SRCLK0       | SRQEN        | SRNQEN       | SRPS   | SRPR      | 0000 0000            | 0000 0000                       |

| 11Bh                   | SRCON1                                                                                                    | SRSPE                                                    | SRSCKE                       | SRSC2E         | SRSC1E       | SRRPE        | SRRCKE       | SRRC2E | SRRC1E    | 0000 0000            | 0000 0000                       |

| 11Ch                   | —                                                                                                         | Unimpleme                                                | nted                         |                |              |              |              |        |           | —                    | —                               |

| 11Dh                   | APFCON                                                                                                    | P3CSEL                                                   | P3BSEL                       | P2DSEL         | P2CSEL       | P2BSEL       | CCP2SEL      | P1CSEL | P1BSEL    | 0000 0000            | 0000 0000                       |

| 11Eh                   | CM3CON0                                                                                                   | C3ON                                                     | C3OUT                        | C3OE           | C3POL        | _            | C3SP         | C3HYS  | C3SYNC    | 0000 -100            | 0000 -100                       |

| 11Fh                   | CM3CON1                                                                                                   | C3INTP                                                   | C3INTN                       | C3PCH1         | C3PCH0       | _            | _            | C3NC   | H<1:0>    | 000000               | 000000                          |

#### TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

**3:** Unimplemented, read as '1'.

### 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See **Section 5.3 "Clock Switching**"for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase-Lock Loop, HFPLL that can produce one of three internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- The MFINTOSC (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

# 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory-calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.7** "Internal **Oscillator Clock Switch Timing**" for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

A fast start-up oscillator allows internal circuits to power-up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

#### 5.2.2.2 MFINTOSC

The Medium-Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.7** "Internal Oscillator Clock Switch Timing" for more information.

The MFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

The Medium-Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

#### 5.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4xPLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Words, the 4xPLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4xPLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4xPLL with the internal oscillator.

# 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table .

Start-up delay specifications are located in the oscillator tables of **Section 30.0** "**Electrical Specifications**"

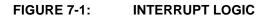

# 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the PIC microcontroller from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

| R/W-0/       | 0 R/W-0/0                        | R-0/0                              | R-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|--------------|----------------------------------|------------------------------------|-----------------|------------------|------------------|------------------|--------------|

| TMR1G        | IF ADIF                          | RCIF                               | TXIF            | SSPIF            | CCP1IF           | TMR2IF           | TMR1IF       |

| bit 7        |                                  |                                    |                 |                  |                  |                  | bit          |

|              |                                  |                                    |                 |                  |                  |                  |              |

| Legend:      |                                  |                                    |                 |                  |                  |                  |              |

| R = Read     | able bit                         | W = Writable                       | bit             | U = Unimple      | mented bit, read | l as '0'         |              |

| u = Bit is   | unchanged                        | x = Bit is unk                     | nown            | -n/n = Value     | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is | set                              | '0' = Bit is cle                   | eared           |                  |                  |                  |              |

| bit 7        | TMR1GIF:                         | Timer1 Gate Inte                   | errupt Flag bit |                  |                  |                  |              |

|              |                                  | pt is pending                      |                 |                  |                  |                  |              |

|              |                                  | pt is not pending                  |                 |                  |                  |                  |              |

| bit 6        | ADIF: A/D                        | Converter Interru                  | upt Flag bit    |                  |                  |                  |              |

|              | 1 = Interru                      | pt is pending                      |                 |                  |                  |                  |              |

|              |                                  | pt is not pending                  |                 |                  |                  |                  |              |

| bit 5        | RCIF: USA                        | ART1 Receive Int                   | errupt Flag bi  | t                |                  |                  |              |

|              |                                  | pt is pending<br>pt is not pending |                 |                  |                  |                  |              |

| bit 4        | TXIF: USA                        | RT1 Transmit Inf                   | errupt Flag bi  | t                |                  |                  |              |

|              | 1 = Interru                      | pt is pending                      |                 |                  |                  |                  |              |

|              | 0 = Interru                      | pt is not pending                  |                 |                  |                  |                  |              |

| bit 3        | SSPIF: Sy                        | nchronous Serial                   | Port (MSSP1     | ) Interrupt Flag | ı bit            |                  |              |

|              |                                  | pt is pending                      |                 |                  |                  |                  |              |

|              |                                  | pt is not pending                  |                 |                  |                  |                  |              |

| bit 2        |                                  | CP1 Interrupt Fla                  | ag bit          |                  |                  |                  |              |

|              |                                  | pt is pending<br>pt is not pending |                 |                  |                  |                  |              |

| bit 1        |                                  |                                    | orrunt Eloa bit |                  |                  |                  |              |

|              |                                  | imer2 to PR2 Int<br>pt is pending  | enupt riag bit  |                  |                  |                  |              |

|              |                                  | pt is not pending                  |                 |                  |                  |                  |              |

| bit 0        |                                  | imer1 Overflow I                   | nterrupt Flag   | bit              |                  |                  |              |

|              |                                  | pt is pending                      | interrupt i lug |                  |                  |                  |              |

|              |                                  | pt is not pending                  |                 |                  |                  |                  |              |

| Note:        | Interrupt flag bit               | s are set when ar                  | n interrupt     |                  |                  |                  |              |

|              |                                  | s, regardless of th                |                 |                  |                  |                  |              |

|              |                                  | ig enable bit or t                 |                 |                  |                  |                  |              |

|              | Enable bit, GIE<br>User software | , of the INTCON<br>e should ens    | •               |                  |                  |                  |              |

|              |                                  | rrupt flag bits are                |                 |                  |                  |                  |              |

|              | to enabling an ir                |                                    |                 |                  |                  |                  |              |

# REGISTER 7-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/        | 0 R/W-0/0                         | R/W-0/0            | R/W-0/0         | R/W-0/0      | R/W-0/0          | U-0          | R/W-0/0      |

|---------------|-----------------------------------|--------------------|-----------------|--------------|------------------|--------------|--------------|

| OSFIF         | C2IF                              | C1IF               | EEIF            | BCLIF        | LCDIF            | —            | CCP2IF       |

| bit 7         |                                   |                    |                 |              |                  |              | bit (        |

|               |                                   |                    |                 |              |                  |              |              |

| Legend:       |                                   |                    |                 |              |                  | (0)          |              |

| R = Reada     |                                   | W = Writable       |                 | •            | mented bit, read |              |              |

|               | unchanged                         | x = Bit is unki    |                 | -n/n = Value | at POR and BOF   | Value at all | other Resets |

| '1' = Bit is  | set                               | '0' = Bit is cle   | ared            |              |                  |              |              |

| bit 7         | <b>OSFIF:</b> Osci                | llator Fail Interr | upt Flag bit    |              |                  |              |              |

|               | 1 = Interrupt                     | is pending         |                 |              |                  |              |              |

|               | 0 = Interrupt                     | is not pending     |                 |              |                  |              |              |

| bit 6         | C2IF: Comp                        | arator C2 Interr   | upt Flag bit    |              |                  |              |              |

|               | 1 = Interrupt                     | 1 0                |                 |              |                  |              |              |

|               |                                   | is not pending     |                 |              |                  |              |              |

| bit 5         | -                                 | arator C1 Interr   | upt Flag bit    |              |                  |              |              |

|               | 1 = Interrupt                     |                    |                 |              |                  |              |              |

| <b>b</b> :+ 4 |                                   | is not pending     |                 |              |                  |              |              |

| bit 4         |                                   | OM Write Com       |                 | DI FIAG DI   |                  |              |              |

|               | 1 = Interrupt<br>0 = Interrupt    | is not pending     |                 |              |                  |              |              |

| bit 3         | •                                 | SP1 Bus Collisio   | n Interrupt Fla | a bit        |                  |              |              |

|               | 1 = Interrupt                     |                    |                 | 9 - 1        |                  |              |              |

|               |                                   | is not pending     |                 |              |                  |              |              |

| bit 2         | LCDIF: LCD                        | Module Interru     | ot Flag bit     |              |                  |              |              |

|               | 1 = Interrupt                     | is pending         |                 |              |                  |              |              |

|               | 0 = Interrupt                     | is not pending     |                 |              |                  |              |              |

| bit 1         | Unimpleme                         | nted: Read as '    | 0'              |              |                  |              |              |

| bit 0         | CCP2IF: CC                        | P2 Interrupt Fla   | g bit           |              |                  |              |              |

|               | 1 = Interrupt                     |                    |                 |              |                  |              |              |

|               | 0 = Interrupt                     | is not pending     |                 |              |                  |              |              |

| Note:         | Interrupt flag bits               | are set when an    | interrunt       |              |                  |              |              |

|               | condition occurs,                 |                    |                 |              |                  |              |              |

|               | its corresponding                 | enable bit or th   | e Global        |              |                  |              |              |

|               | Enable bit, GIE,                  |                    | 0               |              |                  |              |              |

|               | User software appropriate interru | should ensu        |                 |              |                  |              |              |

|               | to enabling an inte               |                    |                 |              |                  |              |              |

# REGISTER 7-7: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

#### **10.1** Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 30.0 "Electrical Specifications**" for the LFINTOSC tolerances.

#### 10.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

| TABLE 10-1: WDI OPERATING MODES | TABLE 10-1: | WDT OPERATING MODES |

|---------------------------------|-------------|---------------------|

|---------------------------------|-------------|---------------------|

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 1.0       | 37     | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | ^              | Disabled    |

| 00        | Х      | Х              | Disabled    |

#### 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 10-2 for more information.

#### 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 5.0** "Oscillator **Module (With Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. See **Section 3.0** "**Memory Organization**" and STATUS register (**Register 3-1**) for more information.

| TABLE 10-2: WDT CLEARING CONDITIONS |

|-------------------------------------|

|-------------------------------------|

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                           |                              |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |

| CLRWDT Command                                           | Cleared                      |

| Oscillator Fail Detected                                 |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |

# 12.10 Register Definitions: PORTD

#### REGISTER 12-13: PORTD: PORTD REGISTER

|                                         |         | -                                                     |              |                  |          |         |         |

|-----------------------------------------|---------|-------------------------------------------------------|--------------|------------------|----------|---------|---------|

| R/W-x/u                                 | R/W-x/u | R/W-x/u                                               | R/W-x/u      | R/W-x/u          | R/W-x/u  | R/W-x/u | R/W-x/u |

| RD7                                     | RD6     | RD5                                                   | RD4          | RD3              | RD2      | RD1     | RD0     |

| bit 7                                   | ·       |                                                       |              | •                |          |         | bit 0   |

|                                         |         |                                                       |              |                  |          |         |         |

| Legend:                                 |         |                                                       |              |                  |          |         |         |

| R = Readable bit W = Writable bit       |         |                                                       | U = Unimpler | nented bit, read | 1 as '0' |         |         |

| u = Bit is unchanged x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |              |                  |          |         |         |

| '1' = Bit is set '0' = Bit is cleared   |         |                                                       |              |                  |          |         |         |

bit 7-0 **RD<7:0>**: PORTD General Purpose I/O Pin bits 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

#### REGISTER 12-14: TRISD: PORTD TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISD<7:0>: PORTD Tri-State Control bits

1 = PORTD pin configured as an input (tri-stated)

0 = PORTD pin configured as an output

#### REGISTER 12-15: LATD: PORTD DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATD7   | LATD6   | LATD5   | LATD4   | LATD3   | LATD2   | LATD1   | LATD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATD<7:0>: PORTD Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

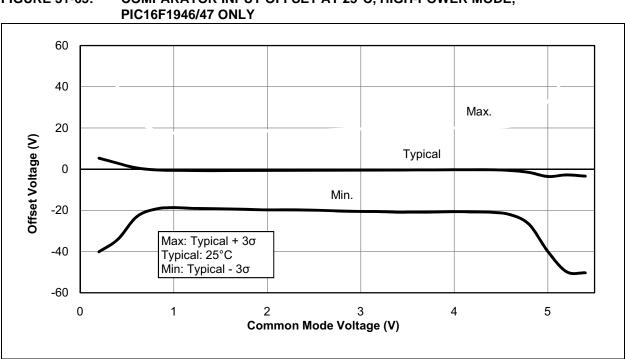

#### 18.7 Comparator Negative Input Selection

The CxNCH<1:0> bits of the CMxCON0 register direct one of four analog pins to the comparator inverting input.

| Note: | To use CxIN+ and CxINx- pins as analog     |

|-------|--------------------------------------------|

|       | input, the appropriate bits must be set in |

|       | the ANSEL register and the correspond-     |

|       | ing TRIS bits must also be set to disable  |

|       | the output drivers.                        |

# 18.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 30.0 "Electrical Specifications"** for more details.

# 18.9 Interaction with ECCP Logic

The comparators can be used as general purpose comparators. Their outputs can be brought out to the CxOUT pins. When the ECCP Auto-Shutdown is active it can use one or both comparator signals. If auto-restart is also enabled, the comparators can be configured as a closed loop analog feedback to the ECCP, thereby, creating an analog controlled PWM.

Note: When the Comparator module is first initialized the output state is unknown. Upon initialization, the user should verify the output state of the comparator prior to relying on the result, primarily when using the result in connection with other peripheral features, such as the ECCP Auto-Shutdown mode.

# 18.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

> Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

# 24.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN bit of the SSPxCON2 register.

| Note: | The MSSPx module must be in an Idle     |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The Baud Rate Generator begins counting and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSPx is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

#### 24.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 24.6.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

#### 24.6.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 24.6.7.4 Typical Receive Sequence

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDAx pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSPx module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSPx module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- User sets the RCEN bit of the SSPxCON2 register and the Master clocks in a byte from the slave.

- 9. After the eighth falling edge of SCLx, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPxUF, clears BF.

- 11. Master sets ACK value sent to slave in ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Masters ACK is clocked out to the Slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

# 25.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 25.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXxSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART. If the RXx/DTx or TXx/CKx pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

The TRIS bits corresponding to the RXx/DTx and TXx/CKx pins should be set.

#### 25.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TXx/CKx line. The TXx/CKx pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

## 25.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDxCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock and is sampled on the rising edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock and is sampled on the falling edge of each clock.

#### 25.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RXx/DTx pin. The RXx/DTx and TXx/CKx pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXxREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXxREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXxREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

| R/W-0/0                                 | R/W-0/0 | R/W-0/0           | R/W-0/0                                               | R/W-0/0      | R/W-0/0          | R/W-0/0 | R/W-0/0 |

|-----------------------------------------|---------|-------------------|-------------------------------------------------------|--------------|------------------|---------|---------|

| SEn                                     | SEn     | SEn               | SEn                                                   | SEn          | SEn              | SEn     | SEn     |

| bit 7                                   |         |                   |                                                       |              |                  |         | bit 0   |

|                                         |         |                   |                                                       |              |                  |         |         |

| Legend:                                 |         |                   |                                                       |              |                  |         |         |

| R = Readable                            | bit     | W = Writable      | bit                                                   | U = Unimpler | mented bit, read | as '0'  |         |

| u = Bit is unchanged x = Bit is unknown |         |                   | -n/n = Value at POR and BOR/Value at all other Resets |              |                  |         |         |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared                                                  |              |                  |         |         |

#### REGISTER 27-5: LCDSEn: LCD SEGMENT ENABLE REGISTERS

bit 7-0 SEn: Segment Enable bits

1 = Segment function of the pin is enabled

0 = I/O function of the pin is enabled

#### REGISTER 27-6: LCDDATAn: LCD DATA REGISTERS

| R/W-x/u   |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| SEGx-COMy |

| bit 7     |           |           |           |           |           |           | bit 0     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SEGx-COMy: Pixel On bits

1 = Pixel ON (dark) 0 = Pixel OFF (clear)

# 30.3 DC Characteristics: PIC16(L)F1946/47-I/E (Industrial, Extended) (Continued)

| PIC16LF | 1946/47                             |      |          |      |       |            |                                                  |  |  |

|---------|-------------------------------------|------|----------|------|-------|------------|--------------------------------------------------|--|--|

| PIC16F1 | 946/47                              |      |          |      |       |            |                                                  |  |  |

| Param   | Device                              |      | <b>-</b> |      | 11    | Conditions |                                                  |  |  |

| No.     | Characteristics                     | Min. | Тур†     | Max. | Units | Vdd        | Note                                             |  |  |

|         | Supply Current (IDD) <sup>(1,</sup> | 2)   |          |      |       |            |                                                  |  |  |