Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 54                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-QFN (9x9)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1946t-i-mr |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-2:** PIC16(L)F1946/47 PINOUT DESCRIPTION

| Name                     | Function | Input<br>Type | Output<br>Type | Description                                                                                       |

|--------------------------|----------|---------------|----------------|---------------------------------------------------------------------------------------------------|

| RA0/AN0/CPS0/SEG33       | RA0      | TTL           | CMOS           | General purpose I/O.                                                                              |

|                          | AN0      | AN            | _              | A/D Channel input.                                                                                |

|                          | CPS0     | AN            | _              | Capacitive sensing input 0.                                                                       |

|                          | SEG33    | _             | AN             | LCD Analog output.                                                                                |

| RA1/AN1/CPS1/SEG18       | RA1      | TTL           | CMOS           | General purpose I/O.                                                                              |

|                          | AN1      | AN            | _              | A/D Channel input.                                                                                |

|                          | CPS1     | AN            | _              | Capacitive sensing input.                                                                         |

|                          | SEG18    | _             | AN             | LCD Analog output.                                                                                |

| RA2/AN2/VREF-/CPS2/SEG34 | RA2      | TTL           | CMOS           | General purpose I/O.                                                                              |

|                          | AN2      | AN            | _              | A/D Channel input.                                                                                |

|                          | VREF-    | AN            | _              | A/D Negative Voltage Reference input.                                                             |

|                          | CPS2     | AN            |                | Capacitive sensing input.                                                                         |

|                          | SEG34    | _             | AN             | LCD Analog output.                                                                                |

| RA3/AN3/VREF+/CPS3/SEG35 | RA3      | TTL           | CMOS           | General purpose I/O.                                                                              |

|                          | AN3      | AN            |                | A/D Channel input.                                                                                |

|                          | VREF+    | AN            |                | A/D Voltage Reference input.                                                                      |

|                          | CPS3     | AN            |                | Capacitive sensing input.                                                                         |

|                          | SEG35    | —             | AN             | LCD Analog output.                                                                                |

| RA4/T0CKI/SEG14          | RA4      | TTL           | CMOS           | General purpose I/O.                                                                              |

|                          | TOCKI    | ST            | _              | Timer0 clock input.                                                                               |

|                          | SEG14    | —             | AN             | LCD Analog output.                                                                                |

| RA5/AN4/CPS4/SEG15       | RA5      | TTL           | CMOS           | General purpose I/O.                                                                              |

|                          | AN4      | AN            | —              | A/D Channel input.                                                                                |

|                          | CPS4     | AN            | _              | Capacitive sensing input.                                                                         |

|                          | SEG15    | _             | AN             | LCD Analog output.                                                                                |

| RA6/OSC2/CLKOUT/SEG36    | RA6      | TTL           | CMOS           | General purpose I/O.                                                                              |

|                          | OSC2     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                                                             |

|                          | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                                                    |

|                          | SEG36    | _             | AN             | LCD Analog output.                                                                                |

| RA7/OSC1/CLKIN/SEG37     | RA7      | TTL           | CMOS           | General purpose I/O.                                                                              |

|                          | OSC1     | XTAL          | —              | Crystal/Resonator (LP, XT, HS modes).                                                             |

|                          | CLKIN    | CMOS          |                | External clock input (EC mode).                                                                   |

|                          | SEG37    | —             | AN             | LCD Analog output.                                                                                |

| RB0/INT/SRI/FLT0/SEG30   | RB0      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up.    |

|                          | INT      | ST            | _              | External interrupt.                                                                               |

|                          | SRI      | _             | ST             | SR Latch input.                                                                                   |

|                          | FLT0     | ST            | _              | ECCP Auto-shutdown Fault input.                                                                   |

|                          | SEG30    | _             | AN             | LCD analog output.                                                                                |

| RB1/SEG8                 | RB1      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up. |

|                          | SEG8     | <u> </u>      | AN             | LCD Analog output.                                                                                |

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$

XTAL = Crystal

HV = High Voltage

levels

Note 1: Pin function is selectable via the APFCON register.

# PIC16(L)F1946/1947

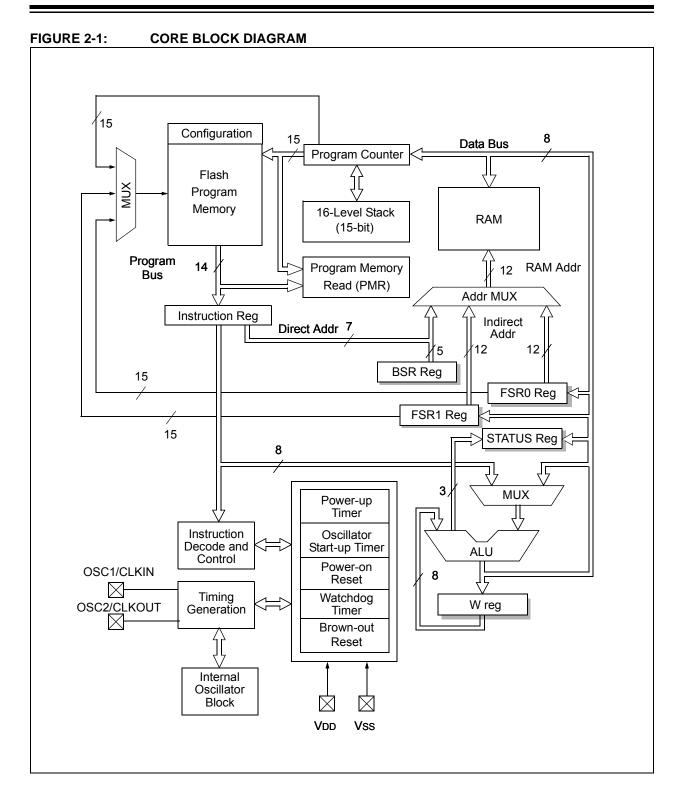

# 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

- Data EEPROM memory<sup>(1)</sup>

|         | Pro | Program Memory Control". |          |         |      |        |      |  |

|---------|-----|--------------------------|----------|---------|------|--------|------|--|

|         | Sec | tion 11                  | .0 "Data | EEPR    | ОМ а | nd Fl  | ash  |  |

|         | the | EECO                     | N regis  | ters is | dese | cribed | l in |  |

|         | met | hod to a                 | access F | lash m  | emor | y thro | ugh  |  |

| Note 1: | The | Data                     | EEPRO    | M Mei   | mory | and    | the  |  |

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

# 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1946/47 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 3-1 and 3-2).

# TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device        | Program Memory Space (Words) | Last Program Memory Address |  |  |

|---------------|------------------------------|-----------------------------|--|--|

| PIC16(L)F1946 | 8,192                        | 1FFFh                       |  |  |

| PIC16(L)F1947 | 16,384                       | 3FFFh                       |  |  |

# PIC16(L)F1946/1947

| Address                | Name   | Bit 7                                                                                                     | Bit 6                        | Bit 5          | Bit 4           | Bit 3        | Bit 2       | Bit 1      | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------|-----------------------------------------------------------------------------------------------------------|------------------------------|----------------|-----------------|--------------|-------------|------------|--------|----------------------|---------------------------------|

| Bank 15                | nk 15  |                                                                                                           |                              |                |                 |              |             |            |        |                      |                                 |

| 780h <sup>(2)</sup>    | INDF0  | Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                              |                |                 |              |             |            |        | xxxx xxxx            | xxxx xxxx                       |

| 781h <sup>(2)</sup>    | INDF1  |                                                                                                           | this location ical register) | uses contents  | s of FSR1H/F    | SR1L to addr | ess data me | mory       |        | xxxx xxxx            | XXXX XXXX                       |

| 782h <sup>(2)</sup>    | PCL    | Program C                                                                                                 | ounter (PC) L                | east Significa | nt Byte         |              |             |            |        | 0000 0000            | 0000 0000                       |

| 783h <sup>(2)</sup>    | STATUS |                                                                                                           |                              |                | TO              | PD           | Z           | DC         | С      | 1 1000               | q quuu                          |

| 784h <sup>(2)</sup>    | FSR0L  | Indirect Dat                                                                                              | ta Memory Ad                 | ldress 0 Low   | Pointer         |              |             |            |        | 0000 0000            | uuuu uuuu                       |

| 785h <sup>(2)</sup>    | FSR0H  | Indirect Dat                                                                                              | a Memory Ad                  | ldress 0 High  | Pointer         |              |             |            |        | 0000 0000            | 0000 0000                       |

| 786h <sup>(2)</sup>    | FSR1L  | Indirect Dat                                                                                              | ta Memory Ad                 | ldress 1 Low   | Pointer         |              |             |            |        | 0000 0000            | uuuu uuuu                       |

| 787h <sup>(2)</sup>    | FSR1H  | Indirect Dat                                                                                              | a Memory Ad                  | ldress 1 High  | Pointer         |              |             |            |        | 0000 0000            | 0000 0000                       |

| 788h <sup>(2)</sup>    | BSR    | _                                                                                                         | -                            | -              |                 | I            | BSR<4:0>    |            |        | 0 0000               | 0 0000                          |

| 789h <sup>(2)</sup>    | WREG   | Working Re                                                                                                | egister                      |                |                 |              |             |            |        | 0000 0000            | uuuu uuuu                       |

| 78Ah <sup>(1, 2)</sup> | PCLATH | _                                                                                                         | Write Buffer                 | for the upper  | 7 bits of the F | Program Cour | iter        |            |        | -000 0000            | -000 0000                       |

| 78Bh <sup>(2)</sup>    | INTCON | GIE                                                                                                       | PEIE                         | TMR0IE         | INTE            | IOCIE        | TMR0IF      | INTF       | IOCIF  | 0000 000x            | 0000 000u                       |

| 78Ch                   | _      | Unimpleme                                                                                                 | nted                         |                |                 |              |             |            |        | _                    | _                               |

| 78Dh                   | _      | Unimpleme                                                                                                 | Unimplemented                |                |                 |              |             |            |        |                      | _                               |

| 78Eh                   | _      | Unimpleme                                                                                                 | Unimplemented                |                |                 |              |             |            |        |                      | _                               |

| 78Fh                   | _      | Unimpleme                                                                                                 | nted                         |                |                 |              |             |            |        | -                    | _                               |

| 790h                   | _      | Unimpleme                                                                                                 | nted                         |                |                 |              |             |            |        | -                    | _                               |

| 791h                   | LCDCON | LCDEN                                                                                                     | SLPEN                        | WERR           | _               | CS<          | 1:0>        | LMU        | X<1:0> | 000- 0011            | 000- 0011                       |

| 792h                   | LCDPS  | WFT                                                                                                       | BIASMD                       | LCDA           | WA              |              | LP<3        | 3:0>       |        | 0000 0000            | 0000 0000                       |

| 793h                   | LCDREF | LCDIRE                                                                                                    | LCDIRS                       | LCDIRI         | —               | VLCD3PE      | VLCD2PE     | VLCD1PE    | -      | 000- 000-            | 000- 000-                       |

| 794h                   | LCDCST | _                                                                                                         | _                            | _              | _               | _            | L           | .CDCST<2:0 | )>     | 000                  | 000                             |

| 795h                   | LCDRL  | LRLA                                                                                                      | P<1:0>                       | LRLBI          | P<1:0>          | _            |             | LRLAT<2:0  | >      | 0000 -000            | 0000 -000                       |

| 796h                   | _      | Unimpleme                                                                                                 | nted                         |                |                 |              |             |            |        | -                    | _                               |

| 797h                   | _      | Unimpleme                                                                                                 | Unimplemented                |                |                 |              |             |            |        | -                    | _                               |

| 798h                   | LCDSE0 |                                                                                                           | SE<7:0>                      |                |                 |              |             |            |        | 0000 0000            | uuuu uuuu                       |

| 799h                   | LCDSE1 |                                                                                                           | SE<15:8>                     |                |                 |              |             |            |        | 0000 0000            | uuuu uuuu                       |

| 79Ah                   | LCDSE2 |                                                                                                           | SE<23:16>                    |                |                 |              |             |            |        | 0000 0000            | uuuu uuuu                       |

| 79Bh                   | LCDSE3 |                                                                                                           |                              |                | SE<31           | :24>         |             |            |        | 0000 0000            | uuuu uuuu                       |

| 79Ch                   | LCDSE4 |                                                                                                           |                              |                | SE<39           | :32>         |             |            |        | 0000 0000            | uuuu uuuu                       |

| 79Dh                   | LCDSE5 | _                                                                                                         | _                            |                |                 | SE<45:       | 40>         |            |        | 00 0000              | uu uuuu                         |

| 79Eh                   | _      | Unimpleme                                                                                                 | nted                         |                |                 |              |             |            |        | _                    | _                               |

#### TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1:

1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: Unimplemented, read as '1'.

# 7.6 Register Definitions: Interrupt Control

| R/W-0/0          | R/W-0/0                                                                                                                          | R/W-0/0                                                    | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0  | R-0/0      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|----------------|------------------|----------|------------|

| GIE              | PEIE                                                                                                                             | TMR0IE                                                     | INTE            | IOCIE          | TMR0IF           | INTF     | IOCIF      |

| bit 7            |                                                                                                                                  |                                                            |                 |                |                  |          | bit 0      |

| Legend:          |                                                                                                                                  |                                                            |                 |                |                  |          |            |

| R = Readable     | bit                                                                                                                              | W = Writable                                               | bit             | U = Unimpler   | mented bit, read | l as '0' |            |

| u = Bit is unch  |                                                                                                                                  | x = Bit is unkr                                            |                 | -              | at POR and BO    |          | her Resets |

| '1' = Bit is set |                                                                                                                                  | '0' = Bit is cle                                           |                 |                |                  |          |            |

| bit 7            |                                                                                                                                  | nterrupt Enable                                            |                 |                |                  |          |            |

|                  | 1 = Enables a<br>0 = Disables                                                                                                    | all active interru<br>all interrupts                       | ıpts            |                |                  |          |            |

| bit 6            | 1 = Enables a                                                                                                                    | eral Interrupt E<br>all active periph<br>all peripheral ir | eral interrupts | 3              |                  |          |            |

| bit 5            | 1 = Enables t                                                                                                                    | er0 Overflow Ir<br>he Timer0 inter<br>the Timer0 inte      | rupt            | e bit          |                  |          |            |

| bit 4            | 1 = Enables t                                                                                                                    | ternal Interrupt<br>he INT externa<br>the INT externa      | l interrupt     |                |                  |          |            |

| bit 3            | 1 = Enables t                                                                                                                    | upt-on-Change<br>he interrupt-on<br>the interrupt-or       | -change         |                |                  |          |            |

| bit 2            | <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed<br>0 = TMR0 register did not overflow      |                                                            |                 |                |                  |          |            |

| bit 1            | INTF: INT External Interrupt Flag bit<br>1 = The INT external interrupt occurred<br>0 = The INT external interrupt did not occur |                                                            |                 |                |                  |          |            |

| bit 0            | 1 = When at I                                                                                                                    | upt-on-Change<br>east one of the<br>he interrupt-on        | interrupt-on-   | change pins ch |                  |          |            |

# REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the interrupt-on-change flags in the IOCBF register have been cleared by software.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

| R/W-0/0          | R/W-0/0        | R/W-0/0                       | R/W/HC-0/0                                         | R/W-x/q           | R/W-0/0          | R/S/HC-0/0      | R/S/HC-0/0      |

|------------------|----------------|-------------------------------|----------------------------------------------------|-------------------|------------------|-----------------|-----------------|

| EEPGD            | CFGS           | LWLO                          | FREE                                               | WRERR             | WREN             | WR              | RD              |

| bit 7            | 0100           | Lifeo                         |                                                    |                   |                  |                 | bit (           |

|                  |                |                               |                                                    |                   |                  |                 |                 |

| Legend:          |                |                               |                                                    |                   |                  |                 |                 |

| R = Readable     |                | W = Writable                  |                                                    | •                 | mented bit, read |                 |                 |

| S = Bit can or   | -              | x = Bit is unk                |                                                    |                   | at POR and BO    |                 | ther Resets     |

| '1' = Bit is set |                | '0' = Bit is cle              | eared                                              | HC = Bit is ci    | eared by hardw   | are             |                 |

| bit 7            | EEPGD: Flas    | sh Program/Da                 | ta EEPROM M                                        | emory Select      | bit              |                 |                 |

|                  |                | s program spa<br>s data EEPRO | ce Flash memo<br>M memory                          | ory               |                  |                 |                 |

| bit 6            |                |                               | EEPROM or C                                        | Configuration 3   | Select bit       |                 |                 |

|                  |                |                               | n, User ID and                                     |                   |                  |                 |                 |

|                  |                | -                             | m or data EEP                                      | ROM Memory        | /                |                 |                 |

| bit 5            |                | Write Latches                 | •                                                  |                   |                  | <b>—</b>        |                 |

|                  |                |                               |                                                    |                   | EPGD = 1 (prog   |                 |                 |

|                  |                | next WR con<br>ated.          | nmand does no                                      | ot initiate a w   | rite; only the p | program memor   | ry latches an   |

|                  |                |                               | mand writes a v                                    | alue from EEI     | DATH:EEDATL      | into program m  | emory latche    |

|                  | and            | initiates a write             | e of all the data                                  | stored in the     | program memo     | ry latches.     |                 |

|                  |                | and EEPGD =                   | 0: (Accessing of                                   | lata EEPRON       | 4)               |                 |                 |

|                  |                |                               |                                                    |                   | e to the data E  | EPROM.          |                 |

| bit 4            | FREE: Progra   | am Flash Eras                 | e Enable bit                                       |                   |                  |                 |                 |

|                  | If CFGS = 1 (  | (Configuration                | space) OR <u>CF</u>                                | GS = 0 and El     | EPGD = 1 (prog   | gram Flash):    |                 |

|                  |                |                               |                                                    | on the next \     | NR command       | (cleared by h   | ardware afte    |

|                  |                | pletion of eras               | e).<br>peration on the                             | novt M/P.com      | mand             |                 |                 |

|                  | 0 - Fen        |                               | peration on the                                    |                   | imanu.           |                 |                 |

|                  |                |                               | 0: (Accessing                                      |                   |                  |                 |                 |

|                  | •              |                               |                                                    | will initiate bot | h a erase cycle  | and a write cyc | de.             |

| bit 3            |                | PROM Error F                  | •                                                  |                   |                  |                 |                 |

|                  |                |                               | improper prog<br>et attempt (write                 |                   | sequence atte    | mpt or termina  | tion (bit is se |

|                  |                |                               | operation comp                                     |                   | ,                |                 |                 |

| bit 2            |                | ram/Erase Ena                 |                                                    |                   | ,-               |                 |                 |

|                  | -              | rogram/erase o                |                                                    |                   |                  |                 |                 |

|                  | 0 = Inhibits p | programming/e                 | rasing of progra                                   | am Flash and      | data EEPROM      |                 |                 |

| bit 1            | WR: Write Co   | ontrol bit                    |                                                    |                   |                  |                 |                 |

|                  |                |                               |                                                    |                   | /erase operatio  |                 |                 |

|                  |                |                               | ned and the bit<br>e set (not cleare               |                   | hardware once    | operation is co | mplete.         |

|                  |                |                               |                                                    |                   | OM is complete   | e and inactive. |                 |

| bit 0            | RD: Read Co    |                               |                                                    |                   | F                |                 |                 |

|                  |                |                               |                                                    |                   |                  |                 |                 |

|                  | 1 = Initiates  | an program F                  | lash or data E                                     | EPROM read        | d. Read takes    | one cycle. RD   | is cleared in   |

|                  | hardware       | e. The RD bit o               | lash or data E<br>an only be set<br>ram Flash or d | (not cleared)     |                  | one cycle. RD   | is cleared i    |

#### REGISTER 11-5: EECON1: EEPROM CONTROL 1 REGISTER

| Name    | Bit 7  | Bit 6           | Bit 5  | Bit 4    | Bit 3  | Bit 2   | Bit 1   | Bit 0  | Register on<br>Page |

|---------|--------|-----------------|--------|----------|--------|---------|---------|--------|---------------------|

| ADCON0  | _      |                 |        | CHS<4:0> |        |         | GO/DONE | ADON   | 161                 |

| ANSELG  | —      | -               | _      | ANSG4    | ANSG3  | ANSG2   | ANSG1   | _      | 144                 |

| CCPxCON | PxM<   | 1:0> <b>(1)</b> | DCxB   | <1:0>    |        | CCPx    | ∕l<3:0> |        | 227                 |

| CMOUT   | —      | _               | _      | _        | _      | MC3OUT  | MC2OUT  | MC1OUT | 179                 |

| CM1CON1 | C1INTP | C1INTN          | C1PCH1 | C1PCH0   |        | —       | C1NCI   | H<1:0> | 179                 |

| CM2CON1 | C2INTP | C2INTN          | C2PCH1 | C2PCH0   | _      | —       | C2NCI   | H<1:0> | 179                 |

| CPSCON0 | CPSON  | CPSRM           | _      | _        | CPSRN  | IG<1:0> | CPSOUT  | TOXCS  | 322                 |

| CPSCON1 | —      | _               | _      | _        |        | CPSCI   | H<3:0>  |        | 323                 |

| LATG    | —      | _               | —      | LATG4    | LATG3  | LATG2   | LATG1   | LATG0  | 143                 |

| LCDCON  | LCDEN  | SLPEN           | WERR   | _        | CS<    | 1:0>    | LMUX    | <1:0>  | 326                 |

| LCDSE3  | SE31   | SE30            | SE29   | SE28     | SE27   | SE26    | SE25    | SE24   | 330                 |

| LCDSE5  | —      | _               | SE45   | SE44     | SE43   | SE42    | SE41    | SE40   | 330                 |

| PORTG   | —      | _               | RG5    | RG4      | RG3    | RG2     | RG1     | RG0    | 143                 |

| TRISG   | —      |                 | TRISG5 | TRISG4   | TRISG3 | TRISG2  | TRISG1  | TRISG0 | 143                 |

| WPUG    | —      | _               | WPUG5  | _        | _      | —       | —       | —      | 144                 |

| TABLE 12-17: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTG |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTG. **Note 1:** Applies to ECCP modules only.

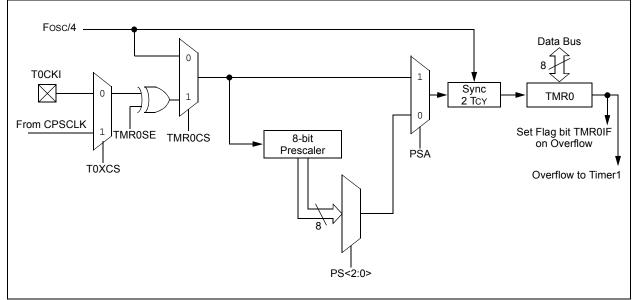

# 20.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- Programmable external clock edge selection

- · Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 20-1 is a block diagram of the Timer0 module.

# 20.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 20.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

| Note: | The value written to the TMR0 register   |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | can be adjusted, in order to account for |  |  |  |  |  |

|       | the two instruction cycle delay when     |  |  |  |  |  |

|       | TMR0 is written.                         |  |  |  |  |  |

# 20.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSCLK) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter mode using the Capacitive Sensing Oscillator (CPSCLK) signal is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

# FIGURE 20-1: BLOCK DIAGRAM OF THE TIMER0

# 21.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 21.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay, similar to the OST delay can be implemented in software by clearing the TMR1IF bit, then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and is reasonably stable.

# 21.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

### 21.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 21.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

# 21.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 21-3 for timing details.

TABLE 21-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

| R/W-0/0              | R/W-0/0                                                                                                                                                | R/W-0/0                                                                        | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| PxRSEN PxDC<6:0>     |                                                                                                                                                        |                                                                                |         |                                                       |         |         |         |  |  |

| bit 7                |                                                                                                                                                        |                                                                                |         |                                                       |         |         | bit (   |  |  |

|                      |                                                                                                                                                        |                                                                                |         |                                                       |         |         |         |  |  |

| Legend:              |                                                                                                                                                        |                                                                                |         |                                                       |         |         |         |  |  |

| R = Readable bit     |                                                                                                                                                        | W = Writable bit                                                               |         | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchanged |                                                                                                                                                        | x = Bit is unknown                                                             |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set     |                                                                                                                                                        | '0' = Bit is cle                                                               | ared    |                                                       |         |         |         |  |  |

|                      |                                                                                                                                                        |                                                                                |         |                                                       |         |         |         |  |  |

| bit 7                | PxRSEN: PWM Restart Enable bit                                                                                                                         |                                                                                |         |                                                       |         |         |         |  |  |

|                      | <ul> <li>1 = Upon auto-shutdown, the CCPxASE bit clears automatically once the shutdown event goes away;<br/>the PWM restarts automatically</li> </ul> |                                                                                |         |                                                       |         |         |         |  |  |

|                      | 0 = Upon a                                                                                                                                             | 0 = Upon auto-shutdown, CCPxASE must be cleared in software to restart the PWM |         |                                                       |         |         |         |  |  |

# REGISTER 23-5: PWMxCON: ENHANCED PWM CONTROL REGISTER<sup>(1)</sup>

#### bit 6-0 PxDC<6:0>: PWM Delay Count bits

PxDCx = Number of Fosc/4 (4 \* Tosc) cycles between the scheduled time when a PWM signal **should** transition active and the **actual** time it transitions active

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

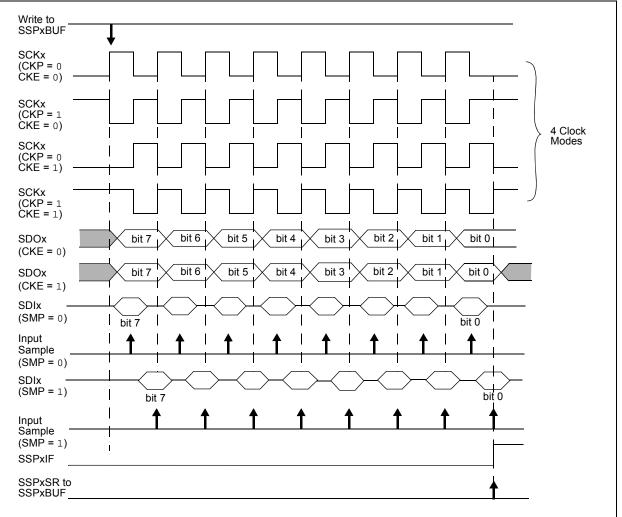

#### 24.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCKx line. The master determines when the slave (Processor 2, Figure 24-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDOx output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDIx pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPxCON1 register and the CKE bit of the SSPxSTAT register. This then, would give waveforms for SPI communication as shown in Figure 24-6, Figure 24-8 and Figure 24-9, where the MSb is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPxADD + 1))

Figure 24-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDOx data is valid before there is a clock edge on SCKx. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

FIGURE 24-6: SPI MODE WAVEFORM (MASTER MODE)

# 24.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCLx pin is held low (see **Section 24.5.6 "Clock Stretching"** for more details). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done, preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then, the SCLx pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCLx input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes Idle and waits for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be released by setting bit CKP.

An MSSPx interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 24.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDAx line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

# 24.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 24-17 can be used as a reference to this list.

- 1. Master sends a Start condition on SDAx and SCLx.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by the user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP is automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCLx, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- Note 1: If the master ACKs, the clock will be stretched.

ACKSTAT is the only bit updated on the rising edge of SCLx (9th) rather than on the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

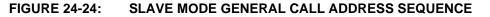

# 24.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address, regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 24-23 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCLx. The slave must then set its ACKDT value and release the clock with communication, progressing as it would normally.

#### 24.5.9 SSPx MASK REGISTER

An SSPx Mask (SSPxMSK) register (Register 24-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSPx operation until written with a mask value.

The SSPx Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0>, only. The SSPx mask has no effect during the reception of the first (high) byte of the address.

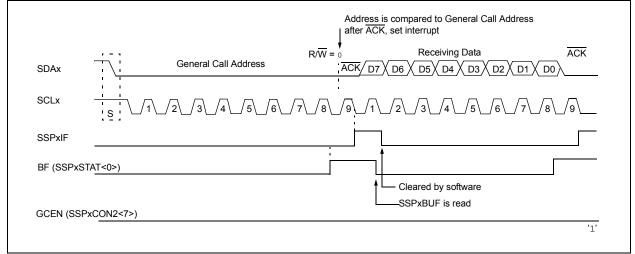

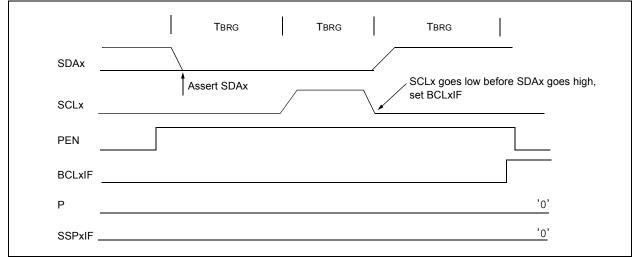

#### 24.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out.

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high.

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 24-37). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 24-38).

# FIGURE 24-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

# FIGURE 24-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# 25.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode would typically be used in RS-232 systems. The receiver block diagram is shown in Figure 25-2. The data is received on the RXx/DTx pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is made via the RCxREG register.

# 25.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCxSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RXx/DTx I/O pin as an input.

Note 1: If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

If the RXx/DTx pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

# 25.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 25.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCxIF interrupt flag bit of the PIR1/PIR3 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCxREG register.

| Note: | If the receive FIFO is overrun, no additional |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | characters will be received until the overrun |  |  |  |  |  |

|       | condition is cleared. See Section 25.1.2.5    |  |  |  |  |  |

|       | "Receive Overrun Error" for more              |  |  |  |  |  |

|       | information on overrun errors.                |  |  |  |  |  |

# 25.1.2.3 Receive Interrupts

The RCxIF interrupt flag bit of the PIR1/PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCxIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCxIF interrupts are enabled by setting the following bits:

- RCxIE interrupt enable bit of the PIE1/PIE4 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCxIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

# 25.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCxSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCxREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCxSTA register which resets the EUSART. Clearing the CREN bit of the RCxSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|

|       | FIFO have framing errors, repeated reads |  |  |  |  |

|       | of the RCxREG will not clear the FERR    |  |  |  |  |

|       | bit.                                     |  |  |  |  |

#### 25.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated If a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCxSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCxSTA register or by resetting the EUSART by clearing the SPEN bit of the RCxSTA register.

# 25.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set, the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

# 25.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCxSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCxIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

# 30.8 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. 1990 |                                       | 1   |                |  |  |

|---------|---------------------------------------|-----|----------------|--|--|

| Т       |                                       |     |                |  |  |

| F       | Frequency                             | Т   | Time           |  |  |

| Lowerc  | ase letters (pp) and their meanings:  |     |                |  |  |

| рр      |                                       |     |                |  |  |

| сс      | CCP1                                  | OSC | OSC1           |  |  |

| ck      | CLKOUT                                | rd  | RD             |  |  |

| CS      | CS                                    | rw  | RD or WR       |  |  |

| di      | SDI                                   | SC  | SCK            |  |  |

| do      | SDO                                   | SS  | SS             |  |  |

| dt      | Data in                               | tO  | TOCKI          |  |  |

| io      | I/O PORT                              | t1  | T1CKI          |  |  |

| mc      | MCLR                                  | wr  | WR             |  |  |

| Upperc  | Uppercase letters and their meanings: |     |                |  |  |

| S       |                                       |     |                |  |  |

| F       | Fall                                  | Р   | Period         |  |  |

| Н       | High                                  | R   | Rise           |  |  |

| I       | Invalid (High-impedance)              | V   | Valid          |  |  |

| L       | Low                                   | Z   | High-impedance |  |  |

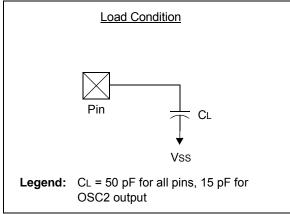

### FIGURE 30-5: LOAD CONDITIONS

# 30.9 AC Characteristics: PIC16(L)F1946/47-I/E

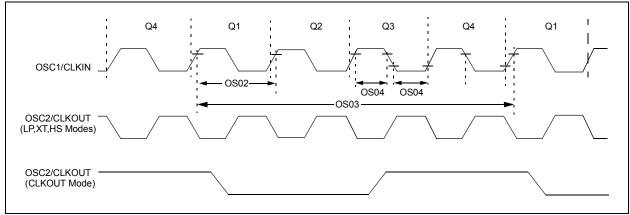

### FIGURE 30-6: CLOCK TIMING

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |                                         |      |        |          |       |                                |

|----------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------|------|--------|----------|-------|--------------------------------|

| Param<br>No.                                                                                                         | Sym.  | Characteristic                          | Min. | Тур†   | Max.     | Units | Conditions                     |

| OS01                                                                                                                 | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   | _      | 0.5      | MHz   | EC Oscillator mode (low)       |

|                                                                                                                      |       |                                         | DC   | —      | 4        | MHz   | EC Oscillator mode (medium)    |

|                                                                                                                      |       |                                         | DC   | _      | 20       | MHz   | EC Oscillator mode (high)      |

|                                                                                                                      |       | Oscillator Frequency <sup>(1)</sup>     | _    | 32.768 | _        | kHz   | LP Oscillator mode             |

|                                                                                                                      |       |                                         | 0.1  | —      | 4        | MHz   | XT Oscillator mode             |

|                                                                                                                      |       |                                         | 1    | —      | 4        | MHz   | HS Oscillator mode             |

|                                                                                                                      |       |                                         | 1    | —      | 20       | MHz   | HS Oscillator mode, VDD > 2.7V |

|                                                                                                                      |       |                                         | DC   | —      | 4        | MHz   | RC Oscillator mode, VDD > 2.0V |

| OS02                                                                                                                 | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27   | —      | ×        | μS    | LP Oscillator mode             |

|                                                                                                                      |       |                                         | 250  | —      | $\infty$ | ns    | XT Oscillator mode             |

|                                                                                                                      |       |                                         | 50   | —      | $\infty$ | ns    | HS Oscillator mode             |

|                                                                                                                      |       |                                         | 50   | —      | ×        | ns    | EC Oscillator mode             |

|                                                                                                                      |       | Oscillator Period <sup>(1)</sup>        | —    | 30.5   | _        | μS    | LP Oscillator mode             |

|                                                                                                                      |       |                                         | 250  | —      | 10,000   | ns    | XT Oscillator mode             |

|                                                                                                                      |       |                                         | 50   | —      | 1,000    | ns    | HS Oscillator mode             |

|                                                                                                                      |       |                                         | 250  | —      | —        | ns    | RC Oscillator mode             |

| OS03                                                                                                                 | Тсү   | Instruction Cycle Time <sup>(1)</sup>   | 200  | Тсү    | DC       | ns    | Tcy = 4/Fosc                   |

| OS04*                                                                                                                | TosH, | External CLKIN High,                    | 2    | _      | _        | μS    | LP oscillator                  |

|                                                                                                                      | TosL  | External CLKIN Low                      | 100  | —      | —        | ns    | XT oscillator                  |

|                                                                                                                      |       |                                         | 20   | —      | —        | ns    | HS oscillator                  |

\* These parameters are characterized but not tested.

† Data in <sup>i</sup> Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

# PIC16(L)F1946/47

# PIC16(L)F1946/47

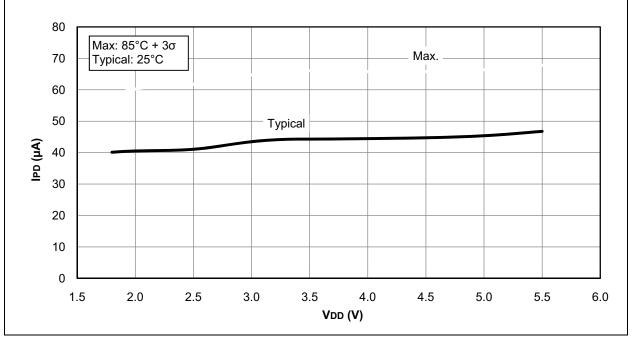

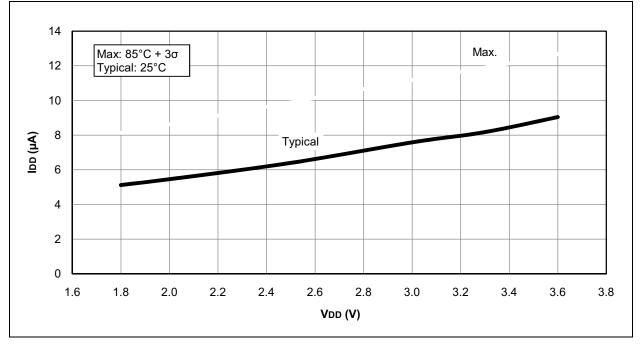

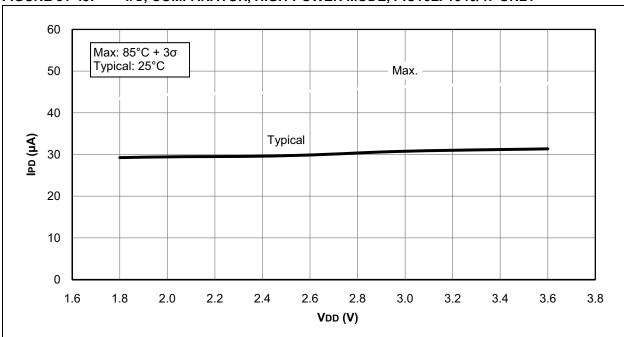

### FIGURE 31-49: IPD, COMPARATOR, HIGH-POWER MODE, PIC16LF1946/47 ONLY